Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XFI

| Betans                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 25                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-UFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-UQFN (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm103t-i-m5 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EVXXXGM00X/10X FAMILY

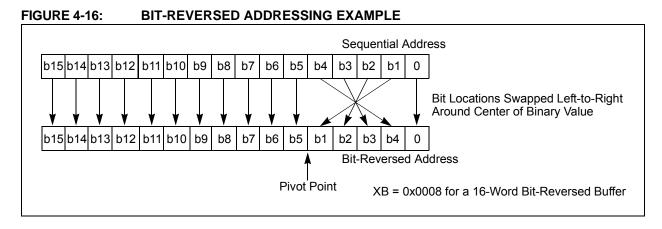

## TABLE 4-46: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | Idress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

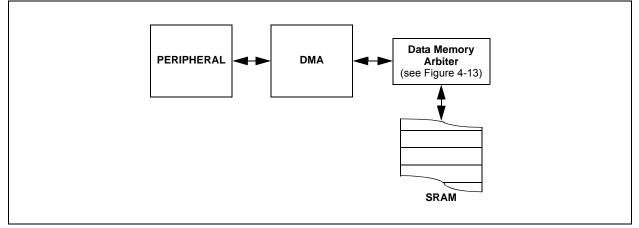

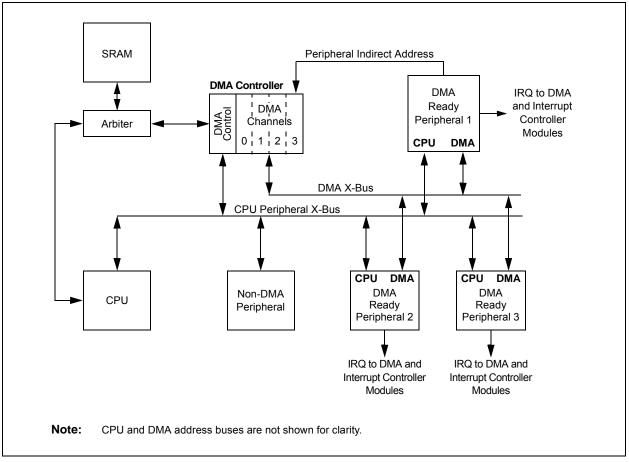

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

Figure 8-2 illustrates the DMA Controller block diagram.

## 8.1 DMAC Controller Registers

Each DMAC Channel x (where x = 0 to 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A High/Low (DMAxSTAH/L)

- 32-Bit DMA Channel x Start Address Register B High/Low (DMAxSTBH/L)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRH/L) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The DMA Interrupt Flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding DMA Interrupt Enable bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding DMA Interrupt Priority bits (DMAxIP) are located in an IPCx register in the interrupt controller.

NOTES:

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode, with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

Note: If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |

|---------------|-------|------------------|-----|------------------|------------------|-----------------|--------|

| R = Readable  | e bit | W = Writable     | bit | U = Unimpler     | mented bit, read | l as '0'        |        |

| Legend:       |       |                  |     |                  |                  |                 |        |

|               |       |                  |     |                  |                  |                 |        |

| bit 7         |       | <u>.</u>         | •   |                  |                  | •               | bit (  |

| —             | —     | —                | —   | _                | —                | —               | —      |

| U-0           | U-0   | U-0              | U-0 | U-0              | U-0              | U-0             | U-0    |

|               |       |                  |     |                  |                  |                 |        |

| bit 15        |       |                  |     |                  |                  | •               | bit    |

| —             | —     | —                | —   | —                | PWM3MD           | PWM2MD          | PWM1MD |

| U-0           | U-0   | U-0              | U-0 | U-0              | R/W-0            | R/W-0           | R/W-0  |

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 **PWM3MD: PWM1MD:** PWMx (x = 1-3) Module Disable bit

1 = PWMx module is disabled

0 = PWMx module is enabled

bit 7-0 Unimplemented: Read as '0'

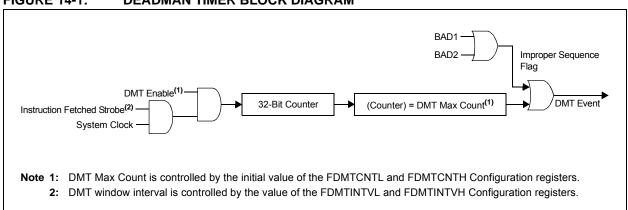

## 14.0 DEADMAN TIMER (DMT)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Deadman Timer (DMT)" (DS70005155) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT, which works on the system clock, is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs, until a count match occurs. Instructions are not fetched when the processor is in Sleep mode.

DMT can be enabled in the Configuration fuse or by software in the DMTCON register by setting the ON bit. The DMT consists of a 32-bit counter with a time-out count match value, as specified by the two 16-bit Configuration Fuse registers: FDMTCNTL and FDMTCNTH.

A DMT is typically used in mission-critical, and safetycritical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 14-1 shows a block diagram of the Deadman Timer module.

#### FIGURE 14-1: DEADMAN TIMER BLOCK DIAGRAM

| U-0           | U-0                                                                                                                                                                      | U-0                                                                              | U-0             | U-0              | U-0            | U-0              | U-0    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------|------------------|----------------|------------------|--------|--|--|--|

| _             | —                                                                                                                                                                        | _                                                                                | —               | —                | —              |                  | —      |  |  |  |

| bit 15        |                                                                                                                                                                          |                                                                                  |                 |                  |                |                  | bit 8  |  |  |  |

|               |                                                                                                                                                                          |                                                                                  |                 |                  |                |                  |        |  |  |  |

| R-0, HC       | R-0, HC                                                                                                                                                                  | R-0, HC                                                                          | U-0             | U-0              | U-0            | U-0              | R-0    |  |  |  |

| BAD1          | BAD2                                                                                                                                                                     | DMTEVENT                                                                         |                 | —                | _              |                  | WINOPN |  |  |  |

| bit 7         |                                                                                                                                                                          |                                                                                  |                 |                  |                |                  | bit 0  |  |  |  |

|               |                                                                                                                                                                          |                                                                                  |                 |                  |                |                  |        |  |  |  |

| Legend:       |                                                                                                                                                                          | HC = Hardwar                                                                     | e Clearable bit |                  |                |                  |        |  |  |  |

| R = Readable  | e bit                                                                                                                                                                    | W = Writable b                                                                   | it              | U = Unimple      | mented bit, re | <b>ad as</b> '0' |        |  |  |  |

| -n = Value at | POR                                                                                                                                                                      | '1' = Bit is set                                                                 |                 | '0' = Bit is cle | eared          | x = Bit is unk   | nown   |  |  |  |

| bit 15-8      | Unimplemer                                                                                                                                                               | nted: Read as '0                                                                 | 3               |                  |                |                  |        |  |  |  |

| bit 7         | BAD1: Dead                                                                                                                                                               | man Timer Bad                                                                    | STEP1<7:0> V    | alue Detect bit  |                |                  |        |  |  |  |

|               |                                                                                                                                                                          | STEP1<7:0> va<br>STEP1<7:0> va                                                   |                 |                  |                |                  |        |  |  |  |

| bit 6         | BAD2: Dead                                                                                                                                                               | man Timer Bad                                                                    | STEP2<7:0> V    | alue Detect bit  |                |                  |        |  |  |  |

|               |                                                                                                                                                                          | STEP2<7:0> va<br>STEP2<7:0> va                                                   |                 |                  |                |                  |        |  |  |  |

| bit 5         | DMTEVENT:                                                                                                                                                                | Deadman Time                                                                     | r Event bit     |                  |                |                  |        |  |  |  |

|               | <ul> <li>1 = Deadman Timer event was detected (counter expired, or bad STEP1&lt;7:0&gt; or STEP2&lt;7:0&gt; value<br/>was entered prior to counter increment)</li> </ul> |                                                                                  |                 |                  |                |                  |        |  |  |  |

| bit 4-1       |                                                                                                                                                                          | 0 = Deadman Timer event was not detected                                         |                 |                  |                |                  |        |  |  |  |

| bit 0         | -                                                                                                                                                                        | Unimplemented: Read as '0' WINORN: Deadman Timer Clear Window bit                |                 |                  |                |                  |        |  |  |  |

| Sit 0         | 1 = Deadmar                                                                                                                                                              | WINOPN: Deadman Timer Clear Window bit<br>1 = Deadman Timer clear window is open |                 |                  |                |                  |        |  |  |  |

|               | 0 = Deadman Timer clear window is not open                                                                                                                               |                                                                                  |                 |                  |                |                  |        |  |  |  |

#### REGISTER 14-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

## 15.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

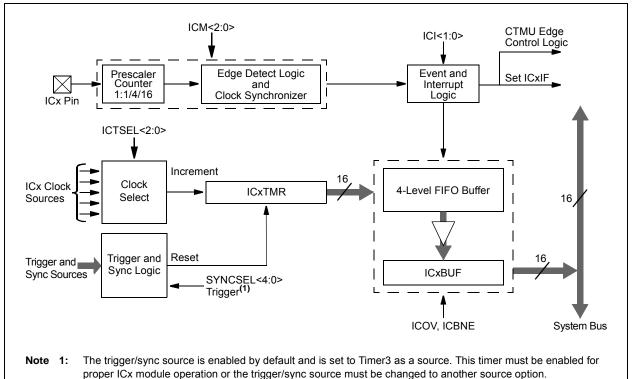

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EVXXXGM00X/10X family devices support 4 input capture channels.

Key features of the input capture module include:

- Hardware-Configurable for 32-Bit Operation in All Modes by Cascading Two Adjacent modules

- Synchronous and Trigger Modes of Output Compare Operation, with up to 31 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

Figure 15-1 shows a block diagram of the Input capture module.

#### FIGURE 15-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

# dsPIC33EVXXXGM00X/10X FAMILY

### REGISTER 17-18: AUXCONx: PWMx AUXILIARY CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|--------|-----|-----|-----|-----------|-----------|-----------|-----------|

| —      | —   |     | —   | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 |

| bit 15 |     |     |     |           |           |           | bit 8     |

| U-0   | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

|-------|-----|----------|----------|----------|----------|---------|---------|

| —     | —   | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN | CHOPLEN |

| bit 7 |     |          |          |          |          |         | bit 0   |

| Legend:      |                                                  |                                                                                           |                                |                                       |  |  |  |  |  |

|--------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------|--|--|--|--|--|

| R = Readab   | ole bit                                          | W = Writable bit                                                                          | U = Unimplemented bit,         | read as '0'                           |  |  |  |  |  |

| -n = Value a | at POR                                           | '1' = Bit is set                                                                          | '0' = Bit is cleared           | x = Bit is unknown                    |  |  |  |  |  |

| bit 15-12    | Unimple                                          | mented: Read as '0'                                                                       |                                |                                       |  |  |  |  |  |

| bit 11-8     | BLANKS                                           | SEL<3:0>: PWMx State Bla                                                                  | nk Source Select bits          |                                       |  |  |  |  |  |

|              | the BCH<br>1001 = F<br>•<br>•<br>0100 = F        | and BCL bits in the LEBCO<br>Reserved                                                     | Nx register).                  | ult input signals (if enabled through |  |  |  |  |  |

|              | 0001 = F                                         | PWM2H is selected as the s<br>PWM1H is selected as the s<br>No state blanking             |                                |                                       |  |  |  |  |  |

| bit 7-6      | Unimple                                          | mented: Read as '0'                                                                       |                                |                                       |  |  |  |  |  |

| bit 5-2      | CHOPSEL<3:0>: PWMx Chop Clock Source Select bits |                                                                                           |                                |                                       |  |  |  |  |  |

|              | The sele<br>1001 = F<br>•                        |                                                                                           | lisable (Chop) the selected PW | /Mx outputs.                          |  |  |  |  |  |

|              | 0010 = F<br>0001 = F                             | PWM3H is selected as the c<br>PWM2H is selected as the c<br>PWM1H is selected as the c    | hop clock source               |                                       |  |  |  |  |  |

| bit 1        | 1 = PWN                                          | EN: PWMxH Output Choppi<br>IxH chopping function is en<br>IxH chopping function is dis    | abled                          |                                       |  |  |  |  |  |

| bit 0        | L = PWN                                          | EN: PWMxL Output Choppin<br>IxL chopping function is ena<br>IxL chopping function is disa | ng Enable bit<br>abled         |                                       |  |  |  |  |  |

## 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. For more information, refer to the SPI specifications in Section 30.0 "Electrical Characteristics".

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

| U-0                 | U-0                              | U-0                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |

|---------------------|----------------------------------|-------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|

|                     |                                  |                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                                  |                                     | Diocon               | DICCDO                                 | MODEIO               | Olin                 | bit                  |

|                     |                                  |                                     |                      |                                        |                      |                      |                      |

| R/W-0               | R/W-0                            | R/W-0                               | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                              | MSTEN                               | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |                                  |                                     |                      | 1                                      |                      |                      | bit                  |

|                     |                                  |                                     |                      |                                        |                      |                      |                      |

| Legend:             |                                  |                                     |                      |                                        |                      |                      |                      |

| R = Readab          | le bit                           | W = Writable                        | bit                  | U = Unimplen                           | nented bit, read     | <b>l as</b> '0'      |                      |

| -n = Value a        | t POR                            | '1' = Bit is set                    |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr      | nown                 |

|                     |                                  |                                     | _ 1                  |                                        |                      |                      |                      |

| bit 15-13           | -                                | ted: Read as '                      |                      |                                        |                      |                      |                      |

| bit 12              |                                  | PI clock is disa                    | -                    | er modes only)                         |                      |                      |                      |

|                     |                                  | PI clock is disa<br>PI clock is ena |                      | ao 1/U                                 |                      |                      |                      |

| bit 11              |                                  | able SDOx Pin                       |                      |                                        |                      |                      |                      |

|                     | 1 = SDOx pin                     | is not used by                      | the module; p        | oin functions as                       | ; I/O                |                      |                      |

|                     |                                  | is controlled b                     |                      |                                        |                      |                      |                      |

| bit 10              | MODE16: Wo                       | ord/Byte Comm                       | unication Sele       | ect bit                                |                      |                      |                      |

|                     |                                  | cation is word-                     | , ,                  |                                        |                      |                      |                      |

|                     |                                  | cation is byte-                     | . ,                  |                                        |                      |                      |                      |

| bit 9               |                                  | ata Input Samp                      | ole Phase bit        |                                        |                      |                      |                      |

|                     | Master mode:                     | :<br>a is sampled at                | the end of da        | ta output time                         |                      |                      |                      |

|                     |                                  |                                     |                      | data output time                       | ie                   |                      |                      |

|                     | Slave mode:                      | -                                   |                      | n Slave mode.                          |                      |                      |                      |

| bit 8               | CKE: Clock E                     | dge Select bit                      | 1)                   |                                        |                      |                      |                      |

|                     |                                  |                                     |                      |                                        | clock state to Id    |                      |                      |

| bit 7               | SSEN: Slave                      | Select Enable                       | bit (Slave mo        | de) <sup>(2)</sup>                     |                      |                      |                      |

|                     |                                  | s used for Slav                     |                      |                                        |                      |                      |                      |

|                     | 0 = SSx pin is                   | s not used by the                   | ne module; pir       | n is controlled b                      | y port function      |                      |                      |

| bit 6               |                                  | olarity Select I                    |                      |                                        |                      |                      |                      |

|                     |                                  |                                     |                      | ve state is a low<br>e state is a high |                      |                      |                      |

| bit 5               | MSTEN: Mas                       | ter Mode Enab                       | le bit               |                                        |                      |                      |                      |

|                     | 1 = Master m<br>0 = Slave mo     |                                     |                      |                                        |                      |                      |                      |

|                     | he CKE bit is not<br>FRMEN = 1). | used in Frame                       | d SPI modes.         | Program this b                         | oit to '0' for Frai  | med SPI modes        | S                    |

| -                   | his bit must be cl               | eared when FF                       | RMEN = 1.            |                                        |                      |                      |                      |

|                     | o not set both pri               |                                     |                      | ers to the value                       | e of 1:1.            |                      |                      |

#### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### REGISTER 24-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5    | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | If SSRCG = 1:                                                                                                                                                                                               |

|            | 111 = Reserved<br>110 = Reserved                                                                                                                                                                            |

|            | 10 = Reserved                                                                                                                                                                                               |

|            | 100 = Reserved                                                                                                                                                                                              |

|            | 011 = Reserved                                                                                                                                                                                              |

|            | 010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion                                                                                                                           |

|            | 001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion                                                                                                                           |

|            | 000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion                                                                                                                           |

|            | If SSRCG = 0:                                                                                                                                                                                               |

|            | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                                                                   |

|            | 110 = CTMU ends sampling and starts conversion                                                                                                                                                              |

|            | 101 = Reserved                                                                                                                                                                                              |

|            | 100 = Timer5 compare ends sampling and starts conversion                                                                                                                                                    |

|            | 011 = PWM primary Special Event Trigger ends sampling and starts conversion                                                                                                                                 |

|            | 010 = Timer3 compare ends sampling and starts conversion<br>001 = Active transition on the INT0 pin ends sampling and starts conversion                                                                     |

|            | 000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)                                                                                                                      |

| <b>L:1</b> |                                                                                                                                                                                                             |

| bit 4      | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                      |

|            | See SSRC<2:0> for details.                                                                                                                                                                                  |

| bit 3      | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                          |

|            | In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':                                                                                                                                     |

|            | 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x) or samples CH0 and CH1                                                                                                                  |

|            | simultaneously (when CHPS<1:0> = 01)<br>0 = Samples multiple channels individually in sequence                                                                                                              |

| hit 0      |                                                                                                                                                                                                             |

| bit 2      | ASAM: ADCx Sample Auto-Start bit                                                                                                                                                                            |

|            | 1 = Sampling begins immediately after last conversion; SAMP bit is auto-set                                                                                                                                 |

|            | 0 = Sampling begins when SAMP bit is set                                                                                                                                                                    |

| bit 1      | SAMP: ADCx Sample Enable bit                                                                                                                                                                                |

|            | 1 = ADCx Sample-and-Hold amplifiers are sampling                                                                                                                                                            |

|            | 0 = ADCx Sample-and-Hold amplifiers are holding                                                                                                                                                             |

|            | If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write '0' to end sampling and start conversion. If SSRC<2:0> $\neq$ 000, |

|            | automatically cleared by hardware to end sampling and start conversion. If $33RC<2.07 \neq 000$ ,                                                                                                           |

| bit 0      | <b>DONE:</b> ADCx Conversion Status bit <sup>(1)</sup>                                                                                                                                                      |

| bit 0      | 1 = ADCx conversion cycle is completed.                                                                                                                                                                     |

|            | 0 = ADCx conversion has not started or is in progress                                                                                                                                                       |

|            | Automatically set by hardware when conversion is complete. Software can write '0' to clear DONE bit                                                                                                         |

|            | status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress.                                                                                                    |

|            | Automatically cleared by hardware at the start of a new conversion.                                                                                                                                         |

|            |                                                                                                                                                                                                             |

**Note 1:** Do not clear the DONE bit in software if auto-sample is enabled (ASAM = 1).

## 26.0 COMPARATOR VOLTAGE REFERENCE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 26.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRxCON registers (Register 26-1 and Register 26-2). The comparator voltage reference provides a range of output voltages with 128 distinct levels. The comparator reference supply voltage can come from either VDD and Vss, or the external CVREF+ and AVss pins. The voltage source is selected by the CVRSS bit (CVRxCON<11>). The settling time of the comparator voltage reference must be considered when changing the CVREF output.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS                 |       |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |  |

|------------------------------------|-------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param<br>No. Symbol Characteristic |       |                                                                     | Min.                                                                                                                                                                                                                                                                                | Тур. <sup>(1)</sup> | Max. | Units | Conditions         |  |

| OS50                               | Fplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 0.8                                                                                                                                                                                                                                                                                 |                     | 8.0  | MHz   | ECPLL, XTPLL modes |  |

| OS51                               | Fsys  | On-Chip VCO System<br>Frequency                                     | 120                                                                                                                                                                                                                                                                                 | —                   | 340  | MHz   |                    |  |

| OS52                               | TLOCK | PLL Start-up Time (Lock Time)                                       | 0.9                                                                                                                                                                                                                                                                                 | 1.5                 | 3.1  | ms    |                    |  |

| OS53                               | DCLK  | CLKO Stability (Jitter) <sup>(2)</sup>                              | -3                                                                                                                                                                                                                                                                                  | 0.5                 | 3    | %     |                    |  |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if FOSC = 120 MHz and the SPI bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHA                      | RACTERISTICS           |         | r <b>d Opera</b><br>ng tempe | rature -          | $40^{\circ}C \le T$ | <b>4.5V to 5.5V (unless o</b><br>$A \le +85^{\circ}C$ for Industrial<br>$A \le +125^{\circ}C$ for Extende | ,     |  |

|-----------------------------|------------------------|---------|------------------------------|-------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-------|--|

| Param<br>No. Characteristic |                        | Min.    | Тур.                         | Max.              | Units               | Condi                                                                                                     | tions |  |

| Internal                    | FRC Accuracy @ FRC Fre | equency | = 7.37 M                     | Hz <sup>(1)</sup> |                     |                                                                                                           |       |  |

| F20a                        | FRC                    | -1      | 0.5                          | +1                | %                   | $-40^{\circ}C \le TA \le +85^{\circ}C \qquad VDD = 4.5-5.5V$                                              |       |  |

| F20b                        | FRC                    | -2      | 1                            | +2                | %                   | $-40^{\circ}C \leq TA \leq +125^{\circ}C  VDD = 4.5-5.5V$                                                 |       |  |

Note 1: Frequency calibrated at +25°C and 5.0V. TUN<5:0> bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS               |                | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                          |                |  |  |

|----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------|----------------|--|--|

| Param<br>No.                     | Characteristic | Min.                                                                                                                                                                                                                                                                        | Тур. | Max. | Units | Conditions                               |                |  |  |

| LPRC @ 32.768 kHz <sup>(1)</sup> |                |                                                                                                                                                                                                                                                                             |      |      |       |                                          |                |  |  |

| F21a                             | LPRC           | -15                                                                                                                                                                                                                                                                         | 5    | +15  | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C$ | VDD = 4.5-5.5V |  |  |

| F21b                             | LPRC           | -30                                                                                                                                                                                                                                                                         | 10   | +30  | %     | $-40^\circ C \le T_A \le +125^\circ C$   | VDD = 4.5-5.5V |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

<sup>© 2013-2016</sup> Microchip Technology Inc.

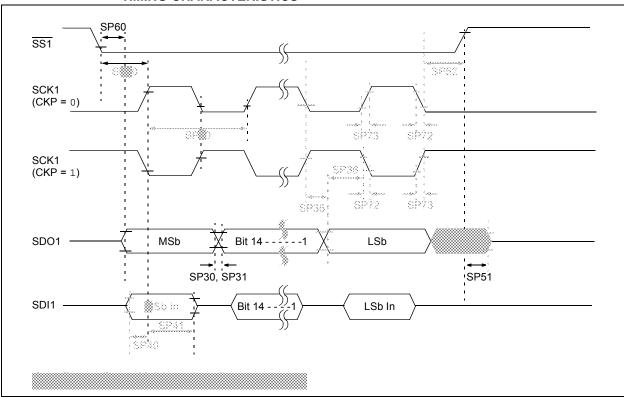

#### FIGURE 30-24: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## dsPIC33EVXXXGM00X/10X FAMILY

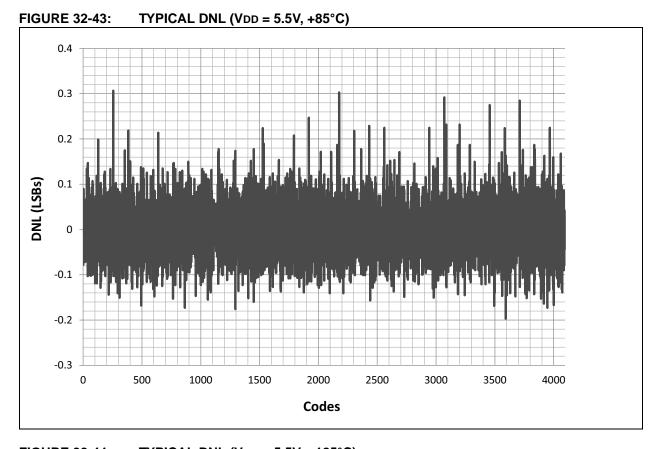

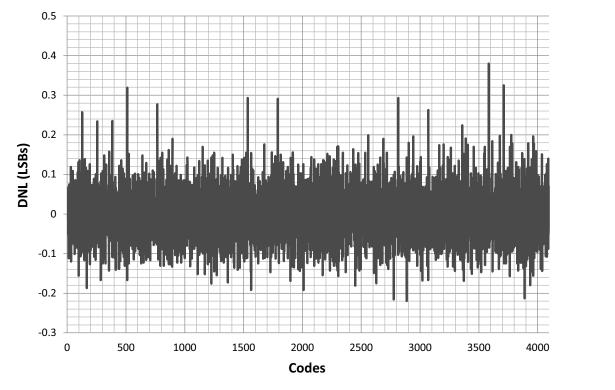

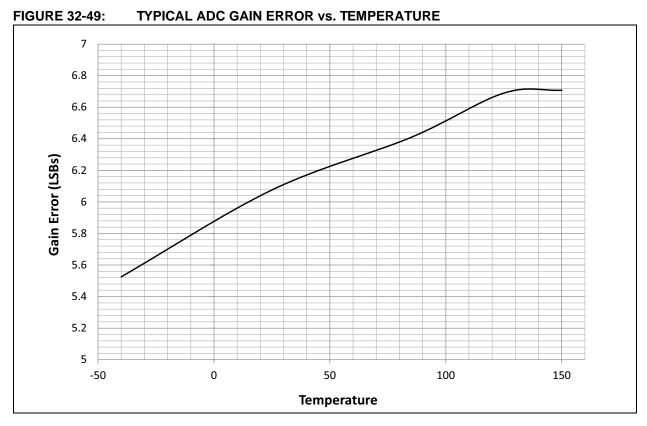

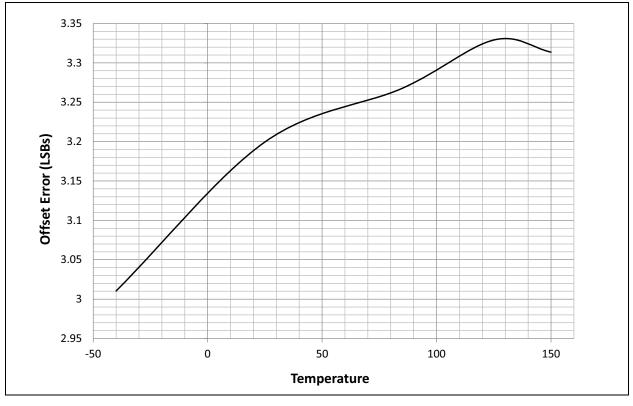

## 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

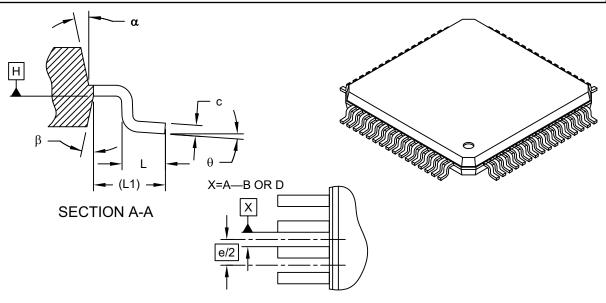

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### DETAIL 1

| Units                    |    | MILLIMETERS |      |      |  |

|--------------------------|----|-------------|------|------|--|

| Dimension Limits         |    | MIN         | NOM  | MAX  |  |

| Number of Leads          | Ν  | 64          |      |      |  |

| Lead Pitch               | е  | 0.50 BSC    |      |      |  |

| Overall Height           | A  | -           | -    | 1.20 |  |

| Molded Package Thickness | A2 | 0.95        | 1.00 | 1.05 |  |

| Standoff                 | A1 | 0.05        | -    | 0.15 |  |

| Foot Length              | L  | 0.45        | 0.60 | 0.75 |  |

| Footprint                | L1 | 1.00 REF    |      |      |  |

| Foot Angle               | ¢  | 0°          | 3.5° | 7°   |  |

| Overall Width            | Е  | 12.00 BSC   |      |      |  |

| Overall Length           | D  | 12.00 BSC   |      |      |  |

| Molded Package Width     | E1 | 10.00 BSC   |      |      |  |

| Molded Package Length    | D1 | 10.00 BSC   |      |      |  |

| Lead Thickness           | С  | 0.09        | -    | 0.20 |  |

| Lead Width               | b  | 0.17        | 0.22 | 0.27 |  |

| Mold Draft Angle Top     | α  | 11°         | 12°  | 13°  |  |

| Mold Draft Angle Bottom  | β  | 11°         | 12°  | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

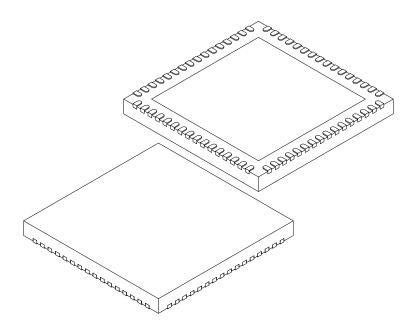

# 64-Lead Very Thin Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [VQFN] With 7.15 x 7.15 Exposed Pad [Also called QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          |          | MILLIMETERS |  |  |  |

|------------------------|-------|----------|----------|-------------|--|--|--|

| Dimension Limits       |       | MIN      | NOM      | MAX         |  |  |  |

| Number of Pins         | N     | 64       |          |             |  |  |  |

| Pitch                  | е     |          | 0.50 BSC |             |  |  |  |

| Overall Height         | Α     | 0.80     | 0.90     | 1.00        |  |  |  |

| Standoff               | A1    | 0.00     | 0.02     | 0.05        |  |  |  |

| Contact Thickness      | A3    | 0.20 REF |          |             |  |  |  |

| Overall Width          | E     | 9.00 BSC |          |             |  |  |  |

| Exposed Pad Width      | E2    | 7.05     | 7.15     | 7.25        |  |  |  |

| Overall Length         | D     | 9.00 BSC |          |             |  |  |  |

| Exposed Pad Length     | D2    | 7.05     | 7.15     | 7.25        |  |  |  |

| Contact Width          | b     | 0.18     | 0.25     | 0.30        |  |  |  |

| Contact Length         | L     | 0.30     | 0.40     | 0.50        |  |  |  |

| Contact-to-Exposed Pad | K     | 0.20     | -        | -           |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149D [MR] Sheet 2 of 2