Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm104t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

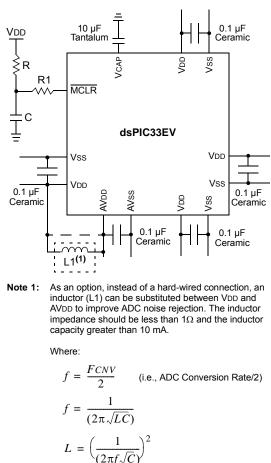

#### TANK CAPACITORS 2.2.1

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor** Connection (VCAP)

A low-ESR (<1 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a capacitor greater than 4.7 µF (10 µF is recommended), with at least a 16V rating connected to the ground. The type can be ceramic or tantalum. See Section 30.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length should not exceed one-quarter inch (6 mm).

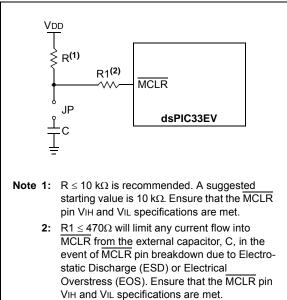

#### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- · Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-1, it is recommended that the capacitor, C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### EXAMPLE OF MCLR PIN CONNECTIONS

# dsPIC33EVXXXGM00X/10X FAMILY

| <b>▲</b> | Reserved                                                          | BSLIM<12:0>(1) + 0x000000                 |                          |

|----------|-------------------------------------------------------------------|-------------------------------------------|--------------------------|

|          | Reserved                                                          | BSLIM<12:0> <sup>(1)</sup> + 0x000002     |                          |

|          | Oscillator Fail Trap Vector                                       | BSLIM<12:0>(1) + 0x000004                 |                          |

|          | Address Error Trap Vector                                         | BSLIM<12:0> <sup>(1)</sup> + 0x000006     |                          |

|          | Generic Hard Trap Vector                                          | BSLIM<12:0> <sup>(1)</sup> + 0x000008     |                          |

|          | Stack Error Trap Vector                                           | BSLIM<12:0>(1) + 0x00000A                 |                          |

|          | Math Error Trap Vector                                            | BSLIM<12:0> <sup>(1)</sup> + 0x00000C     |                          |

|          | DMAC Error Trap Vector                                            | BSLIM<12:0> <sup>(1)</sup> + 0x00000E     |                          |

|          | Generic Soft Trap Vector                                          | BSLIM<12:0>(1) + 0x000010                 |                          |

|          | Reserved                                                          | BSLIM<12:0> <sup>(1)</sup> + 0x000012     |                          |

|          | Interrupt Vector 0                                                | BSLIM<12:0> <sup>(1)</sup> + 0x000014     |                          |

|          | Interrupt Vector 1                                                | BSLIM<12:0> <sup>(1)</sup> + 0x000016     |                          |

|          | :                                                                 | :                                         |                          |

|          | :                                                                 | :                                         |                          |

|          | :                                                                 | :                                         |                          |

| Σ        | Interrupt Vector 52                                               | BSLIM<12:0> <sup>(1)</sup> + 0x00007C     |                          |

|          | Interrupt Vector 53                                               | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|          | Interrupt Vector 54                                               | BSLIM<12:0> <sup>(1)</sup> + 0x000080     | See Table 7-1 for        |

|          | :                                                                 | :                                         | Interrupt Vector Details |

|          | :                                                                 | :                                         | /                        |

|          | :                                                                 | :                                         |                          |

|          | Interrupt Vector 116                                              | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC     |                          |

|          | Interrupt Vector 117                                              | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|          | Interrupt Vector 118                                              | BSLIM<12:0>(1) + 0x000100                 |                          |

|          | Interrupt Vector 119                                              | BSLIM<12:0> <sup>(1)</sup> + 0x000102     |                          |

|          | Interrupt Vector 120                                              | BSLIM<12:0> <sup>(1)</sup> + 0x000104     |                          |

|          | :                                                                 | :                                         |                          |

|          | :                                                                 | :                                         |                          |

|          | :                                                                 | :                                         |                          |

|          | Interrupt Vector 244                                              | BSLIM<12:0> <sup>(1)</sup> + 0x0001FC     |                          |

| V        | Interrupt Vector 245                                              | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE     |                          |

| Note     | 1: The address depends on the si<br>[(BSLIM<12:0> – 1) x 0x400] + | ze of the Boot Segment defined by Offset. | y BSLIM<12:0>:           |

| R/W-0                        | U-0                                          | U-0                                 | U-0            | U-0                                | U-0 | U-0                | U-0   |  |  |  |

|------------------------------|----------------------------------------------|-------------------------------------|----------------|------------------------------------|-----|--------------------|-------|--|--|--|

| DMT                          | —                                            | —                                   | —              | —                                  | —   | —                  | —     |  |  |  |

| bit 15                       |                                              |                                     |                |                                    |     |                    | bit 8 |  |  |  |

|                              |                                              |                                     |                |                                    |     |                    |       |  |  |  |

| U-0                          | U-0                                          | R/W-0                               | R/W-0          | U-0                                | U-0 | U-0                | U-0   |  |  |  |

| —                            | —                                            | DAE                                 | DOOVR          |                                    |     | —                  | _     |  |  |  |

| bit 7                        |                                              |                                     |                |                                    |     |                    | bit 0 |  |  |  |

|                              |                                              |                                     |                |                                    |     |                    |       |  |  |  |

| Legend:                      |                                              |                                     |                |                                    |     |                    |       |  |  |  |

| R = Readable bit W = Writabl |                                              | W = Writable                        | bit            | U = Unimplemented bit, read as '0' |     |                    |       |  |  |  |

| -n = Value at I              | POR                                          | '1' = Bit is set                    |                | '0' = Bit is cleared               |     | x = Bit is unknown |       |  |  |  |

|                              |                                              |                                     |                |                                    |     |                    |       |  |  |  |

| bit 15                       |                                              | an Timer (Soft                      |                | pit                                |     |                    |       |  |  |  |

|                              |                                              | 1 = Deadman Timer trap has occurred |                |                                    |     |                    |       |  |  |  |

|                              |                                              | Timer trap ha                       |                | 1                                  |     |                    |       |  |  |  |

| bit 14-6                     | Unimplemen                                   | ted: Read as '                      | 0'             |                                    |     |                    |       |  |  |  |

| bit 5                        | DAE: DMA Address Error Soft Trap Status bit  |                                     |                |                                    |     |                    |       |  |  |  |

|                              | 1 = DMA address error soft trap has occurred |                                     |                |                                    |     |                    |       |  |  |  |

|                              | 0 = DMA add                                  | ress error soft                     | trap has not o | ccurred                            |     |                    |       |  |  |  |

| bit 4                        | DOOVR: DO                                    | Stack Overflow                      | Soft Trap Sta  | tus bit                            |     |                    |       |  |  |  |

|                              |                                              | overflow soft tr                    | •              |                                    |     |                    |       |  |  |  |

|                              |                                              | overflow soft tr                    | -              | curred                             |     |                    |       |  |  |  |

| bit 3-0                      | Unimplemented: Read as '0'                   |                                     |                |                                    |     |                    |       |  |  |  |

# REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

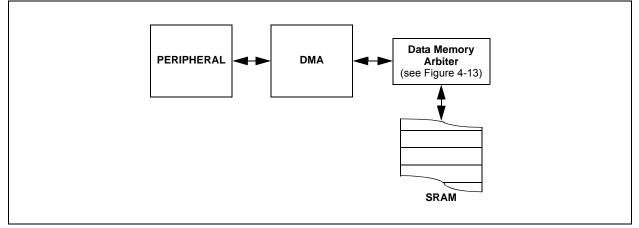

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| Periphera<br>Select II<br>Register | nput | Input/<br>Output | Pin Assignment                 |

|------------------------------------|------|------------------|--------------------------------|

| 00                                 | 000  | I                | Vss                            |

| 00                                 | 001  | I                | CMP1 <sup>(1)</sup>            |

| 0 0                                | 010  | Ι                | CMP2 <sup>(1)</sup>            |

| 000 00                             | 011  | Ι                | CMP3 <sup>(1)</sup>            |

| 000 01                             | 100  | Ι                | CMP4 <sup>(1)</sup>            |

| 000 01                             | 101  | —                | —                              |

| 000 11                             | 100  | Ι                | CMP5 <sup>(1)</sup>            |

| 000 11                             | 101  | _                | _                              |

| 000 11                             | 110  | _                |                                |

| 000 11                             | 111  | _                | _                              |

| 001 00                             | 000  | Ι                | RPI16                          |

| 001 00                             | 001  | I                | RPI17                          |

| 001 00                             | 010  | I                | RPI18                          |

| 001 00                             | 011  | Ι                | RPI19                          |

| 001 01                             | 100  | I/O              | RP20                           |

| 001 01                             | 101  | _                |                                |

| 001 01                             | 110  | _                | _                              |

| 001 01                             | 111  | _                | _                              |

| 001 10                             | 000  | I                | RPI24                          |

| 001 10                             | 001  | I                | RPI25                          |

| 001 10                             | 010  | _                | —                              |

| 001 10                             | 011  | I                | RPI27                          |

| 001 11                             | 100  | Ι                | RPI28                          |

| 001 11                             | 101  |                  | _                              |

| 001 11                             | 110  |                  | _                              |

| 001 11                             | 111  |                  | _                              |

| 010 00                             |      | Ι                | RPI32                          |

| 010 00                             |      | I                | RPI33                          |

| 010 00                             |      | I                | RPI34                          |

| 010 00                             |      | I/O              | RP35                           |

| 010 01                             |      | I/O              | RP36                           |

| 010 01                             |      | I/O              | RP37                           |

| 010 01                             |      | I/O              | RP38                           |

| 010 01                             |      | 1/O              | RP39                           |

| 010 10                             |      | I/O              |                                |

| 010 10                             |      | 1/U              | RPI44                          |

| 010 11                             |      | -                | RPI45                          |

| 010 11                             |      |                  | RPI46                          |

| 010 11                             |      | 1                | RPI47                          |

|                                    |      | I/O              |                                |

| 011 00                             |      | -                | RP48<br>the PPS Input register |

# TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate the PPS Input register values that are unimplemented.

Note 1: These are virtual pins. See Section 11.5.4.1 "Virtual Connections" for more information on selecting this pin assignment.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | —   | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|        |     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP37R5 | RP37R4 | RP37R3 | RP37R2 | RP37R1 | RP37R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP36R5 | RP36R4 | RP36R3 | RP36R2 | RP36R1 | RP36R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP37R<5:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP36R<5:0>:** Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 0

### REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                     | U-0                                                                  | R/W-0, HC                           | R/W-0                                                                    | R-0                 | R-1             |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|---------------------|-----------------|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UTXISEL0                                                                                  |                                                                      | UTXBRK                              | UTXEN <sup>(1)</sup>                                                     | UTXBF               | TRMT            |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |                                                                      |                                     |                                                                          |                     | bit 8           |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |                                                                      |                                     |                                                                          |                     |                 |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                     | R-1                                                                  | R-0                                 | R-0                                                                      | R/C-0               | R-0             |

| URXISEL1        | URXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADDEN                                                                                     | RIDLE                                                                | PERR                                | FERR                                                                     | OERR                | URXDA           |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |                                                                      |                                     |                                                                          |                     | bit 0           |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 0                                                                                       | 1.11                                                                 |                                     |                                                                          |                     |                 |

| Legend:         | L.:4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C = Clearable                                                                             |                                                                      |                                     | are Clearable bit                                                        |                     |                 |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                                                                              | DIT                                                                  | •                                   | mented bit, read                                                         |                     |                 |

| -n = Value at F | YOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                          |                                                                      | '0' = Bit is cle                    | ared                                                                     | x = Bit is unkr     | IOWN            |

| bit 15,13       | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>the trans</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  | ed; do not use<br>t when a chara<br>smit buffer beco<br>t when the las<br>ons are complet | cter is transf<br>omes empty<br>it character<br>ed<br>cter is transf | is shifted out<br>Ferred to the Tra | election bits<br>ansmit Shift Reg<br>of the Transmit<br>ansmit Shift Reg | t Shift Registe     | r; all transmit |

| bit 14          | $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle}}$ $0 = \text{UxTX Idle}$ $\frac{\text{If IREN = 1:}}{1 = \text{IrDA}^{\textcircled{$\mathbb{R}$}} \text{ end}}$ $0 = \text{IrDA ended}$                                                                                                                                                                                                                                                                                                                                                                                       | e state is '1'<br>coded UxTX Id<br>oded UxTX Idle                                         | le state is '1'<br>e state is '0'                                    |                                     |                                                                          |                     |                 |

| bit 12          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ted: Read as '                                                                            | )'                                                                   |                                     |                                                                          |                     |                 |

| bit 11          | 1 = Sends Sy<br>bit; cleare<br>0 = Sync Bre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed by hardware<br>ak transmission                                                         | ext transmis<br>upon compl<br>n is disabled                          |                                     | followed by twe                                                          | elve '0' bits, foll | lowed by Stop   |

| bit 10          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tx Transmit Er                                                                            |                                                                      |                                     |                                                                          |                     |                 |

|                 | 0 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                           |                                                                      | ntrolled by UAR<br>ansmission is    | Tx<br>aborted and the                                                    | e buffer is rese    | t; UxTX pin is  |

| bit 9           | UTXBF: UAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Tx Transmit Bu                                                                            | Iffer Full Stat                                                      | us bit (read-onl                    | y)                                                                       |                     |                 |

|                 | 1 = Transmit<br>0 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                           | ll, at least on                                                      | e more charact                      | er can be writte                                                         | n                   |                 |

| bit 8           | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Shift Register is                                                                         | s empty and t                                                        |                                     | s empty (the last                                                        |                     | as completed)   |

| bit 7-6         | <ul> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> <li>URXISEL&lt;1:0&gt;: UARTx Receive Interrupt Mode Selection bits</li> <li>11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters</li> </ul> |                                                                                           |                                                                      |                                     |                                                                          |                     |                 |

### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

| R/W-0           | R/W-0                                                                  | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0              | R/W-0   |  |  |

|-----------------|------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------------------|------------------|--------------------|---------|--|--|

| F15MSK1         | F15MSK0                                                                | F14MSK1                                            | F14MSK0                                               | F13MSK'                          | F13MSK0          | F12MSK1            | F12MSK0 |  |  |

| bit 15          |                                                                        |                                                    |                                                       |                                  |                  |                    | bit 8   |  |  |

| R/W-0           | R/W-0                                                                  | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0              | R/W-0   |  |  |

| F11MSK1         | F11MSK0                                                                | F10MSK1                                            | F10MSK0                                               | F9MSK1                           | F9MSK0           | F8MSK1             | F8MSK0  |  |  |

| bit 7           |                                                                        |                                                    |                                                       |                                  |                  | 1                  | bit (   |  |  |

| Legend:         |                                                                        |                                                    |                                                       |                                  |                  |                    |         |  |  |

| R = Readable    | bit                                                                    | W = Writable bit                                   |                                                       | U = Unimplemented bit, read as   |                  | <b>as</b> '0'      |         |  |  |

| -n = Value at I | POR                                                                    | '1' = Bit is set                                   |                                                       | '0' = Bit is cleared             |                  | x = Bit is unknown |         |  |  |

| bit 15-14       | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta           | nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg | gisters contain<br>gisters contain<br>gisters contain | the mask<br>the mask<br>the mask |                  |                    |         |  |  |

| bit 13-12       |                                                                        |                                                    |                                                       | ,                                | es as bits 15-14 | ,                  |         |  |  |

| bit 11-10       |                                                                        |                                                    |                                                       | -                                | es as bits 15-14 |                    |         |  |  |

| bit 9-8         |                                                                        |                                                    |                                                       |                                  | es as bits 15-14 |                    |         |  |  |

| bit 7-6         |                                                                        |                                                    |                                                       | -                                | es as bits 15-14 | -                  |         |  |  |

| bit 5-4         | F10MSK<1:0>: Mask Source for Filter 10 bit (same values as bits 15-14) |                                                    |                                                       |                                  |                  |                    |         |  |  |

| bit 3-2         | F9MSK<1:0>: Mask Source for Filter 9 bit (same values as bits 15-14)   |                                                    |                                                       |                                  |                  |                    |         |  |  |

|                 |                                                                        |                                                    |                                                       |                                  |                  |                    |         |  |  |

# REGISTER 22-19: CxFMSKSEL2: CANx FILTERS 15-8 MASK SELECTION REGISTER 2

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bits 15-14)

# dsPIC33EVXXXGM00X/10X FAMILY

# dsPIC33EVXXXGM00X/10X FAMILY

| R/W-                                               | 0 U-0                                | R/W-0                                  | R/W-0                    | R/W-0                   | R/W-0                       | R/W-0                   | R/W-0                   |  |

|----------------------------------------------------|--------------------------------------|----------------------------------------|--------------------------|-------------------------|-----------------------------|-------------------------|-------------------------|--|

| CHON                                               | IB —                                 | CH0SB5 <sup>(1,3)</sup>                | CH0SB4 <sup>(1,3)</sup>  | CH0SB3 <sup>(1,3)</sup> | CH0SB2 <sup>(1,3)</sup>     | CH0SB1 <sup>(1,3)</sup> | CH0SB0 <sup>(1,3)</sup> |  |

| bit 15                                             |                                      |                                        |                          |                         |                             |                         | bit 8                   |  |

|                                                    |                                      |                                        |                          |                         |                             |                         |                         |  |

| R/W-                                               |                                      | R/W-0                                  | R/W-0                    | R/W-0                   | R/W-0                       | R/W-0                   | R/W-0                   |  |

| CHON                                               | IA —                                 | CH0SA5 <sup>(1,3)</sup>                | CH0SA4 <sup>(1,3)</sup>  | CH0SA3 <sup>(1,3)</sup> | CH0SA2 <sup>(1,3)</sup>     | CH0SA1 <sup>(1,3)</sup> | CH0SA0 <sup>(1,3)</sup> |  |

| bit 7                                              |                                      |                                        |                          |                         |                             |                         | bit 0                   |  |

| Logondi                                            |                                      |                                        |                          |                         |                             |                         |                         |  |

| Legend:<br>R = Read                                | table bit                            | W = Writable b                         | nit                      |                         | ented bit, read             | <b>ae</b> '0'           |                         |  |

|                                                    | e at POR                             | (1) = Bit is set                       | JIL                      | '0' = Bit is clea       | -                           | x = Bit is unkr         | NWD                     |  |

|                                                    |                                      |                                        |                          |                         | licu                        |                         |                         |  |

| bit 15                                             |                                      | nannel 0 Negativ                       |                          | for Sample MU           | IX B bit                    |                         |                         |  |

|                                                    | 1 = Channe                           | el 0 negative inp                      | ut is AN1 <sup>(1)</sup> |                         |                             |                         |                         |  |

|                                                    |                                      | el 0 negative inp                      |                          |                         |                             |                         |                         |  |

| bit 14                                             | -                                    | ented: Read as                         |                          |                         |                             | 2)                      |                         |  |

| bit 13-8                                           |                                      | 0>: Channel 0 P                        |                          |                         | e MUX B bits <sup>(1,</sup> | 3)                      |                         |  |

|                                                    |                                      | Channel 0 positiv<br>Channel 0 positiv |                          |                         |                             |                         |                         |  |

|                                                    |                                      | Channel 0 positiv                      |                          |                         | d aap voltage)              |                         |                         |  |

|                                                    | •                                    |                                        |                          | ( III IIII              | 5 - F                       |                         |                         |  |

|                                                    | •                                    |                                        |                          |                         |                             |                         |                         |  |

|                                                    | • 011111 = (                         | Channel 0 positiv                      | ve input is AN3          | 1                       |                             |                         |                         |  |

|                                                    |                                      | Channel 0 positiv                      |                          |                         |                             |                         |                         |  |

|                                                    | •                                    |                                        |                          |                         |                             |                         |                         |  |

|                                                    | •                                    |                                        |                          |                         |                             |                         |                         |  |

|                                                    | • 000001 = 0                         | Channel 0 positiv                      | ve input is AN1          |                         |                             |                         |                         |  |

|                                                    |                                      | Channel 0 positiv                      |                          |                         |                             |                         |                         |  |

| bit 7                                              | CHONA: Ch                            | nannel 0 Negativ                       | e Input Select           | for Sample MU           | IX A bit                    |                         |                         |  |

| 1 = Channel 0 negative input is AN1 <sup>(1)</sup> |                                      |                                        |                          |                         |                             |                         |                         |  |

|                                                    | 0 = Channe                           | el 0 negative inp                      | ut is VREFL              |                         |                             |                         |                         |  |

| bit 6                                              | Unimpleme                            | ented: Read as                         | '0'                      |                         |                             |                         |                         |  |

| Note 1:                                            | AN0 to AN7 are r                     |                                        | •                        | • •                     | •                           | •                       |                         |  |

|                                                    | determine how er                     | • •                                    | · ·                      | -                       |                             |                         |                         |  |

| 2:                                                 | If the op amp is a<br>input is used. | selected (OPAE                         | N bit (CMxCON            | N<10>) = 1), the        | e OAx input is u            | ised; otherwise         | , the ANx               |  |

|                                                    |                                      |                                        |                          |                         |                             |                         |                         |  |

# REGISTER 24-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER

3: See the "Pin Diagrams" section for the available analog channels for each device.

# **REGISTER 24-7:** ADxCSSH: ADCx INPUT SCAN SELECT REGISTER HIGH<sup>(2)</sup> (CONTINUED)

- bit 1 CSS17: ADCx Input Scan Selection bit 1 = Selects ANx for input scan

- 0 = Skips ANx for input scan

- bit 0 CSS16: ADCx Input Scan Selection bit

- 1 = Selects ANx for input scan

- 0 = Skips ANx for input scan

- **Note 1:** If the op amp is selected (OPAEN bit (CMxCON<10>) = 1), the OAx input is used; otherwise, the ANx input is used.

- 2: All bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

# 25.1 Op Amp/Comparator Control Registers

### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER

| R/W-0        | U-0 | U-0 | R-0                  | R-0                  | R-0                  | R-0                  | R-0                  |  |

|--------------|-----|-----|----------------------|----------------------|----------------------|----------------------|----------------------|--|

| PSIDL        | —   | _   | C5EVT <sup>(1)</sup> | C4EVT <sup>(1)</sup> | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |

| bit 15 bit 8 |     |     |                      |                      |                      |                      |                      |  |

|              |     |     |                      |                      |                      |                      |                      |  |

| U-0         | U-0 | U-0 | R-0                  | R-0                  | R-0                  | R-0                  | R-0                  |

|-------------|-----|-----|----------------------|----------------------|----------------------|----------------------|----------------------|

| —           | —   | —   | C5OUT <sup>(2)</sup> | C4OUT <sup>(2)</sup> | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C1OUT <sup>(2)</sup> |

| bit 7 bit 0 |     |     |                      |                      |                      |                      |                      |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15    | <b>PSIDL:</b> Op Amp/Comparator Stop in Idle Mode bit<br>1 = Discontinues operation of all op amps/comparators when device enters Idle mode<br>0 = Continues operation of all op amps/comparators in Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 12-8  | C5EVT:C1EVT: Op Amp/Comparator 1-5 Event Status bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | <ul><li>1 = Op amp/comparator event occurred</li><li>0 = Op amp/comparator event did not occur</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |