Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm002-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                         | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                  |  |  |  |  |  |  |  |

|----------------------------------|-------------|----------------|-----|------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| AVDD                             | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times. |  |  |  |  |  |  |  |

| AVss                             | Р           | Р              | No  | o Ground reference for analog modules.                                       |  |  |  |  |  |  |  |

| Vdd                              | Р           | —              | No  | Positive supply for peripheral logic and I/O pins.                           |  |  |  |  |  |  |  |

| VCAP                             | Р           | _              | No  | CPU logic filter capacitor connection.                                       |  |  |  |  |  |  |  |

| Vss                              | Р           | _              | No  | No Ground reference for logic and I/O pins.                                  |  |  |  |  |  |  |  |

| Legend: CMOS = CM<br>ST = Schmit |             | •              |     |                                                                              |  |  |  |  |  |  |  |

PPS = Peripheral Pin Select

TTL = TTL input buffer

# 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Count Register                                    |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

| IABLE       | 4-3:  | INP    | UICA   | APIUR  | EIH        | ROUGI      |             | CAP      | IURE 4    | REGIS      |               | ,     |          |          |          |          |          |               |

|-------------|-------|--------|--------|--------|------------|------------|-------------|----------|-----------|------------|---------------|-------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11     | Bit 10      | Bit 9    | Bit 8     | Bit 7      | Bit 6         | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1     | 0140  | _      | _      | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | _        | —         | —          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2     | 0142  | _      | _      | _      | _          | _          | _           | -        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF      | 0144  |        |        |        |            |            |             |          | Inp       | ut Capture | 1 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC1TMR      | 0146  |        |        |        |            |            |             |          | Inp       | ut Capture | 1 Timer Regis | ster  |          |          |          |          |          | 0000          |

| IC2CON1     | 0148  | _      | _      | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2     | 014A  | _      | _      | _      | _          | _          | _           | -        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF      | 014C  |        |        |        |            |            |             |          | Inp       | ut Capture | 2 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC2TMR      | 014E  |        |        |        |            |            |             |          | Inp       | ut Capture | 2 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC3CON1     | 0150  | _      | _      | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2     | 0152  | _      | _      | _      | _          | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF      | 0154  |        |        |        |            |            |             |          | Inp       | ut Capture | 3 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC3TMR      | 0156  |        |        |        |            |            |             |          | Inp       | ut Capture | 3 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC4CON1     | 0158  |        |        | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | _        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2     | 015A  |        |        | —      | —          | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF      | 015C  |        |        |        |            |            |             |          | Inp       | ut Capture | 4 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC4TMR      | 015E  |        |        |        |            |            |             |          | Inp       | ut Capture | 4 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| Lamandi     |       |        |        | aati - | unimanlama | optod road | Loo '0' Boo | at value | ara ahawa | in hovedor | simal         |       |          |          |          |          |          |               |

#### TABLE 4-3: INDUT CARTINE 1 THROUGH INDUT CARTINE A REGISTER MAD

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: **I2C1 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                      | Bit 8     | Bit 7       | Bit 6    | Bit 5       | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|----------------------------|-----------|-------------|----------|-------------|--------------|-------|-------|-------|-------|---------------|

| I2C1CON1    | 0200  | I2CEN   | —      | I2CSIDL | SCLREL | STRICT | A10M   | DISSLW                     | SMEN      | GCEN        | STREN    | ACKDT       | ACKEN        | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1CON2    | 0202  | _       | _      | _       | _      | _      | _      | _                          | _         | _           | PCIE     | SCIE        | BOEN         | SDAHT | SBCDE | AHEN  | DHEN  | 1000          |

| I2C1STAT    | 0204  | ACKSTAT | TRSTAT | ACKTIM  |        | _      | BCL    | GCSTAT                     | ADD10     | IWCOL       | I2COV    | D_A         | Р            | S     | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206  |         |        |         |        | _      |        |                            |           |             |          | I2C1 Addr   | ess Register |       |       |       |       | 0000          |

| I2C1MSK     | 0208  |         |        |         |        | _      |        |                            |           |             | 12       | 2C1 Address | Mask Regis   | ster  |       |       |       | 0000          |

| I2C1BRG     | 020A  |         |        |         |        |        |        | E                          | Baud Rate | Generator F | Register |             |              |       |       |       |       | 0000          |

| I2C1TRN     | 020C  |         |        |         |        | _      |        | I2C1 Transmit Register 002 |           |             |          |             |              |       |       | OOFF  |       |               |

| I2C1RCV     | 020E  |         |        |         |        | _      |        | I2C1 Receive Register 0000 |           |             |          |             |              |       |       |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-5: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11                                            | Bit 10 | Bit 9    | Bit 8                                    | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|---------------------------------------------------|--------|----------|------------------------------------------|----------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | _      | USIDL    | IREN   | RTSMD                                             | —      | UEN1     | UEN0                                     | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK                                            | UTXEN  | UTXBF    | TRMT                                     | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _      | _        | _      | _                                                 | _      | _        |                                          |          |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _                                                 | _      | _        | UART1 Receive Register                   |          |          |       |             |         |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        | UART1 Baud Rate Generator Prescaler Register 0000 |        |          |                                          |          |          |       |             |         |        |        | 0000  |               |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD                                             | _      | UEN1     | UEN0                                     | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK                                            | UTXEN  | UTXBF    | TRMT                                     | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _                                                 | _      | _        |                                          |          |          | UART2 | Transmit Re | egister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | _        | _      | —                                                 | _      | —        |                                          |          |          | UART2 | Receive Re  | egister |        |        |       | 0000          |

| U2BRG       | 0238  |          |        |          |        |                                                   | U      | ART2 Bau | 2 Baud Rate Generator Prescaler Register |          |          |       |             |         |        |        |       | 0000          |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-6: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8        | Bit 7      | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|----------|--------------|------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | -      | SPISIDL |        | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT      | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      |        | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN       | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | —      | _       | _        | _            | _          | —           | —      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tra | ansmit and R | eceive Buf | fer Registe | r      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT      | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      |        | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN       | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | —      | _       | —        | _            | _          | _           | —      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        |        |         |        |        |         | SPI2 Tra | ansmit and R | eceive Buf | fer Registe | r      |        |        |        |        |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|             | ••    |        |        |        |          |            |          |          |          |             |       |        |          |          |          |          |          |               |

|-------------|-------|--------|--------|--------|----------|------------|----------|----------|----------|-------------|-------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11     | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6 | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADC1BUF0    | 0300  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUF1    | 0302  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUF2    | 0304  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUF3    | 0306  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUF4    | 0308  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUF5    | 030A  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 5     |        |          |          |          |          |          | xxxx          |

| ADC1BUF6    | 030C  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 6     |        |          |          |          |          |          | xxxx          |

| ADC1BUF7    | 030E  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 7     |        |          |          |          |          |          | xxxx          |

| ADC1BUF8    | 0310  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 8     |        |          |          |          |          |          | xxxx          |

| ADC1BUF9    | 0312  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 9     |        |          |          |          |          |          | xxxx          |

| ADC1BUFA    | 0314  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUFB    | 0316  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUFC    | 0318  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUFD    | 031A  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUFE    | 031C  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUFF    | 031E  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 5     |        |          |          |          |          |          | xxxx          |

| AD1CON1     | 0320  | ADON   | I      | ADSIDL | ADDMABM  | —          | AD12B    | FORM1    | FORM0    | SSRC2       | SSRC1 | SSRC0  | SSRCG    | SIMSAM   | ASAM     | SAMP     | DONE     | 0000          |

| AD1CON2     | 0322  | VCFG2  | VCFG1  | VCFG0  | —        | —          | CSCNA    | CHPS1    | CHPS0    | BUFS        | SMPI4 | SMPI3  | SMPI2    | SMPI1    | SMPI0    | BUFM     | ALTS     | 0000          |

| AD1CON3     | 0324  | ADRC   | I      |        | SAMC4    | SAMC3      | SAMC2    | SAMC1    | SAMC0    | ADCS7       | ADCS6 | ADCS5  | ADCS4    | ADCS3    | ADCS2    | ADCS1    | ADCS0    | 0000          |

| AD1CHS123   | 0326  | _      | I      |        | CH123SB2 | CH123SB1   | CH123NB1 | CH123NB0 | CH123SB0 | —           |       |        | CH123SA2 | CH123SA1 | CH123NA1 | CH123NA0 | CH123SA0 | 0000          |

| AD1CHS0     | 0328  | CH0NB  |        | CH0SB5 | CH0SB4   | CH0SB3     | CH0SB2   | CH0SB1   | CH0SB0   | CH0NA       | -     | CH0SA5 | CH0SA4   | CH0SA3   | CH0SA2   | CH0SA1   | CH0SA0   | 0000          |

| AD1CSSH     | 032E  |        |        |        |          | CSS<31:24> |          |          |          | _           | _     | _      | —        |          | CSS<     | <19:16>  |          | 0000          |

| AD1CSSL     | 0330  |        |        |        |          |            |          |          | CSS      | <15:0>      |       |        |          |          |          |          |          | 0000          |

| AD1CON4     | 0332  | -      | _      | _      | —        | —          | _        | _        | ADDMAEN  | _           | _     | _      | _        | -        | DMABL2   | DMABL1   | DMABL0   | 0000          |

|             |       |        |        |        |          |            | <b>D</b> |          |          |             |       |        |          |          |          |          |          |               |

# TABLE 4-7: ADC1 REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-8: CTMU REGISTER MAP

|   | SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Reset<br>s |

|---|-------------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|-------------------|

| Ī | CTMUCON1    | 033A  | CTMUEN  | -       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | —       |          | _        | _        | _        | _     |       | 0000              |

| Ī | CTMUCON2    | 033C  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _     | _     | 0000              |

|   | CTMUICON    | 033E  | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | -       | _       |          | _        | _        | _        | _     | _     | 0000              |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in the data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configure the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses an EDS or a PSV page.

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing. However, this does not include Register Offset Addressing.

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using the Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-43 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when an overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

# TABLE 4-43: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS AND PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| 0/11        |                     |                | Before       |                        |                | After        |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page Description       |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last Page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>Page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page |

| O,<br>Read  | <b>or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>Page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last Page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  | r 1                 | DSRPAG = 0x001 | 1            | PSV Page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>Page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ WII ]             | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>Page  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

**Note 1:** The Register Indirect Addressing now addresses a location in the Base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

**3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

4: Pseudolinear Addressing is not supported for large offsets.

| R/W-0          | R/W-0                                     | U-0                                  | U-0             | R/W-0                        | U-0              | R/W-0            | R/W-0          |

|----------------|-------------------------------------------|--------------------------------------|-----------------|------------------------------|------------------|------------------|----------------|

| TRAPF          | R IOPUWR                                  |                                      | —               | VREGSF                       |                  | CM               | VREGS          |

| bit 15         |                                           |                                      |                 |                              |                  |                  | bit 8          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| R/W-0          | R/W-0                                     | R/W-0                                | R/W-0           | R/W-0                        | R/W-0            | R/W-1            | R/W-1          |

| EXTR           | SWR                                       | SWDTEN <sup>(2)</sup>                | WDTO            | SLEEP                        | IDLE             | BOR              | POR            |

| bit 7          |                                           |                                      |                 |                              |                  |                  | bit (          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Legend:        |                                           |                                      |                 |                              |                  |                  |                |

| R = Reada      |                                           | W = Writable                         | oit             | •                            | nented bit, read | d as '0'         |                |

| -n = Value     | at POR                                    | '1' = Bit is set                     |                 | '0' = Bit is cle             | ared             | x = Bit is unk   | nown           |

| 6:4 <i>4 C</i> |                                           | Deast Flag bit                       |                 |                              |                  |                  |                |

| bit 15         |                                           | o Reset Flag bit<br>onflict Reset ha | e occurrod      |                              |                  |                  |                |

|                |                                           | onflict Reset ha                     |                 | ed                           |                  |                  |                |

| bit 14         | •                                         | egal Opcode or                       |                 |                              | ess Reset Flag   | a bit            |                |

|                |                                           | al Opcode detec                      |                 | •                            | -                |                  | ter used as ar |

|                |                                           | Pointer caused                       |                 | · · · · · · · · · · · ·      |                  |                  |                |

|                |                                           | I Opcode Rese                        |                 | zed W Register               | Reset has not    | occurred         |                |

| bit 13-12      | -                                         | nted: Read as '                      |                 |                              |                  |                  |                |

| bit 11         |                                           | ash Voltage Reg                      |                 |                              | o bit            |                  |                |

|                |                                           | Itage regulator i                    |                 | •                            | ing Sleep mode   | 2                |                |

| bit 10         |                                           | nted: Read as '                      | -               |                              | ing cleep mout   |                  |                |

| bit 9          | -                                         | ration Mismatch                      |                 |                              |                  |                  |                |

|                | •                                         | uration Mismatc                      | •               | occurred.                    |                  |                  |                |

|                |                                           | uration Mismato                      |                 |                              |                  |                  |                |

| bit 8          | VREGS: Volt                               | age Regulator S                      | Standby Durii   | ng Sleep bit                 |                  |                  |                |

|                |                                           | regulator is activ                   |                 |                              |                  |                  |                |

|                | •                                         | regulator goes i                     |                 | mode during Sle              | еер              |                  |                |

| bit 7          |                                           | nal Reset (MCL                       | ,               |                              |                  |                  |                |

|                |                                           | Clear (pin) Res<br>Clear (pin) Res   |                 |                              |                  |                  |                |

| bit 6          |                                           | are RESET (Instr                     |                 |                              |                  |                  |                |

|                |                                           | instruction has                      |                 |                              |                  |                  |                |

|                | 0 = A reset                               | instruction has                      | not been exe    | ecuted                       |                  |                  |                |

| bit 5          | SWDTEN: So                                | oftware Enable/                      | Disable of W    | DT bit <b><sup>(2)</sup></b> |                  |                  |                |

|                | 1 = WDT is e                              |                                      |                 |                              |                  |                  |                |

|                | 0 = WDT is d                              |                                      |                 |                              |                  |                  |                |

| bit 4          |                                           | hdog Timer Tim                       | -               | it                           |                  |                  |                |

|                |                                           | e-out has occur<br>e-out has not oc  |                 |                              |                  |                  |                |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Note 1:        | All of the Reset sta<br>cause a device Re |                                      | set or cleare   | a in software. S             | etting one of th | ese bits in soft | ware does not  |

| 2:             | If the FWDTEN<1                           |                                      | n hits are '1 1 | ' (unprogramm                | ed) the WDT is   | always enable    | od rogardlaar  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# 7.3 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EVXXXGM00X/10X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# 7.4 Interrupt Control and Status Registers

dsPIC33EVXXXGM00X/10X family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- IFSx

- IECx

- IPCx

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from the INTCON1, INTCON2, INTCON3 and INTCON4 registers.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMT (Deadman Timer), DMA and  ${\tt DO}$  stack overflow status trap sources.

The INTCON4 register contains the ECC Double-Bit Error (ECCDBE) and Software-Generated Hard Trap (SGHT) status bit.

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared through software.

# 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into Vector Number (VECNUM<7:0>) and Interrupt Priority Level bit (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

# 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 to Register 7-7.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| bit 15 |     |     |     |     |     |     | bit 8 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|

| OCFAR<7:0> |       |       |       |       |       |       |       |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 OCFAR<7:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

> 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

NOTES:

# dsPIC33EVXXXGM00X/10X FAMILY

# REGISTER 17-12: TRGCONX: PWMx TRIGGER CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | —   | —   | —   | —     |

| bit 15  |         |         |         |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|-----|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| —     | —   | TRGSTRT5 <sup>(1)</sup> | TRGSTRT4 <sup>(1)</sup> | TRGSTRT3 <sup>(1)</sup> | TRGSTRT2 <sup>(1)</sup> | TRGSTRT1 <sup>(1)</sup> | TRGSTRT0 <sup>(1)</sup> |

| bit 7 |     |                         |                         |                         |                         |                         | bit 0                   |

| Legend:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-12 TRGDIV<3:0>: Trigger Output Divider bits

- 1111 = Triggers output for every 16th trigger event

- 1110 = Triggers output for every 15th trigger event

- 1101 = Triggers output for every 14th trigger event

- 1100 = Triggers output for every 13th trigger event

- 1011 = Triggers output for every 12th trigger event

- 1010 = Triggers output for every 11th trigger event

- 1001 = Triggers output for every 10th trigger event

- 1000 = Triggers output for every 9th trigger event

- 0111 = Triggers output for every 8th trigger event

- 0110 = Triggers output for every 7th trigger event

- 0101 = Triggers output for every 6th trigger event

- 0100 = Triggers output for every 5th trigger event 0011 = Triggers output for every 4th trigger event

- 0010 = Triggers output for every 3rd trigger event

- 0001 = Triggers output for every 2nd trigger event

- 0000 = Triggers output for every trigger event

- bit 11-6 **Unimplemented:** Read as '0'

### bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits<sup>(1)</sup>

111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled

- •

- •

000010 = Waits 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Waits 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Waits 0 PWM cycles before generating the first trigger event after the module is enabled

### **Note 1:** The secondary PWM generator cannot generate PWMx trigger interrupts.

## REGISTER 22-16: CxRXFnSID: CANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

|               |              | -                                                                                                                                                      | •            |                   |                  |                       |       |  |  |  |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|------------------|-----------------------|-------|--|--|--|

| R/W-x         | R/W-x        | R/W-x                                                                                                                                                  | R/W-x        | R/W-x             | R/W-x            | R/W-x                 | R/W-x |  |  |  |

| SID10         | SID9         | SID8                                                                                                                                                   | SID7         | SID6              | SID5             | SID4                  | SID3  |  |  |  |

| bit 15        |              |                                                                                                                                                        |              |                   |                  |                       | bit 8 |  |  |  |

|               |              |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

| R/W-x         | R/W-x        | R/W-x                                                                                                                                                  | U-0          | R/W-x             | U-0              | R/W-x                 | R/W-x |  |  |  |

| SID2          | SID1         | SID0                                                                                                                                                   |              | EXIDE             |                  | EID17                 | EID16 |  |  |  |

| bit 7         |              |                                                                                                                                                        |              |                   |                  |                       | bit C |  |  |  |

|               |              |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

| Legend:       |              |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

| R = Readabl   | e bit        | W = Writable                                                                                                                                           | bit          | U = Unimpler      | nented bit, read | <b>as</b> '0'         |       |  |  |  |

| -n = Value at | POR          | '1' = Bit is set                                                                                                                                       |              | '0' = Bit is cle  | ared             | ed x = Bit is unknown |       |  |  |  |

|               |              |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

| bit 15-5      | SID<10:0>: S | Standard Identif                                                                                                                                       | ier bits     |                   |                  |                       |       |  |  |  |

|               | 0            |                                                                                                                                                        | •            | 1' to match filte |                  |                       |       |  |  |  |

|               | 0            | -                                                                                                                                                      |              | 0' to match filte | er               |                       |       |  |  |  |

| bit 4         | Unimplemen   | ted: Read as '                                                                                                                                         | 0'           |                   |                  |                       |       |  |  |  |

| bit 3         | EXIDE: Exter | nded Identifier I                                                                                                                                      | Enable bit   |                   |                  |                       |       |  |  |  |

|               | If MIDE = 1: |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

|               |              | <ul> <li>1 = Matches only messages with Extended Identifier addresses</li> <li>0 = Matches only messages with Standard Identifier addresses</li> </ul> |              |                   |                  |                       |       |  |  |  |

|               | 0 = Matches  | only messages                                                                                                                                          | with Standar |                   | resses           |                       |       |  |  |  |

|               | Ignores EXID | )E bit.                                                                                                                                                |              |                   |                  |                       |       |  |  |  |

| bit 2         | •            | ted: Read as '                                                                                                                                         | 0'           |                   |                  |                       |       |  |  |  |

| bit 1-0       | •            | Extended Iden                                                                                                                                          |              |                   |                  |                       |       |  |  |  |

|               |              |                                                                                                                                                        |              | 1' to match filte | er               |                       |       |  |  |  |

|               | 0            |                                                                                                                                                        | •            | 0' to match filte |                  |                       |       |  |  |  |

|               | 0            |                                                                                                                                                        |              |                   |                  |                       |       |  |  |  |

# REGISTER 22-17: CxRXFnEID: CANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x           | R/W-x      | R/W-x              | R/W-x   | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|------------|--------------------|---------|-------------------|-----------------|-----------------|-------|

|                 |            |                    | EID     | <15:8>            |                 |                 |       |

| bit 15          |            |                    |         |                   |                 |                 | bit 8 |

| R/W-x           | R/W-x      | R/W-x              | R/W-x   | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |            |                    | EID     | )<7:0>            |                 |                 |       |

| bit 7           |            |                    |         |                   |                 |                 | bit 0 |

| Legend:         |            |                    |         |                   |                 |                 |       |

| R = Readable    | bit        | W = Writable b     | it      | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR        | '1' = Bit is set   |         | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|                 |            |                    |         |                   |                 |                 |       |

| bit 15-0        | EID<15:0>: | Extended Identifie | er bits |                   |                 |                 |       |

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

## **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

- bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(3)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

$\frac{\text{If CPOL} = 1 \text{ (inverted polarity):}}{\text{Low-to-high transition of the comparator output.}}$  $\frac{\text{If CPOL} = 0 \text{ (non-inverted polarity):}}{\text{High-to-low transition of the comparator output.}}$

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

- If CPOL = 0 (non-inverted polarity):

- Low-to-high transition of the comparator output.

- 00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to the internal CVREFIN voltage

- 0 = VIN+ input connects to the CxIN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator x Channel Select bits<sup>(1)</sup>

- 11 = Inverting input of op amp/comparator connects to the CxIN4- pin

- 10 = Inverting input of op amp/comparator connects to the CxIN3- pin

- 01 = Inverting input of op amp/comparator connects to the CxIN2- pin

- 00 = Inverting input of op amp/comparator connects to the CxIN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- 3: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

# TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                            | CKE | СКР | SMP |  |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                     | 0,1 | 0,1 | 0,1 |  |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                     | 1   | 0,1 | 1   |  |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                     | 0   | 0,1 | 1   |  |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                           | 1   | 0   | 0   |  |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                           | 1   | 1   | 0   |  |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                           | 0   | 1   | 0   |  |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                           | 0   | 0   | 0   |  |

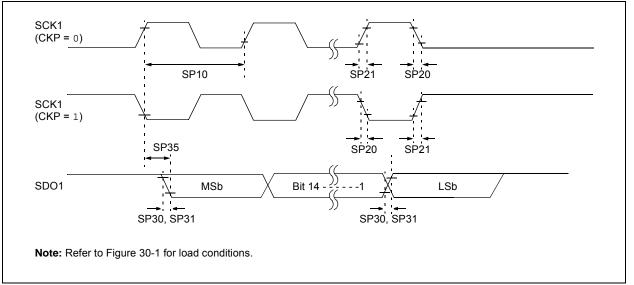

# FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CH/        | ARACTER | RISTICS                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |                                   |          |                                                                                                              |  |  |

|---------------|---------|------------------------------------------------------|------------------------------------------------------|----------|-----------------------------------|----------|--------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.  | Symbol  | Characteristic                                       | Min.                                                 | Тур.     | Max.                              | Units    | Conditions                                                                                                   |  |  |

| Device Supply |         |                                                      |                                                      |          |                                   |          |                                                                                                              |  |  |

| AD01          | AVDD    | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or VBOR                  | _        | Lesser of:<br>VDD + 0.3<br>or 5.5 | V        |                                                                                                              |  |  |

| AD02          | AVss    | Module Vss Supply                                    | Vss – 0.3                                            | _        | Vss + 0.3                         | V        |                                                                                                              |  |  |

|               |         |                                                      | Refere                                               | nce Inpu | ıts                               |          |                                                                                                              |  |  |

| AD05          | Vrefh   | Reference Voltage High                               | 4.5                                                  | —        | 5.5                               | V        | VREFH = AVDD,<br>VREFL = AVSS = 0                                                                            |  |  |

| AD06          | VREFL   | Reference Voltage Low                                | AVss                                                 |          | AVDD - VBORMIN                    | V        | See Note 1                                                                                                   |  |  |

| AD06a         |         |                                                      | 0                                                    | _        | 0                                 | V        | VREFH = AVDD,<br>VREFL = AVSS = 0                                                                            |  |  |

| AD07          | Vref    | Absolute Reference<br>Voltage                        | 4.5                                                  | _        | 5.5                               | V        | Vref = Vrefh – Vrefl                                                                                         |  |  |

| AD08          | IREF    | Current Drain                                        | —                                                    |          | 10<br>600                         | μA<br>μA | ADC off<br>ADC on                                                                                            |  |  |

| AD09          | lad     | Operating Current                                    | _                                                    | 5<br>2   |                                   | mA<br>mA | ADC operating in 10-bit<br>mode (see <b>Note 1</b> )<br>ADC operating in 12-bit<br>mode (see <b>Note 1</b> ) |  |  |

|               |         | •                                                    | Anal                                                 | og Input |                                   |          |                                                                                                              |  |  |

| AD12          | VINH    | Input Voltage Range Vinн                             | VINL                                                 |          | VREFH                             | V        | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input              |  |  |

| AD13          | VINL    | Input Voltage Range Vın∟                             | VREFL                                                | _        | AVss + 1V                         | V        | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input              |  |  |

| AD17          | Rin     | Recommended<br>Impedance of Analog<br>Voltage Source |                                                      |          | 200                               | Ω        | Impedance to achieve<br>maximum performance of<br>ADC                                                        |  |  |

#### TABLE 30-54: ADC MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

# dsPIC33EVXXXGM00X/10X FAMILY

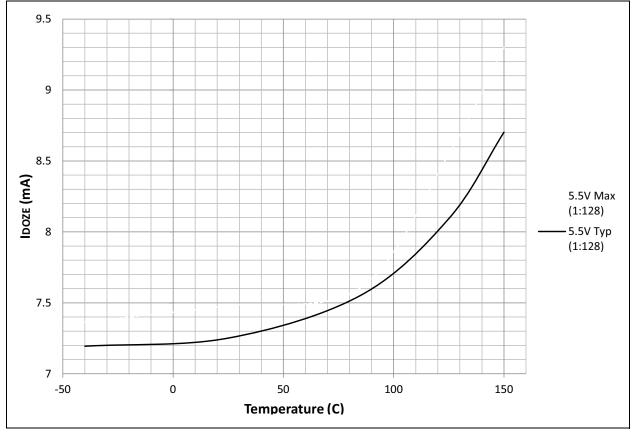

FIGURE 33-12: TYPICAL/MAXIMUM IDOZE vs. TEMPERATURE (DOZE 1:128, 70 MIPS)

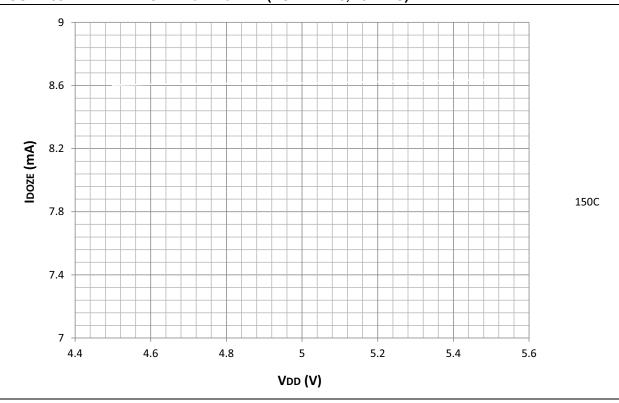

FIGURE 33-11: TYPICAL IDOZE vs. VDD (DOZE 1:128, 70 MIPS)

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

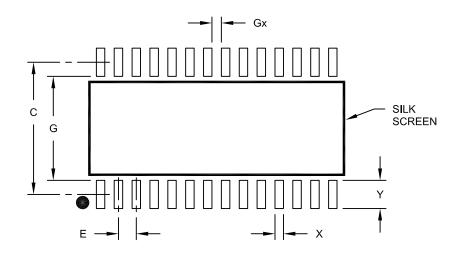

# RECOMMENDED LAND PATTERN

|                          | Units            |      |          |      |  |  |

|--------------------------|------------------|------|----------|------|--|--|

| Dimensior                | Dimension Limits |      |          | MAX  |  |  |

| Contact Pitch            | E                |      | 1.27 BSC |      |  |  |

| Contact Pad Spacing      | С                |      | 9.40     |      |  |  |

| Contact Pad Width (X28)  | Х                |      |          | 0.60 |  |  |

| Contact Pad Length (X28) | Y                |      |          | 2.00 |  |  |

| Distance Between Pads    | Gx               | 0.67 |          |      |  |  |

| Distance Between Pads    | G                | 7.40 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

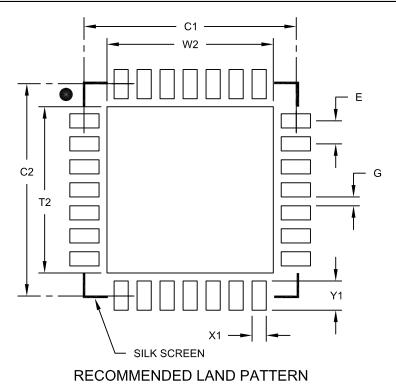

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 4.70 |

| Optional Center Pad Length | T2 |             |      | 4.70 |

| Contact Pad Spacing        | C1 |             | 6.00 |      |

| Contact Pad Spacing        | C2 |             | 6.00 |      |

| Contact Pad Width (X28)    | X1 |             |      | 0.40 |

| Contact Pad Length (X28)   | Y1 |             |      | 0.85 |

| Distance Between Pads      | G  | 0.25        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A