#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm002-e-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

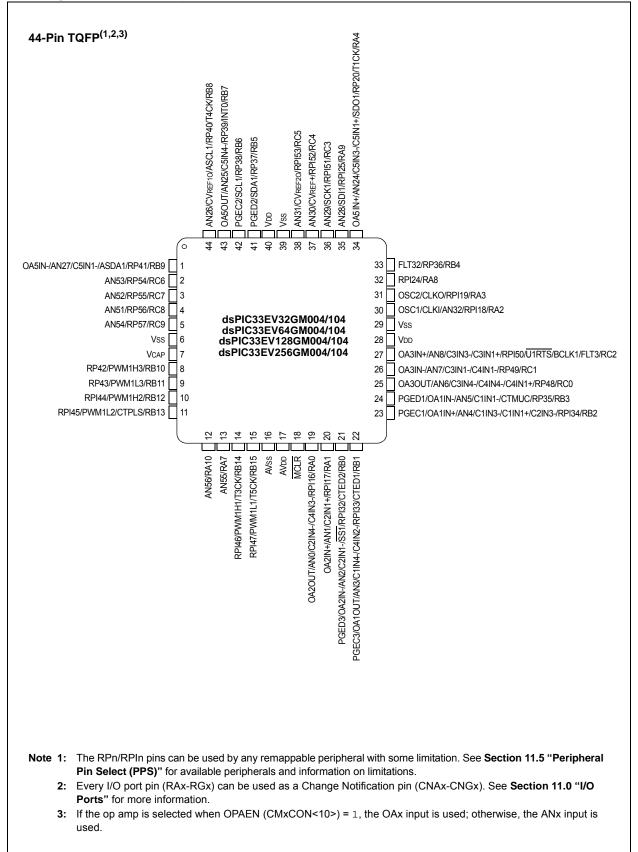

## dsPIC33EVXXXGM00X/10X FAMILY

#### **Pin Diagrams (Continued)**

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EVXXXGM00X/10X family core has two Data Spaces: X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified, linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X DS is used by all instructions and supports all addressing modes. The X DS has separate read and write data buses. The X read data bus is the read data path for all instructions that view the DS as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class). The Y DS is used in concert with the X DS by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to the X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

|             | ••    |        |        |        |          |            |          |          |          |             |       |        |          |          |          |          |          |               |

|-------------|-------|--------|--------|--------|----------|------------|----------|----------|----------|-------------|-------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11     | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6 | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADC1BUF0    | 0300  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUF1    | 0302  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUF2    | 0304  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUF3    | 0306  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUF4    | 0308  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUF5    | 030A  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 5     |        |          |          |          |          |          | xxxx          |

| ADC1BUF6    | 030C  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 6     |        |          |          |          |          |          | xxxx          |

| ADC1BUF7    | 030E  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 7     |        |          |          |          |          |          | xxxx          |

| ADC1BUF8    | 0310  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 8     |        |          |          |          |          |          | xxxx          |

| ADC1BUF9    | 0312  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 9     |        |          |          |          |          |          | xxxx          |

| ADC1BUFA    | 0314  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUFB    | 0316  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUFC    | 0318  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUFD    | 031A  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUFE    | 031C  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUFF    | 031E  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 5     |        |          |          |          |          |          | xxxx          |

| AD1CON1     | 0320  | ADON   | I      | ADSIDL | ADDMABM  | —          | AD12B    | FORM1    | FORM0    | SSRC2       | SSRC1 | SSRC0  | SSRCG    | SIMSAM   | ASAM     | SAMP     | DONE     | 0000          |

| AD1CON2     | 0322  | VCFG2  | VCFG1  | VCFG0  | —        | —          | CSCNA    | CHPS1    | CHPS0    | BUFS        | SMPI4 | SMPI3  | SMPI2    | SMPI1    | SMPI0    | BUFM     | ALTS     | 0000          |

| AD1CON3     | 0324  | ADRC   | I      |        | SAMC4    | SAMC3      | SAMC2    | SAMC1    | SAMC0    | ADCS7       | ADCS6 | ADCS5  | ADCS4    | ADCS3    | ADCS2    | ADCS1    | ADCS0    | 0000          |

| AD1CHS123   | 0326  | _      | I      |        | CH123SB2 | CH123SB1   | CH123NB1 | CH123NB0 | CH123SB0 | —           |       |        | CH123SA2 | CH123SA1 | CH123NA1 | CH123NA0 | CH123SA0 | 0000          |

| AD1CHS0     | 0328  | CH0NB  |        | CH0SB5 | CH0SB4   | CH0SB3     | CH0SB2   | CH0SB1   | CH0SB0   | CH0NA       | -     | CH0SA5 | CH0SA4   | CH0SA3   | CH0SA2   | CH0SA1   | CH0SA0   | 0000          |

| AD1CSSH     | 032E  |        |        |        |          | CSS<31:24> |          |          |          | _           | _     | _      | —        |          | CSS<     | <19:16>  |          | 0000          |

| AD1CSSL     | 0330  |        |        |        |          |            |          |          | CSS      | <15:0>      |       |        |          |          |          |          |          | 0000          |

| AD1CON4     | 0332  | -      | _      | _      | —        | —          | _        | _        | ADDMAEN  | _           | _     | _      | _        | -        | DMABL2   | DMABL1   | DMABL0   | 0000          |

|             |       |        |        |        |          |            | <b>D</b> |          |          |             |       |        |          |          |          |          |          |               |

#### TABLE 4-7: ADC1 REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: CTMU REGISTER MAP

|   | SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Reset<br>s |

|---|-------------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|-------------------|

| Ī | CTMUCON1    | 033A  | CTMUEN  | -       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | —       |          | _        | _        | _        | _     |       | 0000              |

| Ī | CTMUCON2    | 033C  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _     | _     | 0000              |

|   | CTMUICON    | 033E  | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | -       | _       |          | _        | _        | _        | _     | _     | 0000              |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-22: PMD REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1               | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|---------|--------|--------|--------|--------|-------|-------|--------|--------|--------|---------------------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD    | T1MD    | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD <sup>(1)</sup> | AD1MD | 0000          |

| PMD2        | 0762  | _      | —      | —      | —       | IC4MD   | IC3MD  | IC2MD  | IC1MD  |        | —     |       | _      | OC4MD  | OC3MD  | OC2MD               | OC1MD | 0000          |

| PMD3        | 0764  | —      | —      | —      | —       | —       | CMPMD  | _      | _      |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD4        | 0766  | —      | —      | —      | —       | —       | —      | _      | _      |        | —     |       | _      | REFOMD | CTMUMD | _                   | —     | 0000          |

| PMD6        | 076A  | —      | —      | —      | —       | —       | PWM3MD | PWM2MD | PWM1MD |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD7        | 076C  | _      | —      | —      | —       | -       | —      | —      | _      | -      | —     | -     | DMA0MD | —      | —      |                     | —     | 0000          |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA1MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA2MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA3MD |        |        |                     |       |               |

| PMD8        | 076E  | —      | —      | —      | SENT2MD | SENT1MD | —      | _      | DMTMD  |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

#### TABLE 4-41: PORTF REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 Bit ( | All<br>Resets |

|-------------|-------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|---------------|

| TRISF       | 0E64  | _      | —       | —      | —      | —      | —      | —     | —     | _     | —     | —     | —     | —     | —     | TRISF<1:0>  | 0003          |

| PORTF       | 0E66  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | RF<1:0>     | xxxx          |

| LATF        | 0E68  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | LATF<1:0>   | xxxx          |

| ODCF        | 0E6A  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | ODCF<1:0>   | 0000          |

| CNENF       | 0E6C  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | CNIEF<1:0>  | 0000          |

| CNPUF       | 0E6E  | _      | _       | _      | _      | —      | _      | _     | _     | —     | _     | —     | _     | _     | _     | CNPUF<1:0>  | 0000          |

| CNPDF       | 0E70  | _      | _       | _      | _      | —      | _      | _     | _     | _     | _     | —     | _     | _     | _     | CNPDF<1:0>  | 0000          |

| Lawsurds    |       |        | n Decet |        |        |        |        |       |       |       |       |       |       |       |       |             |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-42: PORTG REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG       | 0E78  | _      | _      |        | —      |        | —      |       | TRISC | 6<9:6> |       | —     | _     |       | —     | —     | —     | 03C0          |

| PORTG       | 0E7A  |        | _      | _      | _      | _      | _      |       | RG<   | 9:6>   |       | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG        | 0E7C  |        | _      | _      | _      | _      | _      |       | LATG  | <9:6>  |       | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG        | 0E7E  |        | _      | _      | _      | _      | _      |       | ODCO  | i<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG       | 0E80  |        | _      | _      | _      | _      | _      |       | CNIEC | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG       | 0E82  |        | _      | _      | _      | _      | _      |       | CNPU  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG       | 0E84  | _      | _      |        | —      |        | —      |       | CNPD  | G<9:6> |       | —     | -     | _     | _     | —     | _     | 0000          |

| ANSELG      | 0E86  | _      | _      |        | -      |        | -      |       | ANSG  | <9:6>  |       | -     | _     | _     | —     | _     |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

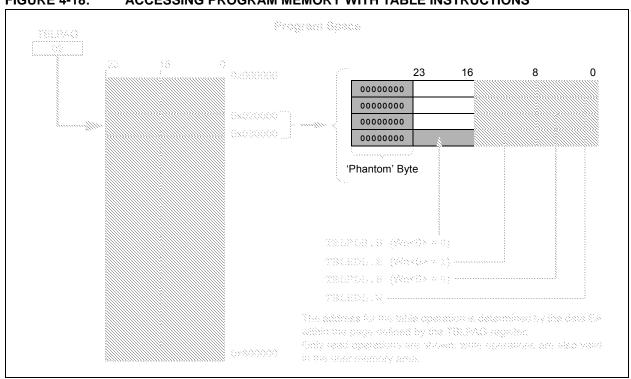

#### 4.7.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through the Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. The TBLRDL and TBLWTL instructions access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space. Accessing the program memory with table instructions is shown in Figure 4-18.

#### FIGURE 4-18: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| U-0             | U-0 | U-0              | U-0            | U-0              | U-0             | U-0                   | U-0         |

|-----------------|-----|------------------|----------------|------------------|-----------------|-----------------------|-------------|

| —               | —   | —                | —              | —                | —               | _                     | —           |

| bit 15          |     |                  |                |                  |                 |                       | bit 8       |

|                 |     |                  |                |                  |                 |                       |             |

| U-0             | U-0 | U-0              | U-0            | U-0              | U-0             | R-0, HS, SC           | R-0, HS, SC |

| —               | —   | —                |                | —                |                 | ECCDBE <sup>(1)</sup> | SGHT        |

| bit 7           |     |                  |                |                  |                 |                       | bit 0       |

|                 |     |                  |                |                  |                 |                       |             |

| Legend:         |     | HS = Hardwar     | e Settable bit | SC = Softwa      | re Clearable bi | t                     |             |

| R = Readable b  | bit | W = Writable b   | bit            | U = Unimplei     | mented bit, rea | d as '0'              |             |

| -n = Value at P | OR  | '1' = Bit is set |                | '0' = Bit is cle | eared           | x = Bit is unkr       | nown        |

#### **REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4**

| bit 15-2 | Unimplemented: Read as '0'                                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| bit 1    | ECCDBE: ECC Double-Bit Error Trap bit <sup>(1)</sup>                                                                      |

|          | <ul><li>1 = ECC double-bit error trap has occurred</li><li>0 = ECC double-bit error trap has not occurred</li></ul>       |

| bit 0    | SGHT: Software-Generated Hard Trap Status bit                                                                             |

|          | <ul><li>1 = Software-generated hard trap has occurred</li><li>0 = Software-generated hard trap has not occurred</li></ul> |

Note 1: ECC double-bit error causes a generic hard trap.

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode, with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

Note: If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| U-0          | U-0           | U-0                                 | U-0              | U-0                                            | U-0               | U-0             | U-0            |

|--------------|---------------|-------------------------------------|------------------|------------------------------------------------|-------------------|-----------------|----------------|

|              | —             | _                                   | _                | _                                              |                   | _               |                |

| bit 15       |               |                                     |                  |                                                |                   |                 | bit 8          |

|              |               |                                     |                  |                                                |                   |                 |                |

| U-0          | R/W-0         | R/W-0                               | R/W-0            | R/W-0                                          | R/W-0             | R/W-0           | R/W-0          |

|              | PCIE          | SCIE                                | BOEN             | SDAHT                                          | SBCDE             | AHEN            | DHEN           |

| bit 7        |               |                                     |                  |                                                |                   |                 | bit 0          |

| Legend:      |               |                                     |                  |                                                |                   |                 |                |

| R = Readab   | le bit        | W = Writable I                      | oit              | U = Unimplem                                   | ented bit, read   | as '0'          |                |

| -n = Value a | t POR         | '1' = Bit is set                    |                  | '0' = Bit is clea                              |                   | x = Bit is unkn | own            |

|              |               |                                     |                  |                                                |                   |                 |                |

| bit 15-7     | Unimplement   | ted: Read as '(                     | )'               |                                                |                   |                 |                |

| bit 6        | PCIE: Stop Co | ondition Interru                    | pt Enable bit (I | <sup>2</sup> C Slave mode                      | only).            |                 |                |

|              |               | nterrupt on detection interrupts    |                  | condition                                      |                   |                 |                |

| bit 5        |               | •                                   |                  | <sup>2</sup> C Slave mode                      | only)             |                 |                |

| bit 5        |               |                                     | •                | or Restart condi                               | • /               |                 |                |

|              |               | ction interrupts                    |                  |                                                |                   |                 |                |

| bit 4        |               | · Overwrite Ena                     | •                | • •                                            |                   |                 |                |

|              |               |                                     |                  | nd an ACK is g                                 |                   | received addre  | ess/data byte, |

|              |               |                                     |                  | <pre>if the RBF bit =<br/>ed when I2CO\</pre>  |                   |                 |                |

| bit 3        |               | x Hold Time Se                      |                  |                                                |                   |                 |                |

|              |               |                                     |                  | after the falling                              |                   |                 |                |

|              |               |                                     |                  | after the falling                              | -                 |                 |                |

| bit 2        |               |                                     |                  | Enable bit (I <sup>2</sup> C<br>mpled low whei |                   | • /             | and state the  |

|              |               | • •                                 |                  | Detection mode                                 |                   |                 | •              |

|              | sequences.    | ·                                   |                  |                                                | ,                 | 0               |                |

|              |               | collision interr                    |                  |                                                |                   |                 |                |

| bit 1        |               | ss Hold Enable                      | •                |                                                |                   |                 |                |

|              |               |                                     | •                | x for a matchir                                | ng received ad    | dress byte; the | e SCLREL bit   |

|              | ·             | ,                                   |                  | he SCLx will be                                | held low          |                 |                |

| hit 0        |               | holding is disab<br>⊣old Enable bit |                  | do only)                                       |                   |                 |                |

| bit 0        |               |                                     |                  | or a received da                               | ata byte: slave l | hardware clears | s the SCLRFI   |

|              | bit (I2CxC    | CON1<12>) and                       |                  |                                                |                   |                 |                |

|              | 0 = Data hold | ling is disabled                    |                  |                                                |                   |                 |                |

#### REGISTER 19-2: I2CxCON2: I2Cx CONTROL REGISTER 2

| R/W-0         | R/W-0                                                                                              | R/W-0                                                  | U-0      | U-0              | U-0             | U-0             | U-0   |

|---------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------|------------------|-----------------|-----------------|-------|

| DMABS2        | DMABS1                                                                                             | DMABS0                                                 | _        | —                | _               | _               | —     |

| pit 15        |                                                                                                    |                                                        |          |                  |                 |                 | bit 8 |

|               |                                                                                                    |                                                        |          |                  |                 |                 |       |

| U-0           | U-0                                                                                                | R/W-0                                                  | R/W-0    | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|               |                                                                                                    | FSA5                                                   | FSA4     | FSA3             | FSA2            | FSA1            | FSA0  |

| oit 7         |                                                                                                    |                                                        |          |                  |                 |                 | bit ( |

| Legend:       |                                                                                                    |                                                        |          |                  |                 |                 |       |

| R = Readable  | e bit                                                                                              | W = Writable t                                         | oit      | U = Unimplen     | nented bit, rea | id as '0'       |       |

| -n = Value at | POR                                                                                                | '1' = Bit is set                                       |          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 12-6      | 101 = 24 buff<br>100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | fers in RAM<br>fers in RAM<br>ers in RAM<br>ers in RAM | 7,       |                  |                 |                 |       |

| bit 5-0       | -                                                                                                  | IFO Area Starts                                        |          | oits             |                 |                 |       |

|               | 11111 = Rec                                                                                        | eive Buffer RB3<br>eive Buffer RB3                     | 31<br>30 |                  |                 |                 |       |

#### REGISTER 22-4: CxFCTRL: CANx FIFO CONTROL REGISTER

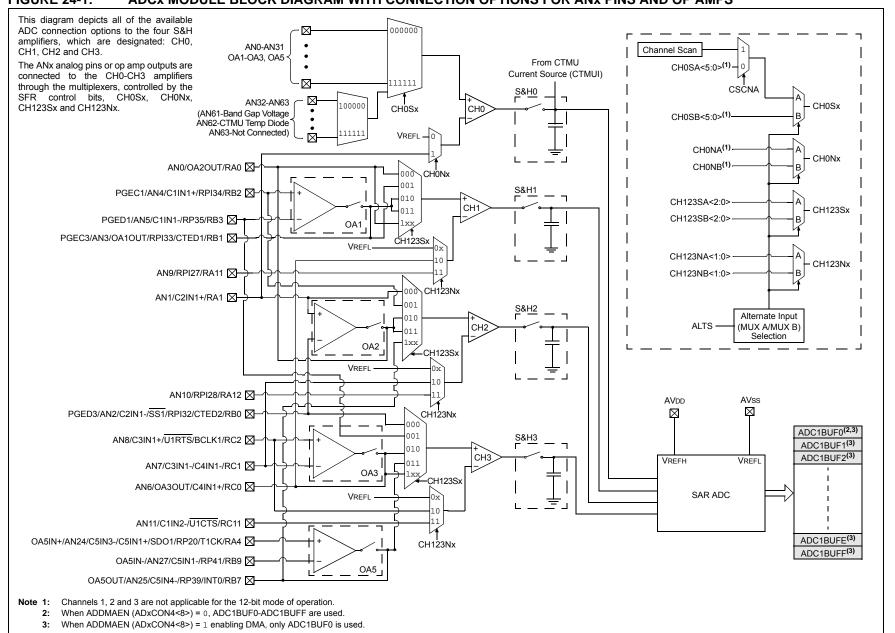

#### FIGURE 24-1: ADCX MODULE BLOCK DIAGRAM WITH CONNECTION OPTIONS FOR ANX PINS AND OP AMPS

#### TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CHARACTERISTICS |                |                                                              | (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                        |      |               |       |                                                                             |

|--------------------|----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol         | Charac                                                       | cteristic <sup>(1)</sup>                                                                                                                                         | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TB10               | T⊤xH           | TxCK High<br>Time                                            | Synchronous<br>mode                                                                                                                                              | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB11               | ΤτχL           | TxCK Low<br>Time                                             | Synchronous<br>mode                                                                                                                                              | Greater of:<br>20 or<br>(Tcy + 20)/N   | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous<br>mode                                                                                                                                              | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                  | 0.75 Tcy + 40                          | _    | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |               |      |               |       |                                        |

|--------------------|----------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------|-------|----------------------------------------|

| Param<br>No.       | Symbol         | Charao                                                       | cteristic <sup>(1)</sup>                                                                                                                                                                                                                                                            | Min.          | Тур. | Max.          | Units | Conditions                             |

| TC10               | ТтхН           | TxCK High<br>Time                                            | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      |      | _             | ns    | Must also meet<br>Parameter TC15       |

| TC11               | ΤτxL           | TxCK Low<br>Time                                             | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      | _    | —             | ns    | Must also meet<br>Parameter TC15       |

| TC15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous,<br>with Prescaler                                                                                                                                                                                                                                                      | 2 Tcy + 40    | _    | —             | ns    | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                                                                                     | 0.75 Tcy + 40 | _    | 1.75 Tcy + 40 | ns    |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

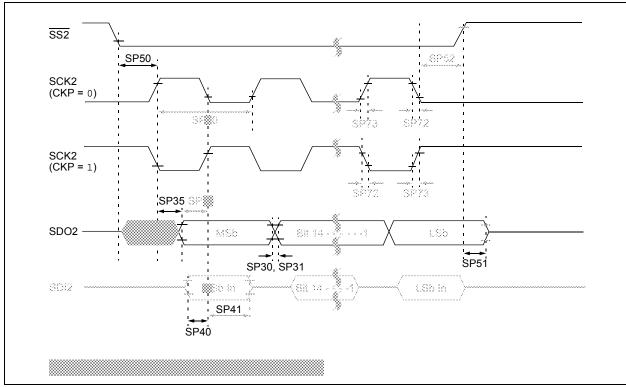

# FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# dsPIC33EVXXXGM00X/10X FAMILY

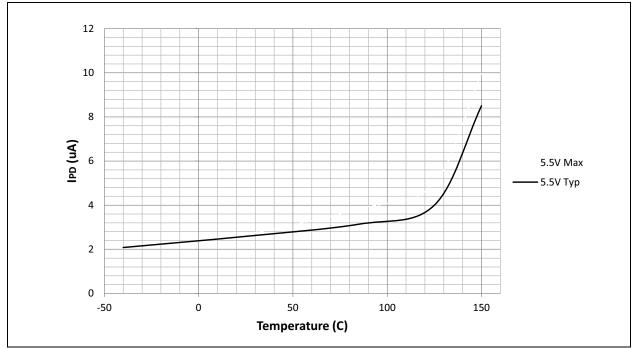

#### FIGURE 32-19: TYPICAL/MAXIMUM △IwDT vs. TEMPERATURE

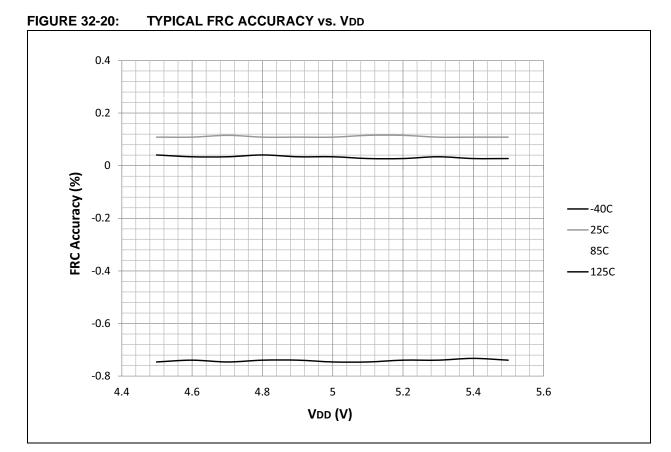

#### 32.5 FRC

DS70005144E-page 422

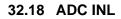

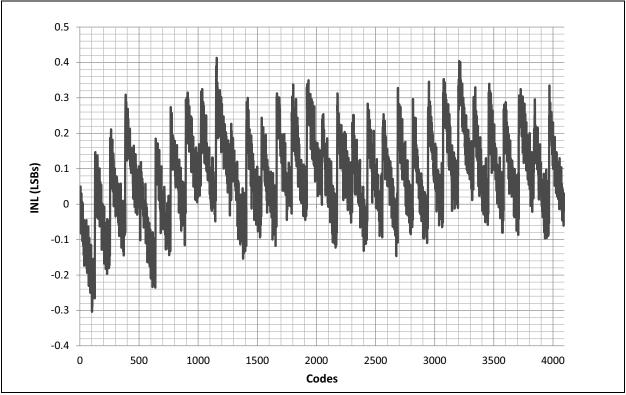

FIGURE 32-46: TYPICAL INL (VDD = 5.5V, +25°C)

# dsPIC33EVXXXGM00X/10X FAMILY

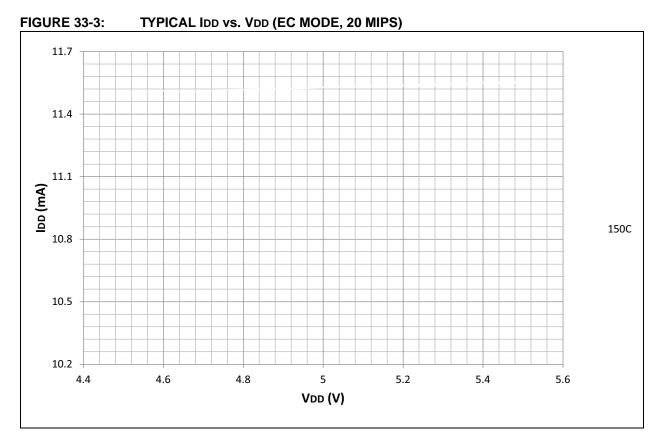

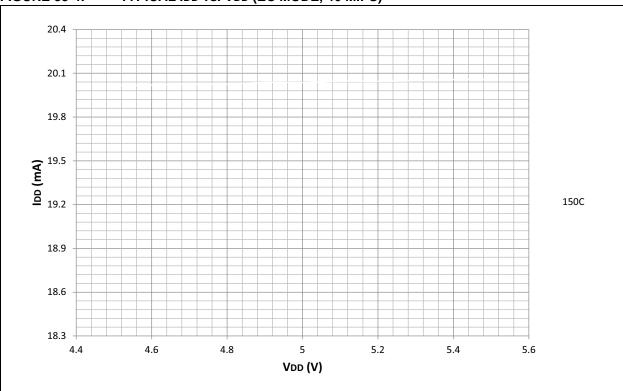

FIGURE 33-4: TYPICAL IDD vs. VDD (EC MODE, 40 MIPS)

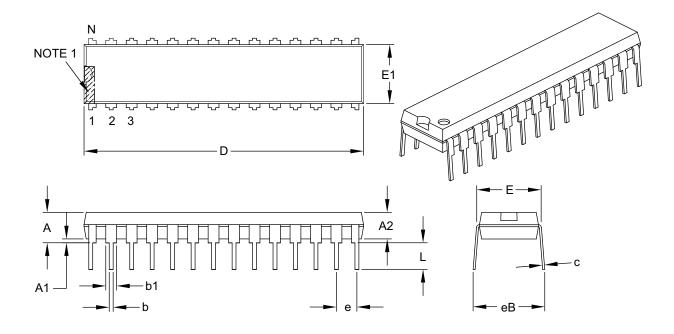

#### 34.2 Package Details

The following sections give the technical details of the packages.

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units                   |          | INCHES |       |  |

|----------------------------|-------------------------|----------|--------|-------|--|

|                            | <b>Dimension Limits</b> | MIN      | NOM    | MAX   |  |

| Number of Pins             | N                       | 28       |        |       |  |

| Pitch                      | e                       | .100 BSC |        |       |  |

| Top to Seating Plane       | A                       | -        | -      | .200  |  |

| Molded Package Thickness   | A2                      | .120     | .135   | .150  |  |

| Base to Seating Plane      | A1                      | .015     | -      | -     |  |

| Shoulder to Shoulder Width | E                       | .290     | .310   | .335  |  |

| Molded Package Width       | E1                      | .240     | .285   | .295  |  |

| Overall Length             | D                       | 1.345    | 1.365  | 1.400 |  |

| Tip to Seating Plane       | L                       | .110     | .130   | .150  |  |

| Lead Thickness             | С                       | .008     | .010   | .015  |  |

| Upper Lead Width           | b1                      | .040     | .050   | .070  |  |

| Lower Lead Width           | b                       | .014     | .018   | .022  |  |

| Overall Row Spacing §      | eB                      | _        | -      | .430  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

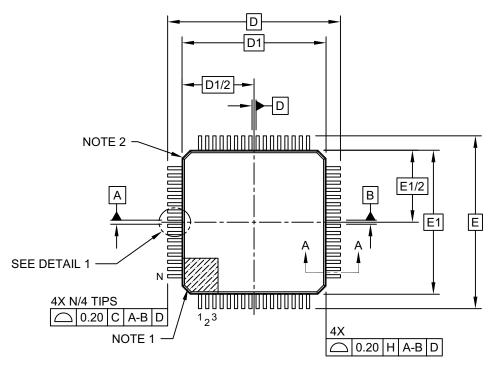

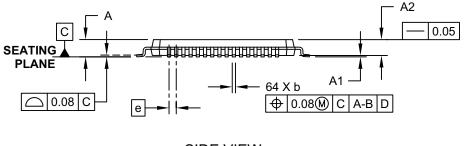

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

| RPOR11 (Peripheral Pin Select Output 11)   | . 170 |

|--------------------------------------------|-------|

| RPOR12 (Peripheral Pin Select Output 12)   | . 171 |

| RPOR13 (Peripheral Pin Select Output 13)   |       |

| RPOR2 (Peripheral Pin Select Output 2)     | . 166 |

| RPOR3 (Peripheral Pin Select Output 3)     | . 166 |

| RPOR4 (Peripheral Pin Select Output 4)     | . 167 |

| RPOR5 (Peripheral Pin Select Output 5)     | . 167 |

| RPOR6 (Peripheral Pin Select Output 6)     |       |

| RPOR7 (Peripheral Pin Select Output 7)     | . 168 |

| RPOR8 (Peripheral Pin Select Output 8)     | . 169 |

| RPOR9 (Peripheral Pin Select Output 9)     | . 169 |

| SENTxCON1 (SENTx Control 1)                |       |

| SENTxDATH (SENTx Receive Data High)        |       |

| SENTxDATL (SENTx Receive Data Low)         |       |

| SENTxSTAT (SENTx Status)                   | . 243 |

| SEVTCMP (PWMx Primary Special Event        |       |

| Compare)                                   |       |

| SPIxCON1 (SPIx Control 1)                  |       |

| SPIxCON2 (SPIx Control 2)                  |       |

| SPIxSTAT (SPIx Status and Control)         |       |

| SR (CPU STATUS)25                          |       |

| T1CON (Timer1 Control)                     |       |

| TRGCONx (PWMx Trigger Control)             |       |

| TRIGx (PWMx Primary Trigger Compare Value) |       |

| TxCON (Timer2 and Timer4 Control)          |       |

| TyCON (Timer3 and Timer5 Control)          |       |

| UxMODE (UARTx Mode)                        |       |

| UxSTA (UARTx Status and Control)           |       |

| Resets                                     |       |

| Brown-out Reset (BOR)                      |       |

| Configuration Mismatch Reset (CM)          |       |

| Illegal Condition Reset (IOPUWR)           |       |

| Illegal Address Mode                       |       |

| Illegal Opcode                             |       |

| Security<br>Uninitialized W Register       |       |

| Master Clear Pin Reset (MCLR)              |       |

| Master Reset Signal (SYSRST)               |       |

| Power-on Reset (POR)                       |       |

| RESET Instruction (SWR)                    |       |

| Trap Conflict Reset (TRAPR)                |       |

| Watchdog Timer Time-out Reset (WDTO)       |       |

| Revision History                           |       |

|                                            | . 400 |

## S

| SENTx Protocol Data Frames                 |  |

|--------------------------------------------|--|

| Serial Peripheral Interface (SPI)          |  |

| Serial Peripheral Interface. See SPI.      |  |

| Single-Edge Nibble Transmission (SENT)     |  |

| Receive Mode                               |  |

| Transmit Mode239                           |  |

| Single-Edge Nibble Transmission for        |  |

| Automotive Applications237                 |  |

| Single-Edge Nibble Transmission. See SENT. |  |

| Software Simulator                         |  |

| MPLAB X SIM                                |  |

| Software Stack Pointer (SSP)74             |  |

| Special Features of the CPU                |  |

| SPI                                        |  |

| Control Registers                          |  |

| Helpful Tips 223                           |  |

## т

| Temperature and Voltage Specifications                      | - 4 |

|-------------------------------------------------------------|-----|

| AC                                                          | 51  |

| High Temperature                                            | ~~  |

| AC                                                          |     |

| Thermal Packaging Characteristics                           |     |

| Third-Party Development Tools                               |     |

| Timer11<br>Control Register1                                |     |

| -                                                           |     |

| Timer2/3 and Timer4/5 1                                     |     |

| Control Registers 1<br>Timing Diagrams                      | 10  |

| 10-Bit ADC Conversion (CHPS<1:0> = 01,                      |     |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000,                      |     |

| SSRCG = 0)                                                  | 00  |

| 10-Bit ADC Conversion (CHPS<1:0> = 01,                      | 00  |

| SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111,                      |     |

| SSRCG = 0, SAMC<4:0> = 00010)                               | 00  |

| 12-Bit ADC Conversion (ASAM = 0, SSRC<2:0> = 00             |     |

| SSRCG = 0)                                                  | 98  |

| BOR and Master Clear Reset                                  | 54  |

| CANx I/O                                                    |     |

| External Clock                                              |     |

| High-Speed PWMx Characteristics                             |     |

| High-Speed PWMx Fault                                       |     |

| I/O Characteristics                                         |     |

| I2Cx Bus Data (Master Mode)                                 |     |

| I2Cx Bus Data (Slave Mode)                                  |     |

| I2Cx Bus Start/Stop Bits (Master Mode)                      |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)                       |     |

| Input Capture x (ICx)                                       |     |

| OCx/PWMx Characteristics                                    | 60  |

| Output Compare x (OCx) Characteristics                      |     |

| Power-on Reset Characteristics                              |     |

| SPI1 Master Mode (Full-Duplex, CKE = 0,                     |     |

| CKP = x, SMP = 1)                                           | 77  |

| SPI1 Master Mode (Full-Duplex, CKE = 1,                     |     |

| CKP = x, SMP = 1)                                           | 76  |

| SPI1 Master Mode (Half-Duplex,                              |     |

| Transmit Only, CKE = 0)                                     | 74  |

| SPI1 Master Mode (Half-Duplex,                              |     |

| Transmit Only, CKE = 1)                                     | 75  |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,                      |     |

| CKP = 0, SMP = 0)                                           | 85  |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,                      |     |

| CKP = 1, SMP = 0)                                           | 83  |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,                      |     |

| CKP = 0, SMP = 0)                                           | 79  |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,                      |     |

| CKP = 1, SMP = 0)                                           | 81  |

| SPI2 Master Mode (Full-Duplex, CKE = 0,                     |     |

| CKP = x, SMP = 1)                                           | 65  |

| SPI2 Master Mode (Full-Duplex, CKE = 1,                     |     |

| CKP = x, SMP = 1)                                           | 64  |

| SPI2 Master Mode (Half-Duplex,                              |     |

| Transmit Only, CKE = 0)                                     | 62  |

| SPI2 Master Mode (Half-Duplex,                              | ~~  |

| Transmit Only, CKE = 1)                                     | 63  |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,                      | 70  |

| CKP = 0, SMP = 0)                                           | 72  |

| SPI2 Slave Mode (Full-Duplex, CKE = 0, $CKD = 1$ , SMD = 0) | 70  |

| CKP = 1, SMP = 0)                                           | 10  |