Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm002-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

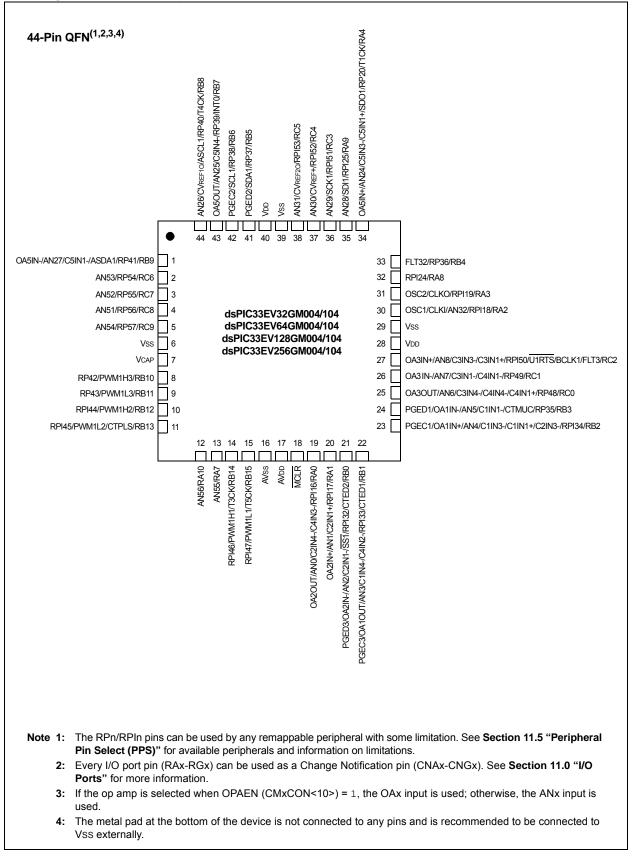

## **Pin Diagrams (Continued)**

| TABLE 1-1: PINO                   |             | D DESC         | RIPTI                                                                         | ONS (CONTINUED)                                                   |  |  |

|-----------------------------------|-------------|----------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS                                                                           | Description                                                       |  |  |

| SCK2                              | I/O         | ST             | Yes                                                                           | Synchronous serial clock input/output for SPI2.                   |  |  |

| SDI2                              | I           | ST             | Yes                                                                           | SPI2 data in.                                                     |  |  |

| SDO2                              | 0           | —              | Yes                                                                           | SPI2 data out.                                                    |  |  |

| SS2                               | I/O         | ST             | Yes                                                                           | SPI2 slave synchronization or frame pulse I/O.                    |  |  |

| SCL1                              | I/O         | ST             | No                                                                            | Synchronous serial clock input/output for I2C1.                   |  |  |

| SDA1                              | I/O         | ST             | No                                                                            | Synchronous serial data input/output for I2C1.                    |  |  |

| ASCL1                             | I/O         | ST             | No                                                                            | Alternate synchronous serial clock input/output for I2C1.         |  |  |

| ASDA1                             | I/O         | ST             | No                                                                            | Alternate synchronous serial data input/output for I2C1.          |  |  |

| C1RX                              | I.          | ST             | Yes                                                                           | CAN1 bus receive pin.                                             |  |  |

| C1TX                              | 0           | —              | Yes                                                                           | CAN1 bus transmit pin.                                            |  |  |

| SENT1TX                           | 0           | —              | Yes                                                                           | SENT1 transmit pin.                                               |  |  |

| SENT1RX                           | 1           | —              | Yes                                                                           | SENT1 receive pin.                                                |  |  |

| SENT2TX                           | 0           | —              | Yes                                                                           | SENT2 transmit pin.                                               |  |  |

| SENT2RX                           | I.          | —              | Yes                                                                           | SENT2 receive pin.                                                |  |  |

| CVREF                             | 0           | Analog         | No                                                                            | Comparator Voltage Reference output.                              |  |  |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | g No Comparator 1 inputs.                                                     |                                                                   |  |  |

| C1OUT                             | 0           | _              | Yes Comparator 1 output.                                                      |                                                                   |  |  |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3- | I           | Analog         | No                                                                            | No Comparator 2 inputs.                                           |  |  |

| C2OUT                             | 0           | —              | Yes                                                                           | Comparator 2 output.                                              |  |  |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3- | I           | Analog         | No                                                                            | Comparator 3 inputs.                                              |  |  |

| C3OUT                             | 0           |                | Yes                                                                           | Comparator 3 output.                                              |  |  |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3- | Ι           | Analog         | No                                                                            | Comparator 4 inputs.                                              |  |  |

| C4OUT                             | 0           | —              | Yes                                                                           | Comparator 4 output.                                              |  |  |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3- | I           | Analog         | No                                                                            | Comparator 5 inputs.                                              |  |  |

| C5OUT                             | 0           | —              | Yes                                                                           | Comparator 5 output.                                              |  |  |

| FLT1-FLT2                         | 1           | ST             | Yes                                                                           | PWM Fault Inputs 1 and 2.                                         |  |  |

| FLT3-FLT8                         | 1           | ST             | NO                                                                            | PWM Fault Inputs 3 to 8.                                          |  |  |

| FLT32                             | 1           | ST             | NO                                                                            | PWM Fault Input 32.                                               |  |  |

| DTCMP1-DTCMP3                     | 1           | ST             | Yes                                                                           | PWM Dead-Time Compensation Inputs 1 to 3.                         |  |  |

| PWM1L-PWM3L                       | 0           | _              | No                                                                            | PWM Low Outputs 1 to 3.                                           |  |  |

| PWM1H-PWM3H                       | 0           | —              | No                                                                            | PWM High Outputs 1 to 3.                                          |  |  |

| SYNCI1                            | 1           | ST             | Yes                                                                           | PWM Synchronization Input 1.                                      |  |  |

| SYNCO1                            | 0           | —              | Yes                                                                           | PWM Synchronization Output 1.                                     |  |  |

| PGED1                             | I/O         | ST             | No                                                                            | Data I/O pin for Programming/Debugging Communication Channel 1.   |  |  |

| PGEC1                             | 1           | ST             | No                                                                            | Clock input pin for Programming/Debugging Communication Channel 1 |  |  |

| PGED2                             | I/O         | ST             | No Data I/O pin for Programming/Debugging Communication Channel 2             |                                                                   |  |  |

| PGEC2                             | 1           | ST             | No Clock input pin for Programming/Debugging Communication Channel            |                                                                   |  |  |

| PGED3                             | I/O         | ST             | No Data I/O pin for Programming/Debugging Communication Channel 3.            |                                                                   |  |  |

| PGEC3                             | I           | ST             | No Clock input pin for Programming/Debugging Communication Chann              |                                                                   |  |  |

| MCLR                              | I/P         | ST             | No Master Clear (Reset) input. This pin is an active-low Reset to the device. |                                                                   |  |  |

| Legend: CMOS = C                  |             |                |                                                                               | or output Analog = Analog input P = Power                         |  |  |

| ST = Schm                         | itt Triaa   | er input w     | /ith CIV                                                                      | IOS levels O = Output I = Input                                   |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | 1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

NOTES:

## TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                    | Bit 14                                                                       | Bit 13                                                                                                   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|----------|------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1     | 0900  | _                         | —                                                                            | OCSIDL                                                                                                   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | —        | ENFLTA     | _            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                     | FLTOUT                                                                       | LTOUT FLTTRIEN OCINV — — — OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 000C |         |         |         |       |          |            |              | 000C   |          |          |          |          |          |               |

| OC1RS       | 0904  |                           |                                                                              |                                                                                                          |         |         |         | Ou    | tput Con | npare 1 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                           |                                                                              |                                                                                                          |         |         |         |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                           |                                                                              |                                                                                                          |         |         |         | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                         | - OCSIDL OCTSEL2 OCTSEL1 OCTSEL0 ENFLTA - OCFLTA TRIGMODE OCM2 OCM1 OCM0 000 |                                                                                                          |         |         |         |       |          | 0000       |              |        |          |          |          |          |          |               |

| OC2CON2     | 090C  | FLTMD                     | FLTOUT                                                                       | FLTTRIEN                                                                                                 | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                           | Output Compare 2 Secondary Register                                          |                                                                                                          |         |         |         |       |          |            | xxxx         |        |          |          |          |          |          |               |

| OC2R        | 0910  |                           |                                                                              |                                                                                                          |         |         |         |       | Outpu    | ut Compare | e 2 Register |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |                           |                                                                              |                                                                                                          |         |         |         | Out   | put Com  | pare 2 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC3CON1     | 0914  | _                         | —                                                                            | OCSIDL                                                                                                   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                     | FLTOUT                                                                       | FLTTRIEN                                                                                                 | OCINV   | _       |         | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                           |                                                                              |                                                                                                          |         |         |         | Ou    | tput Con | npare 3 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                           |                                                                              |                                                                                                          |         |         |         |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                           |                                                                              |                                                                                                          |         |         |         | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  | _                         | —                                                                            | OCSIDL                                                                                                   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                     | FLTOUT                                                                       | FLTTRIEN                                                                                                 | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                           |                                                                              |                                                                                                          |         |         |         | Ou    | tput Con | npare 4 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC4R        | 0924  | Output Compare 4 Register |                                                                              |                                                                                                          |         |         |         |       |          |            | xxxx         |        |          |          |          |          |          |               |

| OC4TMR      | 0926  |                           |                                                                              |                                                                                                          |         |         |         | Out   | put Com  | pare 4 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| Logondu     |       |                           |                                                                              |                                                                                                          |         |         |         |       |          | <i>.</i>   |              |        |          |          |          |          |          |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: CAN1 Module Disable bit<sup>(1)</sup>

- 1 = CAN1 module is disabled0 = CAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EVXXXGM10X devices only.

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | —   | —   | IC4MD | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | _   | —   | OC4MD | OC3MD | OC2MD | OC1MD |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | Unimplemented: Read as '0'                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------|

| bit 11-8  | <b>IC4MD:IC1MD:</b> Input Capture x (x = 1-4) Module Disable bits                                           |

|           | 1 = Input Capture x module is disabled                                                                      |

|           | 0 = Input Capture x module is enabled                                                                       |

| bit 7-4   | Unimplemented: Read as '0'                                                                                  |

| bit 3-0   | <b>OC4MD:OC1MD:</b> Output Compare x (x = 1-4) Module Disable bits                                          |

|           | <ul> <li>1 = Output Compare x module is disabled</li> <li>0 = Output Compare x module is enabled</li> </ul> |

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |  |

|------------------------------|---------------|----------|--------------------|--|

| External Interrupt 1         | INT1          | RPINR0   | INT1R<7:0>         |  |

| External Interrupt 2         | INT2          | RPINR1   | INT2R<7:0>         |  |

| Timer2 External Clock        | T2CK          | RPINR3   | T2CKR<7:0>         |  |

| Input Capture 1              | IC1           | RPINR7   | IC1R<7:0>          |  |

| Input Capture 2              | IC2           | RPINR7   | IC2R<7:0>          |  |

| Input Capture 3              | IC3           | RPINR8   | IC3R<7:0>          |  |

| Input Capture 4              | IC4           | RPINR8   | IC4R<7:0>          |  |

| Output Compare Fault A       | OCFA          | RPINR11  | OCFAR<7:0>         |  |

| PWM Fault 1                  | FLT1          | RPINR12  | FLT1R<7:0>         |  |

| PWM Fault 2                  | FLT2          | RPINR12  | FLT2R<7:0>         |  |

| UART1 Receive                | U1RX          | RPINR18  | U1RXR<7:0>         |  |

| UART2 Receive                | U2RX          | RPINR19  | U2RXR<7:0>         |  |

| SPI2 Data Input              | SDI2          | RPINR22  | SDI2R<7:0>         |  |

| SPI2 Clock Input             | SCK2          | RPINR22  | SCK2R<7:0>         |  |

| SPI2 Slave Select            | SS2           | RPINR23  | SS2R<7:0>          |  |

| CAN1 Receive                 | C1RX          | RPINR26  | C1RXR<7:0>         |  |

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |  |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<7:0>       |  |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<7:0>       |  |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<7:0>       |  |

| SENT1 Input                  | SENT1R        | RPINR44  | SENT1R<7:0>        |  |

| SENT2 Input                  | SENT2R        | RPINR45  | SENT2R<7:0>        |  |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

# 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

# 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The Timer1 External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

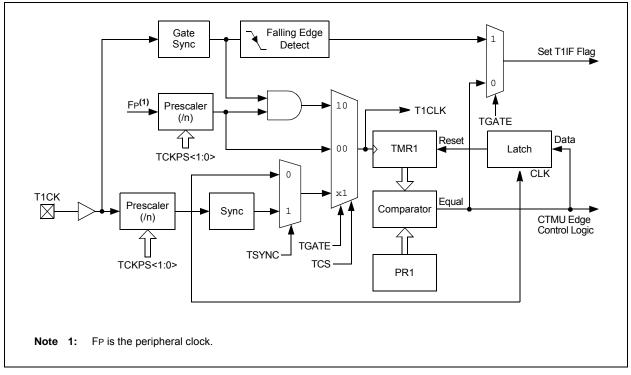

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are given in Table 12-1.

| TABLE 12-1: | TIMER MODE SETTI | NGS |

|-------------|------------------|-----|

|-------------|------------------|-----|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | x     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1

SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to the PWMxL pin; PWMxL output signal is connected to the PWMxH pin

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0

OSYNC: Output Override Synchronization bit

1 = Output overrides through the OVRDAT<1:0> bits are synchronized to the PWMx time base

0 = Output overrides through the OVRDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

#### REGISTER 17-14: TRIGx: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|-----------------------------------|-------|-------|-------|--------------|------------------|-----------------|-------|

|                                   |       |       | TRGCI | MP<15:8>     |                  |                 |       |

| bit 15                            |       |       |       |              |                  |                 | bit 8 |

|                                   |       |       |       |              |                  |                 |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|                                   |       |       | TRGC  | MP<7:0>      |                  |                 |       |

| bit 7                             |       |       |       |              |                  |                 | bit 0 |

|                                   |       |       |       |              |                  |                 |       |

| Legend:                           |       |       |       |              |                  |                 |       |

| R = Readable bit W = Writable bit |       |       | t     | U = Unimpler | mented bit, read | <b>i as</b> '0' |       |

|                                   |       |       |       |              |                  |                 |       |

bit 15-0 **TRGCMP<15:0>:** Trigger Control Value bits

'1' = Bit is set

When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

NOTES:

## 20.2 Transmit Mode

By default, the SENTx module is configured for transmit operation. The module can be configured for continuous asynchronous message frame transmission, or alternatively, for Synchronous mode triggered by software. When enabled, the transmitter will send a Sync followed by the appropriate number of data nibbles, an optional CRC and optional pause pulse. The tick period used by the SENTx transmitter is set by writing a value to the TICKTIME<15:0> (SENTxCON2<15:0>) bits. The tick period calculations are shown in Equation 20-1.

## EQUATION 20-1: TICK PERIOD CALCULATION

$TICKTIME < 15:0 > = \frac{TTICK}{TCLK} - 1$

An optional pause pulse can be used in Asynchronous mode to provide a fixed message frame time period. The frame period used by the SENTx transmitter is set by writing a value to the FRAMETIME<15:0> (SENTxCON3<15:0>) bits. The formulas used to calculate the value of frame time are shown in Equation 20-2.

## EQUATION 20-2: FRAME TIME CALCULATIONS

FRAMETIME<15:0> = TTICK/TFRAME

*FRAMETIME* <15:0>  $\geq$  122 + 27*N*

$FRAMETIME < 15:0 \ge 848 + 12N$

Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6

**Note:** The module will not produce a pause period with less than 12 ticks, regardless of the FRAMETIME<15:0> value. FRAMETIME<15:0> values beyond 2047 will have no effect on the length of a data frame.

## 20.2.1 TRANSMIT MODE CONFIGURATION

## 20.2.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 0 for Transmit mode.

- Write TXM (SENTxCON1<10>) = 0 for Asynchronous Transmit mode or TXM = 1 for Synchronous mode.

- 3. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 4. Write CRCEN (SENTxCON1<8>) for hardware or software CRC calculation.

- 5. Write PPP (SENTxCON1<7>) for optional pause pulse.

- 6. If PPP = 1, write TFRAME to SENTxCON3.

- 7. Write SENTxCON2 with the appropriate value for desired tick period.

- 8. Enable interrupts and set interrupt priority.

- 9. Write initial status and data values to SENTxDATH/L.

- 10. If CRCEN = 0, calculate CRC and write the value to CRC<3:0> (SENTxDATL<3:0>).

- 11. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

User software updates to SENTxDATH/L must be performed after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt to trigger data writes.

| U-0                                                  | U-0                                                                                                                            | U-0                                                                                                                                                                                        | U-0                                   | U-0              | U-0               | U-0            | U-0                     |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------------------|----------------|-------------------------|--|--|--|--|

| _                                                    | —                                                                                                                              | —                                                                                                                                                                                          | —                                     | —                | —                 | —              | —                       |  |  |  |  |

| bit 15                                               |                                                                                                                                |                                                                                                                                                                                            |                                       |                  |                   |                | bit 8                   |  |  |  |  |

| R-0                                                  | R-0                                                                                                                            | R-0                                                                                                                                                                                        | R-0                                   | R-0              | R/C-0             | R-0            | R/W-0, HC               |  |  |  |  |

| PAUSE                                                | NIB2                                                                                                                           | NIB1                                                                                                                                                                                       | NIB0                                  | CRCERR           | FRMERR            | RXIDLE         | SYNCTXEN <sup>(1)</sup> |  |  |  |  |

| bit 7                                                | NIDZ                                                                                                                           | NIDT                                                                                                                                                                                       | NIBO                                  | GROLIN           |                   | INNIDEL        | bit (                   |  |  |  |  |

| 5107                                                 |                                                                                                                                |                                                                                                                                                                                            |                                       |                  |                   |                | Dit t                   |  |  |  |  |

| egend: C = Clearable bit HC = Hardware Clearable bit |                                                                                                                                |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

| R = Readab                                           | ole bit                                                                                                                        | W = Writable                                                                                                                                                                               | e bit                                 | U = Unimple      | mented bit, rea   | id as '0'      |                         |  |  |  |  |

| -n = Value a                                         | at POR                                                                                                                         | '1' = Bit is se                                                                                                                                                                            | •t                                    | '0' = Bit is cle | eared             | x = Bit is unk | nown                    |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

| bit 15-8                                             | -                                                                                                                              | nted: Read as                                                                                                                                                                              |                                       |                  |                   |                |                         |  |  |  |  |

| bit 7                                                |                                                                                                                                | se Period Stat                                                                                                                                                                             |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | ting/receiving a smitting/receiving a |                  | riod              |                |                         |  |  |  |  |

| oit 6-4                                              |                                                                                                                                |                                                                                                                                                                                            | -                                     | ng a pause per   |                   |                |                         |  |  |  |  |

| л 0-4                                                | NIB<2:0>: Nibble Status bit<br>Module in Transmit Mode (RCVEN = 0):                                                            |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | <u>Module in Transmit Mode (RCVEN = 0):</u><br>111 = Module is transmitting a CRC nibble                                       |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | 110 = Module is transmitting Data Nibble 6                                                                                     |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | 101 = Module is transmitting Data Nibble 5                                                                                     |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                | 100 = Module is transmitting Data Nibble 4<br>011 = Module is transmitting Data Nibble 3                                                                                                   |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | ig Data Nibble                        |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | ng Data Nibble                        |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | ng a status nibb                      |                  | riod, or is not t | ransmitting    |                         |  |  |  |  |

|                                                      |                                                                                                                                | eceive Mode (F                                                                                                                                                                             |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | a CRC nibble o                        |                  |                   |                |                         |  |  |  |  |

|                                                      | 110 = Module is receiving Data Nibble 6 or was receiving this nibble when an error occurred                                    |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                | 101 = Module is receiving Data Nibble 5 or was receiving this nibble when an error occurred<br>100 = Module is receiving Data Nibble 4 or was receiving this nibble when an error occurred |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | 011 = Module is receiving Data Nibble 3 or was receiving this nibble when an error occurred                                    |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | 010 = Module is receiving Data Nibble 2 or was receiving this nibble when an error occurred                                    |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | Data Nibble 1 c                       |                  |                   | hen an error o | ccurred                 |  |  |  |  |

|                                                      |                                                                                                                                | -                                                                                                                                                                                          | a status nibble                       | -                | Sync              |                |                         |  |  |  |  |

| bit 3                                                |                                                                                                                                | CRCERR: CRC Status bit (Receive mode only)                                                                                                                                                 |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | <ul> <li>1 = A CRC error occurred for the 1-6 data nibbles in SENTxDATH/L</li> <li>0 = A CRC error has not occurred</li> </ul> |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

| oit 2                                                | FRMERR: Framing Error Status bit (Receive mode only)                                                                           |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      | 1 = A data nibble was received with less than 12 tick periods or greater than 27 tick periods                                  |                                                                                                                                                                                            |                                       |                  |                   |                |                         |  |  |  |  |

|                                                      |                                                                                                                                | error has not o                                                                                                                                                                            |                                       |                  | -                 |                |                         |  |  |  |  |

| oit 1                                                | RXIDLE: SE                                                                                                                     | NTx Receiver                                                                                                                                                                               | Idle Status bit (                     | Receive mode     | e only)           |                |                         |  |  |  |  |

|                                                      |                                                                                                                                |                                                                                                                                                                                            | as been Idle (h                       | igh) for a perio | d of SYNCMA       | X<15:0> or gre | eater                   |  |  |  |  |

|                                                      | 0 = The SEN                                                                                                                    | Tx data bus is                                                                                                                                                                             | not Idle                              |                  |                   |                |                         |  |  |  |  |

| Note 1: II                                           | n Receive mode                                                                                                                 | (RCVEN = 1)                                                                                                                                                                                | the SYNCTXE                           | EN bit is read-c | only.             |                |                         |  |  |  |  |

## REGISTER 20-2: SENTxSTAT: SENTx STATUS REGISTER

**Note 1:** In Receive mode (RCVEN = 1), the SYNCTXEN bit is read-only.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                             | U-0                                        | R/W-0, HC                         | R/W-0                 | R-0                 | R-1            |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------|-----------------------------------|-----------------------|---------------------|----------------|--|--|--|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UTXISEL0                          | _                                          | UTXBRK                            | UTXEN <sup>(1)</sup>  | UTXBF               | TRMT           |  |  |  |

| bit 15          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                                            |                                   |                       | •                   | bit 8          |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |                                            |                                   |                       |                     |                |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                             | R-1                                        | R-0                               | R-0                   | R/C-0               | R-0            |  |  |  |

| URXISEL1        | URXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADDEN                             | RIDLE                                      | PERR                              | FERR                  | OERR                | URXDA          |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |                                            |                                   |                       |                     | bit 0          |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0                               | 1.11                                       |                                   |                       |                     |                |  |  |  |

| Legend:         | L:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C = Clearable                     |                                            |                                   | are Clearable bit     |                     |                |  |  |  |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable                      | DIT                                        | •                                 | mented bit, read      |                     |                |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                  |                                            | '0' = Bit is cle                  | ared                  | x = Bit is unkr     | IOWN           |  |  |  |

| bit 15,13       | <ul> <li>bit 15,13 UTXISEL&lt;1:0&gt;: UARTx Transmission Interrupt Mode Selection bits</li> <li>11 = Reserved; do not use</li> <li>10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a rest the transmit buffer becomes empty</li> <li>01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all trans operations are completed</li> <li>00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is</li> </ul> |                                   |                                            |                                   |                       |                     |                |  |  |  |

| bit 14          | UTXINV: UARTx Transmit Polarity Inversion bit<br>$\frac{If IREN = 0:}{1 = UxTX Idle state is '0'}$ $0 = UxTX Idle state is '1'$ $\frac{If IREN = 1:}{1 = IrDA^{(0)} encoded UxTX Idle state is '1'}$ $0 = IrDA encoded UxTX Idle state is '0'$                                                                                                                                                                                                                                                                                      |                                   |                                            |                                   |                       |                     |                |  |  |  |

| bit 12          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as 'o                   | )'                                         |                                   |                       |                     |                |  |  |  |

| bit 11          | 1 = Sends Sy<br>bit; cleare<br>0 = Sync Bre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ed by hardware<br>ak transmission | ext transmis<br>upon comp<br>n is disabled |                                   | followed by twe       | elve '0' bits, foll | lowed by Stop  |  |  |  |

| bit 10          | UTXEN: UAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Tx Transmit Er                    | nable bit <sup>(1)</sup>                   |                                   |                       |                     |                |  |  |  |

|                 | 0 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                                            | ntrolled by UAR<br>ransmission is | Tx<br>aborted and the | e buffer is rese    | t; UxTX pin is |  |  |  |

| bit 9           | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |                                            |                                   |                       |                     |                |  |  |  |

|                 | <ul> <li>1 = Transmit buffer is full</li> <li>0 = Transmit buffer is not full, at least one more character can be written</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                                   |                       |                     |                |  |  |  |

| bit 8           | <ul> <li>TRMT: Transmit Shift Register (TSR) Empty bit (read-only)</li> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>                                                                                                                                                                                                                                           |                                   |                                            |                                   |                       |                     |                |  |  |  |

| bit 7-6         | URXISEL<1:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0>: UARTx Red                     | ceive Interrup                             | ot Mode Selecti                   | on bits               |                     |                |  |  |  |

|                 | <ul> <li>URXISEL&lt;1:0&gt;: UARTx Receive Interrupt Mode Selection bits</li> <li>11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters</li> </ul>                                                 |                                   |                                            |                                   |                       |                     |                |  |  |  |

## REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EVXXXGM00X/10X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EVXXXGM00X/10X family devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|