Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·>>F

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm003-e-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 9-1 provides the Configuration bits which allow users to choose between the various clock modes.

| Oscillator Mode                                                           | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> |

|---------------------------------------------------------------------------|-------------------|-------------|------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN) <sup>(1,2)</sup>            | Internal          | xx          | 111        |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) <sup>(1)</sup>            | Internal          | xx          | 110        |

| Low-Power RC Oscillator (LPRC) <sup>(1)</sup>                             | Internal          | xx          | 101        |

| Primary Oscillator (HS) with PLL (HSPLL)                                  | Primary           | 10          | 011        |

| Primary Oscillator (XT) with PLL (XTPLL)                                  | Primary           | 01          | 011        |

| Primary Oscillator (EC) with PLL (ECPLL) <sup>(1)</sup>                   | Primary           | 00          | 011        |

| Primary Oscillator (HS)                                                   | Primary           | 10          | 010        |

| Primary Oscillator (XT)                                                   | Primary           | 01          | 010        |

| Primary Oscillator (EC) <sup>(1)</sup>                                    | Primary           | 00          | 010        |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) <sup>(1)</sup> | Internal          | xx          | 001        |

| Fast RC Oscillator (FRC) <sup>(1)</sup>                                   | Internal          | xx          | 000        |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

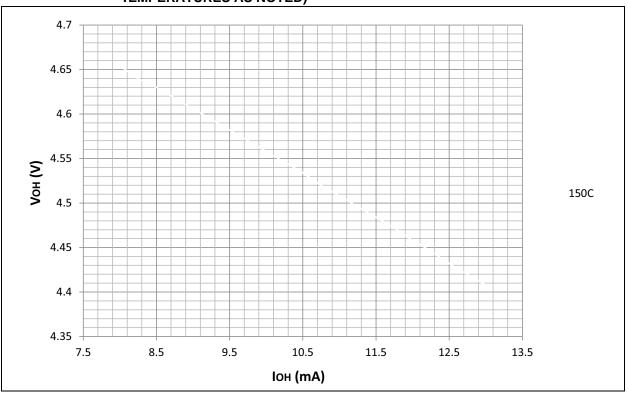

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

### REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = Transmit has not yet started, the SPIxTXB bit is full 0 = Transmit has started, the SPIxTXB bit is empty Standard Buffer mode: Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR. Enhanced Buffer mode: Automatically set in the hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation. bit 0 SPIRBF: SPIx Receive Buffer Full Status bit 1 = Receive is complete, the SPIxRXB bit is full 0 = Receive is incomplete, the SPIxRXB bit is empty Standard Buffer mode:

Automatically set in the hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

## dsPIC33EVXXXGM00X/10X FAMILY

### FIGURE 20-1: SENTX MODULE BLOCK DIAGRAM

FIGURE 20-2: SENTX PROTOCOL DATA FRAMES

| ↓ Sync Period | Status | Data 1 | Data 2 | Data 3 | Data 4 | Data 5 | Data 6 | CRC   | Pause (optional) | $\downarrow$ |  |

|---------------|--------|--------|--------|--------|--------|--------|--------|-------|------------------|--------------|--|

| 56            | 12-27  | 12-27  | 12-27  | 12-27  | 12-27  | 12-27  | 12-27  | 12-27 | 12-768           |              |  |

### REGISTER 20-2: SENTxSTAT: SENTx STATUS REGISTER (CONTINUED)

bit 0 SYNCTXEN: SENTx Synchronization Period Status/Transmit Enable bit<sup>(1)</sup> Module in Receive Mode (RCVEN = 1):

1 = A valid synchronization period was detected; the module is receiving nibble data

0 = No synchronization period has been detected; the module is not receiving nibble data

Module in Asynchronous Transmit Mode (RCVEN = 0, TXM = 0):

The bit always reads as '1' when the module is enabled, indicating the module transmits SENTx data frames continuously. The bit reads '0' when the module is disabled.

Module in Synchronous Transmit Mode (RCVEN = 0, TXM = 1):

1 = The module is transmitting a SENTx data frame

- 0 = The module is not transmitting a data frame, user software may set SYNCTXEN to start another data frame transmission

- Note 1: In Receive mode (RCVEN = 1), the SYNCTXEN bit is read-only.

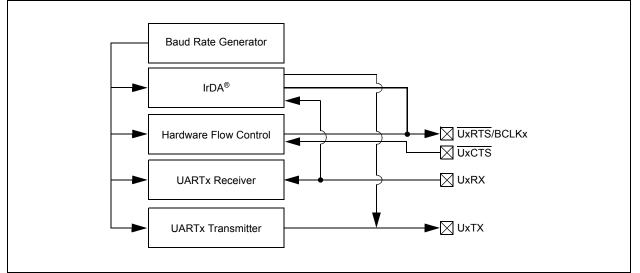

## 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EVXXXGM00X/10X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a

hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

| Note: | Hardware flow control using UxRTS and   |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | UxCTS is not available on all pin count |  |  |  |  |  |  |

|       | devices. See the "Pin Diagrams" section |  |  |  |  |  |  |

|       | for availability.                       |  |  |  |  |  |  |

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

### FIGURE 21-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| R/W-0         | R/W-0                                                                                              | R/W-0                                                  | U-0      | U-0              | U-0             | U-0             | U-0   |

|---------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------|------------------|-----------------|-----------------|-------|

| DMABS2        | DMABS1                                                                                             | DMABS0                                                 | _        | —                | _               | _               | —     |

| pit 15        |                                                                                                    |                                                        |          |                  |                 |                 | bit 8 |

|               |                                                                                                    |                                                        |          |                  |                 |                 |       |

| U-0           | U-0                                                                                                | R/W-0                                                  | R/W-0    | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|               |                                                                                                    | FSA5                                                   | FSA4     | FSA3             | FSA2            | FSA1            | FSA0  |

| oit 7         |                                                                                                    |                                                        |          |                  |                 |                 | bit ( |

| Legend:       |                                                                                                    |                                                        |          |                  |                 |                 |       |

| R = Readable  | e bit                                                                                              | W = Writable t                                         | oit      | U = Unimplen     | nented bit, rea | id as '0'       |       |

| -n = Value at | POR                                                                                                | '1' = Bit is set                                       |          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 12-6      | 101 = 24 buff<br>100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | fers in RAM<br>fers in RAM<br>ers in RAM<br>ers in RAM | 7,       |                  |                 |                 |       |

| bit 5-0       | -                                                                                                  | IFO Area Starts                                        |          | oits             |                 |                 |       |

|               | 11111 = Rec                                                                                        | eive Buffer RB3<br>eive Buffer RB3                     | 31<br>30 |                  |                 |                 |       |

### REGISTER 22-4: CxFCTRL: CANx FIFO CONTROL REGISTER

## dsPIC33EVXXXGM00X/10X FAMILY

| Bit Field     | Register  | Description                                                                                                                                                                                                                                                                                                 |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIOFNC      | FOSC      | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is the general purpose digital I/O pin                                                                                                                                                                        |

| IOL1WAY       | FOSC      | Peripheral Pin Select Configuration bit<br>1 = Allows only one reconfiguration<br>0 = Allows multiple reconfigurations                                                                                                                                                                                      |

| FCKSM<1:0>    | FOSC      | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                           |

| PLLKEN        | FOSC      | PLL Lock Wait Enable bit<br>1 = Clock switches to the PLL source; will wait until the PLL lock signal is valid<br>0 = Clock switch will not wait for PLL lock                                                                                                                                               |

| WDTPS<3:0>    | FWDT      | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                       |

| WDTPRE        | FWDT      | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                       |

| FWDTEN<1:0>   | FWDT      | <ul> <li>Watchdog Timer Enable bits</li> <li>11 = WDT is enabled in hardware</li> <li>10 = WDT is controlled through the SWDTEN bit</li> <li>01 = WDT is enabled only while device is active and disabled in Sleep; the SWDTEN bit is disabled</li> <li>00 = WDT and the SWDTEN bit are disabled</li> </ul> |

| WINDIS        | FWDT      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer is in Non-Window mode<br>0 = Watchdog Timer is in Window mode                                                                                                                                                                                        |

| WDTWIN<1:0>   | FWDT      | Watchdog Timer Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                         |

| BOREN         | FPOR      | Brown-out Reset (BOR) Detection Enable bit<br>1 = BOR is enabled<br>0 = BOR is disabled                                                                                                                                                                                                                     |

| ICS<1:0>      | FICD      | ICD Communication Channel Select bits<br>11 = Communicates on PGEC1 and PGED1<br>10 = Communicates on PGEC2 and PGED2<br>01 = Communicates on PGEC3 and PGED3<br>00 = Reserved, do not use                                                                                                                  |

| DMTIVT<15:0>  | FDMTINTVL | Lower 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTIVT<31:16> | FDMTINTVH | Upper 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTCNT<15:0>  | FDMTCNTL  | Lower 16 Bits of 32-Bit Field that Configures the DMT Instruction Count Time-out Value bits                                                                                                                                                                                                                 |

| TABLE 27-2: | dsPIC33EVXXXGM00X/10X CONFIGURATION BITS DESCRIPTION (CONTINUED) |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

| AC CH        | ARACTERIS | TICS                                                                                              |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                                |

|--------------|-----------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|--------------------------------------------------------------------------------|

| Param<br>No. | Symbol    | Charao                                                                                            | cteristic <sup>(2)</sup>                        | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max.          | Units | Conditions                                                                     |

| TA10         | ТтхН      | T1CK High<br>Time                                                                                 | Synchronous<br>mode                             | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                    |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |

|              |           |                                                                                                   | Asynchronous mode                               | 35                                                                                                                                                                                                                                                                                      | _    | —             | ns    |                                                                                |

| TA11         | ΤτxL      | T1CK Low<br>Time                                                                                  | Synchronous<br>mode                             | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                    | _    |               | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |

|              |           |                                                                                                   | Asynchronous mode                               | 10                                                                                                                                                                                                                                                                                      |      | _             | ns    |                                                                                |

| TA15         | ΤτχΡ      | T1CK Input<br>Period                                                                              | Synchronous<br>mode                             | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                                  | —    | _             | ns    | N = Prescaler<br>Value<br>(1, 8, 64, 256)                                      |

| OS60         | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting TCS<br>(T1CON<1>) bit) |                                                 | DC                                                                                                                                                                                                                                                                                      | _    | 50            | kHz   |                                                                                |

| TA20         | TCKEXTMRL |                                                                                                   | Delay from External T1CK<br>Clock Edge to Timer |                                                                                                                                                                                                                                                                                         |      | 1.75 Tcy + 40 | ns    |                                                                                |

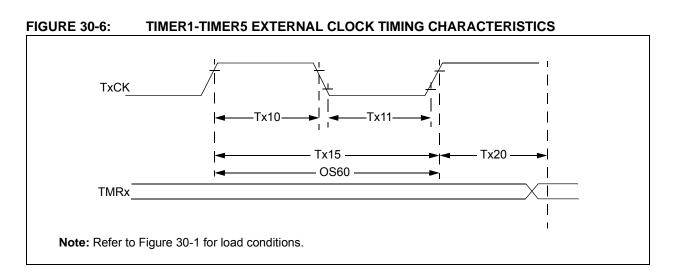

### TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Timer1 is a Type A.

**2:** These parameters are characterized but not tested in manufacturing.

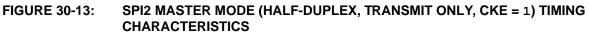

### TABLE 30-31: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| АС СНА | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                                      |

|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|--------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |

| SP10   | FscP                  | Maximum SCK2 Frequency                                                                                                                                                                                                                                                              |      | _                   | 15   | MHz   | See Note 3                           |

| SP20   | TscF                  | SCK2 Output Fall Time                                                                                                                                                                                                                                                               | —    | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP21   | TscR                  | SCK2 Output Rise Time                                                                                                                                                                                                                                                               | —    | —                   | _    | ns    | See Parameter DO31 and Note 4        |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                          | —    | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                                                                                                                                                                                                                                                          | —    | _                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                                                                                                                                                                                                                           |      | 6                   | 20   | ns    |                                      |

| SP36   | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                        | 30   | —                   | _    | ns    |                                      |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

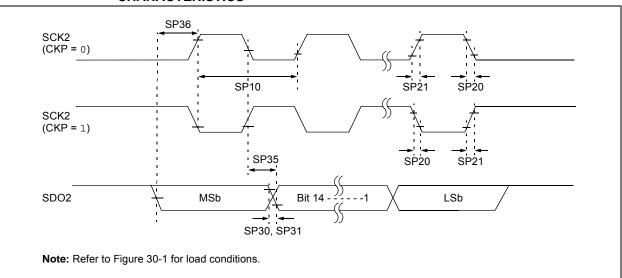

# FIGURE 30-14: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-32:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| АС СНА | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                                      |

|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|--------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                         | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |

| SP10   | FscP                  | Maximum SCK2 Frequency                                                                                                                                                                                                                                                                | _    | _                   | 9    | MHz   | See Note 3                           |

| SP20   | TscF                  | SCK2 Output Fall Time                                                                                                                                                                                                                                                                 | —    | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP21   | TscR                  | SCK2 Output Rise Time                                                                                                                                                                                                                                                                 | —    | —                   | _    | ns    | See Parameter DO31 and Note 4        |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                            | —    | —                   | _    | ns    | See Parameter DO32 and Note 4        |

| SP31   | TdoR                  | SDO2 Data Output Rise<br>Time                                                                                                                                                                                                                                                         | —    | —                   | _    | ns    | See Parameter DO31 and Note 4        |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                                                                                                                                                                                                                             | —    | 6                   | 20   | ns    |                                      |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                          | 30   | —                   | _    | ns    |                                      |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge                                                                                                                                                                                                                                         | 30   | —                   | _    | ns    |                                      |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge                                                                                                                                                                                                                                             | 30   | —                   |      | ns    |                                      |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI2 pins.

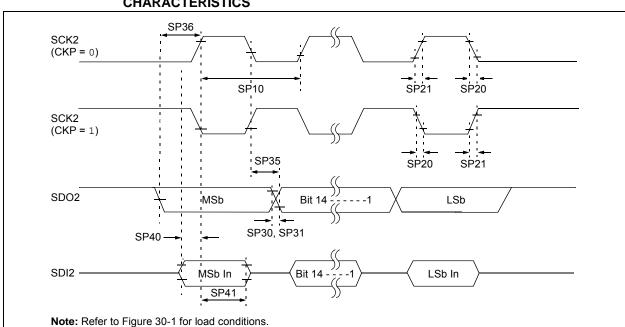

### TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                              | CKE | СКР | SMP |  |  |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |  |  |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |  |  |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |  |  |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |  |  |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |  |  |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |  |  |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |  |  |

### FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

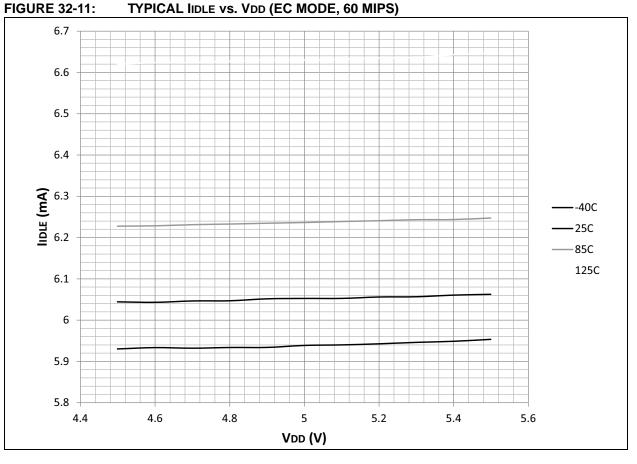

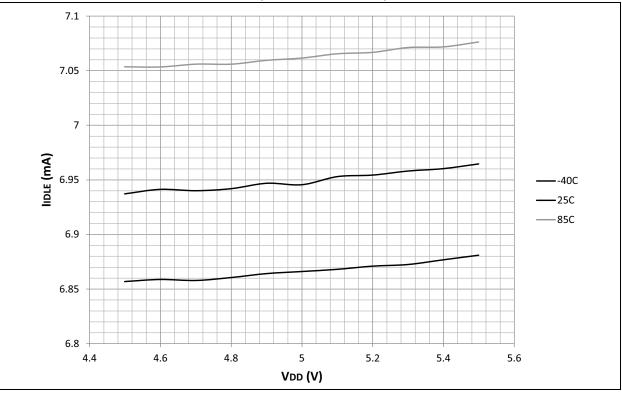

FIGURE 32-12: TYPICAL lidle vs. Vdd (EC MODE, 70 MIPS)

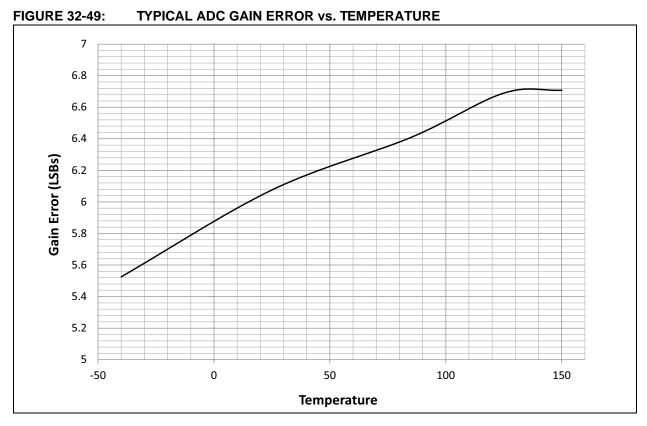

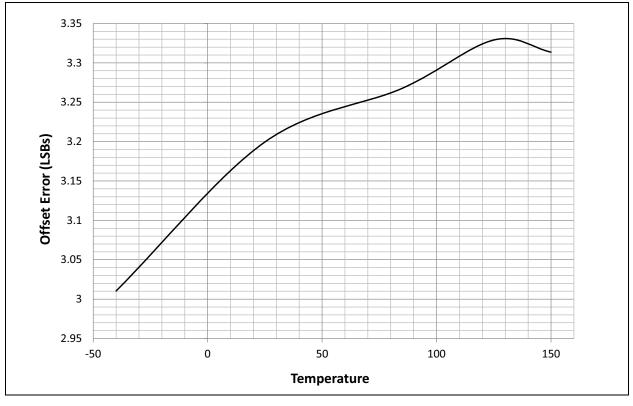

### 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

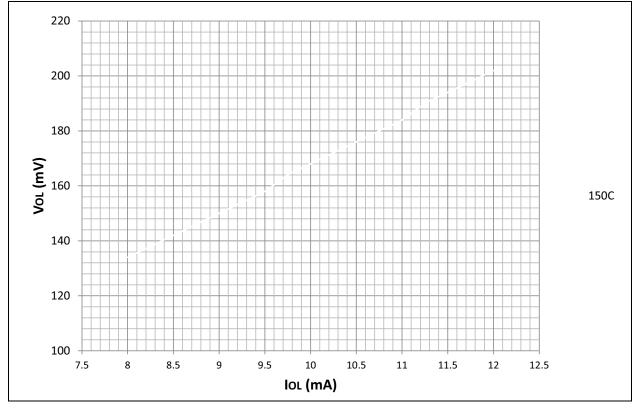

FIGURE 33-27: TYPICAL VOH 4x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

FIGURE 33-28: TYPICAL Vol 8x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

## 34.0 PACKAGING INFORMATION

### 34.1 Package Marking Information

### 28-Lead SPDIP (.300")

### 28-Lead SOIC (.300")

### 28-Lead SSOP

### 28-Lead QFN-S (6x6x0.9 mm)

Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN                                                                                                                                                                          | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                        |

### Example

## Example

### Example

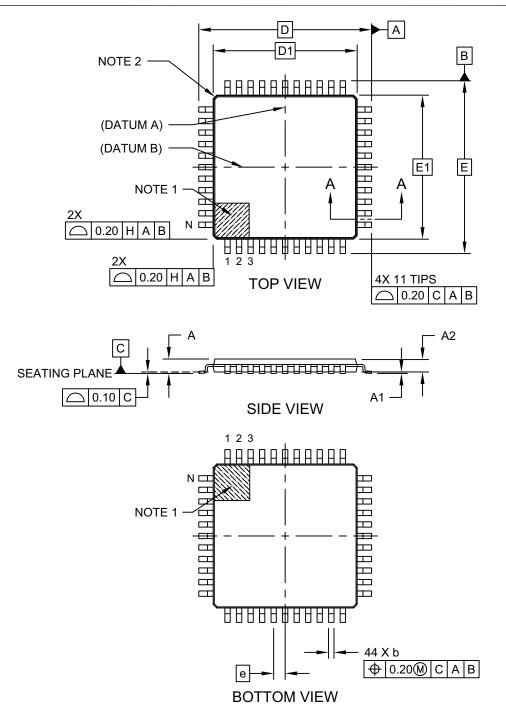

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2