Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm004-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

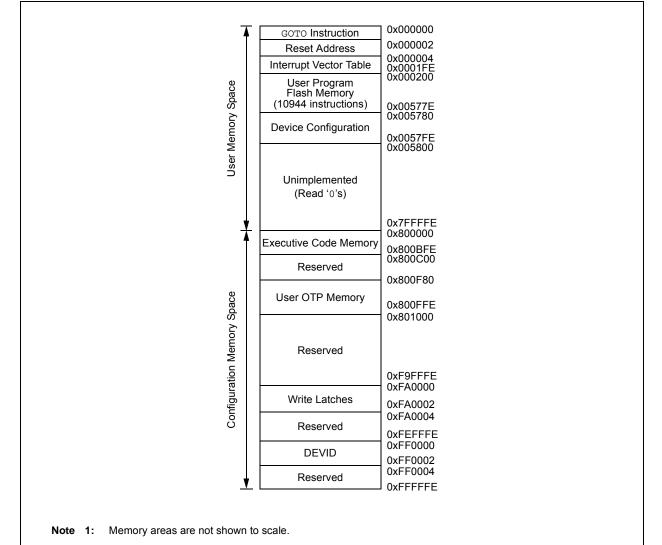

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EVXXXGM00X/10X family architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EVXXXGM00X/10X family devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC, during program execution or from table operation, or from DS remapping, as described in Section 4.7 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x02ABFF). The exception is the use of the TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space and the TBLWT operations, which are used to set up the write latches located in configuration memory space.

The program memory maps, which are presented by the device family and memory size, are shown in Figure 4-1 through Figure 4-4.

| TABLE 4     | -9:   | CAN1     | I REGIS  | STER M   | AP WHE   | N WIN (  | C1CTR    | L<0>) =  | 0 <b>OR</b> 1 | FOR ds   | PIC33E   | VXXXGN   | 110X DE  | VICES    |            |          |          |               |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|---------------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8         | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1     | 0400  | _        | —        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0        | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | —          | -        | WIN      | 0480          |

| C1CTRL2     | 0402  | _        | —        | —        | —        | _        | —        | —        | —             | —        | —        | _        |          | l        | DNCNT<4:0> |          |          | 0000          |

| C1VEC       | 0404  | —        | —        | —        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0       | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0000          |

| C1FCTRL     | 0406  | DMABS2   | DMABS1   | DMABS0   | _        | _        | —        | —        | —             | _        | —        | FSA5     | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO      | 0408  | -        | —        | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0          | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF      | 040A  | -        | —        | ТХВО     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN         | IVRIF    | WAKIF    | ERRIF    | —        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE      | 040C  |          | —        | —        | -        | —        | —        | —        | —             | IVRIE    | WAKIE    | ERRIE    | —        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC        | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0      | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1      | 0410  |          | —        | —        | -        | —        | —        | —        | —             | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2      | 0412  |          | WAKFIL   | —        | -        | —        | SEG2PH2  | SEG2PH1  | SEG2PH0       | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1      | 0414  |          |          |          |          |          |          |          | FLTE          | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1  | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0        | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2  | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0       | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-10: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14                           | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7      | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|----------------------------------|---------|--------|--------|--------|---------|---------------|------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |        |                                  |         |        |        |        | Se      | ee definition | when WIN : | = x     |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |        | RXFUL<15:0> 000                  |         |        |        |        |         |               |            |         | 0000    |        |        |        |         |         |               |

| C1RXFUL2    | 0422          |        | RXFUL<31:16> 00                  |         |        |        |        |         |               |            |         | 0000    |        |        |        |         |         |               |

| C1RXOVF1    | 0428          |        |                                  |         |        |        |        |         | RXOVF         | <15:0>     |         |         |        |        |        |         |         | 0000          |

| C1RXOVF2    | 042A          |        |                                  |         |        |        |        |         | RXOVF         | <31:16>    |         |         |        |        |        |         |         | 0000          |

| C1TR01CON   | 0430          | TXEN1  | TXABT1                           | TXLARB1 | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0       | TXEN0      | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3  | TXABT3                           | TXLARB3 | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0       | TXEN2      | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5  | TXABT5                           | TXLARB5 | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0       | TXEN4      | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7  | TXABT7                           | TXLARB7 | TXERR7 | TXREQ7 | RTREN7 | TX7PRI1 | TX7PRI0       | TXEN6      | TXABAT6 | TXLARB6 | TXERR6 | TXREQ6 | RTREN6 | TX6PRI1 | TX6PRI0 | xxxx          |

| C1RXD       | 0440          |        | CAN1 Receive Data Word Register  |         |        |        |        |         |               |            |         |         | xxxx   |        |        |         |         |               |

| C1TXD       | 0442          |        | CAN1 Transmit Data Word Register |         |        |        |        |         |               |            |         | xxxx    |        |        |        |         |         |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER (CONTINUED)

- bit 3-0 NVMOP<3:0>: NVM Operation Select bits<sup>(1,3,4)</sup>

- 1111 = Reserved

- 1110 = User memory and executive memory bulk erase operation

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Reserved

- 1010 = Reserved

- 1001 = Reserved

- 1000 = Reserved

- 0111 = Reserved

- 0101 = Reserved

- 0100 = Reserved

- 0011 = Memory page erase operation

- 0010 = Memory row program operation

- 0001 = Memory double-word<sup>(5)</sup>

- 0000 = Reserved

- Note 1: These bits can only be reset on a POR.

- 2: If this bit is set, there will be minimal power savings (IIDLE), and upon exiting Idle mode, there is a delay (TVREG) before Flash memory becomes operational.

- 3: All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- 5: Two adjacent words on a 4-word boundary are programmed during execution of this operation.

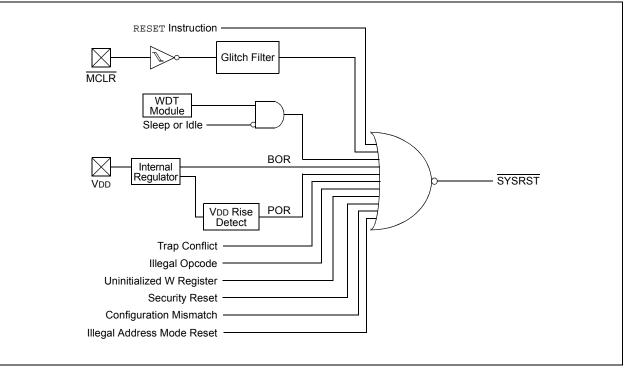

# dsPIC33EVXXXGM00X/10X FAMILY

## FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | U-0   | U-0                   | U-0         |

|----------------------------------------------------------------------|-----|------------------|-----|------------------|-------|-----------------------|-------------|

| —                                                                    | —   | —                | —   | —                | —     | _                     | —           |

| bit 15                                                               |     |                  |     |                  |       |                       | bit 8       |

|                                                                      |     |                  |     |                  |       |                       |             |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | U-0   | R-0, HS, SC           | R-0, HS, SC |

| —                                                                    | —   | —                |     | —                |       | ECCDBE <sup>(1)</sup> | SGHT        |

| bit 7                                                                |     |                  |     |                  |       |                       | bit 0       |

|                                                                      |     |                  |     |                  |       |                       |             |

| Legend:    HS = Hardware Settable bit    SC = Software Clearable bit |     |                  |     |                  |       |                       |             |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                  |       |                       |             |

| -n = Value at P                                                      | OR  | '1' = Bit is set |     | '0' = Bit is cle | eared | x = Bit is unkr       | nown        |

#### **REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4**

| bit 15-2 | Unimplemented: Read as '0'                                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| bit 1    | ECCDBE: ECC Double-Bit Error Trap bit <sup>(1)</sup>                                                                      |

|          | <ul><li>1 = ECC double-bit error trap has occurred</li><li>0 = ECC double-bit error trap has not occurred</li></ul>       |

| bit 0    | SGHT: Software-Generated Hard Trap Status bit                                                                             |

|          | <ul><li>1 = Software-generated hard trap has occurred</li><li>0 = Software-generated hard trap has not occurred</li></ul> |

Note 1: ECC double-bit error causes a generic hard trap.

| U-0             | U-0        | U-0              | U-0      | U-0              | U-0              | U-0           | U-0   |

|-----------------|------------|------------------|----------|------------------|------------------|---------------|-------|

| —               | —          | —                |          | —                | —                | —             | —     |

| bit 15          |            |                  |          |                  |                  |               | bit 8 |

|                 |            |                  |          |                  |                  |               |       |

| R/W-0           | R/W-0      | R/W-0            | R/W-0    | R/W-0            | R/W-0            | R/W-0         | R/W-0 |

|                 |            |                  | STEP     | 2<7:0>           |                  |               |       |

| bit 7           |            |                  |          |                  |                  |               | bit 0 |

|                 |            |                  |          |                  |                  |               |       |

| Legend:         |            |                  |          |                  |                  |               |       |

| R = Readable    | bit        | W = Writable     | bit      | U = Unimpler     | mented bit, read | <b>as</b> '0' |       |

| -n = Value at P | OR         | '1' = Bit is set |          | '0' = Bit is cle | x = Bit is unkr  | nown          |       |

| <u> </u>        |            |                  |          |                  |                  |               |       |

| bit 15-8        | Unimplemen | ted: Read as '   | 0'       |                  |                  |               |       |

| bit 7-0         | STEP2<7:0> | : DMT Clear Ti   | mer bits |                  |                  |               |       |

#### REGISTER 14-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if preceded by the correct loading of the STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading the DMTCNTL/H register and observing the counter being reset.

All Other

Write Patterns = Sets the BAD2 bit; the value of STEP1<7:0> will remain unchanged and the new value being written to STEP2<7:0> will be captured. These bits are cleared when a DMT Reset event occurs.

# REGISTER 14-7: DMTPSCNTL: DMT POST CONFIGURE COUNT STATUS REGISTER LOW

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0          | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|----------------|-------|

|                                                                      |       |                  | PSCN  | T<15:8>          |       |                |       |

| bit 15                                                               |       |                  |       |                  |       |                | bit 8 |

|                                                                      |       |                  |       |                  |       |                |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0          | R/W-0 |

|                                                                      |       |                  | PSCN  | NT<7:0>          |       |                |       |

| bit 7                                                                |       |                  |       |                  |       |                | bit 0 |

|                                                                      |       |                  |       |                  |       |                |       |

| Legend:                                                              |       |                  |       |                  |       |                |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                |       |

| -n = Value at P                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unk | nown  |

bit 15-0 **PSCNT<15:0>:** Lower DMT Instruction Count Value Configuration Status bits This is always the value of the FDMTCNTL Configuration register.

## REGISTER 14-8: DMTPSCNTH: DMT POST CONFIGURE COUNT STATUS REGISTER HIGH

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

|                                                                        |       |       | PSCN  | T<31:24>                           |       |       |       |

| bit 15                                                                 |       |       |       |                                    |       |       | bit 8 |

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                        |       |       | PSCN  | T<23:16>                           |       |       |       |

| bit 7                                                                  |       |       |       |                                    |       |       | bit ( |

| Legend:                                                                |       |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit                                      |       |       |       | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       | nown  |       |                                    |       |       |       |

bit 15-0 **PSCNT<31:16>:** Higher DMT Instruction Count Value Configuration Status bits This is always the value of the FDMTCNTH Configuration register.

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 **FLTMD FLTOUT FLTTRIEN** OCINV \_\_\_\_ \_\_\_\_ OC32 \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0, HS R/W-0 R/W-0 R/W-1 R/W-1 R/W-0 R/W-0 OCTRIG OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 TRIGSTAT SYNCSEL1 SYNCSEL0 bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTMD: Fault Mode Select bit 1 = Fault mode is maintained until the Fault source is removed; the OCFLTA bit is cleared in software and a new PWM period starts 0 = Fault mode is maintained until the Fault source is removed and a new PWM period starts bit 14 FLTOUT: Fault Out bit 1 = PWM output is driven high on a Fault 0 = PWM output is driven low on a Fault bit 13 FLTTRIEN: Fault Output State Select bit 1 = OCx pin is tri-stated on a Fault condition 0 = OCx pin I/O state is defined by the FLTOUT bit on a Fault condition bit 12 **OCINV:** Output Compare x Invert bit 1 = OCx output is inverted 0 = OCx output is not inverted bit 11-9 Unimplemented: Read as '0' bit 8 OC32: Cascade Two OCx Modules Enable bit (32-bit operation) 1 = Cascade module operation is enabled 0 = Cascade module operation is disabled bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit 1 = Triggers OCx from the source designated by the SYNCSELx bits 0 = Synchronizes OCx with the source designated by the SYNCSELx bits bit 6 TRIGSTAT: Timer Trigger Status bit 1 = Timer source has been triggered and is running 0 = Timer source has not been triggered and is being held clear bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit 1 = Output Compare x is tri-stated 0 = Output Compare x module drives the OCx pin

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

**Note 1:** Do not use the OCx module as its own synchronization or trigger source.

2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

# REGISTER 17-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

|                 |       | DAMA             |       | D/14/ 0           |                  | D 44/ 0            |       |  |  |

|-----------------|-------|------------------|-------|-------------------|------------------|--------------------|-------|--|--|

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |

|                 |       |                  | PDC   | x<15:8>           |                  |                    |       |  |  |

| bit 15          |       |                  |       |                   |                  |                    | bit 8 |  |  |

|                 |       |                  |       |                   |                  |                    | ]     |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |

|                 |       |                  | PDC   | \$x<7:0>          |                  |                    |       |  |  |

| bit 7           |       |                  |       |                   |                  |                    | bit 0 |  |  |

|                 |       |                  |       |                   |                  |                    |       |  |  |

| Legend:         |       |                  |       |                   |                  |                    |       |  |  |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, read | <b>d as</b> '0'    |       |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

#### REGISTER 17-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0                                               | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|-----------------------------------------------------|-------|------------------|-------|-----------------|-------|

|                 |       |                                                     | PHAS  | Ex<15:8>         |       |                 |       |

| bit 15          |       |                                                     |       |                  |       |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0                                               | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                                                     | PHAS  | Ex<7:0>          |       |                 |       |

| bit 7           |       |                                                     |       |                  |       |                 | bit 0 |

| Legend:         |       |                                                     |       |                  |       |                 |       |

| R = Readable    | bit   | W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                 |       |

| -n = Value at P | OR    | '1' = Bit is set                                    |       | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs.

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL.

| U-0             | R/W-0                                                                           | R/W-0                | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                        | R/W-0                 | R/W-0                | R/W-0           |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|----------------------|-----------------|--|--|--|--|--|

| —               | CLSRC4                                                                          | CLSRC3               | CLSRC2                                                                                                                                                                                                                                                                       | CLSRC1                       | CLSRC0                | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |

| bit 15          |                                                                                 |                      | CLSRC3  CLSRC2  CLSRC1  CLSRC0  CLPOL <sup>(2)</sup> R/W-1  R/W-1  R/W-0  R/W-0    LTSRC2  FLTSRC1  FLTSRC0  FLTPOL <sup>(2)</sup> FLTMOD1    =  Writable bit  U = Unimplemented bit, read as '0'  =    =  Bit is set  '0' = Bit is cleared  x = Bit is unkno    Read as '0' | bit 8                        |                       |                      |                 |  |  |  |  |  |

|                 |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

| R/W-1           | R/W-1                                                                           |                      | 1                                                                                                                                                                                                                                                                            | 1                            | -                     | -                    | R/W-0           |  |  |  |  |  |

| FLTSRC4         | FLTSRC3                                                                         | FLTSRC2              | FLTSRC1                                                                                                                                                                                                                                                                      | FLTSRC0                      | FLTPOL <sup>(2)</sup> | FLTMOD1              | FLTMOD0         |  |  |  |  |  |

| bit 7           |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      | bit (           |  |  |  |  |  |

| Legend:         |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

| R = Readable    | bit                                                                             | W = Writable         | bit                                                                                                                                                                                                                                                                          | U = Unimpler                 | mented bit, read      | <b>as</b> '0'        |                 |  |  |  |  |  |

| -n = Value at I | POR                                                                             | '1' = Bit is set     |                                                                                                                                                                                                                                                                              | '0' = Bit is cle             | ared                  | x = Bit is unkr      | iown            |  |  |  |  |  |

|                 |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

| bit 15          | -                                                                               |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

| bit 14-10       | CLSRC<4:0>: Current-Limit Control Signal Source Select for PWM Generator x bits |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 11111 <b>= Faul</b>                                                             |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 11110 <b>= Res</b>                                                              | erved                |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | •                                                                               |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | •                                                                               |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 01100 = Op Amp/Comparator 5                                                     |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 01011 = Com                                                                     |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 |                                                                                 | Amp/Comparate        |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 |                                                                                 |                      | or 1                                                                                                                                                                                                                                                                         |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00111 = Faul<br>00110 = Faul                                                    |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00110 = Faul                                                                    |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00100 = Faul                                                                    |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00011 = Faul                                                                    |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00010 <b>= Faul</b>                                                             | t 3                  |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00001 <b>= Faul</b>                                                             | t 2                  |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 00000 <b>= Faul</b>                                                             | t 1 <b>(default)</b> |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

| bit 9           | CLPOL: Curr                                                                     | ent-Limit Polari     | ty for PWM G                                                                                                                                                                                                                                                                 | enerator x bit <sup>(2</sup> | )                     |                      |                 |  |  |  |  |  |

|                 |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | 0 = The selec                                                                   | ted current-limi     | t source is act                                                                                                                                                                                                                                                              | ive-high                     |                       |                      |                 |  |  |  |  |  |

| bit 8           | CLMOD: Curi                                                                     | rent-Limit Mode      | Enable for P                                                                                                                                                                                                                                                                 | WM Generator                 | x bit                 |                      |                 |  |  |  |  |  |

|                 |                                                                                 |                      |                                                                                                                                                                                                                                                                              |                              |                       |                      |                 |  |  |  |  |  |

|                 | ne PWMLOCK (<br>unlock sequen                                                   |                      |                                                                                                                                                                                                                                                                              | :0>) is a '1', the           | e FCLCONx reg         | ister can only b     | e written after |  |  |  |  |  |

# REGISTER 17-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 21.2 UART Control Registers

# REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                     | DE: UARTx N                                                       |                                                             | TER                             |                                          |                  |                           |

|-----------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|

| R/W-0                 | U-0                                                            | R/W-0                                                             | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |

| UARTEN <sup>(1)</sup> |                                                                | USIDL                                                             | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |

| bit 15                |                                                                |                                                                   |                                                             | ·                               | •                                        |                  | bit 8                     |

| R/W-0, HC             | R/W-0                                                          | R/W-0, HC                                                         | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |

| WAKE                  | LPBACK                                                         | ABAUD                                                             | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |

| bit 7                 |                                                                | 101100                                                            | Orodity                                                     | ыкоп                            | TDOLLI                                   | TDOLLO           | bit (                     |

|                       |                                                                |                                                                   |                                                             |                                 |                                          |                  |                           |

| Legend:               |                                                                | HC = Hardwar                                                      | e Clearable bit                                             | t                               |                                          |                  |                           |

| R = Readable          | e bit                                                          | W = Writable I                                                    | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |

| -n = Value at         | POR                                                            | '1' = Bit is set                                                  |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |

| bit 15                | 1 = UARTx is                                                   | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U          | ARTx pins are                                               |                                 |                                          |                  |                           |

|                       | is minima                                                      |                                                                   |                                                             |                                 |                                          |                  |                           |

| bit 14                | •                                                              | ted: Read as '0                                                   |                                                             |                                 |                                          |                  |                           |

| bit 13                |                                                                | Tx Stop in Idle N                                                 |                                                             |                                 |                                          |                  |                           |

|                       |                                                                | nues module op<br>es module opera                                 |                                                             |                                 | s Idle mode                              |                  |                           |

| bit 12                | IREN: IrDA <sup>®</sup>                                        | Encoder and De                                                    | ecoder Enable                                               | bit <sup>(2)</sup>              |                                          |                  |                           |

|                       |                                                                | oder and decod                                                    |                                                             |                                 |                                          |                  |                           |

| bit 11                |                                                                | le Selection for                                                  |                                                             |                                 |                                          |                  |                           |

|                       | 1 = UxRTS p                                                    | oin is in Simplex<br>oin is in Flow Co                            | mode                                                        |                                 |                                          |                  |                           |

| bit 10                |                                                                | ited: Read as '0                                                  |                                                             |                                 |                                          |                  |                           |

| bit 9-8               | -                                                              | IARTx Pin Enab                                                    |                                                             |                                 |                                          |                  |                           |

|                       | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                   | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |

| bit 7                 | WAKE: UAR                                                      | Tx Wake-up on                                                     | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |

|                       | in hardwa                                                      | ontinues to sam<br>are on the follow<br>is not enabled            |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |

| bit 6                 | -                                                              | RTx Loopback                                                      | Mode Select b                                               | it                              |                                          |                  |                           |

|                       |                                                                | k mode is enab                                                    |                                                             |                                 |                                          |                  |                           |

|                       |                                                                | k mode is disab                                                   |                                                             |                                 |                                          |                  |                           |

| "d:<br>tra            | efer to " <b>Univers</b><br>sPIC33/PIC24 F<br>insmit operation | amily Referenc                                                    | e <i>Manual"</i> for i                                      | nformation on e                 | enabling the U                           |                  |                           |

|                       | is feature is only                                             | -                                                                 |                                                             |                                 | )).                                      |                  |                           |

| <b>3:</b> Th          | is feature is only                                             | y available on 4                                                  | 4-pin and 64-p                                              | in devices.                     |                                          |                  |                           |

4: This feature is only available on 64-pin devices.

# 24.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Analog-to-Digital (ADC) module in the dsPIC33EVXXXGM00X/10X family devices supports up to 36 analog input channels.

The ADC module can be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

**Note:** The ADC module needs to be disabled before modifying the AD12B bit.

# 24.1 Key Features

# 24.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) Conversion

- Conversion Speeds of up to 1.1 Msps

- Up to 36 Analog Input Pins

- Connections to Four Internal Op Amps

- Connections to the Charge Time Measurement Unit (CTMU) and Temperature Measurement Diode

- Simultaneous Sampling of:

- Up to four analog input pins

- Four op amp outputs

- Combinations of Analog Inputs and Op Amp Outputs

- Automatic Channel Scan mode

- Selectable Conversion Trigger Source

- Selectable Buffer Fill modes

- Four Result Alignment Options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle Modes

# 24.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed previously, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration. Therefore, simultaneous sampling of multiple channels is not supported.

The ADC has up to 36 analog inputs. The analog inputs, AN32 through AN63, are multiplexed, thus providing flexibility in using any of these analog inputs in addition to the analog inputs, AN0 through AN31. Since AN32 through AN63 are multiplexed, do not use two channels simultaneously, since it may result in erroneous output from the module. These analog inputs are shared with op amp inputs and outputs, comparator inputs and external voltage references. When op amp/comparator functionality is enabled, the analog input that shares that pin is no longer available. The actual number of analog input pins and op amps depends on the specific device.

A block diagram of the ADC module with connection options is shown in Figure 24-1. Figure 24-2 shows a block diagram of the ADC conversion clock period.

## **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

- bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(3)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

$\frac{\text{If CPOL} = 1 \text{ (inverted polarity):}}{\text{Low-to-high transition of the comparator output.}}$  $\frac{\text{If CPOL} = 0 \text{ (non-inverted polarity):}}{\text{High-to-low transition of the comparator output.}}$

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

- If CPOL = 0 (non-inverted polarity):

- Low-to-high transition of the comparator output.

- 00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to the internal CVREFIN voltage

- 0 = VIN+ input connects to the CxIN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator x Channel Select bits<sup>(1)</sup>

- 11 = Inverting input of op amp/comparator connects to the CxIN4- pin

- 10 = Inverting input of op amp/comparator connects to the CxIN3- pin

- 01 = Inverting input of op amp/comparator connects to the CxIN2- pin

- 00 = Inverting input of op amp/comparator connects to the CxIN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- 3: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax       | Description                                      | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------|--------------------------------------------------|---------------|----------------|--------------------------|

| 8                  | BSW                  | BSW.C   | Ws,Wb                 | Write C bit to Ws <wb></wb>                      | 1             | 1              | None                     |

|                    |                      | BSW.Z   | Ws,Wb                 | Write Z bit to Ws <wb></wb>                      | 1             | 1              | None                     |

| 9                  | BTG                  | BTG     | f,#bit4               | Bit Toggle f                                     | 1             | 1              | None                     |

|                    |                      | BTG     | Ws,#bit4              | Bit Toggle Ws                                    | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4               | Bit Test f, Skip if Clear                        | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC    | Ws,#bit4              | Bit Test Ws, Skip if Clear                       | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4               | Bit Test f, Skip if Set                          | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4              | Bit Test Ws, Skip if Set                         | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4               | Bit Test f                                       | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4              | Bit Test Ws to C                                 | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4              | Bit Test Ws to Z                                 | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                       | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                       | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4               | Bit Test then Set f                              | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4              | Bit Test Ws to C, then Set                       | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4              | Bit Test Ws to Z, then Set                       | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                 | Call subroutine                                  | 2             | 4              | SFA                      |

|                    |                      | CALL    | Wn                    | Call indirect subroutine                         | 1             | 4              | SFA                      |

|                    |                      | CALL.L  | Wn                    | Call indirect subroutine (long address)          | 1             | 4              | SFA                      |

| 15                 | CLR                  | CLR     | f                     | f = 0x0000                                       | 1             | 1              | None                     |

|                    |                      | CLR     | WREG                  | WREG = 0x0000                                    | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                    | Ws = 0x0000                                      | 1             | 1              | None                     |

|                    |                      | CLR     | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                                | 1             | 1              | OA,OB,SA,<br>SB          |

| 16                 | CLRWDT               | CLRWDT  |                       | Clear Watchdog Timer                             | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM     | f                     | $f = \overline{f}$                               | 1             | 1              | N,Z                      |

|                    |                      | COM     | f,WREG                | WREG = f                                         | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd                 | $Wd = \overline{Ws}$                             | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                     | Compare f with WREG                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit8              | Compare Wb with lit8                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                     | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0     | f                     | Compare f with 0x0000                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                    | Compare Ws with 0x0000                           | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                     | Compare f with WREG, with Borrow                 | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit8              | Compare Wb with lit8, with Borrow                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                 | Compare Wb with Ws, with Borrow<br>(Wb – Ws – C) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                 | Compare Wb with Wn, skip if =                    | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr            | Compare Wb with Wn, branch if =                  | 1             | 1 (5)          | None                     |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                 | Compare Wb with Wn, skip if >                    | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if >                  | 1             | 1 (5)          | None                     |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                 | Compare Wb with Wn, skip if <                    | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if <                  | 1             | 1 (5)          | None                     |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                 | Compare Wb with Wn, skip if ≠                    | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      |         |                       |                                                  | +             | . /            |                          |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

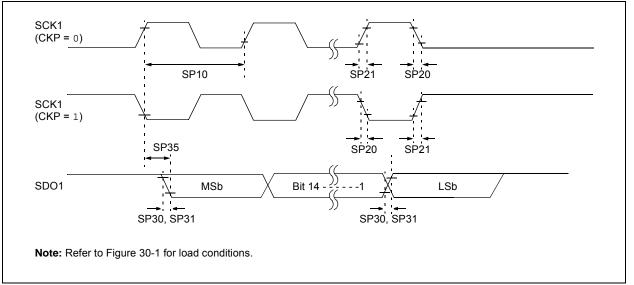

# TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                            | CKE | СКР | SMP |  |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                     | 0,1 | 0,1 | 0,1 |  |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                     | 1   | 0,1 | 1   |  |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                     | 0   | 0,1 | 1   |  |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                           | 1   | 0   | 0   |  |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                           | 1   | 1   | 0   |  |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                           | 0   | 1   | 0   |  |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                           | 0   | 0   | 0   |  |

# FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

# dsPIC33EVXXXGM00X/10X FAMILY

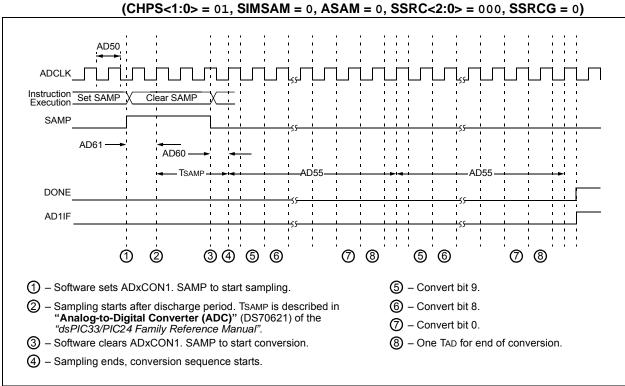

# FIGURE 30-35: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS

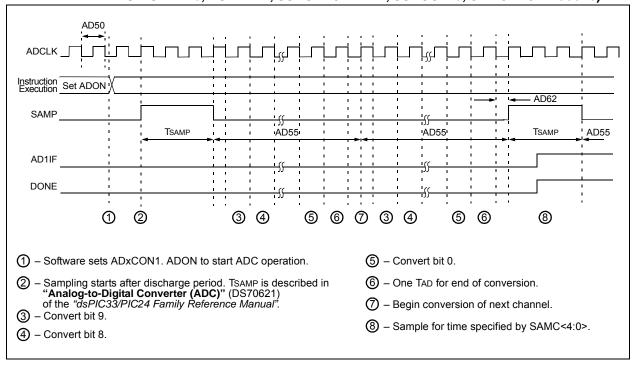

### FIGURE 30-36: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

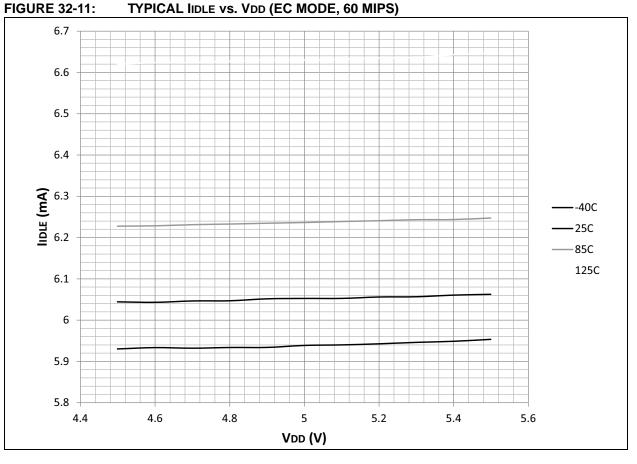

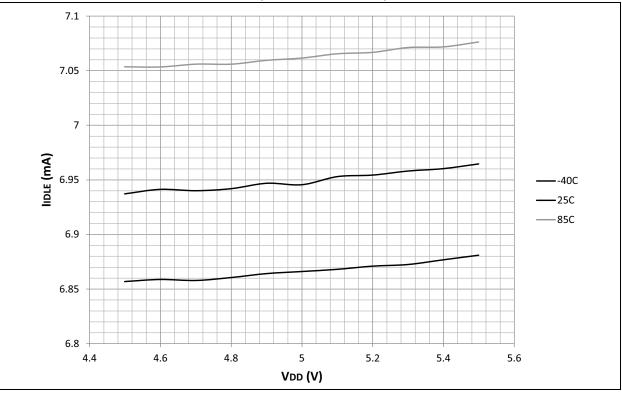

FIGURE 32-12: TYPICAL lidle vs. Vdd (EC MODE, 70 MIPS)

# dsPIC33EVXXXGM00X/10X FAMILY

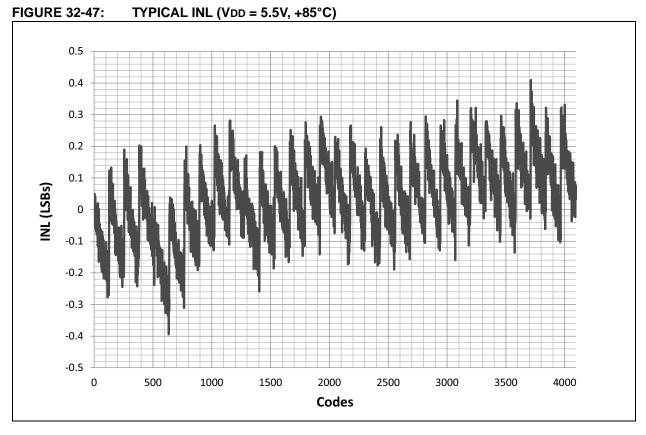

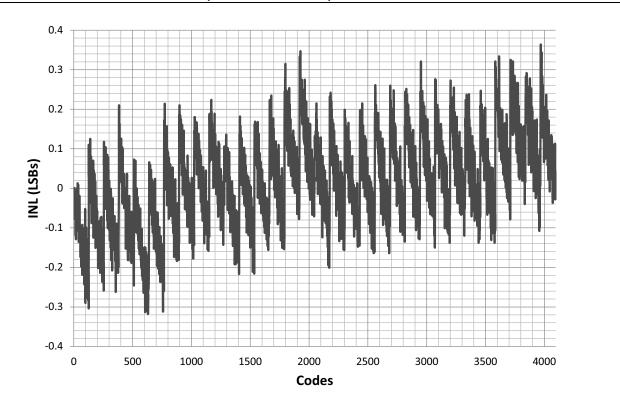

FIGURE 32-48: TYPICAL INL (VDD = 5.5V, +125°C)

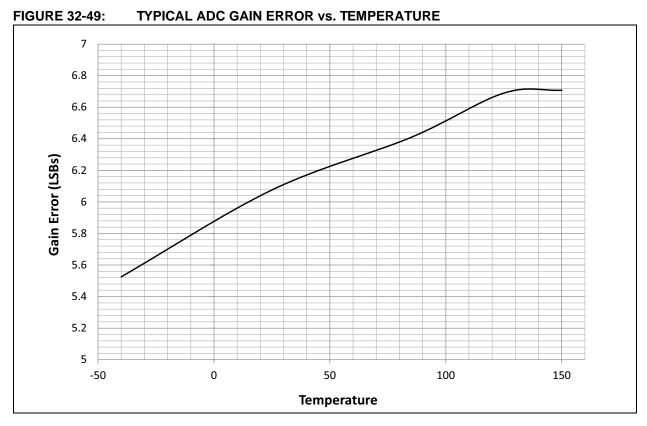

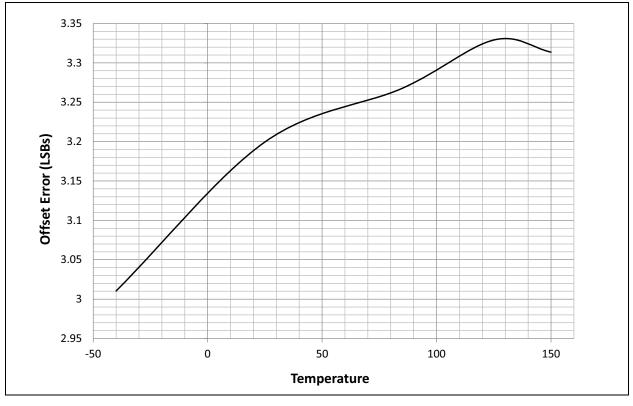

# 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

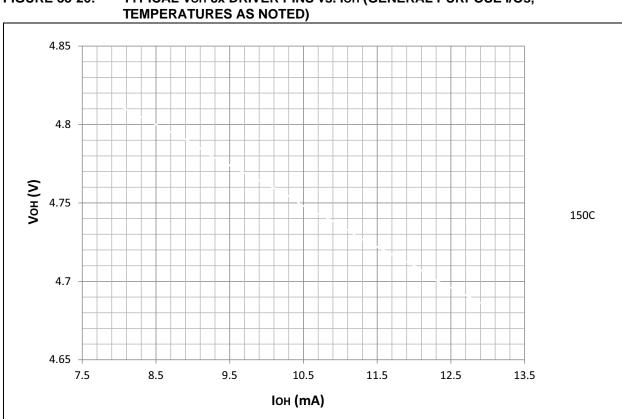

# 33.10 Voltage Output Low (VOL) – Voltage Output High (VOH)

# FIGURE 33-26: TYPICAL VOH 8x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os,