Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

|                           | • 11                                                                            |

| Product Status            | Active                                                                          |

| Core Processor            | dsPIC                                                                           |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 60 MIPs                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O             | 35                                                                              |

| Program Memory Size       | 32KB (11K x 24)                                                                 |

| Program Memory Type       | FLASH                                                                           |

| EEPROM Size               | -                                                                               |

| RAM Size                  | 4K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters           | A/D 24x10/12b                                                                   |

| Oscillator Type           | Internal                                                                        |

| Operating Temperature     | -40°C ~ 125°C (TA)                                                              |

| Mounting Type             | Surface Mount                                                                   |

| Package / Case            | 44-TQFP                                                                         |

| Supplier Device Package   | 44-TQFP (10x10)                                                                 |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm004-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

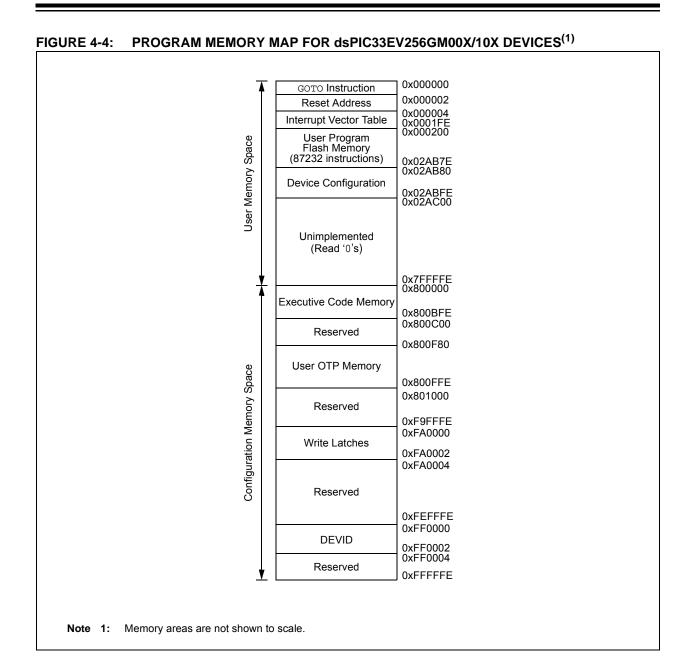

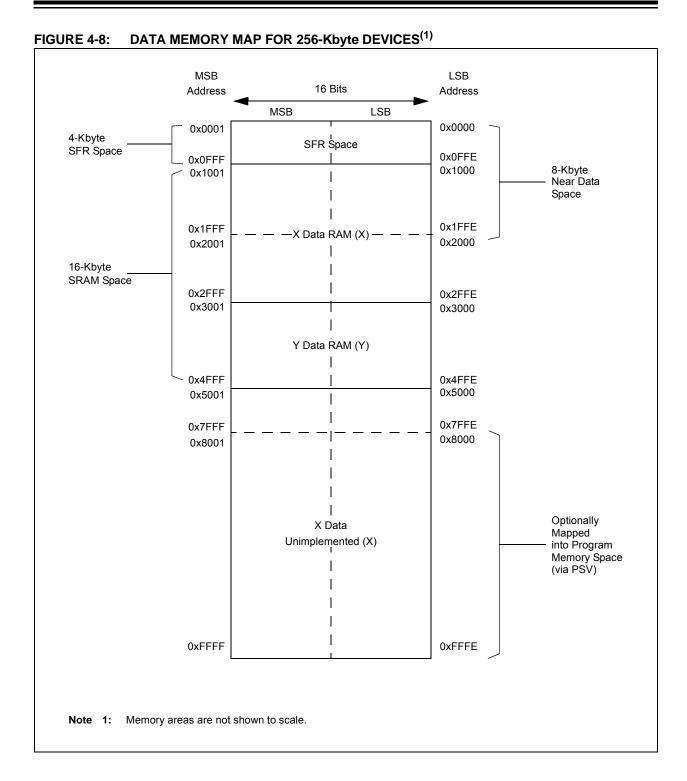

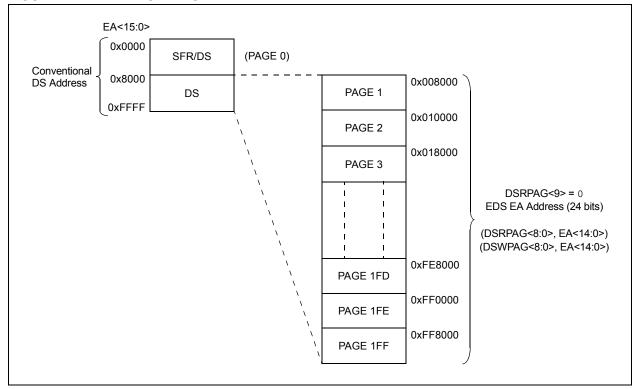

#### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

**2:** Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit. EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0** "**Program Space Visibility from Data Space**" in "**dsPIC33E/PIC24E Program Memory**" (DS70000613) of the "*dsPIC33/PIC24 Family Reference Manual*".

FIGURE 4-12: EDS MEMORY MAP

#### RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED) **REGISTER 6-1:**

bit 3 SLEEP: Wake-up from Sleep Flag bit 1 = Device has been in Sleep mode 0 = Device has not been in Sleep mode bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode bit 1 BOR: Brown-out Reset Flag bit 1 = A Brown-out Reset has occurred 0 = A Brown-out Reset has not occurred POR: Power-on Reset Flag bit bit 0

1 = A Power-on Reset has occurred 0 = A Power-on Reset has not occurred

Note 1: All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | _   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing latency is enabled

0 = Fixed exception processing latency is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

bit 2 **Unimplemented:** Read as '0' bit 1 **C1MD:** CAN1 Module Disable bit<sup>(1)</sup>

1 = CAN1 module is disabled 0 = CAN1 module is enabled

bit 0 AD1MD: ADC1 Module Disable bit

1 = ADC1 module is disabled 0 = ADC1 module is enabled

Note 1: This bit is available on dsPIC33EVXXXGM10X devices only.

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | _   | _   | _   | IC4MD | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | OC4MD | OC3MD | OC2MD | OC1MD |

| bit 7 |     |     |     |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 Unimplemented: Read as '0'

bit 11-8 **IC4MD:IC1MD:** Input Capture x (x = 1-4) Module Disable bits

1 = Input Capture x module is disabled0 = Input Capture x module is enabled

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 **OC4MD:OC1MD:** Output Compare x (x = 1-4) Module Disable bits

1 = Output Compare x module is disabled0 = Output Compare x module is enabled

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|-----|--------|--------|--------|

| _      | _   | _   | _   | _   | PWM3MD | PWM2MD | PWM1MD |

| bit 15 |     |     |     |     |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 **PWM3MD:PWM1MD:** PWMx (x = 1-3) Module Disable bit

1 = PWMx module is disabled 0 = PWMx module is enabled

bit 7-0 **Unimplemented:** Read as '0'

| IOTES: |  |  |  |  |

|--------|--|--|--|--|

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

## REGISTER 17-16: LEBCONX: PWMx LEADING-EDGE BLANKING CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0 | U-0   |

|--------|-------|-------|-------|----------|---------|-----|-------|

| PHR    | PHF   | PLR   | PLF   | FLTLEBEN | CLLEBEN | _   | _     |

| bit 15 |       |       |       |          |         |     | bit 8 |

| U-0   | U-0 | R/W-0              | R/W-0              | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|--------------------|--------------------|-------|-------|-------|-------|

| _     | _   | всн <sup>(1)</sup> | BCL <sup>(1)</sup> | BPHH  | BPHL  | BPLH  | BPLL  |

| bit 7 |     |                    |                    |       |       |       | bit 0 |

| Logona.      |                                                                                                                                                                                                                    |                                                                                           |                                                                                                         |                                  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| R = Readab   | ole bit                                                                                                                                                                                                            | W = Writable bit                                                                          | U = Unimplemented bit,                                                                                  | read as '0'                      |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                                             | '1' = Bit is set                                                                          | '0' = Bit is cleared                                                                                    | x = Bit is unknown               |  |  |  |

| bit 15       | 1 = Rising                                                                                                                                                                                                         | /MxH Rising Edge Trigger E<br>g edge of PWMxH will triggo<br>ing-Edge Blanking ignores t  | er the Leading-Edge Blanking                                                                            | counter                          |  |  |  |

| bit 14       | <b>PHF:</b> PW<br>1 = Fallin                                                                                                                                                                                       | MxH Falling Edge Trigger E                                                                | Enable bit<br>er the Leading-Edge Blanking                                                              | counter                          |  |  |  |

| bit 13       | <ul> <li>PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger the Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores the rising edge of PWMxL</li> </ul> |                                                                                           |                                                                                                         |                                  |  |  |  |

| bit 12       | 1 = Fallin                                                                                                                                                                                                         | MxL Falling Edge Trigger E<br>g edge of PWMxL will triggong-Edge Blanking ignores t       | er the Leading-Edge Blanking                                                                            | counter                          |  |  |  |

| bit 11       | 1 = Leadi                                                                                                                                                                                                          |                                                                                           | ge Blanking Enable bit<br>d to the selected Fault input<br>plied to the selected Fault inpu             | ıt                               |  |  |  |

| bit 10       | 1 = Leadi                                                                                                                                                                                                          | ng-Edge Blanking is applie                                                                | ing-Edge Blanking Enable bit<br>d to the selected current-limit in<br>plied to the selected current-lir |                                  |  |  |  |

| bit 9-6      | Unimple                                                                                                                                                                                                            | mented: Read as '0'                                                                       |                                                                                                         |                                  |  |  |  |

| bit 5        | 1 = State                                                                                                                                                                                                          | nking in Selected Blanking<br>blanking (of current-limit ar<br>anking when the selected b | nd/or Fault input signals) when                                                                         | selected blanking signal is high |  |  |  |

| bit 4        | 1 = State                                                                                                                                                                                                          | nking in Selected Blanking<br>blanking (of current-limit ar<br>anking when the selected b | nd/or Fault input signals) when                                                                         | selected blanking signal is low  |  |  |  |

| bit 3        | 1 = State                                                                                                                                                                                                          | lanking in PWMxH High En<br>blanking (of current-limit ar<br>anking when the PWMxH o      | nd/or Fault input signals) when                                                                         | the PWMxH output is high         |  |  |  |

| bit 2        | 1 = State                                                                                                                                                                                                          | anking in PWMxH Low Ena<br>blanking (of current-limit ar<br>anking when the PWMxH o       | nd/or Fault input signals) when                                                                         | the PWMxH output is low          |  |  |  |

| bit 1        | 1 = State                                                                                                                                                                                                          | anking in PWMxL High Ena<br>blanking (of current-limit ar<br>anking when the PWMxL or     | nd/or Fault input signals) when                                                                         | the PWMxL output is high         |  |  |  |

| bit 0        | 1 = State                                                                                                                                                                                                          | anking in PWMxL Low Ena<br>blanking (of current-limit ar<br>anking when the PWMxL or      | nd/or Fault input signals) when                                                                         | the PWMxL output is low          |  |  |  |

Note 1: The blanking signal is selected through the BLANKSEL<3:0> bits in the AUXCONx register.

Legend:

## REGISTER 18-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER (CONTINUED)

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

$\ensuremath{\mathtt{1}}$  = Transmit has not yet started, the SPIxTXB bit is full

0 = Transmit has started, the SPIxTXB bit is empty

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Automatically set in the hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

- 1 = Receive is complete, the SPIxRXB bit is full

- 0 = Receive is incomplete, the SPIxRXB bit is empty

#### Standard Buffer mode:

Automatically set in the hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

## Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

#### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled, pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data is sampled at the end of data output time

0 = Input data is sampled at the middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

## REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1 (CONTINUED)

bit 7 **GCEN:** General Call Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception

0 = General call address is disabled.

bit 6 STREN: SCLx Clock Stretch Enable bit

In I<sup>2</sup>C Slave mode only, used in conjunction with the SCLREL bit.

1 = Enables clock stretching

0 = Disables clock stretching

bit 5 ACKDT: Acknowledge Data bit

In I<sup>2</sup>C Master mode, during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

In  $I^2C$  Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.

1 = NACK is sent

0 = ACK is sent

bit 4 ACKEN: Acknowledge Sequence Enable bit

In I<sup>2</sup>C Master mode only; applicable during Master Receive mode.

1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit

0 = Acknowledge sequence is Idle

bit 3 **RCEN:** Receive Enable bit (I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for I<sup>2</sup>C, automatically cleared by hardware at the end of 8-bit receive data byte

0 = Receive sequence is not in progress

bit 2 **PEN:** Stop Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Stop condition on SDAx and SCLx pins

0 = Stop condition is Idle

bit 1 **RSEN:** Restart Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Restart condition on SDAx and SCLx pins

0 = Restart condition is Idle

bit 0 **SEN:** Start Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Start condition on SDAx and SCLx pins

0 = Start condition is Idle

**Note 1:** Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.

2: Automatically cleared to '0' at the beginning of slave transmission.

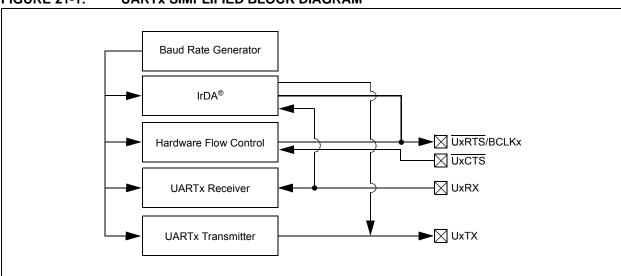

# 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EVXXXGM00X/10X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a

hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an  $\text{IrDA}^{\text{®}}$  encoder and decoder.

Note: Hardware flow control using UxRTS and UxCTS is not available on all pin count devices. See the "Pin Diagrams" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

FIGURE 21-1: UARTX SIMPLIFIED BLOCK DIAGRAM

## REGISTER 22-4: CxFCTRL: CANx FIFO CONTROL REGISTER

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| DMABS2 | DMABS1 | DMABS0 | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | FSA5  | FSA4  | FSA3  | FSA2  | FSA1  | FSA0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 DMABS<2:0>: DMA Buffer Size bits

111 = Reserved

110 = 32 buffers in RAM

101 = 24 buffers in RAM

100 = 16 buffers in RAM

011 = 12 buffers in RAM

010 = 8 buffers in RAM

001 = 6 buffers in RAM

000 = 4 buffers in RAM

bit 12-6 **Unimplemented:** Read as '0'

bit 5-0 FSA<5:0>: FIFO Area Starts with Buffer bits

11111 = Receive Buffer RB31

11110 = Receive Buffer RB30

•

•

00001 = TX/RX Buffer TRB1 00000 = TX/RX Buffer TRB0

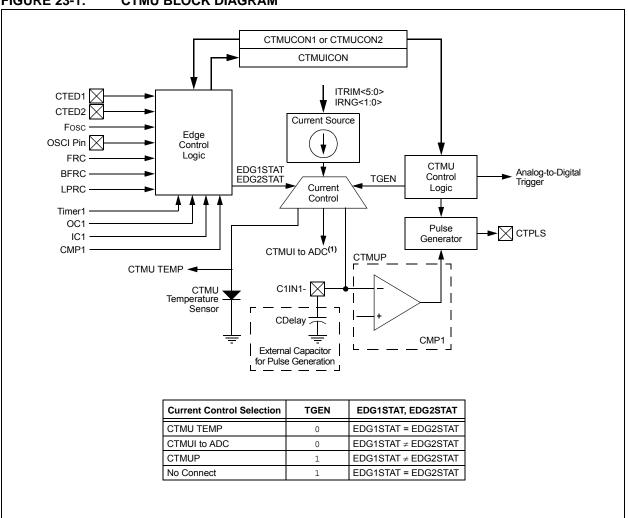

## FIGURE 23-1: CTMU BLOCK DIAGRAM

**Note 1:** Current source to particular ANx pins is provided only when 10-Bit ADC mode is chosen.

TABLE 30-44: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Op<br>(unless other<br>Operating ter | erwise st                        | t <b>ated)</b><br>re -40° | C ≤ Ta ≤ | .5V to 5.5V<br>≤ +85°C for Industrial<br>≤ +125°C for Extended |  |  |  |

|--------------------|-----------------------|--------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------|----------|----------------------------------------------------------------|--|--|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                          | Min. Typ. <sup>(2)</sup> Max. Ui |                           | Units    | Conditions                                                     |  |  |  |

| SP70               | FscP                  | Maximum SCK1 Input Frequency               | _                                             | _                                | 25                        | MHz      | See Note 3                                                     |  |  |  |

| SP72               | TscF                  | SCK1 Input Fall Time                       | _                                             |                                  |                           | ns       | See Parameter DO32 and <b>Note 4</b>                           |  |  |  |

| SP73               | TscR                  | SCK1 Input Rise Time                       | _                                             |                                  | 1                         | ns       | See Parameter DO31 and <b>Note 4</b>                           |  |  |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _                                             |                                  | _                         | ns       | See Parameter DO32 and <b>Note 4</b>                           |  |  |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _                                             | _                                | _                         | ns       | See Parameter DO31 and <b>Note 4</b>                           |  |  |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge  | _                                             | 6                                | 20                        | ns       |                                                                |  |  |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 20                                            | _                                | _                         | ns       |                                                                |  |  |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge | 20                                            | _                                | _                         | ns       |                                                                |  |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 15                                            |                                  | _                         | ns       |                                                                |  |  |  |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓ Input            | 120                                           | _                                | _                         | ns       |                                                                |  |  |  |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance     | 10                                            | _                                | 50                        | ns       | See Note 4                                                     |  |  |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                      | 1.5 Tcy + 40                                  |                                  |                           | ns       | See Note 4                                                     |  |  |  |

- Note 1: These parameters are characterized but not tested in manufacturing.

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 40 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-50: OP AMP/COMPARATOR x SPECIFICATIONS

| DC CHARACTERISTICS |                 |                                           | Standard Operating Conditions (see Note 3): 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |              |       |                                                    |  |

|--------------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|-------|----------------------------------------------------|--|

| Param<br>No.       | Symbol          | Characteristic                            | Min.                                                                                                                                                                                                                                                          | Typ. <sup>(1)</sup> | Max.         | Units | Conditions                                         |  |

|                    |                 | Com                                       | parator AC C                                                                                                                                                                                                                                                  | haracte             | ristics      |       |                                                    |  |

| CM10               | TRESP           | Response Time                             | _                                                                                                                                                                                                                                                             | 19                  | 80           | ns    | V+ input step of 100 mV,<br>V- input held at VDD/2 |  |

| CM11               | Тмс2о∨          | Comparator Mode<br>Change to Output Valid | _                                                                                                                                                                                                                                                             | _                   | 10           | μs    |                                                    |  |

|                    |                 | Con                                       | parator DC C                                                                                                                                                                                                                                                  | haracte             | ristics      |       |                                                    |  |

| CM30               | VOFFSET         | Comparator Offset<br>Voltage              | -80                                                                                                                                                                                                                                                           | ±60                 | 80           | mV    |                                                    |  |

| CM31               | VHYST           | Input Hysteresis Voltage                  |                                                                                                                                                                                                                                                               | 30                  | _            | mV    |                                                    |  |

| CM32               | TRISE/<br>TFALL | Comparator Output Rise/Fall Time          | _                                                                                                                                                                                                                                                             | 20                  | _            | ns    | 1 pF load capacitance on input                     |  |

| CM33               | VGAIN           | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                             | 90                  | _            | db    |                                                    |  |

| CM34               | VICM            | Input Common-Mode<br>Voltage              | AVss                                                                                                                                                                                                                                                          | _                   | AVDD         | V     |                                                    |  |

|                    |                 | Oį                                        | Amp AC Cha                                                                                                                                                                                                                                                    | aracteri            | stics        |       |                                                    |  |

| CM20               | SR              | Slew Rate                                 | _                                                                                                                                                                                                                                                             | 9                   | _            | V/µs  | 10 pF load                                         |  |

| CM21               | Рм              | Phase Margin                              | _                                                                                                                                                                                                                                                             | 35                  | _            | °C    | G = 100V/V, 10 pF load                             |  |

| CM22               | Gм              | Gain Margin                               | _                                                                                                                                                                                                                                                             | 20                  | _            | db    | G = 100V/V, 10 pF load                             |  |

| CM23               | GBW             | Gain Bandwidth                            | _                                                                                                                                                                                                                                                             | 10                  | _            | MHz   | 10 pF load                                         |  |

|                    |                 | Op                                        | Amp DC Cha                                                                                                                                                                                                                                                    | aracteri            | stics        |       |                                                    |  |

| CM40               | VCMR            | Common-Mode Input<br>Voltage Range        | AVss                                                                                                                                                                                                                                                          | _                   | AVDD         | V     |                                                    |  |

| CM41               | CMRR            | Common-Mode<br>Rejection Ratio            | _                                                                                                                                                                                                                                                             | 45                  | _            | db    | VCM = AVDD/2                                       |  |

| CM42               | VOFFSET         | Op Amp Offset Voltage                     | -50                                                                                                                                                                                                                                                           | ±6                  | 50           | mV    |                                                    |  |

| CM43               | VGAIN           | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                             | 90                  | _            | db    |                                                    |  |

| CM44               | los             | Input Offset Current                      | _                                                                                                                                                                                                                                                             |                     | _            | _     | See pad leakage<br>currents in Table 30-10         |  |

| CM45               | lв              | Input Bias Current                        | _                                                                                                                                                                                                                                                             | _                   | _            | _     | See pad leakage currents in Table 30-10            |  |

| CM46               | lout            | Output Current                            | _                                                                                                                                                                                                                                                             | _                   | 420          | μA    | With minimum value of RFEEDBACK (CM48)             |  |

| CM48               | RFEEDBACK       | Feedback Resistance<br>Value              | 8                                                                                                                                                                                                                                                             | _                   | _            | kΩ    | Note 2                                             |  |

| CM49a              | Vout            | Output Voltage                            | AVss + 0.075                                                                                                                                                                                                                                                  | _                   | AVDD - 0.075 | V     | Ιουτ = 420 μΑ                                      |  |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

<sup>2:</sup> Resistances can vary by ±10% between op amps.

**<sup>3:</sup>** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

# 31.2 AC Characteristics and Timing Parameters

The information contained in this section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in **Section 30.2 "AC Characteristics and Timing Parameters"**, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in **Section 30.2 "AC Characteristics and Timing Parameters"** is the Industrial and Extended temperature equivalent of HOS53.

TABLE 31-12: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +150°C                             |

|                    | Operating voltage VDD range as described in Table 31-1.               |

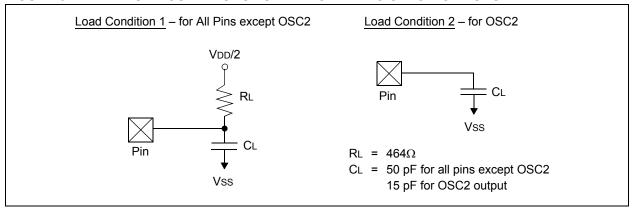

## FIGURE 31-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

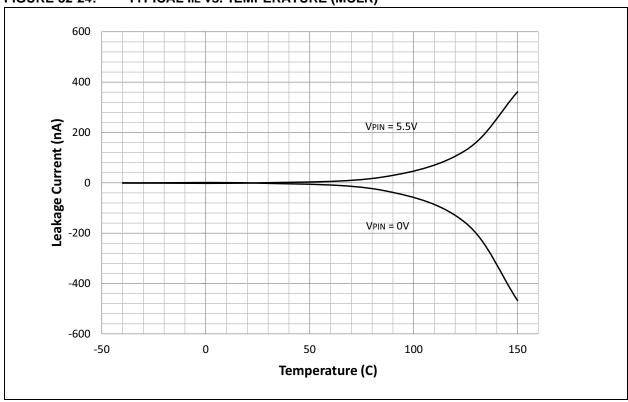

## 32.7 Leakage Current

# FIGURE 32-24: TYPICAL IIL vs. TEMPERATURE (MCLR)

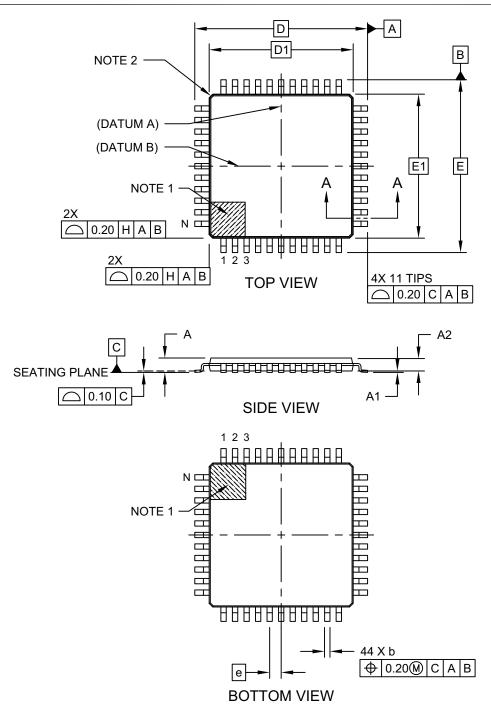

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2