Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm004-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0                                                                | U-0                                                     | U-0                                                     | U-0                                | U-0                            | R-0                                | R-0             | R-0    |

|--------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|------------------------------------|--------------------------------|------------------------------------|-----------------|--------|

| _                                                                  |                                                         |                                                         | —                                  | _                              | CCTXI2                             | CCTXI1          | CCTXI0 |

| oit 15                                                             |                                                         |                                                         |                                    |                                |                                    |                 | bit 8  |

|                                                                    |                                                         |                                                         |                                    |                                |                                    |                 |        |

| U-0                                                                | U-0                                                     | U-0                                                     | U-0                                | U-0                            | R-0                                | R/W-0           | R/W-0  |

| _                                                                  |                                                         |                                                         | _                                  | —                              | MCTXI2                             | MCTXI1          | MCTXI0 |

| bit 7                                                              |                                                         |                                                         |                                    |                                |                                    |                 | bit C  |

|                                                                    |                                                         |                                                         |                                    |                                |                                    |                 |        |

| Legend:                                                            |                                                         |                                                         |                                    |                                |                                    |                 |        |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                         |                                                         |                                    |                                |                                    |                 |        |

| -n = Value a                                                       | t POR                                                   | '1' = Bit is set                                        |                                    | '0' = Bit is cle               | eared                              | x = Bit is unkr | nown   |

| bit 7-3                                                            | 001 = Alterna<br>000 = Default                          | ed<br>te Working Re<br>te Working Re<br>register set is | gister Set 1 is<br>currently in us | currently in us                |                                    |                 |        |

|                                                                    | -                                                       | ted: Read as '                                          |                                    |                                |                                    |                 |        |

| bit 2-0                                                            | 111 = Reserv<br>•<br>•<br>011 = Reserv<br>010 = Alterna | ed<br>te Working Re<br>te Working Re                    | gister Set 2 w                     | as most recen<br>as most recen | tly manually se<br>tly manually se |                 |        |

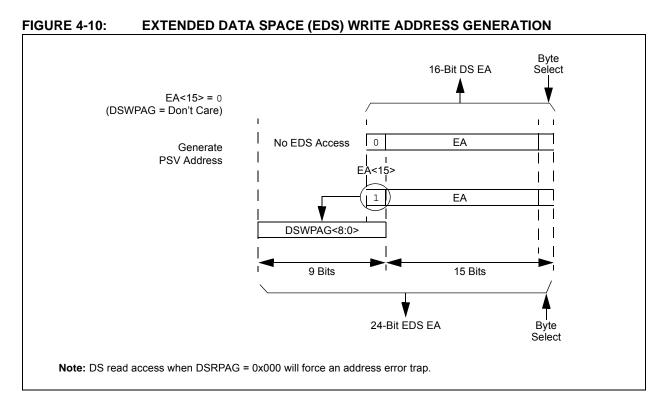

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Figure 4-11.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, therefore, the DSWPAG is dedicated to DS, including EDS. The Data Space and EDS can be read from and written to using DSRPAG and DSWPAG, respectively.

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

- Illegal Address Mode Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this device data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in the other sections of this device data sheet.

**Note:** The status bits in the RCON register should be cleared after they are read. Therefore, the next RCON register value after a device Reset is meaningful.

Note: In all types of Resets, to select the device clock source, the contents of OSCCON are initialized from the FNOSCx Configuration bits in the FOSCSEL Configuration register.

| U-0                               | U-0                                | U-0              | R/W-0       | R/W-0                                   | U-0 | U-0 | R/W-0 |  |  |

|-----------------------------------|------------------------------------|------------------|-------------|-----------------------------------------|-----|-----|-------|--|--|

|                                   | —                                  |                  | SENT2MD     | SENT1MD                                 | _   | _   | DMTMD |  |  |

| bit 15                            | ·                                  |                  | •           | •                                       |     |     | bit 8 |  |  |

|                                   |                                    |                  |             |                                         |     |     |       |  |  |

| U-0                               | U-0                                | U-0              | U-0         | U-0                                     | U-0 | U-0 | U-0   |  |  |

| _                                 | —                                  |                  | —           | —                                       | —   | —   | —     |  |  |

| bit 7                             |                                    |                  |             |                                         |     |     | bit 0 |  |  |

|                                   |                                    |                  |             |                                         |     |     |       |  |  |

| Legend:                           |                                    |                  |             |                                         |     |     |       |  |  |

| R = Readable bit W = Writable bit |                                    |                  | bit         | U = Unimplemented bit, read as '0'      |     |     |       |  |  |

| -n = Value at                     | -n = Value at POR '1' = Bit is set |                  |             | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

|                                   |                                    |                  |             |                                         |     |     |       |  |  |

| bit 15-13                         | Unimplemen                         | ted: Read as '   | כי          |                                         |     |     |       |  |  |

| bit 12                            | SENT2MD: S                         | ENT2 Module      | Disable bit |                                         |     |     |       |  |  |

|                                   |                                    | odule is disable |             |                                         |     |     |       |  |  |

|                                   |                                    | odule is enable  |             |                                         |     |     |       |  |  |

| bit 11                            |                                    | ENT1 Module      |             |                                         |     |     |       |  |  |

|                                   |                                    | odule is disabl  |             |                                         |     |     |       |  |  |

|                                   |                                    | odule is enable  |             |                                         |     |     |       |  |  |

| bit 10-9                          | -                                  | ted: Read as '   |             |                                         |     |     |       |  |  |

| bit 8                             | DMTMD: Dea                         | idman Timer D    | isable bit  |                                         |     |     |       |  |  |

|                                   |                                    | Timer is disab   |             |                                         |     |     |       |  |  |

|                                   |                                    | Timer is enabl   |             |                                         |     |     |       |  |  |

| bit 7-0                           | Unimplemen                         | ted: Read as '   | כ'          |                                         |     |     |       |  |  |

## REGISTER 10-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

| U-0                                                                        | U-0                                      | U-0              | U-0   | U-0          | U-0              | U-0           | U-0   |  |

|----------------------------------------------------------------------------|------------------------------------------|------------------|-------|--------------|------------------|---------------|-------|--|

| —                                                                          | —                                        | —                | —     | —            | —                | —             | —     |  |

| bit 15                                                                     |                                          |                  |       |              |                  |               | bit 8 |  |

|                                                                            |                                          |                  |       |              |                  |               |       |  |

| R/W-0                                                                      | R/W-0                                    | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0         | R/W-0 |  |

|                                                                            |                                          |                  | STEP  | 2<7:0>       |                  |               |       |  |

| bit 7                                                                      |                                          |                  |       |              |                  |               | bit 0 |  |

|                                                                            |                                          |                  |       |              |                  |               |       |  |

| Legend:                                                                    |                                          |                  |       |              |                  |               |       |  |

| R = Readable b                                                             | bit                                      | W = Writable     | bit   | U = Unimplei | mented bit, read | <b>as</b> '0' |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                          |                  |       |              |                  | nown          |       |  |

|                                                                            |                                          |                  |       |              |                  |               |       |  |

| bit 15-8                                                                   | Unimplemen                               | ted: Read as     | 0'    |              |                  |               |       |  |

| bit 7-0                                                                    | bit 7-0 STEP2<7:0>: DMT Clear Timer bits |                  |       |              |                  |               |       |  |

| -n = Value at P<br>bit 15-8                                                | OR<br>Unimplemen                         | '1' = Bit is set | 0'    |              |                  |               | nown  |  |

#### REGISTER 14-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if preceded by the correct loading of the STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading the DMTCNTL/H register and observing the counter being reset.

All Other

Write Patterns = Sets the BAD2 bit; the value of STEP1<7:0> will remain unchanged and the new value being written to STEP2<7:0> will be captured. These bits are cleared when a DMT Reset event occurs.

### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits <sup>(4)</sup>                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111 = Reserved                                                                                                                                                                         |

|         | 11110 = Reserved                                                                                                                                                                         |

|         | 1110 = Reserved                                                                                                                                                                          |

|         | 11100 = CTMU trigger is the source for the capture timer synchronization                                                                                                                 |

|         | 11011 = ADC1 interrupt is the source for the capture timer synchronization <sup>(5)</sup>                                                                                                |

|         | 11010 = Analog Comparator 3 is the source for the capture timer synchronization <sup>(5)</sup>                                                                                           |

|         | 11001 = Analog Comparator 2 is the source for the capture timer synchronization <sup>(5)</sup>                                                                                           |

|         | 11000 = Analog Comparator 1 is the source for the capture timer synchronization <sup>(5)</sup>                                                                                           |

|         | 10111 = Analog Comparator 5 is the source for the capture timer synchronization <sup>(5)</sup>                                                                                           |

|         | 10110 = Analog Comparator 4 is the source for the capture timer synchronization <sup>(5)</sup>                                                                                           |

|         | 10101 = Reserved                                                                                                                                                                         |

|         | 10100 = Reserved                                                                                                                                                                         |

|         | 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization                                                                                                    |

|         | 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization                                                                                                    |

|         | 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization                                                                                                    |

|         | 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization                                                                                                    |

|         | 01111 = GP Timer5 is the source for the capture timer synchronization                                                                                                                    |

|         | 01110 = GP Timer4 is the source for the capture timer synchronization                                                                                                                    |

|         | 01101 = GP Timer3 is the source for the capture timer synchronization                                                                                                                    |

|         | 01100 = GP Timer2 is the source for the capture timer synchronization                                                                                                                    |

|         | 01011 = GP Timer1 is the source for the capture timer synchronization                                                                                                                    |

|         | 01010 = Reserved                                                                                                                                                                         |

|         | 01001 = Reserved                                                                                                                                                                         |

|         | 01000 = Input Capture 4 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                               |

|         | 00111 = Input Capture 3 is the source for the capture timer synchronization <sup>(6)</sup><br>00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup> |

|         | 00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                               |

|         | 00100 = Output Compare 4 is the source for the capture timer synchronization                                                                                                             |

|         | 00011 = Output Compare 3 is the source for the capture timer synchronization                                                                                                             |

|         | 00011 = Output Compare 2 is the source for the capture timer synchronization                                                                                                             |

|         | 00001 = Output Compare 1 is the source for the capture timer synchronization                                                                                                             |

|         | 00000 = Reserved                                                                                                                                                                         |

| Note 1: | The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.                                                                                                            |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

# dsPIC33EVXXXGM00X/10X FAMILY

NOTES:

| R/W-0        | R/W-0                                                            | R/W-0                                                                     | R/W-0                                                               | R/W-0                                                                                    | R/W-0                    | R/W-0                | R/W-0                |

|--------------|------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|----------------------|----------------------|

| ITRIM5       | ITRIM4                                                           | ITRIM3                                                                    | ITRIM2                                                              | ITRIM1                                                                                   | ITRIM0                   | IRNG1 <sup>(2)</sup> | IRNG0 <sup>(2)</sup> |

| bit 15       | - 1                                                              |                                                                           |                                                                     | 1                                                                                        | 1                        |                      | bit                  |

|              |                                                                  |                                                                           |                                                                     |                                                                                          |                          |                      |                      |

| U-0          | U-0                                                              | U-0                                                                       | U-0                                                                 | U-0                                                                                      | U-0                      | U-0                  | U-0                  |

| —            | —                                                                | —                                                                         | —                                                                   | —                                                                                        | —                        | —                    | —                    |

| bit 7        |                                                                  |                                                                           |                                                                     |                                                                                          |                          |                      | bit (                |

| Legend:      |                                                                  |                                                                           |                                                                     |                                                                                          |                          |                      |                      |

| R = Readab   | le bit                                                           | W = Writable                                                              | bit                                                                 | U = Unimplem                                                                             | nented bit, read         | d as '0'             |                      |

| -n = Value a | It POR                                                           | '1' = Bit is set                                                          |                                                                     | '0' = Bit is clea                                                                        | ared                     | x = Bit is unkn      | iown                 |

|              | 000001 = Mir<br>000000 = No<br>111111 = Mir<br>111110 = Mir<br>• | nimum positive<br>minal current o<br>nimum negativ<br>nimum negativ       | change from r<br>output specified<br>e change from<br>e change from | nominal current<br>nominal current<br>d by IRNG<1:0><br>nominal curren<br>nominal curren | + 2%<br>t – 2%<br>t – 4% |                      |                      |

|              |                                                                  |                                                                           |                                                                     | n nominal currer<br>n nominal currer                                                     |                          |                      |                      |

| bit 9-8      | 11 = 100 × Ba<br>10 = 10 × Bas<br>01 = Base Cu<br>00 = 1000 × B  | ase Current<br>se Current<br>Irrent Level<br>Base Current <sup>(1</sup> ) |                                                                     | bits <sup>(2)</sup>                                                                      |                          |                      |                      |

| bit 7-0      | Unimplemen                                                       | ted: Read as '                                                            | 0'                                                                  |                                                                                          |                          |                      |                      |

|              | This current range<br>Refer to the CTML                          |                                                                           |                                                                     |                                                                                          | -                        |                      |                      |

# REGISTER 23-3: CTMUICON: CTMU CURRENT CONTROL REGISTER<sup>(3)</sup>

for the current range selection values.3: Current sources are not generated when 12-Bit ADC mode is chosen. Current sources are active only when 10-Bit ADC mode is chosen.

| TABLE 30-10: | DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS |

|--------------|--------------------------------------------------|

|--------------|--------------------------------------------------|

| DC CHARACTERISTICS |        |                                                                       | Standard Ope<br>(unless other<br>Operating tem | t <b>ed)</b><br>-40°C ≤ <sup>-</sup> | <b>5.5V</b><br>5°C for Industrial<br>25°C for Extended |       |                                                                                                                                        |

|--------------------|--------|-----------------------------------------------------------------------|------------------------------------------------|--------------------------------------|--------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                        | Min.                                           | Тур. <sup>(1)</sup>                  | Max.                                                   | Units | Conditions                                                                                                                             |

|                    | VIL    | Input Low Voltage                                                     |                                                |                                      |                                                        |       |                                                                                                                                        |

| DI10               |        | I/O Pins                                                              | Vss                                            |                                      | 0.2 Vdd                                                | V     |                                                                                                                                        |

|                    | Vih    | Input High Voltage                                                    |                                                |                                      |                                                        |       |                                                                                                                                        |

| DI20               |        | I/O Pins                                                              | 0.75 VDD                                       |                                      | 5.5                                                    | V     |                                                                                                                                        |

| DI30               | ICNPU  | Change Notification Pull-up<br>Current                                | 200                                            | 375                                  | 600                                                    | μA    | VDD = 5.0V, VPIN = VSS                                                                                                                 |

| DI31               | ICNPD  | Change Notification<br>Pull-Down Current <sup>(7)</sup>               | 175                                            | 400                                  | 625                                                    | μA    | VDD = 5.0V, VPIN = VDD                                                                                                                 |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                |                                                |                                      |                                                        |       |                                                                                                                                        |

| DI50               |        | I/O Pins                                                              | -100                                           | -                                    | 100                                                    | nA    | $Vss \le VPIN \le VDD,$ pin at high-impedance                                                                                          |

| DI55               |        | MCLR                                                                  | -700                                           |                                      | 700                                                    | nA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                               |

| DI56               |        | OSC1                                                                  | -200                                           | _                                    | 200                                                    | nA    | $\label{eq:VSS} \begin{split} &VSS \leq V \text{PIN} \leq V \text{DD}, \\ &XT \text{ and } HS \text{ modes} \end{split}$               |

| Dl60a              | licl   | Input Low Injection Current                                           | 0                                              | _                                    | <sub>-5</sub> (4,6)                                    |       | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP and RB7                                                                         |

| DI60b              | ІІСН   | Input High Injection Current                                          | 0                                              | —                                    | +5 <sup>(5,6)</sup>                                    | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP, RB7 and all 5V<br>tolerant pins <sup>(5)</sup>                                 |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | <sub>-20</sub> (7)                             | _                                    | +20(7)                                                 |       | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from all<br>I/O pins<br>(   IICL  +   IICH   ) $\leq \sum$ IICT |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

- 5: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 6: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 7: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

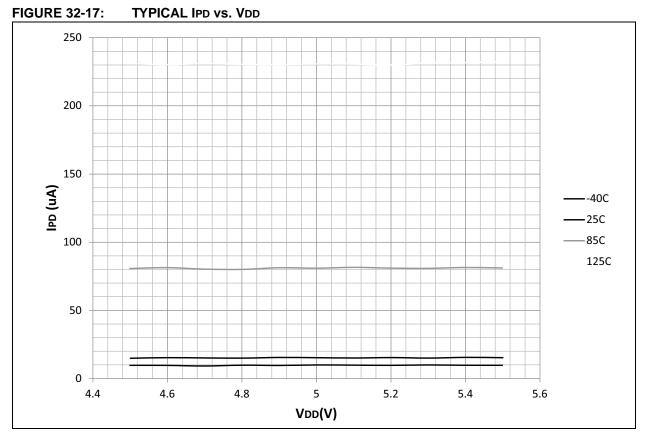

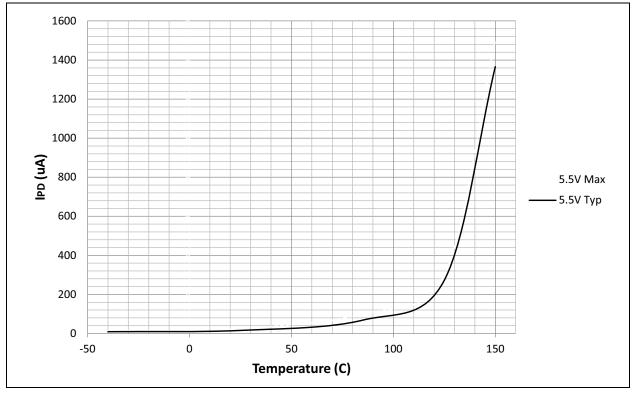

## 32.4 IPD

© 2013-2016 Microchip Technology Inc.

# dsPIC33EVXXXGM00X/10X FAMILY

# FIGURE 33-15: **TYPICAL/MAXIMUM** ∆IwDT vs. **TEMPERATURE** 12 10 8 IPD (NA) 6 5.5V Max <del>-</del> 5.5V Typ 4 2 0 -50 0 50 100 150 **Temperature (C)**

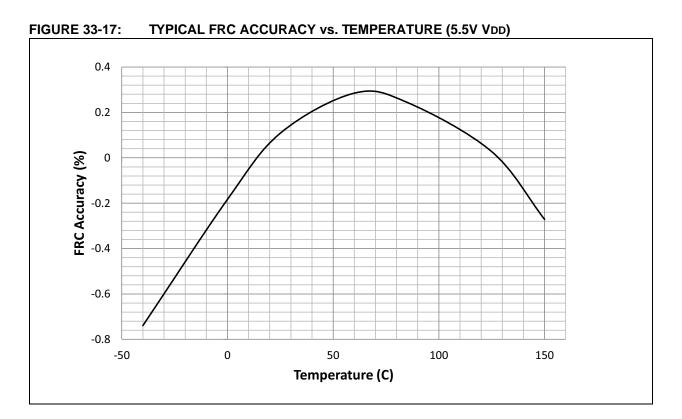

# 33.5 FRC

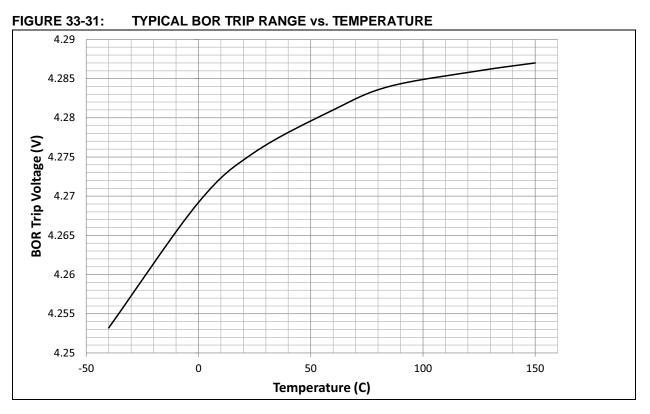

## 33.12 VBOR

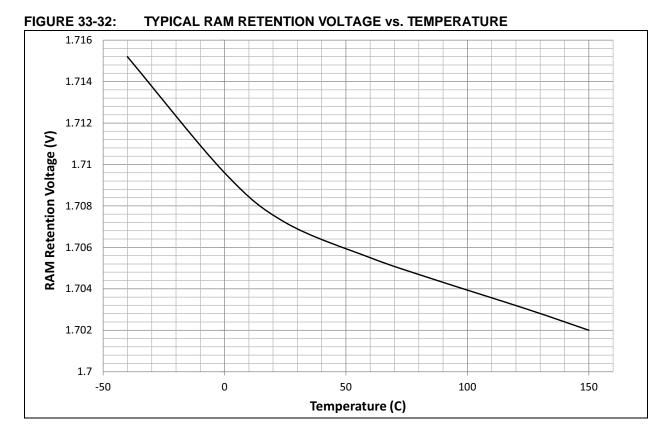

## 33.13 RAM Retention

© 2013-2016 Microchip Technology Inc.

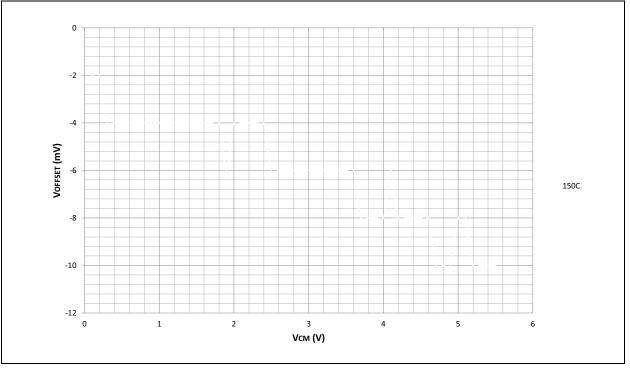

## 33.14 Comparator Op Amp Offset

## FIGURE 33-33: TYPICAL COMPARATOR OFFSET vs. Vcm

## 34.2 Package Details

The following sections give the technical details of the packages.

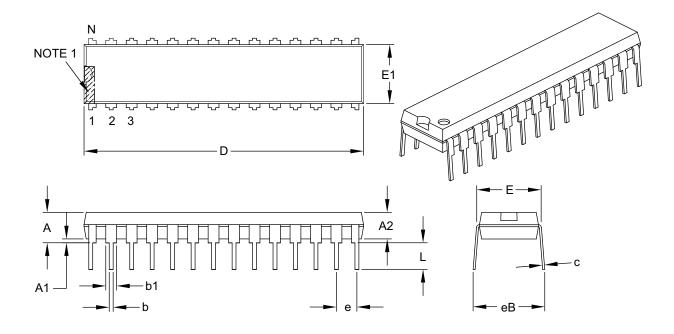

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units                   |       | INCHES   |       |

|----------------------------|-------------------------|-------|----------|-------|

|                            | <b>Dimension Limits</b> | MIN   | NOM      | MAX   |

| Number of Pins             | N                       |       | 28       | •     |

| Pitch                      | e                       |       | .100 BSC |       |

| Top to Seating Plane       | A                       | -     | -        | .200  |

| Molded Package Thickness   | A2                      | .120  | .135     | .150  |

| Base to Seating Plane      | A1                      | .015  | -        | -     |

| Shoulder to Shoulder Width | E                       | .290  | .310     | .335  |

| Molded Package Width       | E1                      | .240  | .285     | .295  |

| Overall Length             | D                       | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L                       | .110  | .130     | .150  |

| Lead Thickness             | С                       | .008  | .010     | .015  |

| Upper Lead Width           | b1                      | .040  | .050     | .070  |

| Lower Lead Width           | b                       | .014  | .018     | .022  |

| Overall Row Spacing §      | eB                      | _     | -        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

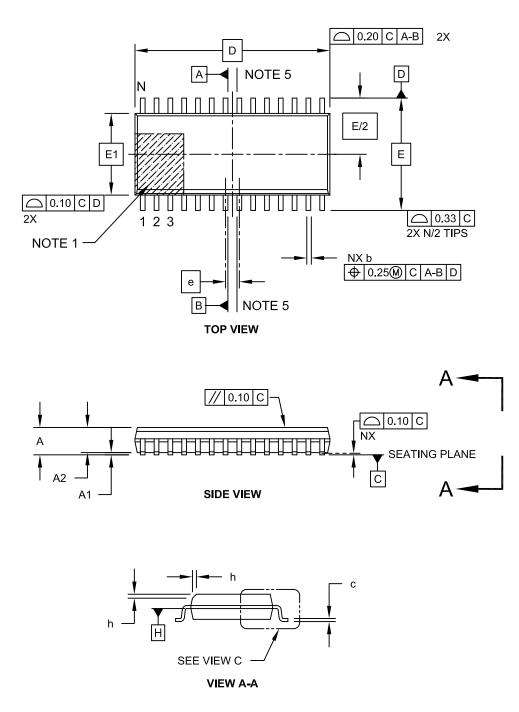

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

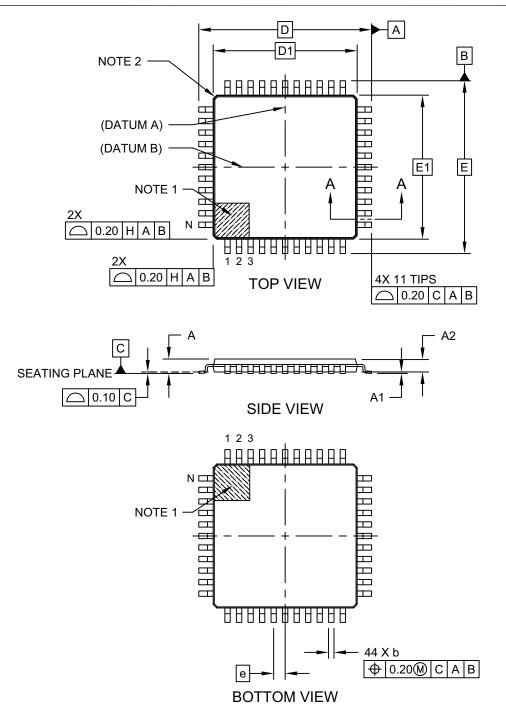

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

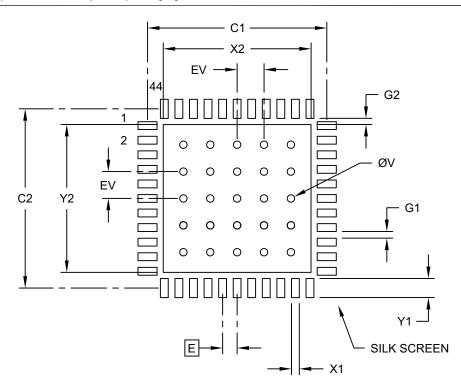

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                  | Ν               | <b>IILLIMETER</b> | S    |      |

|----------------------------------|-----------------|-------------------|------|------|

| Dimension                        | MIN             | NOM               | MAX  |      |

| Contact Pitch                    | Contact Pitch E |                   |      |      |

| Optional Center Pad Width        | X2              |                   |      | 6.60 |

| Optional Center Pad Length       | Y2              |                   |      | 6.60 |

| Contact Pad Spacing              | C1              |                   | 8.00 |      |

| Contact Pad Spacing              | C2              |                   | 8.00 |      |

| Contact Pad Width (X44)          | X1              |                   |      | 0.35 |

| Contact Pad Length (X44)         | Y1              |                   |      | 0.85 |

| Contact Pad to Contact Pad (X40) | G1              | 0.30              |      |      |

| Contact Pad to Center Pad (X44)  | G2              | 0.28              |      |      |

| Thermal Via Diameter             | V               |                   | 0.33 |      |

| Thermal Via Pitch                | EV              |                   | 1.20 |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

## ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

06/23/16