Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm004t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

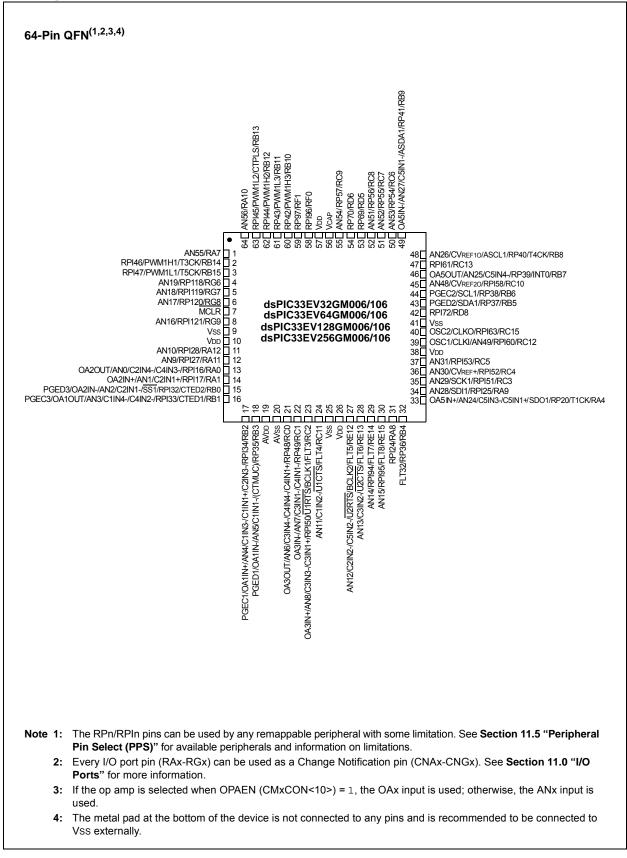

### Pin Diagrams (Continued)

## TABLE 4-33: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX02 DEVICES

|             |       |        |        |        |        |        |        |       |       |       |       |       |                   |       |            |       |       | · · · · · · · · · · · · · · · · · · · |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------------------|-------|------------|-------|-------|---------------------------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4             | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets                         |

| TRISA       | 0E00  | _      | —      | _      | —      | —      | —      | —     | _     | _     | _     | _     |                   | -     | TRISA<4:0> | >     |       | DF9F                                  |

| PORTA       | 0E02  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |                   |       | RA<4:0>    |       |       | 0000                                  |

| LATA        | 0E04  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA<4:0>         |       |            |       | 0000  |                                       |

| ODCA        | 0E06  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ODCA<4:0>         |       |            | 0000  |       |                                       |

| CNENA       | 0E08  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |                   | (     | CNIEA<4:0  | >     |       | 0000                                  |

| CNPUA       | 0E0A  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |                   | C     | NPUA<4:0   | >     |       | 0000                                  |

| CNPDA       | 0E0C  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |                   | C     | NPDA<4:0   | >     |       | 0000                                  |

| ANSELA      | 0E0E  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ANSA4 — ANSA<2:0> |       |            | 1813  |       |                                       |

| SR1A        | 0E10  | _      | —      | _      | _      | _      | _      | _     | _     | —     | _     | _     | SR1A4             | _     | —          | —     | —     | 0000                                  |

| SR0A        | 0E12  | _      | _      | _      | —      | —      | -      | —     |       | _     | _     |       | SR0A4             | _     | _          | -     | _     | 0000                                  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-------------------------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E14  |        | TRISB<15:0> F           |        |        |        |        |       |           |       |       | FFFF  |       |       |       |       |       |               |

| PORTB       | 0E16  |        | RB<15:0> xx             |        |        |        |        |       |           |       |       | xxxx  |       |       |       |       |       |               |

| LATB        | 0E18  |        | LATB<15:0> xxx          |        |        |        |        |       |           |       | xxxx  |       |       |       |       |       |       |               |

| ODCB        | 0E1A  |        |                         |        |        |        |        |       | ODCB<15   | :0>   |       |       |       |       |       |       |       | 0000          |

| CNENB       | 0E1C  |        |                         |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1E  |        |                         |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E20  |        |                         |        |        |        |        |       | CNPDB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| ANSELB      | 0E22  |        | ANSB<9:7> ANSB<3:0> 038 |        |        |        |        |       |           |       | 038F  |       |       |       |       |       |       |               |

| SR1B        | 0E24  |        | _                       | _      | _      |        |        |       | SR1B<9:7> |       | _     |       | SR1B4 | —     | _     | —     |       | 0000          |

| SR0B        | 0E26  | _      | —                       | _      | _      | _      | _      | :     | SR0B<9:7> |       | _     | _     | SR0B4 | _     | -     | _     | _     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | SLEEP: Wake-up from Sleep Flag bit     |

|-------|----------------------------------------|

|       | 1 = Device has been in Sleep mode      |

|       | 0 = Device has not been in Sleep mode  |

| bit 2 | IDLE: Wake-up from Idle Flag bit       |

|       | 1 = Device was in Idle mode            |

|       | 0 = Device was not in Idle mode        |

| bit 1 | BOR: Brown-out Reset Flag bit          |

|       | 1 = A Brown-out Reset has occurred     |

|       | 0 = A Brown-out Reset has not occurred |

| bit 0 | POR: Power-on Reset Flag bit           |

|       | 1 = A Power-on Reset has occurred      |

|       | 0 = A Power-on Reset has not occurred  |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0           | U-0                  | U-0                                                                                                      | U-0            | U-0                                | U-0   | U-0             | U-0   |  |  |  |  |  |

|---------------|----------------------|----------------------------------------------------------------------------------------------------------|----------------|------------------------------------|-------|-----------------|-------|--|--|--|--|--|

| —             | _                    | _                                                                                                        | —              | —                                  | _     | _               | _     |  |  |  |  |  |

| bit 15        |                      |                                                                                                          |                |                                    |       |                 | bit 8 |  |  |  |  |  |

| r             |                      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

| U-0           | U-0                  | U-0                                                                                                      | U-0            | R-1                                | R-1   | R-1             | R-1   |  |  |  |  |  |

|               |                      | <u> </u>                                                                                                 | —              |                                    | LSTCH | l<3:0>          |       |  |  |  |  |  |

| bit 7         |                      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

| r             |                      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

| Legend:       |                      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

| R = Readabl   | le bit               | W = Writable                                                                                             | bit            | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |  |  |

| -n = Value at | t POR                | '1' = Bit is set                                                                                         |                | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |  |  |  |  |

|               |                      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

| bit 15-4      | Unimplemen           | ted: Read as '                                                                                           | 0'             |                                    |       |                 |       |  |  |  |  |  |

| bit 3-0       | LSTCH<3:0>           | : Last DMAC C                                                                                            | hannel Active  | Status bits                        |       |                 |       |  |  |  |  |  |

|               |                      | MA transfer has                                                                                          | s occurred sin | ce system Res                      | set   |                 |       |  |  |  |  |  |

|               | 1110 <b>= Rese</b> i | rved                                                                                                     |                |                                    |       |                 |       |  |  |  |  |  |

|               | •                    |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

|               | •                    |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

|               | 0100 = Reserved      |                                                                                                          |                |                                    |       |                 |       |  |  |  |  |  |

|               | 0100                 |                                                                                                          | as handled by  | Channel 3                          |       |                 |       |  |  |  |  |  |

|               |                      | 0011 = Last data transfer was handled by Channel 3<br>0010 = Last data transfer was handled by Channel 2 |                |                                    |       |                 |       |  |  |  |  |  |

|               |                      | 0001 = Last data transfer was handled by Channel 1                                                       |                |                                    |       |                 |       |  |  |  |  |  |

|               |                      | lata transfer wa                                                                                         | -              |                                    |       |                 |       |  |  |  |  |  |

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK2R6                                            | SCK2R5                                                                           | SCK2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SCK2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SCK2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SCK2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCK2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDI2R6                                            | SDI2R5                                                                           | SDI2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SDI2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SDI2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDI2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit                                               | W = Writable                                                                     | bit                                                                                                                                                                                                                                                                                                                                                                                                           | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>d as</b> '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| POR                                               | '1' = Bit is set                                                                 | :                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •<br>•<br>000000001 =<br>00000000 =               | Input tied to Cl                                                                 | MP1<br>SS                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (see Table 1 <sup>-</sup><br>10110101 =<br>•<br>• | 1-2 for input pin<br>Input tied to RI                                            | selection num<br>PI181                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | esponding RPn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   | SCK2R6         R/W-0         SDI2R6         e bit         POR         SCK2R<7:0: | SCK2R6         SCK2R5           R/W-0         R/W-0           SDI2R6         SDI2R5           e bit         W = Writable           POR         '1' = Bit is set           SCK2R<7:0>: Assign SPI2           (see Table 11-2 for input pin           10110101 = Input tied to RI           .           00000001 = Input tied to VS           SDI2R<7:0>: Assign SPI2 E           (see Table 11-2 for input pin | SCK2R6         SCK2R5         SCK2R4           R/W-0         R/W-0         R/W-0           SDI2R6         SDI2R5         SDI2R4           e bit         W = Writable bit           POR         '1' = Bit is set           SCK2R<7:0>: Assign SPI2 Clock Input (S<br>(see Table 11-2 for input pin selection num<br>10110101 = Input tied to RPI181           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         .           .         . | SCK2R6         SCK2R5         SCK2R4         SCK2R3           R/W-0         R/W-0         R/W-0         R/W-0           SDI2R6         SDI2R5         SDI2R4         SDI2R3           e bit         W = Writable bit         U = Unimpler           POR         '1' = Bit is set         '0' = Bit is cle           SCK2R<7:0>:         Assign SPI2 Clock Input (SCK2) to the Correct (see Table 11-2 for input pin selection numbers)           10110101 = Input tied to RPI181         .           .         .           00000001 = Input tied to CMP1           00000001 = Input tied to Vss           SDI2R<7:0>: Assign SPI2 Data Input (SDI2) to the Correct (see Table 11-2 for input pin selection numbers)           10110101 = Input tied to RPI181           .           .           . | SCK2R6         SCK2R5         SCK2R4         SCK2R3         SCK2R2           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0           SDI2R6         SDI2R5         SDI2R4         SDI2R3         SDI2R2           e bit         W = Writable bit         U = Unimplemented bit, read           POR         '1' = Bit is set         '0' = Bit is cleared           SCK2R<7:0>: Assign SPI2 Clock Input (SCK2) to the Corresponding R (see Table 11-2 for input pin selection numbers)           10110101 = Input tied to RPI181           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           .           . | SCK2R6         SCK2R5         SCK2R4         SCK2R3         SCK2R2         SCK2R1           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0           SDI2R6         SDI2R5         SDI2R4         SDI2R3         SDI2R2         SDI2R1           e bit         W = Writable bit         U = Unimplemented bit, read as '0'         POR         '1' = Bit is set         '0' = Bit is cleared         x = Bit is unkr           SCK2R         Sasign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)         10110101 = Input tied to RPI181         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         .         .           .         .         .         .         . |

## REGISTER 11-10: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

NOTES:

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

These modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 and Timer4/5 operate in the following three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules

- ADC1 Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. The T3CON and T5CON registers are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw). Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, the T3CON and T5CON control bits are ignored. Only the T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

Block diagrams for the Type B and Type C timers are shown in Figure 13-1 and Figure 13-2, respectively.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, Timer3, Timer4 and Timer5 can trigger a DMA data transfer.

### REGISTER 14-5: DMTCNTL: DEADMAN TIMER COUNT REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0 |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-----------------|-------------------|-------|--|

|                 |       |                  | COUNT | ER<15:8>                                |                 |                   |       |  |

| bit 15          |       |                  |       |                                         |                 |                   | bit 8 |  |

|                 |       |                  |       |                                         |                 |                   |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0 |  |

|                 |       |                  | COUN  | ΓER<7:0>                                |                 |                   |       |  |

| bit 7           |       |                  |       |                                         |                 |                   | bit 0 |  |