Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

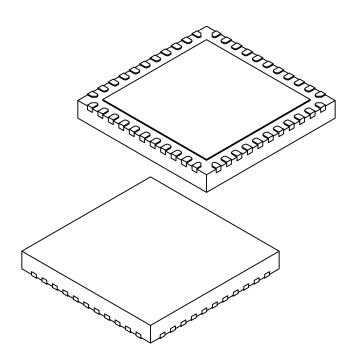

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm006-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*, which are available from the Microchip web site (www.microchip.com). The following documents should be considered as the general reference for the operation of a particular module or device feature:

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "dsPIC33E/PIC24E Program Memory" (DS70000613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70000600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70000598)

- "Timers" (DS70362)

- "CodeGuard™ Intermediate Security" (DS70005182)

- "Deadman Timer (DMT)" (DS70005155)

- "Input Capture" (DS70000352)

- "Output Compare" (DS70005157)

- "High-Speed PWM"(DS70645)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

- "Serial Peripheral Interface (SPI)" (DS70005185)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "Enhanced Controller Area Network (ECAN™)"(DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70000357)

- "Device Configuration" (DS70000618)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

- "Single-Edge Nibble Transmission (SENT) Module" (DS70005145)

#### **CPU Control Registers** 3.6

| R/W-0                 | R/W-0                                   | R/W-0                                | R/W-0             | R/C-0                   | R/C-0                        | R-0                           | R/W-0          |

|-----------------------|-----------------------------------------|--------------------------------------|-------------------|-------------------------|------------------------------|-------------------------------|----------------|

| 0A                    | ОВ                                      | SA <sup>(3)</sup>                    | SB <sup>(3)</sup> | OAB                     | SAB                          | DA                            | DC             |

| bit 15                | 00                                      | 0,1                                  | 08                | 0,18                    | 0,10                         | BA                            | bit 8          |

|                       |                                         |                                      |                   |                         |                              |                               | bit (          |

| R/W-0                 | R/W-0                                   | R/W-0                                | R-0               | R/W-0                   | R/W-0                        | R/W-0                         | R/W-0          |

| IPL2 <sup>(1,2)</sup> | ) IPL1 <sup>(1,2)</sup>                 | IPL0 <sup>(1,2)</sup>                | RA                | N                       | OV                           | Z                             | С              |

| bit 7                 |                                         |                                      |                   |                         |                              |                               | bit (          |

| Levend                |                                         |                                      | - h:4             |                         |                              |                               |                |

| Legend:               |                                         | C = Clearable                        |                   |                         | nonted bit was               |                               |                |

| R = Reada             |                                         | W = Writable                         |                   | -                       | mented bit, rea              |                               |                |

| -n = Value            | at POR                                  | '1' = Bit is set                     |                   | '0' = Bit is cle        | ared                         | x = Bit is unkr               | nown           |

| bit 15                | OA: Accumu                              | lator A Overflo                      | w Status bit      |                         |                              |                               |                |

|                       | 1 = Accumul                             | ator A has over                      | flowed            |                         |                              |                               |                |

|                       | 0 = Accumul                             | ator A has not                       | overflowed        |                         |                              |                               |                |

| bit 14                | OB: Accumu                              | lator B Overflo                      | w Status bit      |                         |                              |                               |                |

|                       |                                         | ator B has over                      |                   |                         |                              |                               |                |

|                       |                                         | ator B has not o                     |                   |                         |                              |                               |                |

| bit 13                | SA: Accumu                              | lator A Saturati                     | on 'Sticky' Sta   | atus bit <sup>(3)</sup> |                              |                               |                |

|                       |                                         | ator A is satura<br>ator A is not sa |                   | en saturated at         | some time                    |                               |                |

| bit 12                | SB: Accumu                              | lator B Saturati                     | on 'Sticky' Sta   | atus bit <sup>(3)</sup> |                              |                               |                |

|                       |                                         | ator B is satura<br>ator B is not sa |                   | en saturated at         | some time                    |                               |                |

| bit 11                | <b>0AB:</b> OA    (                     | OB Combined A                        | Accumulator C     | Overflow Status         | bit                          |                               |                |

|                       |                                         | ator A or B has                      |                   |                         |                              |                               |                |

|                       | 0 = Accumul                             | ator A and B ha                      | ave not overflo   | owed                    |                              |                               |                |

| bit 10                | <b>SAB:</b> SA    S                     | B Combined A                         | ccumulator 'S     | ticky' Status bit       |                              |                               |                |

|                       |                                         | ator A or B is s<br>ator A and B ha  |                   |                         | ed at some tim               | ie                            |                |

| bit 9                 | DA: DO Loop                             | Active bit                           |                   |                         |                              |                               |                |

|                       |                                         | s in progress<br>s not in progres    | s                 |                         |                              |                               |                |

| bit 8                 | -                                       | U Half Carry/B                       |                   |                         |                              |                               |                |

|                       |                                         | •                                    |                   | (for byte-sized o       | data) or 8 <sup>th</sup> Iow | order bit (for wo             | ord-sized data |

|                       |                                         | sult occurred                        | 11-               |                         | ,                            |                               |                |

|                       |                                         |                                      |                   | bit (for byte-siz       | ed data) or 8 <sup>ti</sup>  | <sup>h</sup> low-order bit (1 | for word-size  |

|                       | data) of                                | the result occu                      | rred              |                         |                              |                               |                |

|                       | The IPL<2:0> bits<br>Level. The value i |                                      |                   |                         |                              |                               |                |

|                       | The IPL<2:0> Sta                        | -                                    |                   |                         |                              |                               |                |

|                       | $\Delta$ data write to the              |                                      | -                 |                         | -                            | -                             | nd SB or by    |

3: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

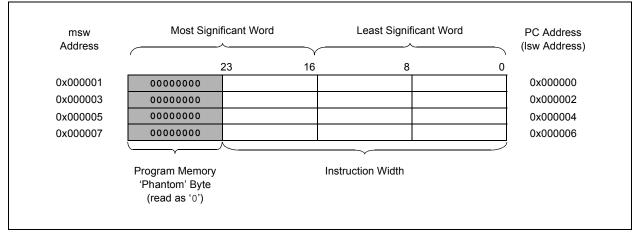

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-5).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with the Data Memory Space Addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EVXXXGM00X/10X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000 of Flash memory, with the actual address for the start of code at address, 0x000002 of Flash memory.

For more information on the Interrupt Vector Tables, see **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

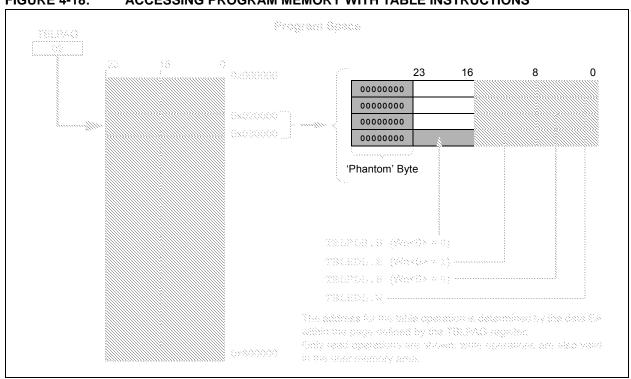

#### 4.7.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through the Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. The TBLRDL and TBLWTL instructions access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space. Accessing the program memory with table instructions is shown in Figure 4-18.

#### FIGURE 4-18: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| R/W-0          | R/W-0                                     | U-0                                  | U-0             | R/W-0                        | U-0              | R/W-0            | R/W-0          |

|----------------|-------------------------------------------|--------------------------------------|-----------------|------------------------------|------------------|------------------|----------------|

| TRAPF          | R IOPUWR                                  |                                      | —               | VREGSF                       |                  | CM               | VREGS          |

| bit 15         |                                           |                                      |                 |                              |                  |                  | bit 8          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| R/W-0          | R/W-0                                     | R/W-0                                | R/W-0           | R/W-0                        | R/W-0            | R/W-1            | R/W-1          |

| EXTR           | SWR                                       | SWDTEN <sup>(2)</sup>                | WDTO            | SLEEP                        | IDLE             | BOR              | POR            |

| bit 7          |                                           |                                      |                 |                              |                  |                  | bit (          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Legend:        |                                           |                                      |                 |                              |                  |                  |                |

| R = Reada      |                                           | W = Writable                         | oit             | •                            | nented bit, read | d as '0'         |                |

| -n = Value     | at POR                                    | '1' = Bit is set                     |                 | '0' = Bit is cle             | ared             | x = Bit is unk   | nown           |

| 6:4 <i>4 C</i> |                                           | Deast Flag bit                       |                 |                              |                  |                  |                |

| bit 15         |                                           | D Reset Flag bit<br>onflict Reset ha | e occurrod      |                              |                  |                  |                |

|                |                                           | onflict Reset ha                     |                 | ed                           |                  |                  |                |

| bit 14         | •                                         | egal Opcode or                       |                 |                              | ess Reset Flag   | a bit            |                |

|                |                                           | al Opcode detec                      |                 | •                            | -                |                  | ter used as ar |

|                |                                           | Pointer caused                       |                 | · · · · · · · · · · · ·      |                  |                  |                |

|                |                                           | I Opcode Rese                        |                 | zed W Register               | Reset has not    | occurred         |                |

| bit 13-12      | -                                         | nted: Read as '                      |                 |                              |                  |                  |                |

| bit 11         |                                           | ash Voltage Reg                      |                 |                              | o bit            |                  |                |

|                |                                           | Itage regulator i                    |                 | •                            | ing Sleep mode   | 2                |                |

| bit 10         |                                           | nted: Read as '                      | -               |                              | ing cleep mout   |                  |                |

| bit 9          | -                                         | ration Mismatch                      |                 |                              |                  |                  |                |

|                | •                                         | uration Mismatc                      | •               | occurred.                    |                  |                  |                |

|                |                                           | uration Mismato                      |                 |                              |                  |                  |                |

| bit 8          | VREGS: Volt                               | age Regulator S                      | Standby Durii   | ng Sleep bit                 |                  |                  |                |

|                |                                           | regulator is activ                   |                 |                              |                  |                  |                |

|                | •                                         | regulator goes i                     |                 | mode during Sle              | еер              |                  |                |

| bit 7          |                                           | nal Reset (MCL                       | ,               |                              |                  |                  |                |

|                |                                           | Clear (pin) Res<br>Clear (pin) Res   |                 |                              |                  |                  |                |

| bit 6          |                                           | are RESET (Instr                     |                 |                              |                  |                  |                |

|                |                                           | instruction has                      |                 |                              |                  |                  |                |

|                | 0 = A reset                               | instruction has                      | not been exe    | ecuted                       |                  |                  |                |

| bit 5          | SWDTEN: So                                | oftware Enable/                      | Disable of W    | DT bit <b><sup>(2)</sup></b> |                  |                  |                |

|                | 1 = WDT is e                              |                                      |                 |                              |                  |                  |                |

|                | 0 = WDT is d                              |                                      |                 |                              |                  |                  |                |

| bit 4          |                                           | hdog Timer Tim                       | -               | it                           |                  |                  |                |

|                |                                           | e-out has occur<br>e-out has not oc  |                 |                              |                  |                  |                |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Note 1:        | All of the Reset sta<br>cause a device Re |                                      | set or cleare   | a in software. S             | etting one of th | ese bits in soft | ware does not  |

| 2:             | If the FWDTEN<1                           |                                      | n hits are '1 1 | ' (unprogramm                | ed) the WDT is   | always enable    | od rogardlaar  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-1        | R/W-0         | R/W-0                                 | U-0          | U-0              | U-0              | U-0             | R/W-0  |

|--------------|---------------|---------------------------------------|--------------|------------------|------------------|-----------------|--------|

| GIE          | DISI          | SWTRAP                                |              |                  | —                | —               | AIVTEN |

| bit 15       |               |                                       |              |                  |                  |                 | bit 8  |

|              |               |                                       |              |                  |                  |                 |        |

| U-0          | U-0           | U-0                                   | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —            | —             | —                                     | _            | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7        |               |                                       |              |                  |                  |                 | bit 0  |

|              |               |                                       |              |                  |                  |                 |        |

| Legend:      |               |                                       |              |                  |                  |                 |        |

| R = Readab   | le bit        | W = Writable b                        | oit          | •                | mented bit, read | as '0'          |        |

| -n = Value a | t POR         | '1' = Bit is set                      |              | '0' = Bit is cle | eared            | x = Bit is unki | nown   |

|              |               |                                       |              |                  |                  |                 |        |

| bit 15       |               | Interrupt Enable                      |              |                  |                  |                 |        |

|              |               | s and associated<br>s are disabled, b |              |                  |                  |                 |        |

| bit 14       |               | Instruction Status                    | •            | Suil enabled     |                  |                 |        |

| DIL 14       |               | struction is active                   |              |                  |                  |                 |        |

|              |               | struction is not a                    | -            |                  |                  |                 |        |

| bit 13       | SWTRAP: S     | Software Trap Sta                     | atus bit     |                  |                  |                 |        |

|              |               | e trap is enabled                     |              |                  |                  |                 |        |

|              | 0 = Software  | e trap is disabled                    |              |                  |                  |                 |        |

| bit 12-9     | Unimpleme     | nted: Read as 'o                      | כ'           |                  |                  |                 |        |

| bit 8        | AIVTEN: Alt   | ernate Interrupt                      | Vector Table | is Enabled bit   |                  |                 |        |

|              | 1 = AIVT is e |                                       |              |                  |                  |                 |        |

| L:1 7 0      | 0 = AIVT is 0 |                                       | - 1          |                  |                  |                 |        |

| bit 7-3      | -             | nted: Read as '                       |              |                  |                  |                 |        |

| bit 2        |               | ternal Interrupt 2                    | •            | t Polarity Selec | ct bit           |                 |        |

|              |               | on negative edg                       |              |                  |                  |                 |        |

| bit 1        | •             | ternal Interrupt 1                    |              | t Polarity Selec | rt bit           |                 |        |

|              |               | on negative edg                       | •            |                  |                  |                 |        |

|              |               | on positive edg                       |              |                  |                  |                 |        |

| bit 0        | INTOEP: Ext   | ternal Interrupt 0                    | Edge Detec   | t Polarity Selec | ct bit           |                 |        |

|              |               | on negative edg                       |              |                  |                  |                 |        |

|              | 0 = Interrupt | on positive edg                       | е            |                  |                  |                 |        |

|              |               |                                       |              |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

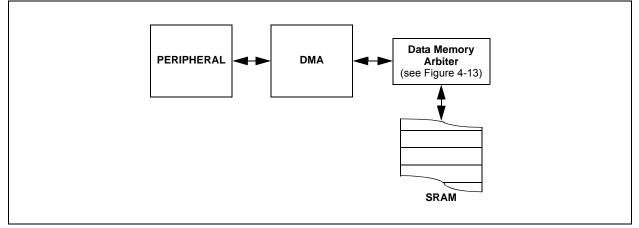

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| R/W-0         | R/W-0                                | R/W-0                | R/W-0                | R/W-0                             | R/W-0            | R/W-0           | R/W-1          |

|---------------|--------------------------------------|----------------------|----------------------|-----------------------------------|------------------|-----------------|----------------|

| ROI           | DOZE2 <sup>(3)</sup>                 | DOZE1 <sup>(3)</sup> | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>            | FRCDIV2          | FRCDIV1         | FRCDIV0        |

| bit 15        |                                      | •                    | -                    | -                                 |                  | •               | bit 8          |

|               |                                      |                      | DAMO                 | D/M/ 0                            |                  | R/W-0           | DAMA           |

| R/W-0         | R/W-0                                | U-0                  | R/W-0                | R/W-0                             | R/W-0            |                 | R/W-0          |

| PLLPOST1      | PLLPOST0                             | —                    | PLLPRE4              | PLLPRE3                           | PLLPRE2          | PLLPRE1         | PLLPRE0        |

| bit 7         |                                      |                      |                      |                                   |                  |                 | bit C          |

| Legend:       |                                      |                      |                      |                                   |                  |                 |                |

| R = Readable  | bit                                  | W = Writable         | bit                  | U = Unimpler                      | nented bit, read | l as '0'        |                |

| -n = Value at | POR                                  | '1' = Bit is set     |                      | '0' = Bit is cle                  | ared             | x = Bit is unkr | nown           |

| bit 15        |                                      | on Interrupt b       | i+                   |                                   |                  |                 |                |

|               |                                      | will clear the E     |                      |                                   |                  |                 |                |

|               |                                      | have no effect       |                      | N bit                             |                  |                 |                |

| bit 14-12     | •                                    | Processor Clo        |                      |                                   |                  |                 |                |

|               | 111 = FCY div                        |                      |                      |                                   |                  |                 |                |

|               | 110 = FCY div                        |                      |                      |                                   |                  |                 |                |

|               | 101 = FCY div                        |                      |                      |                                   |                  |                 |                |

|               | 100 = FCY div<br>011 = FCY div       |                      |                      |                                   |                  |                 |                |

|               | 010 = FCY div                        |                      |                      |                                   |                  |                 |                |

|               | 001 = Fcy div                        |                      |                      |                                   |                  |                 |                |

|               |                                      | vided by 1 (def      |                      |                                   |                  |                 |                |

| bit 11        |                                      | e Mode Enable        |                      |                                   |                  |                 |                |

|               |                                      |                      |                      | tween the peri<br>atio are forced |                  | nd the process  | or clocks      |

| bit 10-8      | FRCDIV<2:0>                          | -: Internal Fast     | RC Oscillator        | Postscaler bit                    | S                |                 |                |

|               | 111 <b>= FRC d</b> i                 | vided by 256         |                      |                                   |                  |                 |                |

|               | 110 <b>= FRC di</b>                  |                      |                      |                                   |                  |                 |                |

|               | 101 = FRC di                         | •                    |                      |                                   |                  |                 |                |

|               | 100 = FRC di<br>011 = FRC di         |                      |                      |                                   |                  |                 |                |

|               | 010 = FRC di                         |                      |                      |                                   |                  |                 |                |

|               |                                      | vided by 2 (de       | fault)               |                                   |                  |                 |                |

|               | 000 <b>= FRC di</b>                  | •                    |                      |                                   |                  |                 |                |

| bit 7-6       | PLLPOST<1:                           | 0>: PLL VCO          | Output Divide        | r Select bits (al                 | so denoted as    | 'N2', PLL posts | caler)         |

|               | 11 = Output d                        |                      |                      |                                   |                  |                 |                |

|               | 10 = Reserve<br>01 = Output d        |                      |                      |                                   |                  |                 |                |

|               | 00 = Output d                        |                      |                      |                                   |                  |                 |                |

| bit 5         |                                      | ted: Read as '       | 0'                   |                                   |                  |                 |                |

| Note 1: Th    | is bit is cleared v                  | when the ROI         | bit is set and a     | an interrupt occ                  | urs.             |                 |                |

| <b>2:</b> Th  | is register resets                   | s only on a Pov      | wer-on Reset         | (POR).                            |                  |                 |                |

|               | )ZE<2:0> bits ca<br>)ZE<2:0> are igi |                      | en to when th        | e DOZEN bit is                    | clear. If DOZE   | N = 1, any wri  | tes to         |

|               | o DOZEN bit cou                      |                      | 075-2.05 -           |                                   | 2.0 > - 0.00 on  | attempt by up   | or ooftwara to |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode, with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

Note: If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

## 17.0 HIGH-SPEED PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM Generators

- Two PWM Outputs per PWM Generator

- Individual Period and Duty Cycle for each PWM Pair

- Duty Cycle, Dead Time, Phase Shift and Frequency Resolution of 8.32 ns

- Independent Fault and Current-Limit Inputs for Six PWM Outputs

- Redundant Output

- Center-Aligned PWM mode

- Output Override Control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for Input Clock

- PWMxL and PWMxH Output Pin Swapping

- Independent PWM Frequency, Duty Cycle and Phase-Shift Changes for each PWM Generator

- Dead-Time Compensation

- Enhanced Leading-Edge Blanking (LEB) Functionality

- Frequency Resolution Enhancement

- PWM Capture Functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns at 60 MIPS.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on the master time base.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin, that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 17-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 17.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs as follows:

- FLT1 and FLT2, available on 28-pin, 44-pin and 64-pin packages, which are remappable using the PPS feature

- FLT3, available on 44-pin and 64-pin packages, which is available as a fixed pin

- FLT4-FLT8, available on 64-pin packages, which are available as fixed pins

- · FLT32 is available on a fixed pin on all devices

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 17.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

**Note:** The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCONx<1:0>), regardless of the state of FLT32.

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C<sup>TM</sup>)" (DS70000195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains one Inter-Integrated Circuit (I<sup>2</sup>C) module, I2C1.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has the following 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave modes of Operation

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly

- · Support for Address Bit Masking up to Lower 7 Bits

- I<sup>2</sup>C Slave Enhancements:

- SDAx hold time selection of SMBus (300 ns or 150 ns)

- Start/Stop bit interrupt enables

Figure 19-1 shows a block diagram of the I<sup>2</sup>C module.

## 19.1 I<sup>2</sup>C Baud Rate Generator

The Baud Rate Generator (BRG) used for I<sup>2</sup>C mode operation is used to set the SCL clock frequency for 100 kHz, 400 kHz and 1 MHz. The BRG reload value is contained in the I2CxBRG register. The BRG will automatically begin counting on a write to the I2CxTRN register.

Equation 19-1 and Equation 19-2 provide the BRG reload formula and FSCL frequency, respectively.

#### EQUATION 19-1: BRG FORMULA

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - Delay \right) \times \frac{FCY}{2} \right) - 2$$

Where:

Delay varies from 110 ns to 130 ns.

#### EQUATION 19-2: FSCL FREQUENCY

FSCL = FCY/((I2CxBRG + 2) \* 2)

## 26.2 Comparator Voltage Reference Registers

## REGISTER 26-1: CVR1CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0  | R/W-0 | U-0   | U-0   | R/W-0 | R/W-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|---------|-------|-------|

| CVREN  | CVROE | —     | _     | CVRSS | VREFSEL | —     | _     |

| bit 15 |       |       |       |       |         |       | bit 8 |

|        |       |       |       |       |         |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| _      | CVR6  | CVR5  | CVR4  | CVR3  | CVR2    | CVR1  | CVR0  |

| bit 7  |       |       |       |       |         |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | CVREN: Comparator Voltage Reference Enable bit                      |

|-----------|---------------------------------------------------------------------|

|           | 1 = Comparator voltage reference circuit is powered on              |

|           | 0 = Comparator voltage reference circuit is powered down            |

| bit 14    | CVROE: Comparator Voltage Reference Output Enable (CVREF10 Pin) bit |

|           | 1 = Voltage level is output on the CVREF10 pin                      |

|           | 0 = Voltage level is disconnected from the CVREF10 pin              |

| bit 13-12 | Unimplemented: Read as '0'                                          |

| bit 11    | CVRSS: Comparator Voltage Reference Source Selection bit            |

|           | 1 = Comparator reference source, CVRSRC = CVREF+ – AVSS             |

|           | 0 = Comparator reference source, CVRSRC = AVDD – AVSS               |

| bit 10    | VREFSEL: Voltage Reference Select bit                               |

|           | 1 = CVREFIN = CVREF+                                                |

|           | 0 = CVREFIN is generated by the resistor network                    |

| bit 9-7   | Unimplemented: Read as '0'                                          |

| bit 6-0   | CVR<6:0>: Comparator Voltage Reference Value Selection bits         |

|           | 1111111 = 127/128 x VREF input voltage                              |

|           | •                                                                   |

|           | •                                                                   |

|           | •                                                                   |

|           | 0000000 = <b>0.0 volts</b>                                          |

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EV instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into following five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the Status Flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have the following three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

| DC CHARACT       | ERISTICS            |      | (unless oth | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |         |  |  |  |

|------------------|---------------------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|--|--|--|

| Parameter<br>No. | Typ. <sup>(2)</sup> | Max. | Units       |                                                                                                                                                                                                                                                                                       | Conditions |         |  |  |  |

| Idle Current (li | dle) <sup>(1)</sup> |      |             | ·                                                                                                                                                                                                                                                                                     |            |         |  |  |  |

| DC40d            | 1.25                | 2    | mA          | -40°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC40a            | 1.25                | 2    | mA          | +25°C                                                                                                                                                                                                                                                                                 | 5.0V       | 10 MIPS |  |  |  |

| DC40b            | 1.5                 | 2.6  | mA          | +85°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC40c            | 1.5                 | 2.6  | mA          | +125°C                                                                                                                                                                                                                                                                                |            |         |  |  |  |

| DC42d            | 2.3                 | 3    | mA          | -40°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC42a            | 2.3                 | 3    | mA          | +25°C                                                                                                                                                                                                                                                                                 | 5.0)/      |         |  |  |  |

| DC42b            | 2.6                 | 3.45 | mA          | +85°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC42c            | 2.6                 | 3.85 | mA          | +125°C                                                                                                                                                                                                                                                                                |            |         |  |  |  |

| DC44d            | 6.9                 | 8    | mA          | -40°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC44a            | 6.9                 | 8    | mA          | +25°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

| DC44b            | 7.25                | 8.6  | mA          | +85°C                                                                                                                                                                                                                                                                                 |            |         |  |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

# TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                                  | Standard Op<br>(unless othe<br>Operating ter | erwise st           | a <b>ted)</b><br>e -40° | C ≤ TA ≤ | <b>W to 5.5V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------|---------------------|-------------------------|----------|-----------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                                                    | Min.                                         | Typ. <sup>(2)</sup> | Max.                    | Units    | Conditions                                                      |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                                                     | _                                            | _                   | 11                      | MHz      | See Note 3                                                      |

| SP72               | TscF                  | SCK2 Input Fall Time                                                             | _                                            |                     | _                       | ns       | See Parameter DO32 and <b>Note 4</b>                            |

| SP73               | TscR                  | SCK2 Input Rise Time                                                             | —                                            | —                   | _                       | ns       | See Parameter DO31 and <b>Note 4</b>                            |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                                                       | —                                            | _                   | _                       | ns       | See Parameter DO32 and <b>Note 4</b>                            |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                                                       | —                                            | _                   | _                       | ns       | See Parameter DO31 and <b>Note 4</b>                            |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                        | —                                            | 6                   | 20                      | ns       |                                                                 |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                     | 30                                           | _                   | _                       | ns       |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge                                       | 30                                           | _                   | _                       | ns       |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge                                        | 30                                           | —                   | _                       | ns       |                                                                 |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{\text{SS2}} \downarrow$ to SCK2 $\uparrow$ or SCK2 $\downarrow$ Input | 120                                          | —                   | _                       | ns       |                                                                 |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance                                           | 10                                           | —                   | 50                      | ns       | See Note 4                                                      |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                                                            | 1.5 Tcy + 40                                 | —                   |                         | ns       | See Note 4                                                      |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

**4:** Assumes 50 pF load on all SPI2 pins.

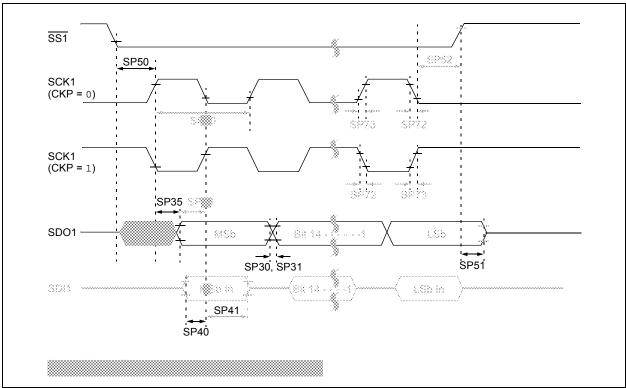

FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| АС СНА       |        | otherwi                        | se stateo<br>rature | <b>d)</b><br>-40°C ≤ | (see Note 1): 4.5V to 5.5V<br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended |       |                                                  |

|--------------|--------|--------------------------------|---------------------|----------------------|-----------------------------------------------------------------------------------------------|-------|--------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                 | Min.                | Тур.                 | Max.                                                                                          | Units | Conditions                                       |

|              |        | ADC A                          | Accuracy            | (10-Bit              | Mode)                                                                                         |       |                                                  |

| AD20b        | Nr     | Resolution                     | 1(                  | ) data bi            | ts                                                                                            | bits  |                                                  |

| AD21b        | INL    | Integral Nonlinearity          | -1.5                | _                    | +1.5                                                                                          | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD22b        | DNL    | Differential Nonlinearity      | ≥ 1                 | —                    | < 1                                                                                           | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD23b        | Gerr   | Gain Error                     | 1                   | 3                    | 6                                                                                             | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD24b        | EOFF   | Offset Error                   | 1                   | 2                    | 4                                                                                             | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD25b        | —      | Monotonicity <sup>(2)</sup>    | —                   | —                    |                                                                                               | —     | Guaranteed                                       |

|              |        | Dynamic                        | Performa            | nce (10-             | Bit Mod                                                                                       | e)    |                                                  |

| AD30b        | THD    | Total Harmonic Distortion      | _                   |                      | -64                                                                                           | dB    |                                                  |

| AD31b        | SINAD  | Signal to Noise and Distortion | 57                  | 58.5                 | _                                                                                             | dB    |                                                  |

| AD32b        | SFDR   | Spurious Free Dynamic<br>Range | 72                  | _                    | —                                                                                             | dB    |                                                  |

| AD33b        | Fnyq   | Input Signal Bandwidth         | _                   | —                    | 550                                                                                           | kHz   |                                                  |

| AD34b        | ENOB   | Effective Number of Bits       | 9.16                | 9.4                  |                                                                                               | bits  |                                                  |

### TABLE 30-56: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: The conversion result never decreases with an increase in the input voltage.

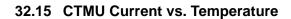

#### FIGURE 32-39: TYPICAL CTMU CURRENT (IRNG) vs. TEMPERATURE

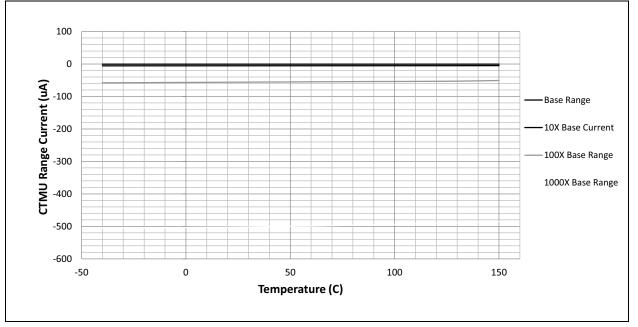

## 32.16 CTMU Temperature Forward Diode

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  |          |          |      |  |

|-------------------------|--------|----------|----------|------|--|

| Dimension               | Limits | MIN      | NOM      | MAX  |  |

| Number of Pins          | N      |          | 44       |      |  |

| Pitch                   | е      |          | 0.65 BSC |      |  |

| Overall Height          | A      | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF |          |      |  |

| Overall Width           | E      |          | 8.00 BSC |      |  |

| Exposed Pad Width       | E2     | 6.25     | 6.45     | 6.60 |  |

| Overall Length          | D      | 8.00 BSC |          |      |  |

| Exposed Pad Length      | D2     | 6.25     | 6.45     | 6.60 |  |

| Terminal Width          | b      | 0.20     | 0.30     | 0.35 |  |

| Terminal Length         | L      | 0.30     | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | К      | 0.20     | -        | -    |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2