Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | dsPIC                                                                           |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 60 MIPs                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| lumber of I/O             | 53                                                                              |

| Program Memory Size       | 32KB (11K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AAM Size                  | 4K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Oata Converters           | A/D 36x10/12b                                                                   |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type             | Surface Mount                                                                   |

| Package / Case            | 64-TQFP                                                                         |

| Supplier Device Package   | 64-TQFP (10x10)                                                                 |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm006-e-pt |

### 5.4 Error Correcting Code (ECC)

In order to improve program memory performance and durability, these devices include Error Correcting Code functionality (ECC) as an integral part of the Flash memory controller. ECC can determine the presence of single-bit errors in program data, including which bit is in error, and correct the data automatically without user intervention. ECC cannot be disabled.

When data is written to program memory, ECC generates a 7-bit Hamming code parity value for every two (24-bit) instruction words. The data is stored in blocks of 48 data bits and 7 parity bits; parity data is not memory-mapped and is inaccessible. When the data is read back, the ECC calculates the parity on it and compares it to the previously stored parity value. If a parity mismatch occurs, there are two possible outcomes:

- Single-bit errors are automatically identified and corrected on read-back. An optional device-level interrupt (ECCSBEIF) is also generated.

- Double-bit errors will generate a generic hard trap and the read data is not changed. If special exception handling for the trap is not implemented, a device Reset will also occur.

To use the single-bit error interrupt, set the ECC Single-Bit Error Interrupt Enable bit (ECCSBEIE) and configure the ECCSBEIP bits to set the appropriate interrupt priority.

Except for the single-bit error interrupt, error events are not captured or counted by hardware. This functionality can be implemented in the software application, but it is the user's responsibility to do so.

#### 5.5 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 5.5.1 KEY RESOURCES

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 5.6 Control Registers

The following five SFRs are used to read and write the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program, inactive panel erase) and initiates the program/erase cycle.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. For row programming operation, data to be written to program Flash memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of the first element in row programming data).

#### **REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x          | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------|----------------|-------|-------|-------|-------|-------|-------|--|--|

|       | NVMADRU<23:16> |       |       |       |       |       |       |  |  |

| bit 7 |                |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMADRU<23:16>: NVM Memory Upper Write Address bits

Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be

read or written to by the user application.

#### **NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER REGISTER 5-3:**

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| NVMADR<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       |       |  |  |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| NVMADR<7:0> |       |       |       |       |       |       |       |  |

| bit 7 bit   |       |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register

may be read or written to by the user application.

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/S-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | _   | _   | _   | _   | _   | _   | _     |

| bit 15               | •   |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Forces a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-8 **Unimplemented:** Read as '0'

bit 7-0 IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits

01000110 = TX data request  $(CAN1)^{(2)}$

00100110 = Input Capture 4 (IC4)

00100101 = Input Capture 3 (IC3)

00100010 = RX data ready (CAN1)

00100001 = SPI2 transfer done (SPI2)

00011111 = UART2 Transmitter (UART2TX)

00011110 = UART2 Receiver (UART2RX)

00011100 = Timer5 (TMR5)

00011011 = Timer4 (TMR4)

00011010 = Output Compare 4 (OC4)

00011001 = Output Compare 3 (OC3)

00001101 = ADC1 convert done (ADC1)

00001100 = UART1 Transmitter (UART1TX)

00001011 = UART1 Receiver (UART1RX)

00001010 = SPI1 transfer done (SPI1)

00001000 = Timer3 (TMR3)

00000111 = Timer2 (TMR2)

00000110 = Output Compare 2 (OC2)

00000101 = Input Capture 2 (IC2)

00000010 = Output Compare 1 (OC1)

00000001 = Input Capture 1 (IC1)

00000000 = External Interrupt 0 (INT0)

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This select bit is only available on dsPIC33EVXXXGM10X devices.

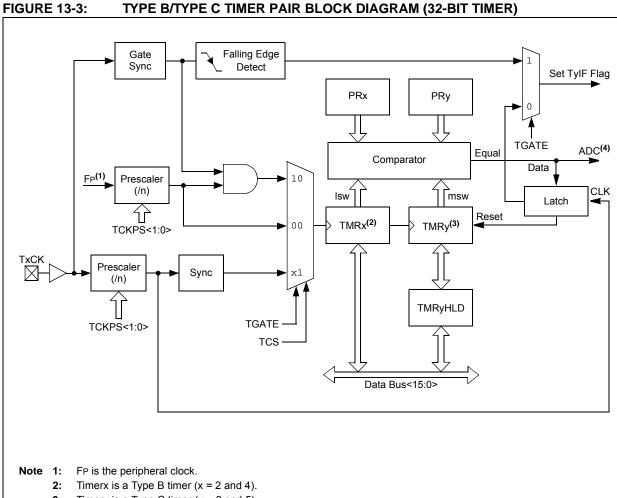

- 3: Timery is a Type C timer (y = 3 and 5).

- 4: The ADC trigger is available only on the TMR3:TMR2 and TMR5:TMR4 32-bit timer pairs.

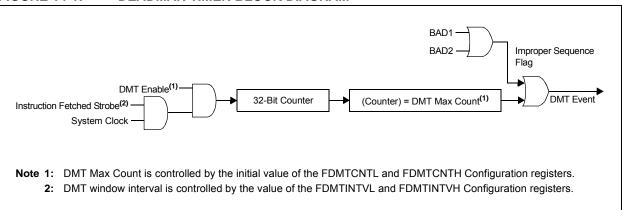

## 14.0 DEADMAN TIMER (DMT)

Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Deadman Timer (DMT)" (DS70005155) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT, which works on the system clock, is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs, until a count match occurs. Instructions are not fetched when the processor is in Sleep mode.

DMT can be enabled in the Configuration fuse or by software in the DMTCON register by setting the ON bit. The DMT consists of a 32-bit counter with a time-out count match value, as specified by the two 16-bit Configuration Fuse registers: FDMTCNTL and FDMTCNTH.

A DMT is typically used in mission-critical, and safety-critical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 14-1 shows a block diagram of the Deadman Timer module.

#### FIGURE 14-1: DEADMAN TIMER BLOCK DIAGRAM

#### 17.0 HIGH-SPEED PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- · Three PWM Generators

- Two PWM Outputs per PWM Generator

- Individual Period and Duty Cycle for each PWM Pair

- Duty Cycle, Dead Time, Phase Shift and Frequency Resolution of 8.32 ns

- Independent Fault and Current-Limit Inputs for Six PWM Outputs

- Redundant Output

- · Center-Aligned PWM mode

- · Output Override Control

- Chop mode (also known as Gated mode)

- · Special Event Trigger

- · Prescaler for Input Clock

- PWMxL and PWMxH Output Pin Swapping

- Independent PWM Frequency, Duty Cycle and Phase-Shift Changes for each PWM Generator

- · Dead-Time Compensation

- Enhanced Leading-Edge Blanking (LEB) Functionality

- Frequency Resolution Enhancement

- · PWM Capture Functionality

Note: In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns at 60 MIPS.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on the master time base.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin, that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 17-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

#### 17.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs as follows:

- FLT1 and FLT2, available on 28-pin, 44-pin and 64-pin packages, which are remappable using the PPS feature

- FLT3, available on 44-pin and 64-pin packages, which is available as a fixed pin

- FLT4-FLT8, available on 64-pin packages, which are available as fixed pins

- · FLT32 is available on a fixed pin on all devices

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 17.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the high-speed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

**Note:** The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCONx<1:0>), regardless of the state of FLT32.

## 22.3 CAN Control Registers

#### REGISTER 22-1: CxCTRL1: CANx CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-------|-------|--------|--------|--------|--------|

| _      | _   | CSIDL | ABAT  | CANCKS | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |     |       |       |        |        |        | bit 8  |

| R-1     | R-0     | R-0     | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|---------|---------|---------|-----|--------|-----|-----|-------|

| OPMODE2 | OPMODE1 | OPMODE0 | _   | CANCAP | _   | _   | WIN   |

| bit 7   |         |         |     |        |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 CSIDL: CANx Stop in Idle Mode bit

1 = Discontinues module operation when the device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 ABAT: Abort All Pending Transmissions bit

1 = Signals all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 CANCKS: CANx Module Clock (FCAN) Source Select bit

1 = FCAN is equal to 2 \* FP 0 = FCAN is equal to FP

bit 10-8 **REQOP<2:0>:** Request Operation Mode bits

111 = Sets Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Sets Configuration mode 011 = Sets Listen Only mode

010 = Sets Loopback mode 001 = Sets Disable mode

000 = Sets Normal Operation mode

bit 7-5 **OPMODE<2:0>**: Operation Mode bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode 001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 4 Unimplemented: Read as '0'

bit 3 CANCAP: CANx Message Receive Timer Capture Event Enable bit

1 = Enables input capture based on CAN message receive

0 = Disables CAN capture

bit 2-1 **Unimplemented:** Read as '0'

bit 0 WIN: SFR Map Window Select bit

1 = Uses filter window

0 = Uses buffer window

#### REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F13BP3 | F13BP2 | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F15BP<3:0>: RX Buffer Mask for Filter 15 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 **F14BP<3:0>:** RX Buffer Mask for Filter 14 bits (same values as bits 15-12) bit 7-4 **F13BP<3:0>:** RX Buffer Mask for Filter 13 bits (same values as bits 15-12)

bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)

#### REGISTER 23-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|---------|----------|----------|----------|----------|----------|----------|

| EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT |

| bit 15  |         |          |          |          |          |          | bit 8    |

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0   |

|---------|---------|----------|----------|----------|----------|-----|-------|

| EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _   | _     |

| bit 7   |         |          |          |          |          |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 EDG1MOD: Edge 1 Edge Sampling Mode Selection bit

1 = Edge 1 is edge-sensitive 0 = Edge 1 is level-sensitive

bit 14 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 is programmed for a positive edge response 0 = Edge 1 is programmed for a negative edge response

bit 13-10 EDG1SEL<3:0>: Edge 1 Source Select bits

1111 **=** Fosc

1110 = OSCI pin

1101 = FRC Oscillator

1100 = BFRC Oscillator

1011 = Internal LPRC Oscillator

1010 = Reserved

1001 = Reserved

1000 = Reserved

0111 = Reserved

0110 = Reserved

0101 = Reserved 0100 = Reserved

0011 = CTED1 pin

0010 = CTED2 pin

0001 = OC1 module

0000 = TMR1 module

bit 9 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control the edge source.

1 = Edge 2 has occurred

0 = Edge 2 has not occurred

bit 8 **EDG1STAT:** Edge 1 Status bit

Indicates the status of Edge 1 and can be written to control the edge source.

1 = Edge 1 has occurred

0 = Edge 1 has not occurred

bit 7 EDG2MOD: Edge 2 Edge Sampling Mode Selection bit

1 = Edge 2 is edge-sensitive

0 = Edge 2 is level-sensitive

bit 6 EDG2POL: Edge 2 Polarity Select bit

1 = Edge 2 is programmed for a positive edge response

0 = Edge 2 is programmed for a negative edge response

## REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

bit 1 **BUFM:** Buffer Fill Mode Select bit

1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt

0 = Always starts filling the buffer from the Start address

bit 0 ALTS: Alternate Input Sample Mode Select bit

1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample

0 = Always uses channel input selects for Sample MUX A

**Note 1:** The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVSS.

## REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits<sup>(2)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output.

00 = Trigger/event/interrupt generation is disabled

bit 5 **Unimplemented:** Read as '0'

bit 4 CREF: Comparator 4 Reference Select bit (VIN+ input)<sup>(1)</sup>

1 = VIN+ input connects to the internal CVREFIN voltage

0 = VIN+ input connects to the C4IN1+ pin

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 **CCH<1:0>:** Comparator 4 Channel Select bits<sup>(1)</sup>

11 = VIN- input of comparator connects to the C4IN4- pin

10 = VIN- input of comparator connects to the C4IN3- pin

01 = VIN- input of comparator connects to the C4IN2- pin

00 = VIN- input of comparator connects to the C4IN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

TABLE 30-35: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)

TIMING REQUIREMENTS

| AC CHA | ARACTERIST            | Standard Op<br>(unless other<br>Operating ter | erwise st    | t <b>ated)</b><br>re -40° | C ≤ Ta ≤ | +85°C for Industrial<br>+125°C for Extended |                                      |

|--------|-----------------------|-----------------------------------------------|--------------|---------------------------|----------|---------------------------------------------|--------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min.         | Typ. <sup>(2)</sup>       | Max.     | Units                                       | Conditions                           |

| SP70   | FscP                  | Maximum SCK2 Input Frequency                  | _            | _                         | 11       | MHz                                         | See Note 3                           |

| SP72   | TscF                  | SCK2 Input Fall Time                          | _            | _                         | I        | ns                                          | See Parameter DO32 and <b>Note 4</b> |

| SP73   | TscR                  | SCK2 Input Rise Time                          | _            | _                         |          | ns                                          | See Parameter DO31 and <b>Note 4</b> |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                    | _            | _                         | 1        | ns                                          | See Parameter DO32 and <b>Note 4</b> |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                    | _            | _                         | _        | ns                                          | See Parameter DO31 and <b>Note 4</b> |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge     | _            | 6                         | 20       | ns                                          |                                      |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge     | 30           | _                         | _        | ns                                          |                                      |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge    | 30           | _                         | _        | ns                                          |                                      |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30           | _                         | _        | ns                                          |                                      |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input               | 120          |                           | 1        | ns                                          |                                      |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance        | 10           | _                         | 50       | ns                                          | See Note 4                           |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                         | 1.5 Tcy + 40 | _                         | _        | ns                                          | See Note 4                           |

| SP60   | TssL2doV              | SDO2 Data Output Valid after SS2 Edge         | _            | _                         | 50       | ns                                          |                                      |

**Note 1:** These parameters are characterized but not tested in manufacturing.

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

#### TABLE 30-58: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC CH        | AC CHARACTERISTICS |                                                                      | Standard Operating Conditions (see Note 1): 4.5V to 5.5 (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |          |                                      |

|--------------|--------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|----------|--------------------------------------|

| Param<br>No. | Symbol             | Characteristic                                                       | Min.                                                                                                                                                                                                                                                         | Typ. <sup>(4)</sup> | Max. | Units    | Conditions                           |

|              |                    | Cloc                                                                 | k Parame                                                                                                                                                                                                                                                     | eters               |      | <u>'</u> |                                      |

| AD50         | TAD                | ADC Clock Period                                                     | 75                                                                                                                                                                                                                                                           | _                   | _    | ns       |                                      |

| AD51         | trc                | ADC Internal RC Oscillator Period                                    | _                                                                                                                                                                                                                                                            | 250                 | _    | ns       |                                      |

|              |                    | Con                                                                  | version F                                                                                                                                                                                                                                                    | Rate                |      |          | •                                    |

| AD55         | tconv              | Conversion Time                                                      | _                                                                                                                                                                                                                                                            | 12                  | _    | TAD      |                                      |

| AD56         | FCNV               | Throughput Rate                                                      | _                                                                                                                                                                                                                                                            | _                   | 1.1  | Msps     | Using simultaneous sampling          |

| AD57a        | TSAMP              | Sample Time When Sampling Any ANx Input                              | 2                                                                                                                                                                                                                                                            | _                   | _    | TAD      |                                      |

| AD57b        | TSAMP              | Sample Time When Sampling the Op Amp Outputs                         | 4                                                                                                                                                                                                                                                            | _                   | _    | TAD      |                                      |

|              |                    | Timin                                                                | g Param                                                                                                                                                                                                                                                      | eters               |      |          |                                      |

| AD60         | tPCS               | Conversion Start from Sample Trigger <sup>(2)</sup>                  | 2                                                                                                                                                                                                                                                            | _                   | 3    | TAD      | Auto-convert trigger is not selected |

| AD61         | tPSS               | Sample Start from Setting Sample (SAMP) bit <sup>(2)</sup>           | 2                                                                                                                                                                                                                                                            | _                   | 3    | TAD      |                                      |

| AD62         | tcss               | Conversion Completion to Sample Start (ASAM = 1) <sup>(2)</sup>      | _                                                                                                                                                                                                                                                            | 0.5                 | _    | TAD      |                                      |

| AD63         | tDPU               | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(2)</sup> | _                                                                                                                                                                                                                                                            | _                   | 20   | μS       | See Note 3                           |

- Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

- **2:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- **3:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (ADxCON1<15>) = 1). During this time, the ADC result is indeterminate.

- 4: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-59: DMA MODULE TIMING REQUIREMENTS

| AC CH        | ARACTERISTICS                  | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |   |       |            |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-------|------------|

| Param<br>No. | Characteristic                 | Min. Typ. <sup>(1)</sup> Max. Units                                                                                                                                                                                                              |   |   | Units | Conditions |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <sup>(2)</sup>                                                                                                                                                                                                                             | _ | _ | ns    |            |

- **Note 1:** These parameters are characterized but not tested in manufacturing.

- **2:** Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

## TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT    | ERISTICS      |      |       |                                         | 5V to 5.5V (unless otherwise stated)<br>≤ +150°C for High Temperature |  |  |

|---------------|---------------|------|-------|-----------------------------------------|-----------------------------------------------------------------------|--|--|

| Parameter No. | Typical       | Max  | Units | Conditions                              |                                                                       |  |  |

| Power-Down    | Current (IPD) |      |       |                                         |                                                                       |  |  |

| HDC60e        | 1300          | 2500 | μΑ    | +150°C 5V Base Power-Down Current       |                                                                       |  |  |

| HDC61c        | 10            | 50   | μΑ    | +150°C 5V Watchdog Timer Current: ΔIWDT |                                                                       |  |  |

## TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG     | CTERISTICS |     |       |            |    | (unless otherwise stated)<br>for High Temperature |

|---------------|------------|-----|-------|------------|----|---------------------------------------------------|

| Parameter No. | Typical    | Max | Units | Conditions |    |                                                   |

| HDC40e        | 2.6        | 5.0 | mA    | +150°C     | 5V | 10 MIPS                                           |

| HDC42e        | 3.6        | 7.0 | mA    | +150°C     | 5V | 20 MIPS                                           |

## TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAC     | CTERISTICS |      |       | •          |    | V (unless otherwise stated) C for High Temperature |  |

|---------------|------------|------|-------|------------|----|----------------------------------------------------|--|

| Parameter No. | Typical    | Max  | Units | Conditions |    |                                                    |  |

| HDC20e        | 5.9        | 8.0  | mA    | +150°C     | 5V | 10 MIPS                                            |  |

| HDC22e        | 10.3       | 15.0 | mA    | +150°C     | 5V | 20 MIPS                                            |  |

| HDC23e        | 19.0       | 25.0 | mA    | +150°C     | 5V | 40 MIPS                                            |  |

## TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARAC     | CTERISTICS |      | l '        |       |            | •  | nless otherwise stated)<br>r High Temperature |  |

|---------------|------------|------|------------|-------|------------|----|-----------------------------------------------|--|

| Parameter No. | Typical    | Max  | Doze Ratio | Units | Conditions |    |                                               |  |

| HDC73a        | 18.5       | 22.0 | 1:2        | mA    | :45000 51/ |    | 40 MIPS                                       |  |

| HDC73g        | 8.35       | 12.0 | 1:128      | mA    | +150°C     | 5V | 40 MIPS                                       |  |

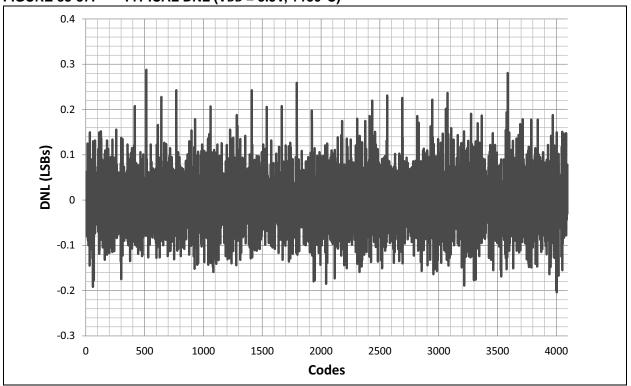

## 33.17 ADC DNL

FIGURE 33-37: TYPICAL DNL (VDD = 5.5V, +150°C)

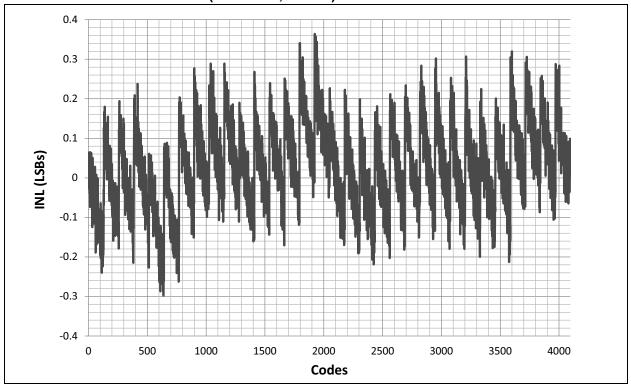

## 33.18 ADC INL

FIGURE 33-38: TYPICAL INL (VDD = 5.5V, +150°C)

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |           |      |

|--------------------------|-------------|------|-----------|------|

| Dimension                | MIN         | NOM  | MAX       |      |

| Number of Leads          | N           |      | 44        |      |

| Lead Pitch               | е           |      | 0.80 BSC  |      |

| Overall Height           | Α           | -    | -         | 1.20 |

| Standoff                 | A1          | 0.05 | -         | 0.15 |

| Molded Package Thickness | A2          | 0.95 | 1.00      | 1.05 |

| Overall Width            | Е           |      | 12.00 BSC |      |

| Molded Package Width     | E1          |      | 10.00 BSC |      |

| Overall Length           | D           |      | 12.00 BSC |      |

| Molded Package Length    | D1          |      | 10.00 BSC |      |

| Lead Width               | b           | 0.30 | 0.37      | 0.45 |

| Lead Thickness           | С           | 0.09 | -         | 0.20 |

| Lead Length              | L           | 0.45 | 0.60      | 0.75 |

| Footprint                | L1          |      | 1.00 REF  |      |

| Foot Angle               | θ           | 0°   | 3.5°      | 7°   |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Exact shape of each corner is optional.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

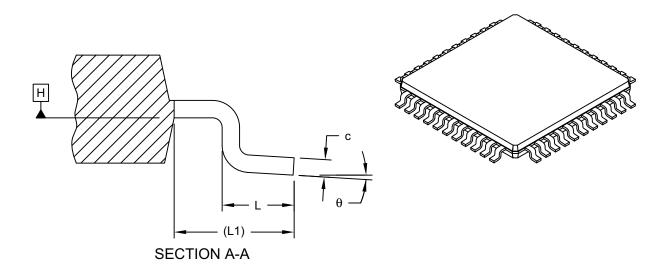

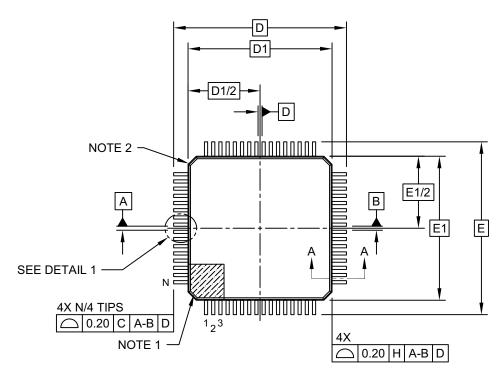

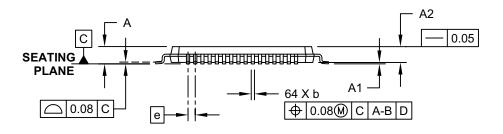

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

## **INDEX**

| A                                                |         | Timer1 External Clock Requirements        | 357 |

|--------------------------------------------------|---------|-------------------------------------------|-----|

| Absolute Maximum Ratings                         | 341     | Timer2 and Timer4 (Type B) External Clock |     |

| AC Characteristics                               |         | Requirements                              | 358 |

| 10-Bit ADC Conversion Requirements               |         | Timer3 and Timer5 (Type C) External Clock |     |

|                                                  |         | Requirements                              | 358 |

| 12-Bit ADC Conversion Requirements               |         | UARTx I/O Requirements                    |     |

| 12Cx Bus Data Requirements (Master Mode)         |         | ADC                                       |     |

| ADC Module                                       |         | 10-Bit Configuration                      | 285 |

| ADC Module (10-Bit Mode)                         |         | 12-Bit Configuration                      |     |

| ADC Module (12-Bit Mode)                         |         | Control Registers                         |     |

| CANx I/O Requirements                            | 391     | Helpful Tips                              |     |

| Capacitive Loading Requirements on               |         |                                           |     |

| Output Pins                                      | 351     | Key Features                              |     |

| DMA Module Requirements                          | 401     | Alternate Interrupt Vector Table (AIVT)   | 95  |

| External Clock Requirements                      | 352     | Analog-to-Digital Converter. See ADC.     |     |

| High Temperature                                 |         | Assemblers                                |     |

| ADC Module (10-Bit Mode)                         |         | MPASM Assembler                           |     |

| ADC Module (12-Bit Mode)                         |         | MPLAB Assembler, Linker, Librarian        | 338 |

| Internal FRC Accuracy                            |         | В                                         |     |

| Internal LPRC Accuracy                           |         | В                                         |     |

| · · · · · · · · · · · · · · · · · · ·            |         | Bit-Reversed Addressing                   |     |

| PLL Clock                                        |         | Example                                   | 78  |

| High-Speed PWMx Requirements                     |         | Implementation                            |     |

| I/O Requirements                                 |         | Sequence Table (16-Entry)                 |     |

| I2Cx Bus Data Requirements (Slave Mode)          |         | Block Diagrams                            |     |

| Input Capture x (ICx) Requirements               |         | 16-Bit Timer1 Module                      | 173 |

| Internal FRC Accuracy                            | 353     | Accessing Program Memory with             | 170 |

| Internal LPRC Accuracy                           | 353     | Table Instructions                        | 0.  |

| Load Conditions35                                | 51, 408 |                                           |     |

| OCx/PWMx Mode Requirements                       | 360     | ADCx Conversion Clock Period              | 281 |

| Op Amp/Comparator x Voltage Reference            |         | ADCx with Connection Options for ANx Pins |     |

| Settling Time                                    | 393     | and Op Amps                               |     |

| Output Compare x (OCx) Requirements              |         | Addressing for Table Registers            | 83  |

| PLL Clock                                        |         | Arbiter Architecture                      | 73  |

|                                                  |         | CALL Stack Frame                          | 74  |

| Reset, Watchdog Timer, Oscillator Start-up Timer |         | CANx Module                               | 254 |

| and Power-up Timer Requirements                  | 350     | Comparator Voltage Reference Module       | 314 |

| SPI1 Master Mode (Full-Duplex, CKE = 0,          |         | Connections for On-Chip Voltage Regulator |     |

| CKP = x, SMP = 1) Requirements                   | 378     | CPU Core                                  |     |

| SPI1 Master Mode (Full-Duplex, CKE = 1,          |         | CTMU Module                               |     |

| CKP = x, SMP = 1)                                | 376     | Data Access from Program Space Address    | 200 |

| SPI1 Master Mode (Half-Duplex,                   |         | Generation                                | 80  |

| Transmit Only) Requirements                      | 375     | Deadman Timer Module                      |     |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,           |         |                                           |     |

| CKP = 0, SMP = 0) Requirements                   | 386     | Digital Filter Interconnect               |     |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,           |         | DMA Controller                            |     |

| CKP = 1, SMP = 0) Requirements                   | 384     | dsPIC33EVXXXGM00X/10X Family              |     |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,           |         | EDS Read Address Generation               | 68  |

| CKP = 0, SMP = 0) Requirements                   | 380     | EDS Write Address Generation              |     |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,           | 500     | High-Speed PWMx Architectural Overview    | 201 |

| · · ·                                            | 202     | High-Speed PWMx Register Interconnection  | 202 |

| CKP = 1, SMP = 0) Requirements                   | 382     | I2Cx Module                               | 230 |

| SPI2 Master Mode (Full-Duplex, CKE = 0,          |         | Input Capture x Module                    |     |

| CKP = x, SMP = 1) Requirements                   | 365     | MCLR Pin Connections                      |     |

| SPI2 Master Mode (Full-Duplex, CKE = 1,          |         | Multiplexing Remappable Output for RPn    |     |

| CKP = x, SMP = 1) Requirements                   | 364     | Op Amp/Comparator x Module                |     |

| SPI2 Master Mode (Half-Duplex,                   |         | Oscillator Circuit Placement              |     |

| Transmit Only) Requirements                      | 363     |                                           |     |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,           |         | Oscillator System                         |     |

| CKP = 0, SMP = 0) Requirements                   | 373     | Output Compare x Module                   |     |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,           | -       | Paged Data Memory Space                   |     |

| CKP = 1, SMP = 0) Requirements                   | 371     | Peripheral to DMA Controller              |     |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,           | 0. 1    | PLL Module                                |     |

| CKP = 0, SMP = 0) Requirements                   | 367     | Recommended Minimum Connection            | 18  |

| , ,                                              | 501     | Remappable Input for U1RX                 | 146 |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,           | 260     | Reset System                              | 92  |

| CKP = 1, SMP = 0) Requirements                   | ১७५     | •                                         |     |