Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm006-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Timers/Output Compare/Input Capture**

- Nine General Purpose Timers:

- Five 16-bit and up to two 32-bit timers/counters; Timer3 can provide ADC trigger

- Four Output Compare modules Configurable as Timers/Counters

- Four Input Capture modules

## **Communication Interfaces**

- Two Enhanced Addressable Universal Asynchronous Receiver/Transmitter (UART) modules (6.25 Mbps):

- With support for LIN/J2602 bus and IrDA®

- High and low speed (SCI)

- Two SPI modules (15 Mbps):

- 25 Mbps data rate without using PPS

- One I<sup>2</sup>C module (up to 1 Mbaud) with SMBus Support

- Two SENT J2716 (Single-Edge Nibble Transmission-Transmit/Receive) module for Automotive Applications

- One CAN module:

- 32 buffers, 16 filters and three masks

## **Direct Memory Access (DMA)**

- 4-Channel DMA with User-Selectable Priority Arbitration

- UART, Serial Peripheral Interface (SPI), ADC, Input Capture, Output Compare and Controller Area Network (CAN)

## Input/Output

- GPIO Registers to Support Selectable Slew Rate I/Os

- Peripheral Pin Select (PPS) to allow Function Remap

- Sink/Source: 8 mA or 12 mA, Pin-Specific for Standard VOH/VOL

- · Selectable Open-Drain, Pull-ups and Pull-Downs

- Change Notice Interrupts on All I/O Pins

## **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1: -40°C to +125°C) Compliant

- AEC-Q100 REVG (Grade 0: -40°C to +150°C) Compliant

- Class B Safety Library, IEC 60730

## **Class B Fault Handling Support**

- Backup FRC

- · Windowed WDT uses LPRC

- Windowed Deadman Timer (DMT) uses System Clock (System Windowed Watchdog Timer)

- H/W Clock Monitor Circuit

- Oscillator Frequency Monitoring through CTMU (OSCI, SYSCLK, FRC, BFRC, LPRC)

- Dedicated PWM Fault Pin

- Lockable Clock Configuration

## **Debugger Development Support**

- In-Circuit and In-Application Programming

- · Three Complex and Five Simple Breakpoints

- Trace and Run-Time Watch

# dsPIC33EVXXXGM00X/10X FAMILY

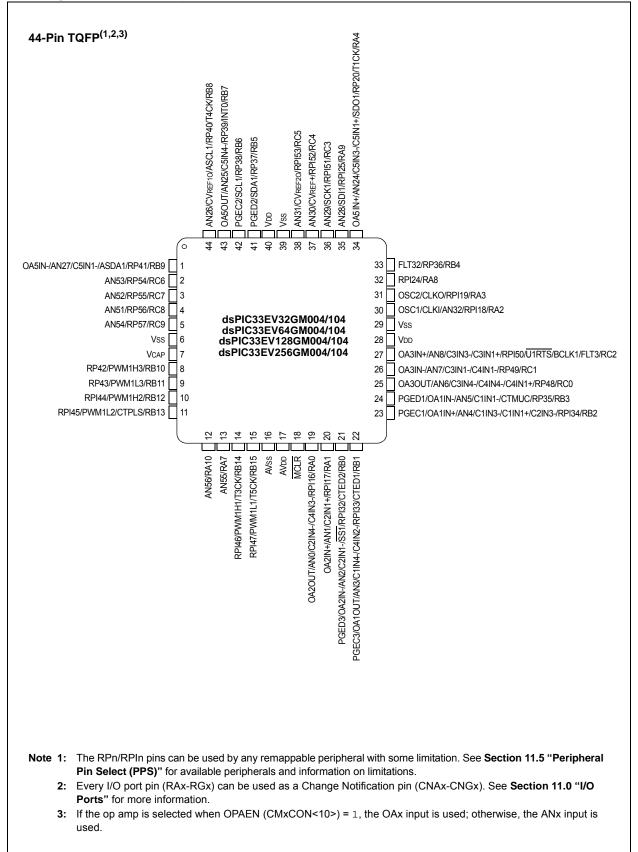

## **Pin Diagrams (Continued)**

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

## 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

## TABLE 4-29: PWM GENERATOR 2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | _        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2     | 0C44  | _       | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2        | 0C46  |         |         |         |         |           |           |           | PDC2             | <15:0>    |         |          |          |          |          |          |          | 0000          |

| PHASE2      | 0C48  |         |         |         |         |           |           |           | PHASE            | 2<15:0>   |         |          |          |          |          |          |          | 0000          |

| DTR2        | 0C4A  | -       | _       |         |         |           |           |           |                  | DTR2      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2     | 0C4C  |         |         |         |         |           |           |           |                  | ALTDTR    | 2<13:0> |          |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |         |         |         |         |           |           |           | TRGCN            | 1P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON2     | 0C54  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | —         | —         | —         | —                |           |         | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP2     | 0C58  |         |         |         |         |           |           |           | PWMCA            | .P2<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON2     | 0C5A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | —         | —                |           |         | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | -       | _       | _       |         |           |           |           |                  |           | LEB<    | :11:0>   |          |          |          |          |          | 0000          |

| AUXCON2     | 0C5E  | -       | -       | _       |         | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> |           | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

|             |       |         |         |         |         |           |           |           |                  |           |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-30: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | —        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON3     | 0C64  | -       | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC3        | 0C66  |         |         |         |         |           |           |           | PDC              | 3<15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE3      | 0C68  |         |         |         |         |           |           |           | PHASI            | E3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR3        | 0C6A  | _       | —       |         |         |           |           |           |                  | DTR3      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR3     | 0C6C  | _       | —       |         |         |           |           |           |                  | ALTDTF    | 3<13:0> |          |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |         |         |         |         |           |           |           | TRGC             | /IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON3     | 0C74  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 |           | _         |           | —                | —         | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP3     | 0C78  |         |         |         |         |           |           |           | PWMCA            | AP3<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON3     | 0C7A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _                | —         | —       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY3     | 0C7C  | _       | _       | _       | _       |           |           |           |                  |           | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON3     | 0C7E  | _       | _       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | —         | —       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PORTC REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13 | Bit 12             | Bit 11       | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|--------|--------------------|--------------|--------|-------|-------|---------|----------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC       | 0E28  | TRISC15 | _      |        |                    |              |        |       |       | TRISC<1 | 3:0>     |       |       |       |       |       |       | BFFF          |

| PORTC       | 0E2A  | RC15    | _      |        |                    |              |        |       |       | RC<13:  | 0>       |       |       |       |       |       |       | xxxx          |

| LATC        | 0E2C  | LATC15  | _      |        |                    | LATC<13:0> 2 |        |       |       |         |          |       | xxxx  |       |       |       |       |               |

| ODCC        | 0E2E  | ODCC15  | _      |        | ODCC<13:0>         |              |        |       |       |         |          | 0000  |       |       |       |       |       |               |

| CNENC       | 0E30  | CNIEC15 | _      |        |                    |              |        |       |       | CNIEC<1 | 3:0>     |       |       |       |       |       |       | 0000          |

| CNPUC       | 0E32  | CNPUC15 | _      |        |                    |              |        |       |       | CNPUC<1 | 3:0>     |       |       |       |       |       |       | 0000          |

| CNPDC       | 0E34  | CNPDC15 | _      |        |                    |              |        |       |       | CNPDC<1 | 3:0>     |       |       |       |       |       |       | 0000          |

| ANSELC      | 0E36  | _       | _      | _      |                    |              |        |       |       | AN      | SC<12:0> |       |       |       |       |       |       | 1FFF          |

| SR1C        | 0E38  | _       | _      | _      | SR1C<9:6> SR1C3 00 |              |        |       |       |         |          |       |       | 0000  |       |       |       |               |

| SR0C        | 0E3A  | —       | —      | _      | SR0C<9:6> SR0C3 0  |              |        |       |       |         |          |       | 0000  |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-38: PORTC REGISTER MAP FOR dsPIC33EVXXXGMX04 DEVICES

|             | T T   |        | 1      |        |        |        |        |       |       |       | 1     | 1     |        | 1     |       |       |       | 1             |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TRISC       | 0E28  | _      | —      | _      | _      | —      | _      |       |       |       |       | TRISC | ><9:0> |       |       |       |       | BFFF          |

| PORTC       | 0E2A  | _      | _      | _      | _      | _      | _      |       |       |       |       | RC<   | 9:0>   |       |       |       |       | xxxx          |

| LATC        | 0E2C  | _      | _      | _      | _      | _      | _      |       |       |       |       | LATC  | <9:0>  |       |       |       |       | xxxx          |

| ODCC        | 0E2E  | _      | _      | _      | _      | _      | _      |       |       |       |       | ODCC  | <9:0>  |       |       |       |       | 0000          |

| CNENC       | 0E30  | _      | _      | _      | _      | _      | _      |       |       |       |       | CNIEC | C<9:0> |       |       |       |       | 0000          |

| CNPUC       | 0E32  | _      | _      | _      | _      | _      | _      |       |       |       |       | CNPU  | C<9:0> |       |       |       |       | 0000          |

| CNPDC       | 0E34  | _      | _      | _      | _      | _      | _      |       |       |       |       | CNPD  | C<9:0> |       |       |       |       | 0000          |

| ANSELC      | 0E36  | _      | _      | _      | _      | _      | _      |       |       |       |       | ANSC  | <9:0>  |       |       |       |       | 0807          |

| SR1C        | 0E38  | _      | —      | _      | —      | _      | _      |       | SR1C  | <9:6> |       | —     | —      | SR1C3 | _     | —     | _     | 0000          |

| SR0C        | 0E3A  | _      | —      | _      | —      | _      | —      |       | SR0C  | <9:6> |       | —     | —      | SR0C3 | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.3.1 PAGED MEMORY SCHEME

The dsPIC33EVXXXGM00X/10X family architecture extends the available DS through a paging scheme, which allows the available DS to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the Base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Data Space Read Page register (DSRPAG) or the 9-bit Data Space Write Page register (DSWPAG), to form an EDS address, or Program Space Visibility (PSV) address.

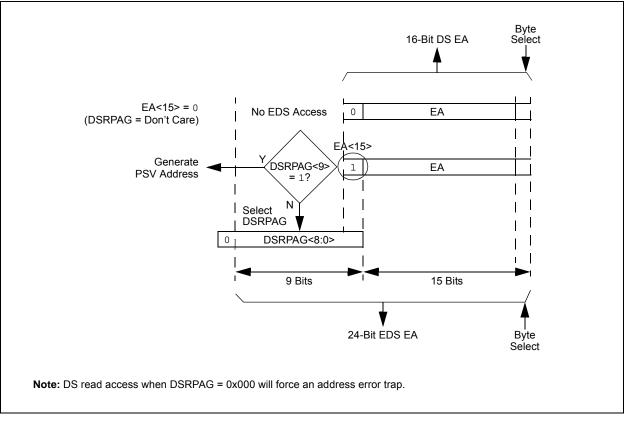

The Data Space Page registers are located in the SFR space. Construction of the EDS address is shown in Figure 4-9 and Figure 4-10. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS write address.

### FIGURE 4-9: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

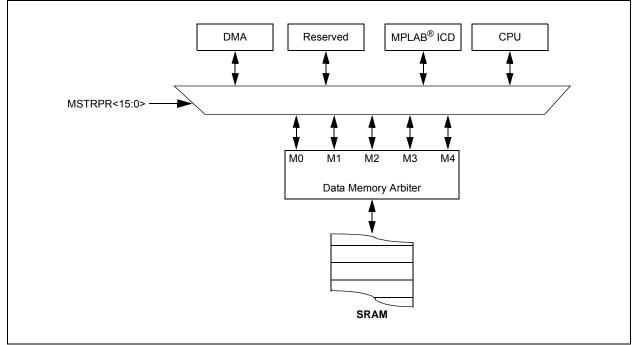

# 4.3.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the MPLAB<sup>®</sup> ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the MPLAB ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities

below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are listed in Table 4-44.

Figure 4-13 shows the arbiter architecture.

The bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

# TABLE 4-44:DATA MEMORY BUS<br/>ARBITER PRIORITY

| Driarity     | MSTRPR<15:0            | > Bit Setting <sup>(1)</sup> |

|--------------|------------------------|------------------------------|

| Priority     | 0x0000                 | 0x0020                       |

| M0 (highest) | CPU                    | DMA                          |

| M1           | Reserved               | CPU                          |

| M2           | Reserved               | Reserved                     |

| M3           | DMA                    | Reserved                     |

| M4 (lowest)  | MPLAB <sup>®</sup> ICD | MPLAB ICD                    |

Note 1: All other values of MSTRPR<15:0> are reserved.

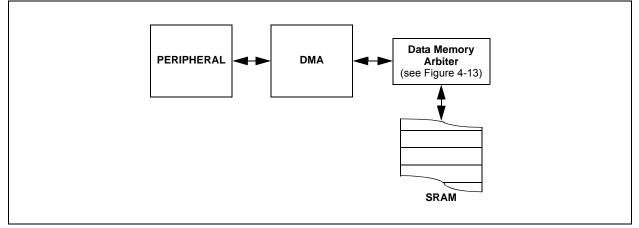

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

## **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PAI   | )<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|------------------|-------|-------|

| —      | —   |       |       | CNT<  | 13:8> <b>(2)</b> |       |       |

| bit 15 |     |       |       |       |                  |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <b>(2)</b> |       |       |       |

| bit 7 |       |       |       |                 |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

| R/W-0         | R/W-0                                | R/W-0                | R/W-0                | R/W-0                             | R/W-0                     | R/W-0           | R/W-1          |

|---------------|--------------------------------------|----------------------|----------------------|-----------------------------------|---------------------------|-----------------|----------------|

| ROI           | DOZE2 <sup>(3)</sup>                 | DOZE1 <sup>(3)</sup> | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>            | FRCDIV2                   | FRCDIV1         | FRCDIV0        |

| bit 15        |                                      | •                    | -                    | -                                 |                           | •               | bit 8          |

|               |                                      |                      | DAMO                 | D/M/ 0                            |                           | R/W-0           | DAMA           |

| R/W-0         | R/W-0                                | U-0                  | R/W-0                | R/W-0                             | R/W-0                     |                 | R/W-0          |

| PLLPOST1      | PLLPOST0                             | —                    | PLLPRE4              | PLLPRE3                           | PLLPRE2                   | PLLPRE1         | PLLPRE0        |

| bit 7         |                                      |                      |                      |                                   |                           |                 | bit C          |

| Legend:       |                                      |                      |                      |                                   |                           |                 |                |

| R = Readable  | bit                                  | W = Writable         | bit                  | U = Unimpler                      | nented bit, read          | l as '0'        |                |

| -n = Value at | POR                                  | '1' = Bit is set     |                      | '0' = Bit is cle                  | ared                      | x = Bit is unkr | nown           |

| bit 15        |                                      | on Interrupt b       | i+                   |                                   |                           |                 |                |

|               |                                      | will clear the E     |                      |                                   |                           |                 |                |

|               |                                      | have no effect       |                      | N bit                             |                           |                 |                |

| bit 14-12     | •                                    | Processor Clo        |                      |                                   |                           |                 |                |

|               | 111 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 110 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 101 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 100 = FCY div<br>011 = FCY div       |                      |                      |                                   |                           |                 |                |

|               | 010 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 001 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               |                                      | vided by 1 (def      |                      |                                   |                           |                 |                |

| bit 11        |                                      | e Mode Enable        |                      |                                   |                           |                 |                |

|               |                                      |                      |                      | tween the peri<br>atio are forced |                           | nd the process  | or clocks      |

| bit 10-8      | FRCDIV<2:0>                          | -: Internal Fast     | RC Oscillator        | Postscaler bit                    | S                         |                 |                |

|               | 111 <b>= FRC d</b> i                 | vided by 256         |                      |                                   |                           |                 |                |

|               | 110 <b>= FRC di</b>                  |                      |                      |                                   |                           |                 |                |

|               | 101 = FRC di                         | •                    |                      |                                   |                           |                 |                |

|               | 100 = FRC di<br>011 = FRC di         |                      |                      |                                   |                           |                 |                |

|               | 010 = FRC di                         |                      |                      |                                   |                           |                 |                |

|               |                                      | vided by 2 (de       | fault)               |                                   |                           |                 |                |

|               | 000 <b>= FRC di</b>                  | •                    |                      |                                   |                           |                 |                |

| bit 7-6       | PLLPOST<1:                           | 0>: PLL VCO          | Output Divide        | r Select bits (al                 | so denoted as             | 'N2', PLL posts | caler)         |

|               | 11 = Output d                        |                      |                      |                                   |                           |                 |                |

|               | 10 = Reserve<br>01 = Output d        |                      |                      |                                   |                           |                 |                |

|               | 00 = Output d                        |                      |                      |                                   |                           |                 |                |

| bit 5         |                                      | ted: Read as '       | 0'                   |                                   |                           |                 |                |

| Note 1: Th    | is bit is cleared v                  | when the ROI         | bit is set and a     | an interrupt occ                  | urs.                      |                 |                |

| <b>2:</b> Th  | is register resets                   | s only on a Pov      | wer-on Reset         | (POR).                            |                           |                 |                |

|               | )ZE<2:0> bits ca<br>)ZE<2:0> are igi |                      | en to when th        | e DOZEN bit is                    | clear. If DOZE            | N = 1, any wri  | tes to         |

|               | o DOZEN bit cou                      |                      | 075-2.05 -           |                                   | $2 \cdot 0 > - 0 = 0 = 0$ | attempt by up   | or ooftwara to |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| R/W-0         | R/W-0        | R/W-0                                | R/W-0    | R/W-0            | U-0            | R/W-0               | U-0          |

|---------------|--------------|--------------------------------------|----------|------------------|----------------|---------------------|--------------|

| T5MD          | T4MD         | T3MD                                 | T2MD     | T1MD             | —              | PWMMD               | —            |

| bit 15        |              |                                      |          |                  |                |                     | bit 8        |

| R/W-0         | R/W-0        | R/W-0                                | R/W-0    | R/W-0            | U-0            | R/W-0               | R/W-0        |

| I2C1MD        |              |                                      |          |                  | 0-0            | C1MD <sup>(1)</sup> |              |

| bit 7         | U2MD         | U1MD                                 | SPI2MD   | SPI1MD           | —              | CTMD                | AD1MD<br>bit |

|               |              |                                      |          |                  |                |                     |              |

| Legend:       |              |                                      |          |                  |                |                     |              |

| R = Readable  |              | W = Writable                         |          | •                | mented bit, re | ad as '0'           |              |

| -n = Value at | POR          | '1' = Bit is set                     |          | '0' = Bit is cle | ared           | x = Bit is unkn     | own          |

| bit 15        | T5MD: Timer  | 5 Module Disal                       | ole bit  |                  |                |                     |              |

|               |              | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 14        | T4MD: Timer  | 4 Module Disal                       | ole bit  |                  |                |                     |              |

|               | 1 = Timer4 m | odule is disable                     | ed       |                  |                |                     |              |

| bit 13        |              | 3 Module Disal                       |          |                  |                |                     |              |

|               |              | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 12        | T2MD: Timer  | 2 Module Disal                       | ole bit  |                  |                |                     |              |

|               | -            | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 11        | T1MD: Timer  | 1 Module Disal                       | ole bit  |                  |                |                     |              |

|               | -            | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 10        | Unimplemen   | ted: Read as '                       | 0'       |                  |                |                     |              |

| bit 9         | PWMMD: PW    | /M Module Dis                        | able bit |                  |                |                     |              |

|               |              | dule is disabled<br>dule is enabled  |          |                  |                |                     |              |

| bit 8         | Unimplemen   | ted: Read as '                       | 0'       |                  |                |                     |              |

| bit 7         | 12C1MD: 12C  | 1 Module Disal                       | ole bit  |                  |                |                     |              |

|               |              | lule is disabled<br>lule is enabled  |          |                  |                |                     |              |

| bit 6         | U2MD: UART   | 2 Module Disa                        | ble bit  |                  |                |                     |              |

|               | -            | nodule is disabl<br>nodule is enable |          |                  |                |                     |              |

| bit 5         | U1MD: UART   | 1 Module Disa                        | ble bit  |                  |                |                     |              |

|               |              | nodule is disabl<br>nodule is enable |          |                  |                |                     |              |

| bit 4         | SPI2MD: SPI  | 2 Module Disa                        | ole bit  |                  |                |                     |              |

|               |              | lule is disabled<br>lule is enabled  |          |                  |                |                     |              |

| bit 3         | SPI1MD: SPI  | 1 Module Disa                        | ole bit  |                  |                |                     |              |

|               |              | dule is disabled<br>dule is enabled  |          |                  |                |                     |              |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** This bit is available on dsPIC33EVXXXGM10X devices only.

| U-0                                | U-0                                                                           | U-0          | U-0                             | U-0                                | U-0 | U-0        | U-0   |  |  |

|------------------------------------|-------------------------------------------------------------------------------|--------------|---------------------------------|------------------------------------|-----|------------|-------|--|--|

| —                                  | —                                                                             | —            | —                               |                                    | —   | —          | —     |  |  |

| bit 15                             |                                                                               |              |                                 |                                    |     |            | bit 8 |  |  |

|                                    |                                                                               |              |                                 |                                    |     |            |       |  |  |

| U-0                                | U-0                                                                           | U-0          | R/W-0                           | U-0                                | U-0 | U-0        | U-0   |  |  |

| —                                  | —                                                                             | —            | DMA0MD <sup>(1)</sup>           | —                                  | —   | _          | —     |  |  |

|                                    |                                                                               |              | DMA1MD <sup>(1)</sup>           | -                                  |     |            |       |  |  |

|                                    |                                                                               |              | DMA2MD <sup>(1)</sup>           | -                                  |     |            |       |  |  |

|                                    |                                                                               |              | DMA3MD <sup>(1)</sup>           |                                    |     |            |       |  |  |

| bit 7                              |                                                                               |              |                                 |                                    |     |            | bit C |  |  |

|                                    |                                                                               |              |                                 |                                    |     |            |       |  |  |

| Legend:                            |                                                                               |              |                                 |                                    |     |            |       |  |  |

| R = Readable bit W = Writable bit  |                                                                               |              |                                 | U = Unimplemented bit, read as '0' |     |            |       |  |  |

| -n = Value at POR '1' = Bit is set |                                                                               | et           | '0' = Bit is cleared x = Bit is |                                    |     | is unknown |       |  |  |

|                                    |                                                                               |              |                                 |                                    |     |            |       |  |  |

| bit 15-5                           | Unimplement                                                                   |              |                                 |                                    |     |            |       |  |  |

| bit 4                              | DMA0MD: DMA0 Module Disable bit <sup>(1)</sup>                                |              |                                 |                                    |     |            |       |  |  |

|                                    | 1 = DMA0 module is disabled<br>0 = DMA0 module is enabled                     |              |                                 |                                    |     |            |       |  |  |

|                                    |                                                                               |              |                                 |                                    |     |            |       |  |  |

|                                    | DMA1MD: DMA1 Module Disable bit <sup>(1)</sup><br>1 = DMA1 module is disabled |              |                                 |                                    |     |            |       |  |  |

|                                    | 0 = DMA1 module is enabled                                                    |              |                                 |                                    |     |            |       |  |  |

|                                    | DMA2MD: DMA2 Module Disable bit <sup>(1)</sup>                                |              |                                 |                                    |     |            |       |  |  |

|                                    | 1 = DMA2 module is disabled                                                   |              |                                 |                                    |     |            |       |  |  |

|                                    | 0 = DMA2 module is enabled                                                    |              |                                 |                                    |     |            |       |  |  |

|                                    | DMA3MD: DMA3 Module Disable bit <sup>(1)</sup>                                |              |                                 |                                    |     |            |       |  |  |

|                                    | 1 = DMA3 mo<br>0 = DMA3 mo                                                    |              |                                 |                                    |     |            |       |  |  |

| bit 3-0                            | Unimplemen                                                                    | ted: Read as | '0'                             |                                    |     |            |       |  |  |

|                                    |                                                                               |              |                                 |                                    |     |            |       |  |  |

### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

**Note 1:** This single bit enables and disables all four DMA channels.

## 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function,  $TRISx = 0 \ge 0$ , while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**. NOTES:

| U-0                   | U-0                                                    | R-0                                                                        | R-0   | R-0               | R-0             | R-0                | R-0   |  |  |

|-----------------------|--------------------------------------------------------|----------------------------------------------------------------------------|-------|-------------------|-----------------|--------------------|-------|--|--|

| _                     | —                                                      | FBP5                                                                       | FBP4  | FBP3              | FBP2            | FBP1               | FBP0  |  |  |

| bit 15                |                                                        |                                                                            | •     |                   |                 | ·                  | bit   |  |  |

|                       |                                                        |                                                                            |       |                   |                 |                    |       |  |  |

| U-0                   | U-0                                                    | R-0                                                                        | R-0   | R-0               | R-0             | R-0                | R-0   |  |  |

|                       | —                                                      | FNRB5                                                                      | FNRB4 | FNRB3             | FNRB2           | FNRB1              | FNRB0 |  |  |

| bit 7                 |                                                        |                                                                            |       |                   |                 |                    | bit   |  |  |

| Lowende               |                                                        |                                                                            |       |                   |                 |                    |       |  |  |

| Legend:<br>R = Readab | le bit                                                 | W = Writable                                                               | bit   | U = Unimpler      | nented bit, rea | nd as '0'          |       |  |  |

| -n = Value at POR     |                                                        | '1' = Bit is set                                                           |       | '0' = Bit is clea |                 | x = Bit is unknown |       |  |  |

|                       |                                                        |                                                                            |       |                   |                 |                    |       |  |  |

| bit 15-14             | Unimpleme                                              | nted: Read as '                                                            | 0'    |                   |                 |                    |       |  |  |

| bit 13-8              | FBP<5:0>: FIFO Buffer Pointer bits                     |                                                                            |       |                   |                 |                    |       |  |  |

|                       | 011111 = RB31 buffer                                   |                                                                            |       |                   |                 |                    |       |  |  |

|                       | 011110 <b>=</b> R                                      | B30 buffer                                                                 |       |                   |                 |                    |       |  |  |

|                       | •                                                      |                                                                            |       |                   |                 |                    |       |  |  |

|                       |                                                        |                                                                            |       |                   |                 |                    |       |  |  |

|                       | •                                                      |                                                                            |       |                   |                 |                    |       |  |  |

|                       | 000001 = TF                                            | RB1 buffer                                                                 |       |                   |                 |                    |       |  |  |

|                       | 000001 = TF<br>000000 = TF                             |                                                                            |       |                   |                 |                    |       |  |  |

| bit 7-6               | 000000 = TF                                            |                                                                            | 0'    |                   |                 |                    |       |  |  |

| bit 7-6<br>bit 5-0    | 000000 = TR<br>Unimplement                             | RB0 buffer                                                                 |       | ter bits          |                 |                    |       |  |  |

|                       | 000000 = TF<br>Unimplement<br>FNRB<5:0>:<br>011111 = R | RB0 buffer<br><b>nted:</b> Read as 6<br>FIFO Next Rea<br>B31 buffer        |       | ter bits          |                 |                    |       |  |  |

|                       | 000000 = Tf<br>Unimplemen<br>FNRB<5:0>:                | RB0 buffer<br><b>nted:</b> Read as 6<br>FIFO Next Rea<br>B31 buffer        |       | ter bits          |                 |                    |       |  |  |

|                       | 000000 = TF<br>Unimplement<br>FNRB<5:0>:<br>011111 = R | RB0 buffer<br><b>nted:</b> Read as 6<br>FIFO Next Rea<br>B31 buffer        |       | ter bits          |                 |                    |       |  |  |

|                       | 000000 = TF<br>Unimplement<br>FNRB<5:0>:<br>011111 = R | RB0 buffer<br><b>nted:</b> Read as 6<br>FIFO Next Rea<br>B31 buffer        |       | ter bits          |                 |                    |       |  |  |

|                       | 000000 = TF<br>Unimplement<br>FNRB<5:0>:<br>011111 = R | RB0 buffer<br>nted: Read as '<br>FIFO Next Rea<br>B31 buffer<br>B30 buffer |       | ter bits          |                 |                    |       |  |  |

## REGISTER 22-5: CxFIFO: CANx FIFO STATUS REGISTER

| REGISTER                | 24-2: ADx                                                                                                                                                                                      | CON2: ADCx (         | CONTROL RI     | EGISTER 2        |                     |                 |       |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------------------|---------------------|-----------------|-------|--|--|--|

| R/W-0                   | R/W-0                                                                                                                                                                                          | R/W-0                | U-0            | U-0              | R/W-0               | R/W-0           | R/W-0 |  |  |  |

| VCFG2 <sup>(1)</sup>    | VCFG1 <sup>(1)</sup>                                                                                                                                                                           | VCFG0 <sup>(1)</sup> | —              | _                | CSCNA               | CHPS1           | CHPS0 |  |  |  |

| bit 15                  |                                                                                                                                                                                                |                      |                |                  |                     |                 | bit   |  |  |  |

| R-0                     | R/W-0                                                                                                                                                                                          | R/W-0                | R/W-0          | R/W-0            | R/W-0               | R/W-0           | R/W-0 |  |  |  |

| BUFS                    | SMPI4                                                                                                                                                                                          | SMPI3                | SMPI2          | SMPI1            | SMPI0               | BUFM            | ALTS  |  |  |  |

| bit 7                   |                                                                                                                                                                                                |                      | 0111112        |                  |                     | Dor m           | bit   |  |  |  |

| <u> </u>                |                                                                                                                                                                                                |                      |                |                  |                     |                 |       |  |  |  |

| Legend:<br>R = Readable | - hit                                                                                                                                                                                          | M = Mritabla k       |                |                  | manted hit read     |                 |       |  |  |  |

|                         |                                                                                                                                                                                                | W = Writable k       | DIL            | •                | nented bit, read    |                 |       |  |  |  |

| -n = Value at           | PUR                                                                                                                                                                                            | '1' = Bit is set     |                | '0' = Bit is cle | ared                | x = Bit is unkr | iown  |  |  |  |

| bit 15-13               | VCFG<2:0>                                                                                                                                                                                      | Converter Volta      | ge Reference   | Configuration I  | oits <sup>(1)</sup> |                 |       |  |  |  |

|                         | Value                                                                                                                                                                                          | VREFH                | VREFL          |                  |                     |                 |       |  |  |  |

|                         | xxx                                                                                                                                                                                            | AVdd                 | AVss           |                  |                     |                 |       |  |  |  |

| bit 12-11               | Unimpleme                                                                                                                                                                                      | ented: Read as '0    | ,              |                  |                     |                 |       |  |  |  |

| bit 10                  | CSCNA: Inp                                                                                                                                                                                     | out Scan Select b    | it             |                  |                     |                 |       |  |  |  |

|                         | 1 = Scans inputs for CH0+ during Sample MUX A                                                                                                                                                  |                      |                |                  |                     |                 |       |  |  |  |

|                         | 0 = Does not scan inputs                                                                                                                                                                       |                      |                |                  |                     |                 |       |  |  |  |

| bit 9-8                 | CHPS<1:0>: Channel Select bits                                                                                                                                                                 |                      |                |                  |                     |                 |       |  |  |  |

|                         | In 12-Bit Mode (AD21B = 1), CHPS<1:0> bits are Unimplemented and are Read as '0':                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | 1x = Converts CH0, CH1, CH2 and CH3<br>01 = Converts CH0 and CH1                                                                                                                               |                      |                |                  |                     |                 |       |  |  |  |

|                         | 00 = Conve                                                                                                                                                                                     |                      |                |                  |                     |                 |       |  |  |  |

| bit 7                   | <b>BUFS:</b> Buffer Fill Status bit (only valid when BUFM = 1)                                                                                                                                 |                      |                |                  |                     |                 |       |  |  |  |

|                         | 1 = ADCx is currently filling the second half of the buffer; the user application should access data in th                                                                                     |                      |                |                  |                     |                 |       |  |  |  |

|                         | first half of the buffer                                                                                                                                                                       |                      |                |                  |                     |                 |       |  |  |  |

|                         | 0 = ADCx is currently filling the first half of the buffer; the user application should access data in th<br>second half of the buffer                                                         |                      |                |                  |                     |                 |       |  |  |  |

|                         |                                                                                                                                                                                                |                      |                |                  |                     |                 |       |  |  |  |

| bit 6-2                 | SMPI<4:0>: Increment Rate bits<br>When ADDMAEN = 0:                                                                                                                                            |                      |                |                  |                     |                 |       |  |  |  |

|                         | $\frac{\text{VNEH ADDIVIAEN} = 0}{\text{x}1111}$ = Generates interrupt after completion of every 16th sample/conversion operation                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | x1110 = Generates interrupt after completion of every 15th sample/conversion operation                                                                                                         |                      |                |                  |                     |                 |       |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | •<br>x0001 = Generates interrupt after completion of every 2nd sample/conversion operation                                                                                                     |                      |                |                  |                     |                 |       |  |  |  |

|                         | x0000 = Generates interrupt after completion of every sample/conversion operation                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | When ADDMAEN = 1:                                                                                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | 11111 = Increments the DMA address after completion of every 32nd sample/conversion operation<br>11110 = Increments the DMA address after completion of every 31st sample/conversion operation |                      |                |                  |                     |                 |       |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                |                  |                     |                 |       |  |  |  |

|                         | 00001 = Increments the DMA address after completion of every 2nd sample/conversion operation                                                                                                   |                      |                |                  |                     |                 |       |  |  |  |

|                         |                                                                                                                                                                                                | crements the DMA     |                |                  |                     |                 |       |  |  |  |

| Note 1. Th              |                                                                                                                                                                                                | H Input is connec    | ted to AVop ar | nd the VREEL in  | inut is connecte    | d to AVss       |       |  |  |  |

### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2

**Note 1:** The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

## 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 29.7 MPLAB REAL ICE In-Circuit Emulator System