Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm102-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

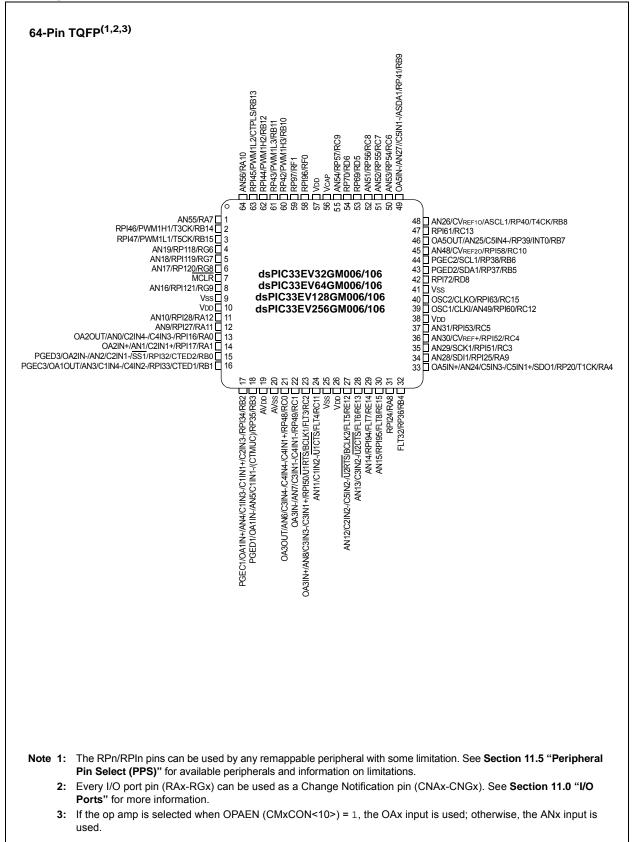

#### **Pin Diagrams (Continued)**

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = Overflow has not occurred for signed arithmetic                                                                                                                                                          |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                              |

| Note 1. | The IPI <2:0> hits are concatenated with the IPI 3 hit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                      |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |                 |        |         |        |        |       | -     |                  |       | -     |       |         |        |        | -      |               |

|-------------|-------|--------|-----------------|--------|---------|--------|--------|-------|-------|------------------|-------|-------|-------|---------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN            | WRERR  | NVMSIDL | _      | _      | RPDF  | URERR | _                | —     | _     | _     | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        | NVMADR<15:0> 00 |        |         |        |        |       |       |                  |       | 0000  |       |         |        |        |        |               |

| NVMADRU     | 072C  | _      | _               | _      | _       |        | _      | _     | _     | NVMADRU<23:16>   |       |       |       | 0000    |        |        |        |               |

| NVMKEY      | 072E  | _      | _               | _      | _       |        | _      | _     | _     |                  |       |       | NVMK  | EY<7:0> |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |                 |        |         |        |        |       | NVMSF | RCADR<15:        | 1>    |       |       |         |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _               | _      | _       |        | _      | _     | _     | NVMSRCADR<23:16> |       |       |       |         | 0000   |        |        |               |

| Lonondy     |       |        |                 |        |         |        |        |       |       |                  |       |       |       |         |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8       | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|-------------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS       | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0       | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0     | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |             |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       | TUN<5:0> 00 |          |          |        |           | 0000    |         |         |         |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

#### TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | —     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

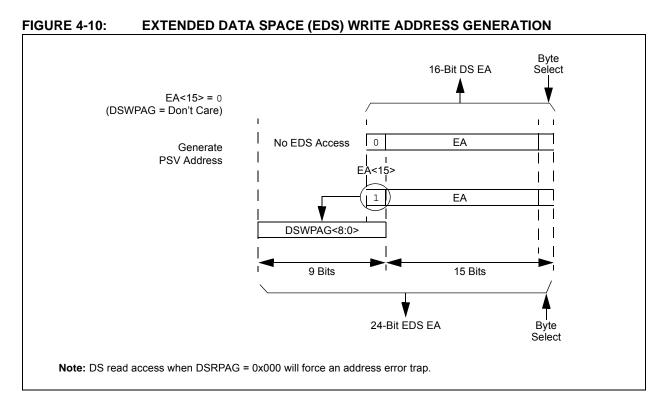

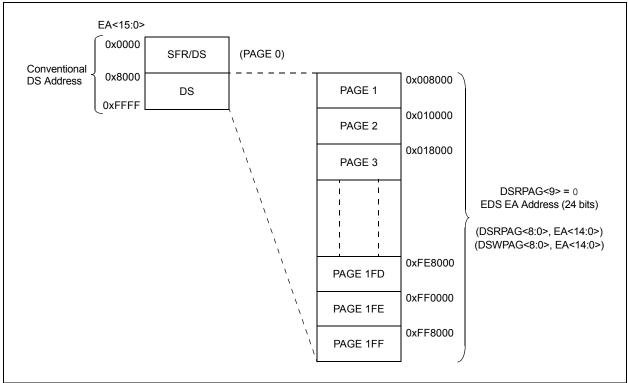

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Figure 4-11.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, therefore, the DSWPAG is dedicated to DS, including EDS. The Data Space and EDS can be read from and written to using DSRPAG and DSWPAG, respectively.

#### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

## **REGISTER 9-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0        | U-0             | U-0              | U-0             | U-0              | U-0      | R/W-0   |

|--------------|------------|-----------------|------------------|-----------------|------------------|----------|---------|

|              | —          | —               | _                | —               | —                | —        | PLLDIV8 |

| bit 15       |            |                 |                  |                 |                  |          | bit 8   |

|              |            |                 |                  |                 |                  |          |         |

| R/W-0        | R/W-0      | R/W-1           | R/W-1            | R/W-0           | R/W-0            | R/W-0    | R/W-0   |

|              |            |                 | PLLD             | IV<7:0>         |                  |          |         |

| bit 7        |            |                 |                  |                 |                  |          | bit 0   |

|              |            |                 |                  |                 |                  |          |         |

| Legend:      |            |                 |                  |                 |                  |          |         |

| R = Readab   | ole bit    | W = Writable    | bit              | U = Unimpler    | mented bit, read | as '0'   |         |

| -n = Value a | at POR     | :               | '0' = Bit is cle | ared            | x = Bit is unk   | nown     |         |

|              |            |                 |                  |                 |                  |          |         |

| bit 15-9     | Unimplemer | nted: Read as ' | 0'               |                 |                  |          |         |

| bit 8-0      | PLLDIV<8:0 | >: PLL Feedba   | ck Divisor bits  | s (also denoted | as 'M', PLL mul  | tiplier) |         |

|              | 111111111  | = 513           |                  |                 |                  |          |         |

|              | •          |                 |                  |                 |                  |          |         |

|              | •          |                 |                  |                 |                  |          |         |

|              | 000110000  | = 50 (default)  |                  |                 |                  |          |         |

|              | •          |                 |                  |                 |                  |          |         |

|              | •          |                 |                  |                 |                  |          |         |

|              | •          |                 |                  |                 |                  |          |         |

|              | 000000010  |                 |                  |                 |                  |          |         |

|              | 000000000  | -               |                  |                 |                  |          |         |

|              |            |                 |                  |                 |                  |          |         |

## REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

| R/W-0         | R/W-0                                                                                                                    | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|------------------|------------------|--------------------|--------|--|--|--|

| FLT2R7        | FLT2R6                                                                                                                   | FLT2R5                             | FLT2R4 | FLT2R3           | FLT2R2           | FLT2R1             | FLT2R0 |  |  |  |

| bit 15        | ·                                                                                                                        |                                    |        |                  |                  |                    | bit 8  |  |  |  |

| R/W-0         | R/W-0                                                                                                                    | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |  |  |  |

| FLT1R7        | FLT1R6                                                                                                                   | FLT1R5                             | FLT1R4 | FLT1R3           | FLT1R2           | FLT1R1             | FLT1R0 |  |  |  |

| oit 7         | I                                                                                                                        |                                    |        |                  |                  |                    | bit 0  |  |  |  |

|               |                                                                                                                          |                                    |        |                  |                  |                    |        |  |  |  |

| _egend:       |                                                                                                                          |                                    |        |                  |                  |                    |        |  |  |  |

| R = Readable  | e bit                                                                                                                    | W = Writable                       | bit    | U = Unimpler     | nented bit, read | <b>d as</b> '0'    |        |  |  |  |

| -n = Value at | POR                                                                                                                      | '1' = Bit is set                   | t      | '0' = Bit is cle | ared             | x = Bit is unknown |        |  |  |  |

| bit 15-8      | FLT2R<7:0>: Assign PWM Fault 2 (FLT2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                                    |        |                  |                  |                    |        |  |  |  |

|               | (see Table 11-2 for input pin selection numbers)                                                                         |                                    |        |                  |                  |                    |        |  |  |  |

|               | •                                                                                                                        | Input tied to R                    | PI181  |                  |                  |                    |        |  |  |  |

|               | •                                                                                                                        |                                    |        |                  |                  |                    |        |  |  |  |

|               | •                                                                                                                        |                                    |        |                  |                  |                    |        |  |  |  |

|               |                                                                                                                          | Input tied to C<br>Input tied to V |        |                  |                  |                    |        |  |  |  |

| bit 7-0       |                                                                                                                          | Assign PWM<br>-2 for input pin     |        |                  | onding RPn Pi    | n bits             |        |  |  |  |

|               | •                                                                                                                        | Input tied to R                    |        | ,                |                  |                    |        |  |  |  |

|               | •                                                                                                                        |                                    |        |                  |                  |                    |        |  |  |  |

|               | •                                                                                                                        |                                    |        |                  |                  |                    |        |  |  |  |

|               |                                                                                                                          |                                    |        |                  |                  |                    |        |  |  |  |

|               | 00000001 = Input tied to CMP1                                                                                            |                                    |        |                  |                  |                    |        |  |  |  |

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

00000000 = Input tied to Vss

#### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup>

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(3)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

## 19.2 I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0   | R/S-1                 | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------------------|--------|-------|--------|-------|

| I2CEN  |     | I2CSIDL | SCLREL <sup>(1)</sup> | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |                       |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 | •     |       | •         |           | •         |           | bit 0     |

| Legend:           | S = Settable bit | HC = Hardware Clearable bit   |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | <b>as</b> '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | k = Bit is unknown |

| bit 15  | I2CEN: I2Cx Enable bit (writable from SW only)                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables the I<sup>2</sup>C module and configures the SDAx and SCLx pins as serial port pins</li> <li>0 = Disables the I<sup>2</sup>C module and all I<sup>2</sup>C pins are controlled by port functions</li> </ul> |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                       |

| bit 13  | I2CSIDL: I2Cx Stop in Idle Mode bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                      |

| bit 12  | SCLREL: SCLx Release Control bit (I <sup>2</sup> C Slave mode only) <sup>(1)</sup>                                                                                                                                               |

|         | Module resets and (I2CEN = 0) sets SCLREL = 1.                                                                                                                                                                                   |

|         | $\frac{\text{If STREN = }0}{2}$                                                                                                                                                                                                  |

|         | 1 = Releases clock                                                                                                                                                                                                               |

|         | 0 = Forces clock low (clock stretch)                                                                                                                                                                                             |

|         | If STREN = 1:<br>1 = Releases clock                                                                                                                                                                                              |

|         | 0 = Holds clock low (clock stretch); user may program this bit to '0', clock stretch at the next SCLx low                                                                                                                        |

| bit 11  | STRICT: Strict I <sup>2</sup> C Reserved Address Rule Enable bit                                                                                                                                                                 |

|         | 1 = Strict reserved addressing is enforced                                                                                                                                                                                       |

|         | In Slave mode, the device does not respond to reserved address space and addresses falling in that category are NACKed.                                                                                                          |

|         | 0 = Reserved addressing would be Acknowledged                                                                                                                                                                                    |

|         | In Slave mode, the device will respond to an address falling in the reserved address space. When there is a match with any of the reserved addresses, the device will generate an ACK.                                           |

| bit 10  | A10M: 10-Bit Slave Address Flag bit                                                                                                                                                                                              |

|         | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                                                                    |

| bit 9   | DISSLW: Slew Rate Control Disable bit                                                                                                                                                                                            |

|         | <ul> <li>1 = Slew rate control is disabled for Standard Speed mode (100 kHz, also disabled for 1 MHz mode)</li> <li>0 = Slew rate control is enabled for High-Speed mode (400 kHz)</li> </ul>                                    |

| bit 8   | SMEN: SMBus Input Levels Enable bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Enables the input logic so thresholds are compliant with the SMBus specification</li> <li>0 = Disables the SMBus-specific inputs</li> </ul>                                                                         |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                 |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

#### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 1 | <ul> <li>BUFM: Buffer Fill Mode Select bit</li> <li>1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt</li> <li>0 = Always starts filling the buffer from the Start address</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <ul> <li>ALTS: Alternate Input Sample Mode Select bit</li> <li>1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample</li> <li>0 = Always uses channel input selects for Sample MUX A</li> </ul>                         |

Note 1: The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

| Base<br>Instr<br># | Assembly<br>Mnemonic                                     | Assembly Syntax Description |                           |                                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------------------------------------------|-----------------------------|---------------------------|-------------------------------------------------|---------------|----------------|--------------------------|

| 8                  | BSW                                                      | BSW.C                       | Ws,Wb                     | Write C bit to Ws <wb></wb>                     | 1             | 1              | None                     |

|                    |                                                          | BSW.Z                       | Ws,Wb                     | Write Z bit to Ws <wb></wb>                     | 1             | 1              | None                     |

| 9                  | BTG                                                      | BTG                         | f,#bit4                   | Bit Toggle f                                    | 1             | 1              | None                     |

|                    |                                                          | BTG                         | Ws,#bit4                  | Bit Toggle Ws                                   | 1             | 1              | None                     |

| 10                 | BTSC     BTSC     f, #bit4     Bit Test f, Skip if Clear |                             | Bit Test f, Skip if Clear | 1                                               | 1<br>(2 or 3) | None           |                          |

|                    |                                                          | BTSC                        | Ws,#bit4                  | Bit Test Ws, Skip if Clear                      | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                                                     | BTSS                        | f,#bit4                   | Bit Test f, Skip if Set                         | 1             | 1<br>(2 or 3)  | None                     |

|                    |                                                          | BTSS                        | Ws,#bit4                  | Bit Test Ws, Skip if Set                        | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                                                     | BTST                        | f,#bit4                   | Bit Test f                                      | 1             | 1              | Z                        |

|                    |                                                          | BTST.C                      | Ws,#bit4                  | Bit Test Ws to C                                | 1             | 1              | С                        |

|                    |                                                          | BTST.Z                      | Ws,#bit4                  | Bit Test Ws to Z                                | 1             | 1              | Z                        |

|                    |                                                          | BTST.C                      | Ws,Wb                     | Bit Test Ws <wb> to C</wb>                      | 1             | 1              | С                        |

|                    |                                                          | BTST.Z                      | Ws,Wb                     | Bit Test Ws <wb> to Z</wb>                      | 1             | 1              | Z                        |

| 13                 | BTSTS                                                    | BTSTS                       | f,#bit4                   | Bit Test then Set f                             | 1             | 1              | Z                        |

|                    |                                                          | BTSTS.C                     | Ws,#bit4                  | Bit Test Ws to C, then Set                      | 1             | 1              | С                        |

|                    |                                                          | BTSTS.Z                     | Ws,#bit4                  | Bit Test Ws to Z, then Set                      | 1             | 1              | Z                        |

| 14                 | CALL                                                     | CALL                        | lit23                     | Call subroutine                                 | 2             | 4              | SFA                      |

|                    |                                                          | CALL                        | Wn                        | Call indirect subroutine                        | 1             | 4              | SFA                      |

|                    |                                                          | CALL.L                      | Wn                        | Call indirect subroutine (long address)         | 1             | 4              | SFA                      |

| 15                 | CLR                                                      | CLR                         | f                         | f = 0x0000                                      | 1             | 1              | None                     |

|                    |                                                          | CLR                         | WREG                      | WREG = 0x0000                                   | 1             | 1              | None                     |

|                    |                                                          | CLR                         | Ws                        | Ws = 0x0000                                     | 1             | 1              | None                     |

|                    |                                                          | CLR                         | Acc,Wx,Wxd,Wy,Wyd,AWB     | Clear Accumulator                               | 1             | 1              | OA,OB,SA,<br>SB          |

| 16                 | CLRWDT                                                   | CLRWDT                      |                           | Clear Watchdog Timer                            | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                                                      | COM                         | f                         | $f = \overline{f}$                              | 1             | 1              | N,Z                      |

|                    |                                                          | COM                         | f,WREG                    | WREG = f                                        | 1             | 1              | N,Z                      |

|                    |                                                          | COM                         | Ws,Wd                     | $Wd = \overline{Ws}$                            | 1             | 1              | N,Z                      |

| 18                 | CP                                                       | CP                          | f                         | Compare f with WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                          | CP                          | Wb,#lit8                  | Compare Wb with lit8                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                          | CP                          | Wb,Ws                     | Compare Wb with Ws (Wb – Ws)                    | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                                                      | CP0                         | f                         | Compare f with 0x0000                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                          | CP0                         | Ws                        | Compare Ws with 0x0000                          | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                                                      | CPB                         | f                         | Compare f with WREG, with Borrow                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                          | CPB                         | Wb,#lit8                  | Compare Wb with lit8, with Borrow               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                          | CPB                         | Wb,Ws                     | Compare Wb with Ws, with Borrow $(Wb - Ws - C)$ | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                                                    | CPSEQ                       | Wb,Wn                     | Compare Wb with Wn, skip if =                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBEQ                                                    | CPBEQ                       | Wb,Wn,Expr                | Compare Wb with Wn, branch if =                 | 1             | 1 (5)          | None                     |

| 22                 | CPSGT                                                    | CPSGT                       | Wb,Wn                     | Compare Wb with Wn, skip if >                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBGT                                                    | CPBGT                       | Wb,Wn,Expr                | Compare Wb with Wn, branch if >                 | 1             | 1 (5)          | None                     |

| 23                 | CPSLT                                                    | CPSLT                       | Wb,Wn                     | Compare Wb with Wn, skip if <                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBLT                                                    | CPBLT                       | Wb,Wn,Expr                | Compare Wb with Wn, branch if <                 | 1             | 1 (5)          | None                     |

| 24                 | CPSNE                                                    | CPSNE                       | Wb,Wn                     | Compare Wb with Wn, skip if ≠                   | 1             | 1<br>(2 or 3)  | None                     |

|                    |                                                          |                             |                           |                                                 | -             | ,              |                          |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                          | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|--------------------|----------------------|--------------------------|-----------------|---------------------------------------------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 53                 | MUL                  | MUL.SS                   | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SS                   | Wb,Ws,Acc       | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SU                   | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SU                   | Wb,Ws,Acc       | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SU                   | Wb,#lit5,Acc    | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.US                   | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.US                   | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.UU                   | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.UU                   | Wb,#lit5,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.UU                   | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MULW.SS                  | Wb,Ws,Wnd       | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MULW.SU                  | Wb,Ws,Wnd       | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MULW.US                  | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MULW.UU                  | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SU                   | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.SU                   | Wb,#lit5,Wnd    | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.UU                   | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL.UU                   | Wb,#lit5,Wnd    | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | MUL                      | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 54                 | NEG                  | NEG                      | Acc             | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                    |                      | NEG                      | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                    |                      | NEG                      | f,WREG          | WREG = $f + 1$                                    | 1             | 1              | C,DC,N,OV,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                    |                      | NEG                      | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 55                 | NOP                  | NOP                      |                 | No Operation                                      | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | NOPR                     |                 | No Operation                                      | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 56                 | POP                  | POP                      | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | POP                      | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | POP.D                    | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | POP.S                    |                 | Pop Shadow Registers                              | 1             | 1              | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 57                 | PUSH                 | PUSH                     | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | I         None           1         OA,OB,OAB,<br>SA,SB,SAB           1         C,DC,N,OV,Z           1         C,DC,N,OV,Z           1         None           1         None |  |  |  |  |  |  |

|                    |                      | PUSH                     | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | NoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneOA,OB,OAB,SA,SBC,DC,N,OV,ZC,DC,N,OV,ZC,DC,N,OV,ZNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNoneNone                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                    |                      | PUSH.D                   | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    |                      | PUSH.S                   |                 | Push Shadow Registers                             | 1             | 1              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 58                 | PWRSAV               | PWRSAV                   | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |