Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm102-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                 | R/W-0                                                | EGISTER             | R-0             | R-0             | R-0        |

|---------------------|------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|-----------------|------------|

| VAR                 | 0-0                          | US1                                                   | US0                                                  | EDT <sup>(1)</sup>  | DL2             | DL1             | R-0<br>DL0 |

| pit 15              | _                            | 031                                                   | 030                                                  | EDI                 | DL2             |                 | bLU        |

| R/W-0               | R/W-0                        | R/W-1                                                 | R/W-0                                                | R/C-0               | R-0             | R/W-0           | R/W-0      |

| SATA                | SATB                         | SATDW                                                 | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA             | RND             | IF         |

| bit 7               | SAID                         | SAIDW                                                 | ACCOAL                                               | IF LOV /            | SFA             | RIND            | bit        |

| Legend:             |                              | C = Clearable                                         | - bit                                                |                     |                 |                 |            |

| R = Readable        | bit                          | W = Writable                                          |                                                      | U = Unimplem        | onted hit rea   | d as '0'        |            |

| -n = Value at F     |                              | '1' = Bit is set                                      |                                                      | '0' = Bit is clea   |                 | x = Bit is unkr |            |

|                     | -                            |                                                       |                                                      |                     |                 |                 |            |

| bit 15              | 1 = Variable e               | exception proce                                       | ocessing Later<br>essing latency                     | is enabled          |                 |                 |            |

| L:4 4 4             |                              |                                                       | sing latency is                                      | enabled             |                 |                 |            |

| bit 14<br>bit 13-12 | •                            | ted: Read as '                                        | 0<br>igned/Signed (                                  | Control hito        |                 |                 |            |

|                     | 01 = DSP eng<br>00 = DSP eng | gine multiplies<br>gine multiplies<br>gine multiplies | are signed                                           |                     |                 |                 |            |

| bit 11              |                              |                                                       | ation Control bi<br>e $DO$ loop at th                | e end of the cu     | rrent loop iter | ation           |            |

| bit 10-8            | 111 = 7 DO lo                | ops are active                                        |                                                      | ts                  |                 |                 |            |

| bit 7               |                              | Saturation En                                         |                                                      |                     |                 |                 |            |

|                     |                              | ator A saturatio<br>ator A saturatio                  |                                                      |                     |                 |                 |            |

| bit 6               | 1 = Accumula                 | Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |                 |                 |            |

| bit 5               | 1 = Data Space               | ce write satura                                       | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit      |                 |            |

| bit 4               | -                            | cumulator Satu                                        | ration Mode S                                        |                     |                 |                 |            |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| TABLE 4-9:       CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1 FOR dsPIC33EVXXXGM10X DEVICES |       |          |          |          |          |          |          |          |          |          |          |          |          |          |            |          |          |               |

|------------------------------------------------------------------------------------------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name                                                                                    | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1                                                                                        | 0400  | _        | —        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0   | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | —          | -        | WIN      | 0480          |

| C1CTRL2                                                                                        | 0402  | _        | —        | —        | —        | _        | —        | —        | —        | —        | —        | _        |          | l        | DNCNT<4:0> |          |          | 0000          |

| C1VEC                                                                                          | 0404  | —        | _        | —        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0  | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0000          |

| C1FCTRL                                                                                        | 0406  | DMABS2   | DMABS1   | DMABS0   | _        | _        | —        | —        | —        | _        | —        | FSA5     | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO                                                                                         | 0408  | -        | —        | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0     | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF                                                                                         | 040A  | -        | —        | ТХВО     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN    | IVRIF    | WAKIF    | ERRIF    | —        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE                                                                                         | 040C  |          | —        | —        | -        | —        | —        | —        | —        | IVRIE    | WAKIE    | ERRIE    | —        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC                                                                                           | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1                                                                                         | 0410  |          | —        | —        | -        | —        | —        | —        | —        | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2                                                                                         | 0412  |          | WAKFIL   | —        | -        | —        | SEG2PH2  | SEG2PH1  | SEG2PH0  | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1                                                                                         | 0414  |          |          |          |          |          |          |          | FLTE     | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1                                                                                     | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0   | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2                                                                                     | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0  | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-10: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14                          | Bit 13                                                                                                              | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7       | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|--------|--------|---------|---------------|-------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |        |                                 |                                                                                                                     |        |        |        | Se      | ee definition | when WIN :  | = x     |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |        |                                 |                                                                                                                     |        |        |        |         | RXFUL         | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C1RXFUL2    | 0422          |        |                                 |                                                                                                                     |        |        |        |         | RXFUL         | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1RXOVF1    | 0428          |        |                                 | RXOVF<15:0> 0000                                                                                                    |        |        |        |         |               |             |         |         |        |        |        |         |         |               |

| C1RXOVF2    | 042A          |        | RXOVF<31:16>                    |                                                                                                                     |        |        |        |         |               |             |         |         |        | 0000   |        |         |         |               |

| C1TR01CON   | 0430          | TXEN1  | TXABT1                          | TXLARB1                                                                                                             | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0       | TXEN0       | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3  | TXABT3                          | TXLARB3                                                                                                             | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0       | TXEN2       | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5  | TXABT5                          | TXLARB5                                                                                                             | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0       | TXEN4       | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7  | TXABT7                          | TXABT7 TXLARB7 TXERR7 TXREQ7 RTREN7 TX7PR11 TX7PR10 TXEN6 TXABAT6 TXLARB6 TXER66 TXREQ6 RTREN6 TX6PR11 TX6PR10 XXXX |        |        |        |         |               |             |         |         |        |        |        |         |         |               |

| C1RXD       | 0440          |        | CAN1 Receive Data Word Register |                                                                                                                     |        |        |        |         |               |             |         |         | xxxx   |        |        |         |         |               |

| C1TXD       | 0442          |        |                                 |                                                                                                                     |        |        |        | CAN1    | Transmit Da   | ata Word Re | egister |         |        |        |        |         |         | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM002/102 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | _     | RP20R5  | RP20R4  | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  |        | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  |       | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  |        | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  |       | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  |        | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  |       | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  |        | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  |       | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR10      | 0684  |        | _      |         |         | RP176   | R<5:0>  |         |         |       | _     | _       | _       | _       | _       | _       | _       | 0000          |

| RPOR11      | 0686  |        | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |       | _     | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | _      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | _     | —     | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  | _      | _      | —       | _       | _       | _       | _       | —       | _     | _     |         |         | RP181   | R<5:0>  |         |         | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-15: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM004/104 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | -     | RP20R5  | RP20R4  | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | -     | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | -     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | -     | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  | _      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | -     | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR5       | 067A  | _      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | -     | _     | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR6       | 067C  | _      | —      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | -     | _     | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR7       | 067E  | —      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     | _     | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR10      | 0684  | —      | _      |         |         | RP176   | R<5:0>  |         |         | _     | _     | _       | _       | _       | _       | _       | _       | 0000          |

| RPOR11      | 0686  | —      | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | _     | _     | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | _      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | _     | _     | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  |        |        | —       | _       | _       | —       | _       | —       | —     |       |         |         | RP181   | R<5:0>  |         |         | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-35: PORTB REGISTER MAP FOR dsPIC33EVXXXGMX04 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|--------|-------|---------------|

| TRISB       | 0E14  |        |                 |        |        |        |        |       | TRISB<15  | :0>   |       |       |       |       |       |        |       | DF9F          |

| PORTB       | 0E16  |        |                 |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |        |       | xxxx          |

| LATB        | 0E18  |        |                 |        |        |        |        |       | LATB<15:  | 0>    |       |       |       |       |       |        |       | xxxx          |

| ODCB        | 0E1A  |        | ODCB<15:0> 0000 |        |        |        |        |       |           |       | 0000  |       |       |       |       |        |       |               |

| CNENB       | 0E1C  |        | CNIEB<15:0> 000 |        |        |        |        |       |           |       | 0000  |       |       |       |       |        |       |               |

| CNPUB       | 0E1E  |        |                 |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |        |       | 0000          |

| CNPDB       | 0E20  |        |                 |        |        |        |        |       | CNPDB<15  | 5:0>  |       |       |       |       |       |        |       | 0000          |

| ANSELB      | 0E22  | _      | _               | _      | _      | _      | _      |       | ANSB<9:7> | •     | _     | _     | _     |       | ANSB  | 8<3:0> |       | 010F          |

| SR1B        | 0E24  | _      | _               | _      | _      | _      | _      | :     | SR1B<9:7> |       | _     | _     | SR1B4 | _     | —     | _      | —     | 0000          |

| SR0B        | 0E26  | —      | -               | _      | _      | —      | —      |       | SR0B<9:7> |       |       | -     | SR0B4 |       |       | -      | _     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-36: PORTB REGISTER MAP FOR dsPIC33EVXXXGMX02 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E14  |        |                 |        |        |        |        |       | TRISB<15  | :0>   |       |       |       |       |       |       |       | DF9F          |

| PORTB       | 0E16  |        |                 |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |       |       | xxxx          |

| LATB        | 0E18  |        |                 |        |        |        |        |       | LATB<15:  | 0>    |       |       |       |       |       |       |       | xxxx          |

| ODCB        | 0E1A  |        | ODCB<15:0> 0000 |        |        |        |        |       |           |       | 0000  |       |       |       |       |       |       |               |

| CNENB       | 0E1C  |        |                 |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1E  |        |                 |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E20  |        |                 |        |        |        |        |       | CNPDB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| ANSELB      | 0E22  |        | —               | —      | —      | _      | —      |       | ANSB<9:7> | •     |       | —     | —     |       | ANSB  | <3:0> |       | 010F          |

| SR1B        | 0E24  | _      | _               | —      | —      | —      | —      |       | SR1B<9:7> |       |       | —     | SR1B4 | _     | _     |       | —     | 0000          |

| SR0B        | 0E26  |        | —               | —      | —      | _      | —      |       | SR0B<9:7> | •     |       | —     | SR0B4 | _     | _     |       | —     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

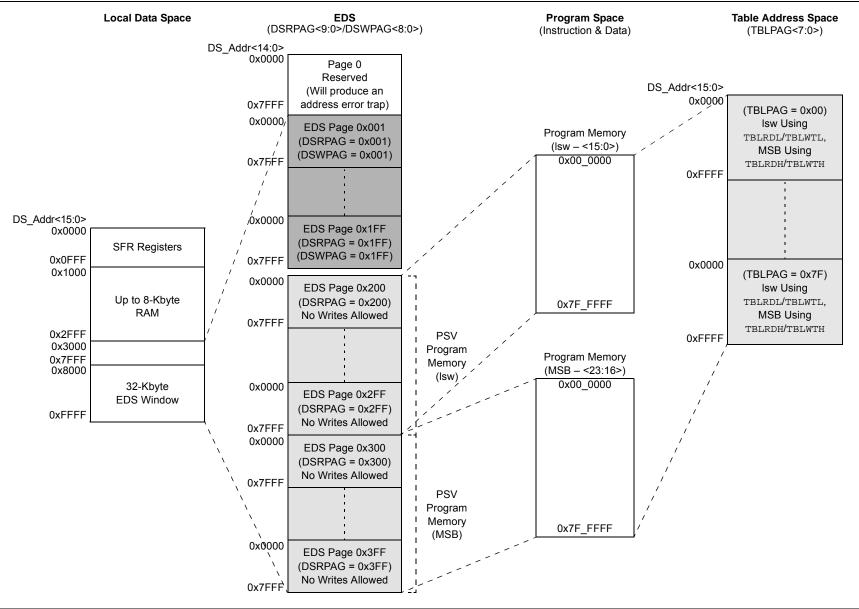

# FIGURE 4-11: PAGED DATA MEMORY SPACE

DS70005144E-page 70

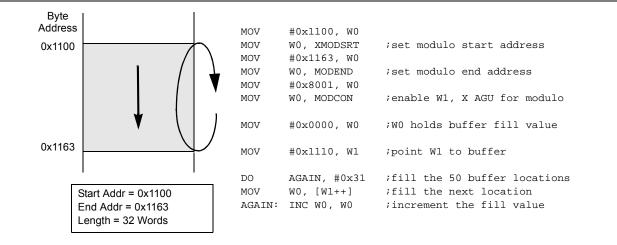

# 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the SFP and SSP, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit (MODCON<15>) is set

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

Figure 4-15 shows an example of Modulo Addressing operation.

Note: Y Data Space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

#### FIGURE 4-15: MODULO ADDRESSING OPERATION EXAMPLE

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

- Illegal Address Mode Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this device data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in the other sections of this device data sheet.

**Note:** The status bits in the RCON register should be cleared after they are read. Therefore, the next RCON register value after a device Reset is meaningful.

Note: In all types of Resets, to select the device clock source, the contents of OSCCON are initialized from the FNOSCx Configuration bits in the FOSCSEL Configuration register.

# dsPIC33EVXXXGM00X/10X FAMILY

| <b>▲</b> | Reserved                                                                                  | BSLIM<12:0>(1) + 0x000000                 |                          |

|----------|-------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------|

|          | Reserved                                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000002     |                          |

|          | Oscillator Fail Trap Vector                                                               | BSLIM<12:0>(1) + 0x000004                 |                          |

|          | Address Error Trap Vector                                                                 | BSLIM<12:0> <sup>(1)</sup> + 0x000006     |                          |

|          | Generic Hard Trap Vector                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000008     |                          |

|          | Stack Error Trap Vector                                                                   | BSLIM<12:0>(1) + 0x00000A                 |                          |

|          | Math Error Trap Vector                                                                    | BSLIM<12:0> <sup>(1)</sup> + 0x00000C     |                          |

|          | DMAC Error Trap Vector                                                                    | BSLIM<12:0> <sup>(1)</sup> + 0x00000E     |                          |

|          | Generic Soft Trap Vector                                                                  | BSLIM<12:0>(1) + 0x000010                 |                          |

|          | Reserved                                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000012     |                          |

|          | Interrupt Vector 0                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000014     |                          |

|          | Interrupt Vector 1                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000016     |                          |

|          | :                                                                                         | :                                         |                          |

|          | :                                                                                         | :                                         |                          |

|          | :                                                                                         | :                                         |                          |

| Σ        | Interrupt Vector 52                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x00007C     |                          |

|          | Interrupt Vector 53                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|          | Interrupt Vector 54                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x000080     | See Table 7-1 for        |

|          | :                                                                                         | :                                         | Interrupt Vector Details |

|          | :                                                                                         | :                                         | /                        |

|          | :                                                                                         | :                                         |                          |

|          | Interrupt Vector 116                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC     |                          |

|          | Interrupt Vector 117                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|          | Interrupt Vector 118                                                                      | BSLIM<12:0>(1) + 0x000100                 |                          |

|          | Interrupt Vector 119                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x000102     |                          |

|          | Interrupt Vector 120                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x000104     |                          |

|          | :                                                                                         | :                                         |                          |

|          | :                                                                                         | :                                         |                          |

|          | :                                                                                         | :                                         |                          |

|          | Interrupt Vector 244                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0001FC     |                          |

| V        | Interrupt Vector 245                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE     |                          |

| Note     | <ol> <li>The address depends on the si<br/>[(BSLIM&lt;12:0&gt; – 1) x 0x400] +</li> </ol> | ze of the Boot Segment defined by Offset. | y BSLIM<12:0>:           |

| R/W-0        | U-0                                                        | R/W-0         | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------------|------------------------------------------------------------|---------------|--------|---------------------|-----|-------|-------|

| VAR          | —                                                          | US1           | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15       |                                                            |               |        |                     |     |       | bit 8 |

|              |                                                            |               |        |                     |     |       |       |

| R/W-0        | R/W-0                                                      | R/W-1         | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA         | SATB                                                       | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7        |                                                            |               |        |                     |     |       | bit 0 |

|              |                                                            |               |        |                     |     |       |       |

| Legend:      |                                                            | C = Clearable | e bit  |                     |     |       |       |

| R = Readable | bit $W = Writable bit$ $U = Unimplemented bit read as '0'$ |               |        |                     |     |       |       |

# REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit 1 = Variable exception processing latency is enabled 0 = Fixed exception processing latency is enabled

bit 3 **IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

x = Bit is unknown

| U-0             | U-0 | U-0                                                 | U-0   | U-0     | U-0 | U-0 | U-0   |

|-----------------|-----|-----------------------------------------------------|-------|---------|-----|-----|-------|

| —               | —   | —                                                   | —     | —       |     | _   | —     |

| bit 15          |     |                                                     |       |         |     |     | bit 8 |

|                 |     |                                                     |       |         |     |     |       |

| R-0             | R-0 | R-0                                                 | R-0   | R-0     | R-0 | R-0 | R-0   |

|                 |     |                                                     | DSADR | <23:16> |     |     |       |

| bit 7           |     |                                                     |       |         |     |     | bit 0 |

|                 |     |                                                     |       |         |     |     |       |

| Legend:         |     |                                                     |       |         |     |     |       |

| R = Readable bi | it  | W = Writable bit U = Unimplemented bit, read as '0' |       |         |     |     |       |

'0' = Bit is cleared

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

'1' = Bit is set

# REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0               | R-0                         | R-0 | R-0  | R-0                                     | R-0                                | R-0 | R-0   |  |

|-------------------|-----------------------------|-----|------|-----------------------------------------|------------------------------------|-----|-------|--|

|                   |                             |     | DSAI | DR<15:8>                                |                                    |     |       |  |

| bit 15            |                             |     |      |                                         |                                    |     | bit 8 |  |

|                   |                             |     |      |                                         |                                    |     |       |  |

| R-0               | R-0                         | R-0 | R-0  | R-0                                     | R-0                                | R-0 | R-0   |  |

| DSADR<7:0>        |                             |     |      |                                         |                                    |     |       |  |

| bit 7             |                             |     |      |                                         |                                    |     | bit 0 |  |

|                   |                             |     |      |                                         |                                    |     |       |  |

| Legend:           |                             |     |      |                                         |                                    |     |       |  |

| R = Readable bit  | le bit W = Writable bit U = |     |      | U = Unimplem                            | U = Unimplemented bit, read as '0' |     |       |  |

| -n = Value at POR | OR '1' = Bit is set         |     |      | '0' = Bit is cleared x = Bit is unknown |                                    |     | iown  |  |

|                   |                             |     |      |                                         |                                    |     |       |  |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS7000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

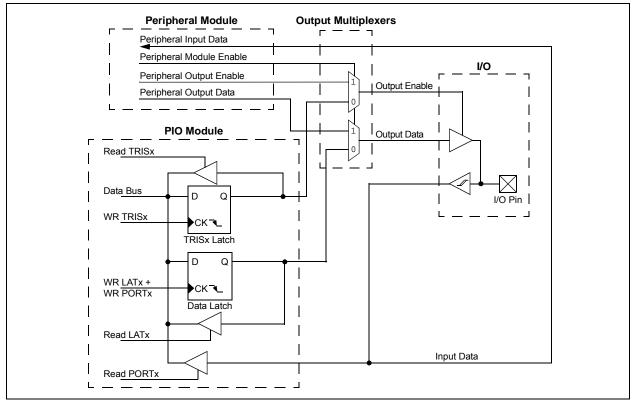

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. All the pins in the device are 5V tolerant pins.

# 11.1 Parallel I/O (PIO) Ports

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch; writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means that the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port, because there is no other competing source of output.

# FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2013-2016 Microchip Technology Inc.

# REGISTER 17-10: DTRx: PWMx DEAD-TIME REGISTER

| U-0                               | U-0   | R/W-0            | R/W-0                 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------------------------|-------|------------------|-----------------------|------------------------------------|-------|-----------------|-------|--|

| —                                 | _     |                  | DTRx<13:8>            |                                    |       |                 |       |  |

| bit 15                            |       |                  |                       |                                    |       |                 | bit 8 |  |

|                                   |       |                  |                       |                                    |       |                 |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                   |       |                  | DTR                   | x<7:0>                             |       |                 |       |  |

| bit 7                             |       |                  |                       |                                    |       |                 | bit   |  |

|                                   |       |                  |                       |                                    |       |                 |       |  |

| Legend:                           |       |                  |                       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  | bit                   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at P                   | OR    | '1' = Bit is set | s set '0' = Bit is cl |                                    | ared  | x = Bit is unkr | nown  |  |

bit 15-14Unimplemented: Read as '0'bit 13-0DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

# REGISTER 17-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|--------|-----|-------|-------|--------|----------|-------|-------|

| —      | —   |       |       | ALTDTF | Rx<13:8> |       |       |

| bit 15 |     |       |       |        |          |       | bit 8 |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| ALTDTRx<7:0> |       |       |       |       |       |       |       |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Alternate Dead-Time Value for PWMx Dead-Time Unit bits

| R/W-0                             | R/W-0                                                   | R/W-0                                 | U-0           | U-0                                     | U-0             | U-0               | U-0    |  |

|-----------------------------------|---------------------------------------------------------|---------------------------------------|---------------|-----------------------------------------|-----------------|-------------------|--------|--|

| FRMEN                             | SPIFSD                                                  | FRMPOL                                | —             | —                                       | _               | —                 |        |  |

| bit 15                            |                                                         |                                       |               |                                         |                 |                   | bit 8  |  |

|                                   |                                                         |                                       |               |                                         |                 |                   |        |  |

| U-0                               | U-0                                                     | U-0                                   | U-0           | U-0                                     | U-0             | R/W-0             | R/W-0  |  |

| —                                 | _                                                       | —                                     | _             | —                                       | _               | FRMDLY            | SPIBEN |  |

| bit 7                             |                                                         |                                       |               |                                         |                 |                   | bit 0  |  |

|                                   |                                                         |                                       |               |                                         |                 |                   |        |  |

| Legend:                           |                                                         |                                       |               |                                         |                 |                   |        |  |

| R = Readable bit W = Writable bit |                                                         |                                       | bit           | U = Unimpler                            | mented bit, rea | ad as '0'         |        |  |

| -n = Value at I                   | POR                                                     | '1' = Bit is set                      |               | '0' = Bit is cleared x = Bit is unknown |                 |                   |        |  |

|                                   |                                                         |                                       |               |                                         |                 |                   |        |  |

| bit 15                            | FRMEN: Fra                                              | med SPIx Suppo                        | ort bit       |                                         |                 |                   |        |  |

|                                   |                                                         |                                       |               | x pin is used as                        | the Frame Sy    | nc pulse input/or | utput) |  |

|                                   |                                                         | SPIx support is c                     |               |                                         |                 |                   |        |  |

| bit 14                            |                                                         | lx Frame Sync P                       |               | on Control bit                          |                 |                   |        |  |

|                                   |                                                         | ync pulse input (<br>ync pulse output |               |                                         |                 |                   |        |  |

| bit 13                            |                                                         | ame Sync Pulse                        | . ,           |                                         |                 |                   |        |  |

| DIL 13                            |                                                         | ync pulse is activ                    | 5             |                                         |                 |                   |        |  |

|                                   |                                                         | ync pulse is activ                    |               |                                         |                 |                   |        |  |

| bit 12-2                          |                                                         | nted: Read as '0                      |               |                                         |                 |                   |        |  |

| bit 1                             | •                                                       | ame Sync Pulse                        |               | t bit                                   |                 |                   |        |  |

|                                   | 1 = Frame Sync pulse coincides with the first bit clock |                                       |               |                                         |                 |                   |        |  |

|                                   | 0 = Frame Sync pulse precedes the first bit clock       |                                       |               |                                         |                 |                   |        |  |

| bit 0                             | SPIBEN: SP                                              | Ix Enhanced But                       | ffer Enable b | bit                                     |                 |                   |        |  |

|                                   | 1 = Enhanced buffer is enabled                          |                                       |               |                                         |                 |                   |        |  |

|                                   | 0 = Enhanced buffer is disabled (Standard mode)         |                                       |               |                                         |                 |                   |        |  |

|                                   |                                                         |                                       |               |                                         |                 |                   |        |  |

# REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

# REGISTER 22-24: CxRXOVF1: CANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0 | R/C-0        | R/C-0             | R/C-0          | R/C-0              | R/C-0 | R/C-0 |

|---------|-------|--------------|-------------------|----------------|--------------------|-------|-------|

|         |       |              | RXOVF             | -<15:8>        |                    |       |       |

| bit 15  |       |              |                   |                |                    |       | bit 8 |

|         |       |              |                   |                |                    |       |       |

| R/C-0   | R/C-0 | R/C-0        | R/C-0             | R/C-0          | R/C-0              | R/C-0 | R/C-0 |

|         |       |              | RXOV              | F<7:0>         |                    |       |       |

| bit 7   |       |              |                   |                |                    |       | bit 0 |

|         |       |              |                   |                |                    |       |       |

| Legend: |       | C = Writable | bit, but only '0' | can be writter | n to clear the bit |       |       |

|         |       |              |                   |                |                    |       |       |

| Logena.           | $\mathbf{O} = \mathbf{V}$ include bit, but only $\mathbf{O}$ |                             |                    |

|-------------------|--------------------------------------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                             | U = Unimplemented bit, read | <b>i as</b> '0'    |

| -n = Value at POR | '1' = Bit is set                                             | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

# REGISTER 22-25: CxRXOVF2: CANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0                                   | R/C-0           | R/C-0     | R/C-0 |  |

|-----------------|-------|------------------|-----------------|-----------------------------------------|-----------------|-----------|-------|--|

|                 |       |                  | RXOV            | F<31:24>                                |                 |           |       |  |

| bit 15          |       |                  |                 |                                         |                 |           | bit 8 |  |

|                 |       |                  |                 |                                         |                 |           |       |  |

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0                                   | R/C-0           | R/C-0     | R/C-0 |  |

|                 |       |                  | RXOV            | F<23:16>                                |                 |           |       |  |

| bit 7           |       |                  |                 |                                         |                 |           | bit 0 |  |

|                 |       |                  |                 |                                         |                 |           |       |  |

| Legend:         |       | C = Writable b   | it, but only '( | )' can be written                       | to clear the b  | bit       |       |  |

| R = Readable    | bit   | W = Writable b   | bit             | U = Unimplen                            | nented bit, rea | ad as '0' |       |  |

| -n = Value at P | 'OR   | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |

bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

| REGISTER                | 24-2: ADx            | CON2: ADCx (                             | CONTROL RI      | EGISTER 2         |                     |                 |                |

|-------------------------|----------------------|------------------------------------------|-----------------|-------------------|---------------------|-----------------|----------------|

| R/W-0                   | R/W-0                | R/W-0                                    | U-0             | U-0               | R/W-0               | R/W-0           | R/W-0          |

| VCFG2 <sup>(1)</sup>    | VCFG1 <sup>(1)</sup> | VCFG0 <sup>(1)</sup>                     | —               | —                 | CSCNA               | CHPS1           | CHPS0          |

| bit 15                  |                      |                                          |                 |                   |                     |                 | bit            |

| R-0                     | R/W-0                | R/W-0                                    | R/W-0           | R/W-0             | R/W-0               | R/W-0           | R/W-0          |

| BUFS                    | SMPI4                | SMPI3                                    | SMPI2           | SMPI1             | SMPI0               | BUFM            | ALTS           |

| bit 7                   |                      |                                          | 0111112         |                   |                     | Dor m           | bit            |

| <u> </u>                |                      |                                          |                 |                   |                     |                 |                |

| Legend:<br>R = Readable | , hit                | W = Writable I                           | sit             | II – Unimplor     | monted bit read     |                 |                |

| -n = Value at           |                      | '1' = Bit is set                         | JIL             | '0' = Bit is cle  | nented bit, read    | x = Bit is unkr |                |

|                         | PUR                  | I = DILIS SEL                            |                 |                   | areu                | X = DILIS UNKI  | IOWII          |

| bit 15-13               | VCFG<2:0>            | . Converter Volta                        | ge Reference    | Configuration I   | bits <sup>(1)</sup> |                 |                |

|                         | Value                | VREFH                                    | VREFL           |                   |                     |                 |                |

|                         | xxx                  | AVdd                                     | AVss            |                   |                     |                 |                |

| bit 12-11               | Unimpleme            | ented: Read as '0                        | ,               |                   |                     |                 |                |

| bit 10                  | CSCNA: Inp           | out Scan Select b                        | it              |                   |                     |                 |                |

|                         |                      | nputs for CH0+ d                         | uring Sample N  | /UX A             |                     |                 |                |

|                         | 0 = Does no          | ot scan inputs                           |                 |                   |                     |                 |                |

| bit 9-8                 | CHPS<1:0>            | Channel Select                           | bits            |                   |                     |                 |                |

|                         |                      | de (AD21B = 1),                          |                 | ts are Unimple    | emented and ar      | e Read as '0':  |                |

|                         |                      | rts CH0, CH1, CH                         | 12 and CH3      |                   |                     |                 |                |

|                         | 01 = Conve           | rts CH0 and CH1<br>rts CH0               |                 |                   |                     |                 |                |

| bit 7                   |                      | er Fill Status bit (                     | only valid when | BUFM = 1          |                     |                 |                |

|                         |                      | s currently filling t                    | -               | -                 | he user applicat    | ion should acce | ess data in th |

|                         |                      | f of the buffer                          |                 | ,                 |                     |                 |                |

|                         |                      | s currently filling                      |                 | the buffer; the   | e user application  | on should acce  | ss data in th  |

|                         |                      | half of the buffer                       |                 |                   |                     |                 |                |

| bit 6-2                 |                      | Increment Rate                           | bits            |                   |                     |                 |                |

|                         | When ADD             |                                          | - (1            |                   |                     |                 | _              |

|                         |                      | enerates interrupt<br>enerates interrupt |                 |                   |                     |                 |                |

|                         | •                    |                                          |                 |                   |                     |                 |                |

|                         | •                    |                                          |                 |                   |                     |                 |                |

|                         | •                    |                                          |                 |                   |                     |                 |                |

|                         |                      | enerates interrupt<br>enerates interrupt |                 |                   |                     |                 |                |

|                         | When ADD             | -                                        | and complete    |                   | npic/conversion     | roperation      |                |

|                         |                      | crements the DM/                         | A address after | completion of     | every 32nd sa       | mple/conversio  | n operation    |

|                         |                      | crements the DM                          |                 |                   |                     |                 |                |

|                         | •                    |                                          |                 |                   | -                   |                 |                |

|                         | •                    |                                          |                 |                   |                     |                 |                |

|                         | •<br>00001 = lpc     | crements the DM                          | A address after | completion of     | every 2nd sam       | nle/conversion  | operation      |

|                         |                      | crements the DM                          |                 |                   |                     |                 |                |

| Note 1. TL              |                      | H Input is connec                        | tod to AVpp     |                   | put in passa-t-     | d to AV/aa      |                |

| NOLE I: IN              |                      | ·□ πουπis connec                         | ieu iu aviju ar | IU IIIE VREEL III | IOULIS CONNECTE     | UIUAVSS.        |                |

# REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2

**Note 1:** The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

| DC CHARACT                                                      | ARACTERISTICS (unles |      |                  | tandard Operating Conditions: 4.5V to 5.5V<br>inless otherwise stated)<br>perating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |                                              |  |  |  |

|-----------------------------------------------------------------|----------------------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------|--|--|--|

| Parameter<br>No.                                                | Typ. <sup>(2)</sup>  | Max. | Units Conditions |                                                                                                                                                                                                              |      |                                              |  |  |  |

| Power-Down Current (IPD) – dsPIC33EVXXXGM00X/10X <sup>(1)</sup> |                      |      |                  |                                                                                                                                                                                                              |      |                                              |  |  |  |

| DC60d                                                           | 9.25                 | 30   | μA               | -40°C                                                                                                                                                                                                        |      |                                              |  |  |  |

| DC60a                                                           | 15.75                | 35   | μA               | +25°C                                                                                                                                                                                                        | E OV | Base Power-Down Current                      |  |  |  |

| DC60b                                                           | 67.75                | 250  | μA               | +85°C                                                                                                                                                                                                        | 5.0V |                                              |  |  |  |

| DC60c                                                           | 270                  | 750  | μA               | +125°C                                                                                                                                                                                                       |      |                                              |  |  |  |

| DC61d                                                           | 1                    | 7    | μA               | -40°C                                                                                                                                                                                                        |      |                                              |  |  |  |

| DC61a                                                           | 1.25                 | 8    | μA               | +25°C                                                                                                                                                                                                        | =    | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |  |  |

| DC61b                                                           | 3.5                  | 12   | μA               | +85°C                                                                                                                                                                                                        | 5.0V |                                              |  |  |  |

| DC61c                                                           | 5                    | 15   | μA               | +125°C                                                                                                                                                                                                       |      |                                              |  |  |  |

## TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** IPD (Sleep) current is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- **2:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

# dsPIC33EVXXXGM00X/10X FAMILY

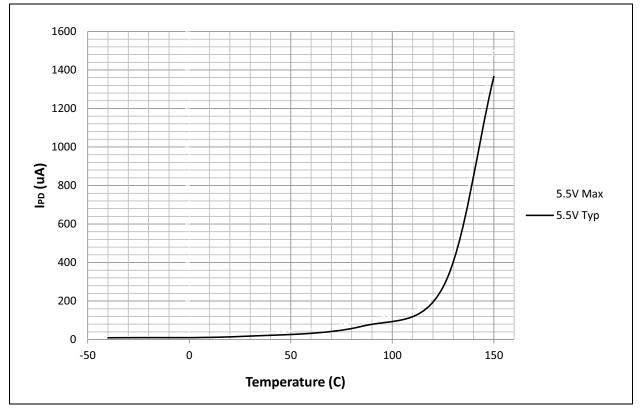

#### 33.4 IPD

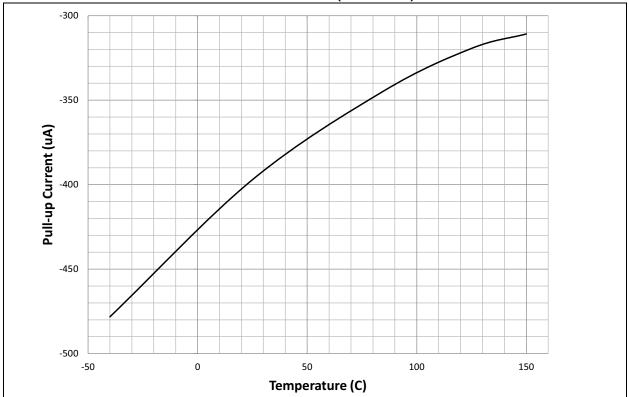

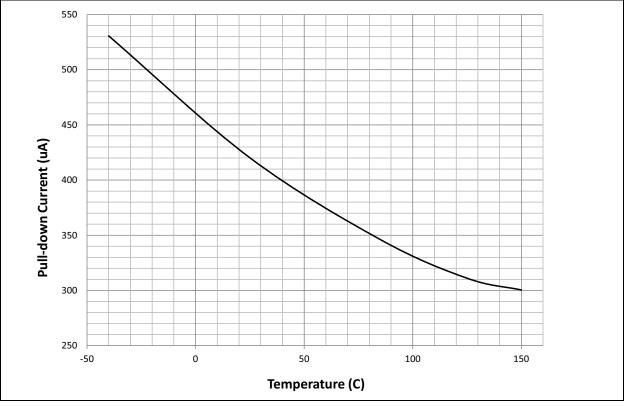

# 33.8 Pull-up/Pull-Down Current

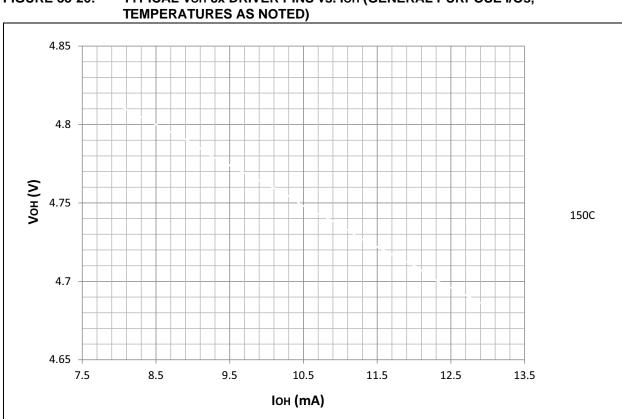

# 33.10 Voltage Output Low (VOL) – Voltage Output High (VOH)

# FIGURE 33-26: TYPICAL VOH 8x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os,