Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm102-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33EVXXXGM00X/10X family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. The data for the ALU operation can come from the W register array or from the data memory, depending on the addressing mode of the instruction. Similarly, the output data from the ALU can be written to the W register array or a data memory location.

For information on the SR bits affected by each instruction, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes the single-cycle per bit of the divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.8 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON) as follows:

- Fractional or Integer DSP Multiply (IF)

- Signed, Unsigned or Mixed-Sign DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

# TABLE 3-2:DSP INSTRUCTIONSSUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

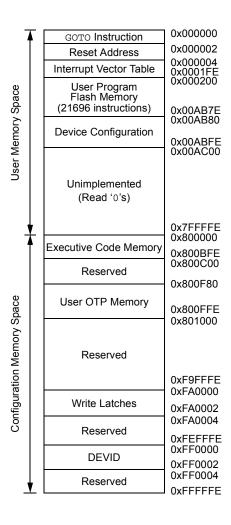

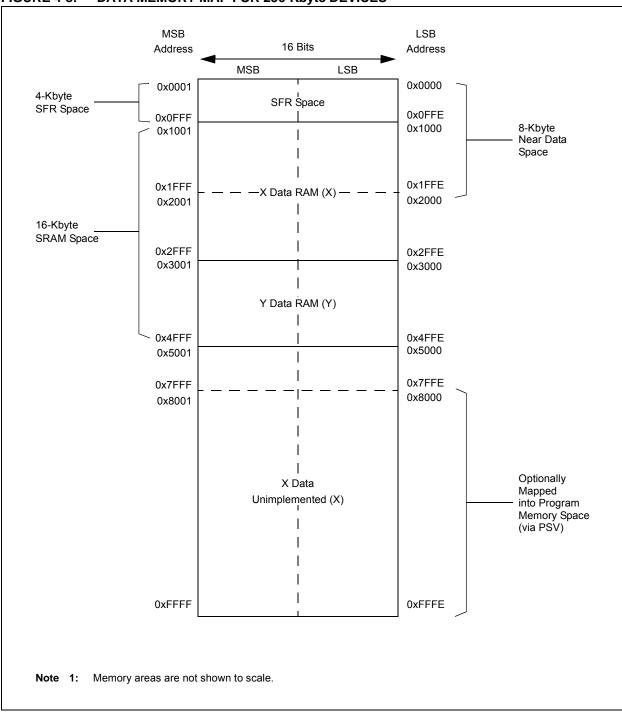

**Note 1:** Memory areas are not shown to scale.

## 4.3 Special Function Register Maps

#### TABLE 4-1: CPU CORE REGISTER MAP

|             | - • • |        |        | LOISIL |             |           |        |           |             |              |       |            |              |                                                                                           |             |       |       |                   |  |  |  |  |  |

|-------------|-------|--------|--------|--------|-------------|-----------|--------|-----------|-------------|--------------|-------|------------|--------------|-------------------------------------------------------------------------------------------|-------------|-------|-------|-------------------|--|--|--|--|--|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11    | Bit 10 | Bit 9     | Bit 8       | Bit 7        | Bit 6 | Bit 5      | Bit 4        | Bit 3                                                                                     | Bit 2       | Bit 1 | Bit 0 | All<br>Reset<br>s |  |  |  |  |  |

| W0          | 0000  |        |        |        |             |           |        |           | W0 (W       | REG)         |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W1          | 0002  |        |        |        |             |           |        |           | Ŵ           |              |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W2          | 0004  |        |        |        |             |           |        |           | W           | 2            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W3          | 0006  |        |        |        |             |           |        |           | W           | 3            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W4          | 0008  |        |        |        |             |           |        |           |             |              |       |            | 0000         |                                                                                           |             |       |       |                   |  |  |  |  |  |

| W5          | 000A  |        |        |        |             |           |        |           | W           | 5            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W6          | 000C  |        |        |        |             |           |        |           | We          | 6            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W7          | 000E  |        |        |        |             |           |        |           | W           | 7            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W8          | 0010  |        |        |        |             |           |        |           | W           | 3            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W9          | 0012  |        |        |        |             |           |        |           | W           | 9            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W10         | 0014  |        |        |        |             |           |        |           | W1          | 0            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W11         | 0016  |        |        |        |             |           |        |           | W1          | 1            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W12         | 0018  |        |        |        |             |           |        |           |             |              | 0000  |            |              |                                                                                           |             |       |       |                   |  |  |  |  |  |

| W13         | 001A  |        |        |        |             |           |        |           | W1          | 3            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W14         | 001C  |        |        |        |             |           |        |           | W1          | 4            |       |            |              |                                                                                           |             |       |       | 0000              |  |  |  |  |  |

| W15         | 001E  |        |        |        |             |           |        |           | W1          | 5            |       |            |              |                                                                                           |             |       |       | 0800              |  |  |  |  |  |

| SPLIM       | 0020  |        |        |        |             |           |        |           | SPL         | IM           |       |            |              |                                                                                           |             |       |       | xxxx              |  |  |  |  |  |

| ACCAL       | 0022  |        |        |        |             |           |        |           | ACC         | AL           |       |            |              |                                                                                           |             |       |       | xxxx              |  |  |  |  |  |

| ACCAH       | 0024  |        |        |        |             |           |        |           | ACC         | AH           |       |            |              |                                                                                           |             |       |       | xxxx              |  |  |  |  |  |

| ACCAU       | 0026  |        |        | Sig    | n Extension | of ACCA<3 | 9>     |           |             |              |       |            | ACC          | CAU                                                                                       |             |       |       | xxxx              |  |  |  |  |  |

| ACCBL       | 0028  |        |        |        |             |           |        |           | ACC         | BL           |       |            |              |                                                                                           |             |       |       | xxxx              |  |  |  |  |  |

| ACCBH       | 002A  |        |        |        |             |           |        |           | ACC         | BH           |       |            |              |                                                                                           |             |       |       | xxxx              |  |  |  |  |  |

| ACCBU       | 002C  |        |        | Sig    | n Extension | of ACCB<3 | 9>     |           |             |              |       |            | ACC          | CBU                                                                                       |             |       |       | xxxx              |  |  |  |  |  |

| PCL         | 002E  |        |        |        |             |           | Pro    | ogram Cou | nter Low We | ord Register | r     |            |              |                                                                                           |             |       | _     | 0000              |  |  |  |  |  |

| PCH         | 0030  | _      | _      | _      | _           | _         | _      | _         | _           | _            |       | F          | Program Cou  | inter High W                                                                              | ord Registe | r     |       | 0000              |  |  |  |  |  |

| DSRPAG      | 0032  | _      | _      | _      | _           | _         | _      |           |             |              | Dat   | a Space Re | ad Page Reg  | gister                                                                                    |             |       |       | 0001              |  |  |  |  |  |

| DSWPAG      | 0034  | _      | _      | _      | _           | _         | _      | _         |             |              |       | Data Spa   | ce Write Pag | e Register                                                                                |             |       |       | 0001              |  |  |  |  |  |

| RCOUNT      | 0036  |        |        |        |             |           |        | REPEAT LC | op Counter  | Register     |       |            |              |                                                                                           |             |       | 0     | xxxx              |  |  |  |  |  |

| DCOUNT      | 0038  |        |        |        |             |           |        | DC        | OUNT<15:1   | >            |       |            |              |                                                                                           |             |       | 0     | xxxx              |  |  |  |  |  |

| DOSTARTL    | 003A  |        |        |        |             |           |        | DOS       | TARTL<15    | :1>          |       |            |              |                                                                                           |             |       | 0     | xxxx              |  |  |  |  |  |

| DOSTARTH    | 003C  | _      | _      |        | _           | _         |        | _         | _           | _            | _     |            |              | DOSTART                                                                                   | H<5:0>      |       |       | 00xx              |  |  |  |  |  |

| DOENDL      | 003E  |        |        |        |             |           |        | DO        | ENDL<15:1   | >            |       |            |              |                                                                                           |             |       | —     | xxxx              |  |  |  |  |  |

| Lonondi     |       |        |        |        |             |           |        |           |             |              |       |            |              | Point where a Departs — a unimplemented read as (a). Departurely a shown is howed as incl |             |       |       |                   |  |  |  |  |  |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

| R/W-0           | R/W-0        | R/W-0                                                             | R/W-0         | R/W-0                              | R/W-0        | R/W-0              | R/W-0 |  |  |  |

|-----------------|--------------|-------------------------------------------------------------------|---------------|------------------------------------|--------------|--------------------|-------|--|--|--|

|                 |              |                                                                   | SENT          | 1R<7:0>                            |              |                    |       |  |  |  |

| bit 15          |              |                                                                   |               |                                    |              |                    | bit 8 |  |  |  |

|                 |              |                                                                   |               |                                    |              |                    |       |  |  |  |

| U-0             | U-0          | U-0                                                               | U-0           | U-0                                | U-0          | U-0                | U-0   |  |  |  |

| —               |              | —                                                                 | —             | —                                  | —            | —                  | —     |  |  |  |

| bit 7           |              |                                                                   |               |                                    |              |                    | bit 0 |  |  |  |

|                 |              |                                                                   |               |                                    |              |                    |       |  |  |  |

| Legend:         |              |                                                                   |               |                                    |              |                    |       |  |  |  |

| R = Readable    | bit          | W = Writable                                                      | bit           | U = Unimplemented bit, read as '0' |              |                    |       |  |  |  |

| -n = Value at F | POR          | '1' = Bit is set                                                  |               | '0' = Bit is cle                   | ared         | x = Bit is unknown |       |  |  |  |

| bit 15-8        | (see Table 1 | <b>0&gt;:</b> Assign SEN<br>1-2 for input pin<br>Input tied to RI | selection nur |                                    | esponding RP | n Pin bits         |       |  |  |  |

|                 |              | Input tied to CI                                                  |               |                                    |              |                    |       |  |  |  |

### REGISTER 11-16: RPINR44: PERIPHERAL PIN SELECT INPUT REGISTER 44

#### REGISTER 11-17: RPINR45: PERIPHERAL PIN SELECT INPUT REGISTER 45

| U-0           | U-0                                   | U-0                                                                                                         | U-0                    | U-0              | U-0              | U-0                | U-0   |  |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|------------------|------------------|--------------------|-------|--|

| —             | —                                     | -                                                                                                           | _                      | —                | —                | _                  | —     |  |

| bit 15        |                                       |                                                                                                             |                        |                  |                  |                    | bit 8 |  |

| DAMA          | D/M/ O                                |                                                                                                             |                        |                  |                  |                    |       |  |

| R/W-0         | R/W-0                                 | R/W-0                                                                                                       | R/W-0                  | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |

|               |                                       |                                                                                                             | SENT                   | 2R<7:0>          |                  |                    |       |  |

| bit 7         |                                       |                                                                                                             |                        |                  |                  |                    | bit 0 |  |

|               |                                       |                                                                                                             |                        |                  |                  |                    |       |  |

| Legend:       |                                       |                                                                                                             |                        |                  |                  |                    |       |  |

| R = Readabl   | le bit                                | W = Writable                                                                                                | bit                    | U = Unimpler     | mented bit, read | <b>l as</b> '0'    |       |  |

| -n = Value at | t POR                                 | '1' = Bit is set                                                                                            |                        | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|               |                                       |                                                                                                             |                        |                  |                  |                    |       |  |

| bit 15-8      | Unimplemer                            | ted: Read as '                                                                                              | 0'                     |                  |                  |                    |       |  |

| bit 7-0       | (see Table 11<br>10110101 =<br>•<br>• | <ul> <li>Assign SEN</li> <li>2 for input pin</li> <li>Input tied to RI</li> <li>Input tied to CI</li> </ul> | selection nun<br>PI181 |                  | responding RPr   | Pin bits           |       |  |

|               |                                       | Input tied to Vs                                                                                            |                        |                  |                  |                    |       |  |

## 16.1 Output Compare Control Registers

## REGISTER 16-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                      | R/W-0                                                                                            | R/W-0                                                   | R/W-0                                    | R/W-0            | U-0             | U-0   |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------|------------------|-----------------|-------|--|--|--|

|               | —                                                                                                        | OCSIDL                                                                                           | OCTSEL2                                                 | OCTSEL1                                  | OCTSEL0          | —               | —     |  |  |  |

| bit 15        |                                                                                                          |                                                                                                  |                                                         |                                          |                  |                 | bit 8 |  |  |  |

|               |                                                                                                          |                                                                                                  |                                                         |                                          |                  |                 |       |  |  |  |

| R/W-0         | U-0                                                                                                      | U-0                                                                                              | R/W-0, HSC                                              | R/W-0                                    | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| ENFLTA        | <u> </u>                                                                                                 | _                                                                                                | OCFLTA                                                  | TRIGMODE                                 | OCM2             | OCM1            | OCM0  |  |  |  |

| bit 7         |                                                                                                          |                                                                                                  |                                                         |                                          |                  |                 | bit ( |  |  |  |

| Legend:       |                                                                                                          | HSC = Hardv                                                                                      | vare Settable/Cl                                        | earable bit                              |                  |                 |       |  |  |  |

| R = Readable  | e bit                                                                                                    | W = Writable                                                                                     | bit                                                     | U = Unimplem                             | nented bit, read | <b>l as</b> '0' |       |  |  |  |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                                                                                 | t                                                       | '0' = Bit is clea                        | ared             | x = Bit is unkn | iown  |  |  |  |

| bit 12-10     | OCTSEL<2:0<br>111 = Periphe<br>110 = Reserv<br>101 = Reserv<br>100 = T1CLK<br>011 = T5CLK<br>010 = T4CLK | >: Output Con<br>eral clock (FP)<br>red<br>is the clock so<br>is the clock so<br>is the clock so | ource of the OC<br>ource of the OC<br>ource of the OC   | elect bits<br>x (only the syne<br>x<br>x |                  | s is supported) |       |  |  |  |

|               | 001 = T3CLK is the clock source of the OCx<br>000 = T2CLK is the clock source of the OCx                 |                                                                                                  |                                                         |                                          |                  |                 |       |  |  |  |

| bit 9-8       | Unimplemen                                                                                               | ted: Read as '                                                                                   | 0'                                                      |                                          |                  |                 |       |  |  |  |

| bit 7         | 1 = Output C                                                                                             | ompare Fault                                                                                     | k Fault A Input E<br>A (OCFA) input<br>A (OCFA) input   | is enabled                               |                  |                 |       |  |  |  |

| bit 6-5       | -                                                                                                        | ted: Read as '                                                                                   |                                                         |                                          |                  |                 |       |  |  |  |

| bit 4         | 1 = PWM Fai                                                                                              | ult A condition                                                                                  | ndition Status bit<br>on the OCFA pi<br>on the OCFA pi  | in has occurred                          |                  |                 |       |  |  |  |

| bit 3         | 1 = TRIGSTA                                                                                              | T (OCxCON2                                                                                       | Mode Select bit<br><6>) is cleared v<br>nly by software |                                          | = OCxTMR or i    | n software      |       |  |  |  |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

NOTES:

### 20.2 Transmit Mode

By default, the SENTx module is configured for transmit operation. The module can be configured for continuous asynchronous message frame transmission, or alternatively, for Synchronous mode triggered by software. When enabled, the transmitter will send a Sync followed by the appropriate number of data nibbles, an optional CRC and optional pause pulse. The tick period used by the SENTx transmitter is set by writing a value to the TICKTIME<15:0> (SENTxCON2<15:0>) bits. The tick period calculations are shown in Equation 20-1.

#### EQUATION 20-1: TICK PERIOD CALCULATION

$TICKTIME < 15:0 > = \frac{TTICK}{TCLK} - 1$

An optional pause pulse can be used in Asynchronous mode to provide a fixed message frame time period. The frame period used by the SENTx transmitter is set by writing a value to the FRAMETIME<15:0> (SENTxCON3<15:0>) bits. The formulas used to calculate the value of frame time are shown in Equation 20-2.

#### EQUATION 20-2: FRAME TIME CALCULATIONS

FRAMETIME<15:0> = TTICK/TFRAME

*FRAMETIME*<15:0>  $\geq$  122 + 27*N*

$FRAMETIME < 15:0 \ge 848 + 12N$

Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6

**Note:** The module will not produce a pause period with less than 12 ticks, regardless of the FRAMETIME<15:0> value. FRAMETIME<15:0> values beyond 2047 will have no effect on the length of a data frame.

#### 20.2.1 TRANSMIT MODE CONFIGURATION

#### 20.2.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 0 for Transmit mode.

- Write TXM (SENTxCON1<10>) = 0 for Asynchronous Transmit mode or TXM = 1 for Synchronous mode.

- 3. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 4. Write CRCEN (SENTxCON1<8>) for hardware or software CRC calculation.

- 5. Write PPP (SENTxCON1<7>) for optional pause pulse.

- 6. If PPP = 1, write TFRAME to SENTxCON3.

- 7. Write SENTxCON2 with the appropriate value for desired tick period.

- 8. Enable interrupts and set interrupt priority.

- 9. Write initial status and data values to SENTxDATH/L.

- 10. If CRCEN = 0, calculate CRC and write the value to CRC<3:0> (SENTxDATL<3:0>).

- 11. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

User software updates to SENTxDATH/L must be performed after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt to trigger data writes.

| U-0                                  | U-0                                                                                                                            | U-0                                                                                      | U-0                                   | U-0              | U-0               | U-0               | U-0                     |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------------------|-------------------|-------------------------|--|--|--|--|--|

| _                                    | —                                                                                                                              | —                                                                                        | —                                     | —                | —                 | —                 | —                       |  |  |  |  |  |

| bit 15                               |                                                                                                                                |                                                                                          |                                       |                  |                   |                   | bit 8                   |  |  |  |  |  |

| R-0                                  | R-0                                                                                                                            | R-0                                                                                      | R-0                                   | R-0              | R/C-0             | R-0               | R/W-0, HC               |  |  |  |  |  |

| PAUSE                                | NIB2                                                                                                                           | NIB1                                                                                     | NIB0                                  | CRCERR           | FRMERR            | RXIDLE            | SYNCTXEN <sup>(1)</sup> |  |  |  |  |  |

| bit 7                                | NIDZ                                                                                                                           | NIDT                                                                                     | NIBO                                  | GROLIN           |                   | AR RAIDLE STINGTA |                         |  |  |  |  |  |

| 5107                                 |                                                                                                                                |                                                                                          |                                       |                  |                   |                   | bit (                   |  |  |  |  |  |

| Legend:                              |                                                                                                                                | C = Clearabl                                                                             | e bit                                 | HC = Hardwa      | are Clearable b   | oit               |                         |  |  |  |  |  |

| R = Readab                           | ole bit                                                                                                                        | W = Writable                                                                             | e bit                                 | U = Unimple      | mented bit, rea   | id as '0'         |                         |  |  |  |  |  |

| -n = Value a                         | at POR                                                                                                                         | '1' = Bit is se                                                                          | •t                                    | '0' = Bit is cle | eared             | x = Bit is unk    | nown                    |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          |                                       |                  |                   |                   |                         |  |  |  |  |  |

| bit 15-8                             | -                                                                                                                              | nted: Read as                                                                            |                                       |                  |                   |                   |                         |  |  |  |  |  |

| bit 7                                |                                                                                                                                | se Period Stat                                                                           |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | ting/receiving a smitting/receiving a |                  | riod              |                   |                         |  |  |  |  |  |

| oit 6-4                              |                                                                                                                                | ibble Status bi                                                                          | -                                     | ng a pause per   |                   |                   |                         |  |  |  |  |  |

| Module in Transmit Mode (RCVEN = 0): |                                                                                                                                |                                                                                          |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                | 111 = Module is transmitting a CRC nibble                                                |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                | 110 = Module is transmitting Data Nibble 6                                               |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                | 101 = Module is transmitting Data Nibble 5<br>100 = Module is transmitting Data Nibble 4 |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | ng Data Nibble<br>ng Data Nibble      |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | ng Data Nibble                        |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | ng a status nibb                      |                  | riod, or is not t | ransmitting       |                         |  |  |  |  |  |

|                                      |                                                                                                                                | eceive Mode (F                                                                           |                                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | a CRC nibble o                        |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | Data Nibble 6 c                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | Data Nibble 5 c<br>Data Nibble 4 c    |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | Data Nibble 3 c                       |                  |                   |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                | •                                                                                        | Data Nibble 2 c                       |                  | •                 |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | Data Nibble 1 c                       |                  |                   | hen an error o    | ccurred                 |  |  |  |  |  |

|                                      |                                                                                                                                | -                                                                                        | a status nibble                       | -                | Sync              |                   |                         |  |  |  |  |  |

| bit 3                                |                                                                                                                                |                                                                                          | Receive mode                          | • ·              |                   |                   |                         |  |  |  |  |  |

|                                      | <ul> <li>1 = A CRC error occurred for the 1-6 data nibbles in SENTxDATH/L</li> <li>0 = A CRC error has not occurred</li> </ul> |                                                                                          |                                       |                  |                   |                   |                         |  |  |  |  |  |

| oit 2                                | FRMERR: Fr                                                                                                                     | aming Error S                                                                            | tatus bit (Rece                       | ive mode only)   | )                 |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                | •                                                                                        | ived with less t                      | • •              |                   | than 27 tick p    | eriods                  |  |  |  |  |  |

|                                      |                                                                                                                                | error has not o                                                                          |                                       |                  | -                 |                   |                         |  |  |  |  |  |

| oit 1                                | RXIDLE: SE                                                                                                                     | NTx Receiver                                                                             | Idle Status bit (                     | Receive mode     | e only)           |                   |                         |  |  |  |  |  |

|                                      |                                                                                                                                |                                                                                          | as been Idle (h                       | igh) for a perio | d of SYNCMA       | X<15:0> or gre    | eater                   |  |  |  |  |  |

|                                      | 0 = The SEN                                                                                                                    | Tx data bus is                                                                           | not Idle                              |                  |                   |                   |                         |  |  |  |  |  |

| Note 1: II                           | n Receive mode                                                                                                                 | (RCVEN = 1)                                                                              | the SYNCTXE                           | EN bit is read-c | only.             |                   |                         |  |  |  |  |  |

#### REGISTER 20-2: SENTxSTAT: SENTx STATUS REGISTER

**Note 1:** In Receive mode (RCVEN = 1), the SYNCTXEN bit is read-only.

## 22.0 CONTROLLER AREA NETWORK (CAN) MODULE (dsPIC33EVXXXGM10X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 22.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/ protocol was designed to allow communications within noisy environments. The dsPIC33EVXXXGM10X devices contain one CAN module.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The CAN module features are as follows:

- Implementation of the CAN Protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and Extended Data Frames

- 0 to 8-Byte Data Length

- Programmable Bit Rate, up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to Eight Transmit Buffers with Application Specified Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (Standard/Extended Identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback Mode Supports Self-Test Operation

- Signaling through Interrupt Capabilities for All CAN Receiver and Transmitter Error States

- Programmable Clock Source

- Programmable Link to Input Capture 2 (IC2) module for Timestamping and Network Synchronization

- Low-Power Sleep and Idle Modes

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors, and then matched against filters to see if it should be received and stored in one of the Receive registers.

Figure 22-1 shows a block diagram of the CANx module.

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "**Op Amp/Comparator**" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

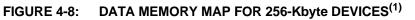

The dsPIC33EVXXXGM00X/10X family devices contain up to five comparators that can be configured in various ways. CMP1, CMP2, CMP3 and CMP5 also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

The following options allow users to:

- Select the Edge for Trigger and Interrupt Generation

- Configure the Comparator Voltage Reference

- Configure Output Blanking and Masking

- Configure as a Comparator or Op Amp (CMP1, CMP2, CMP3 and CMP5 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

#### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |              | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53                 | MUL                  | MUL.SS          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SS          | Wb,Ws,Acc    | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,Ws,Acc    | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Acc | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US          | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Acc | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS         | Wb,Ws,Wnd    | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU         | Wb,Ws,Wnd    | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US         | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU         | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Wnd | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Wnd | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Wnd | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Wnd | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                     |

|                    |                      | MUL             | f            | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 54                 | NEG                  | NEG             | Acc          | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG             | f            | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG             | f,WREG       | WREG = $f + 1$                                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG             | Ws,Wd        | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 55                 | NOP                  | NOP             |              | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR            |              | No Operation                                      | 1             | 1              | None                     |

| 56                 | POP                  | POP             | f            | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP             | Wdo          | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D           | Wnd          | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S           |              | Pop Shadow Registers                              | 1             | 1              | All                      |

| 57                 | PUSH                 | PUSH            | f            | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH            | Wso          | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D          | Wns          | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2              | None                     |

|                    |                      | PUSH.S          |              | Push Shadow Registers                             | 1             | 1              | None                     |

| 58                 | PWRSAV               | PWRSAV          | #lit1        | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 59                 | RCALL                | RCALL           | Expr         | Relative Call                                     | 1             | 4              | SFA                      |

|                    |                      | RCALL           | Wn           | Computed Call                                     | 1             | 4              | SFA                      |

| 60                 | REPEAT               | REPEAT          | #lit15       | Repeat Next Instruction lit15 + 1 times           | 1             | 1              | None                     |

|                    |                      | REPEAT          | Wn           | Repeat Next Instruction (Wn) + 1 times            | 1             | 1              | None                     |

| 61                 | RESET                | RESET           |              | Software device Reset                             | 1             | 1              | None                     |

| 62                 | RETFIE               | RETFIE          |              | Return from interrupt                             | 1             | 6 (5)          | SFA                      |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

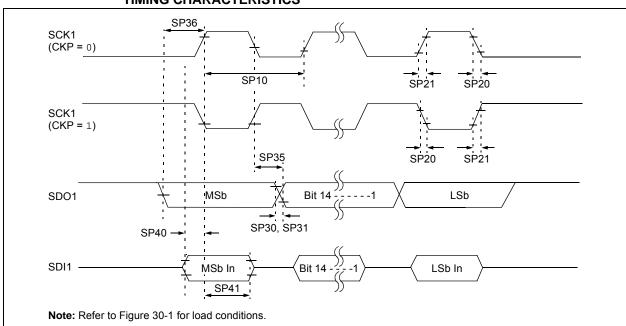

#### FIGURE 30-22: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-40:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| АС СНА | RACTERIST             | ICS                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |                               |  |  |

|--------|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                | Typ. <sup>(2)</sup> | Max. | Units | Conditions                    |  |  |

| SP10   | FscP                  | Maximum SCK1 Frequency                        |                                                                                                                                                                                                                                                                                     | _                   | 25   | MHz   | See Note 3                    |  |  |

| SP20   | TscF                  | SCK1 Output Fall Time                         | —                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO32 and Note 4 |  |  |

| SP21   | TscR                  | SCK1 Output Rise Time                         | —                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO31 and Note 4 |  |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                    | —                                                                                                                                                                                                                                                                                   | —                   |      | ns    | See Parameter DO32 and Note 4 |  |  |

| SP31   | TdoR                  | SDO1 Data Output Rise<br>Time                 | —                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO31 and Note 4 |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | —                                                                                                                                                                                                                                                                                   | 6                   | 20   | ns    |                               |  |  |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO1 Data Output Setup to<br>First SCK1 Edge  | 20                                                                                                                                                                                                                                                                                  | —                   | _    | ns    |                               |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 20                                                                                                                                                                                                                                                                                  | —                   | _    | ns    |                               |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 15                                                                                                                                                                                                                                                                                  | —                   |      | ns    |                               |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPI1 pins.

## dsPIC33EVXXXGM00X/10X FAMILY

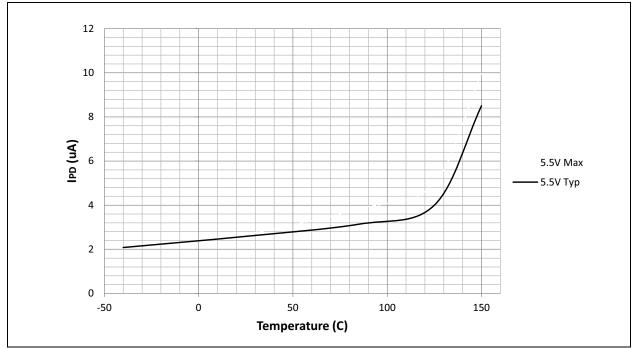

### FIGURE 32-19: TYPICAL/MAXIMUM △IwDT vs. TEMPERATURE

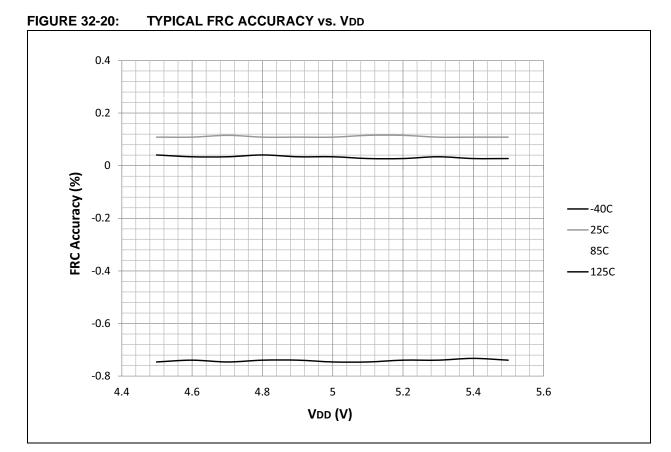

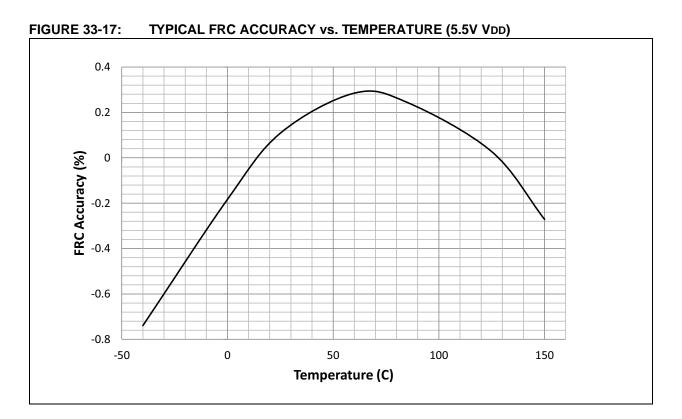

#### 32.5 FRC

DS70005144E-page 422

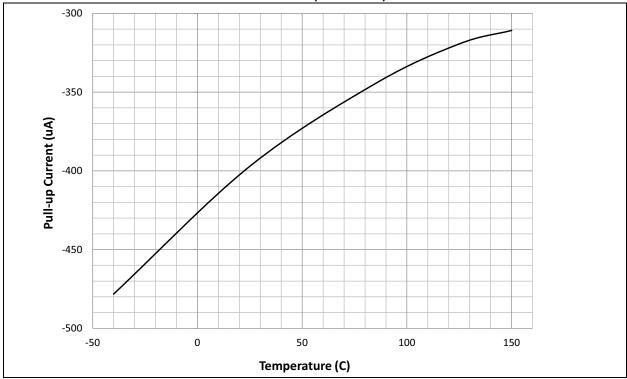

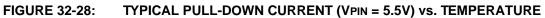

## 32.8 Pull-up and Pull-Down Current

## dsPIC33EVXXXGM00X/10X FAMILY

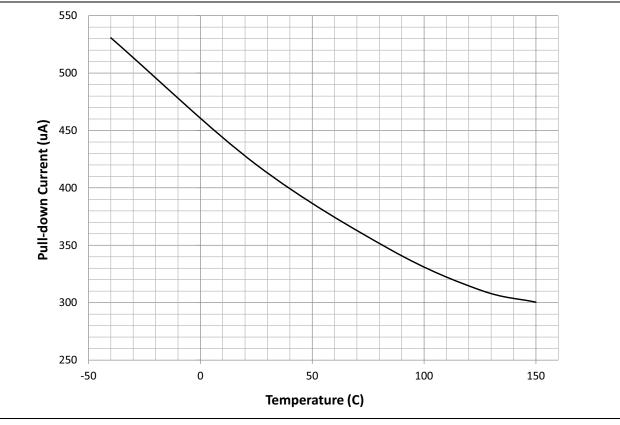

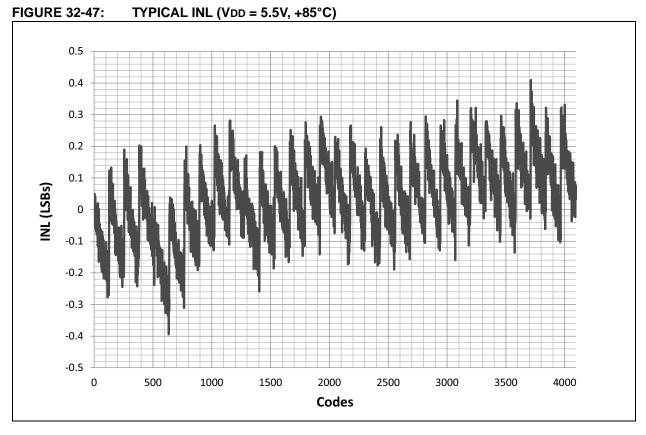

FIGURE 32-48: TYPICAL INL (VDD = 5.5V, +125°C)

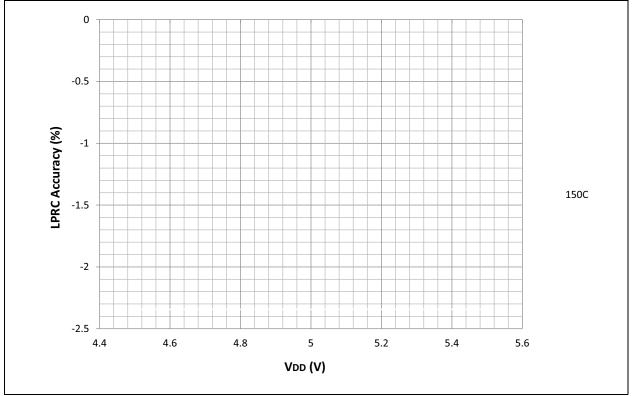

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |  |

|--------------------------|-------------|----------|------|------|--|

| Dimensior                | MIN         | NOM      | MAX  |      |  |

| Contact Pitch            | E           | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С           |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |  |

| Distance Between Pads    | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

#### 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS                  |      |          |      |  |  |  |

|-------------------------|------------------------------|------|----------|------|--|--|--|

| Dimension               | MIN                          | NOM  | MAX      |      |  |  |  |

| Number of Pins          | N                            |      | 28       |      |  |  |  |

| Pitch                   | е                            |      | 0.65 BSC |      |  |  |  |

| Overall Height          | A                            | 0.80 | 0.90     | 1.00 |  |  |  |

| Standoff                | A1                           | 0.00 | 0.02     | 0.05 |  |  |  |

| Terminal Thickness      | rminal Thickness A3 0.20 REF |      |          |      |  |  |  |

| Overall Width           | E                            |      | 6.00 BSC |      |  |  |  |

| Exposed Pad Width       | E2                           | 3.65 | 3.70     | 4.70 |  |  |  |

| Overall Length          | D                            |      | 6.00 BSC |      |  |  |  |

| Exposed Pad Length      | D2                           | 3.65 | 3.70     | 4.70 |  |  |  |

| Terminal Width          | b                            | 0.23 | 0.30     | 0.35 |  |  |  |

| Terminal Length         | L                            | 0.30 | 0.40     | 0.50 |  |  |  |

| Terminal-to-Exposed Pad | K                            | 0.20 | -        | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2