Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm102-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EVXXXGM00X/10X PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show the devices' pinout diagrams.

## TABLE 1: dsPIC33EVXXXGM00X/10X FAMILY DEVICES

|                   | ry Bytes             | es         |     | lels         | s (T1)             | ers           | ure           | pare           |       |      |     |                  |      | ADC         | ts         | arators            |      |              | lect (PPS)                  | I/O (GPIO)                 | rupts               |          | ø            |

|-------------------|----------------------|------------|-----|--------------|--------------------|---------------|---------------|----------------|-------|------|-----|------------------|------|-------------|------------|--------------------|------|--------------|-----------------------------|----------------------------|---------------------|----------|--------------|

| Device            | Program Memory Bytes | SRAM Bytes | CAN | DMA Channels | 16-Bit Timers (T1) | 32-Bit Timers | Input Capture | Output Compare | ВWM   | UART | SPI | I <sup>2</sup> C | SENT | 10/12-Bit A | ADC Inputs | Op Amp/Comparators | CTMU | Security     | Peripheral Pin Select (PPS) | General Purpose I/O (GPIO) | External Interrupts | Pins     | Packages     |

| dsPIC33EV32GM002  | 001/                 | 414        | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV32GM102  | 32K                  | 4K         | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM002  |                      |            | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM102  | 64K                  | 8K         | 1   | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2    | 2   | 1                | 2    | 1           | 11         | 3/4                | 1    | Intermediate | Y                           | 21                         | 3                   | 28       | SPDIP, SOIC, |

| dsPIC33EV128GM002 | 1001/                | 01/        | 0   | 4            | 5                  | 2             | 4             | 4              | 372   | 2    | 2   | 1                | 2    | 1           |            | 5/4                |      | internetiate |                             | 21                         | 5                   | 20       | SSOP, QFN-S  |

| dsPIC33EV128GM102 | 128K                 | 8K         | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM002 | 256K                 | 161        | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM102 | 2001                 | 16K        | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV32GM004  | 32K                  | 4K         | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV32GM104  | JZK                  | 41         | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM004  | 64K                  | 8K         | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM104  | 041                  | or         | 1   | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2    | 2   | 1                | 2    | 1           | 24         | 4/5                | 1    | Intermediate | Y                           | 35                         | 3                   | 44       | TQFP, QFN    |

| dsPIC33EV128GM004 | 128K                 | 8K         | 0   | 7            | 5                  | 2             | -             | -              | 572   | 2    | 2   | 1                | 2    |             | 27         | 7/5                |      | internediate |                             | 55                         | 5                   |          |              |

| dsPIC33EV128GM104 | 1201                 | UIX        | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM004 | 256K                 | 16K        | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM104 |                      |            | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV32GM006  | 32K                  | 4K         | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV32GM106  |                      |            | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM006  | 64K                  | 8K         | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV64GM106  | 2                    | 5.1        | 1   | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2    | 2   | 1                | 2    | 1           | 36         | 4/5                | 1    | Intermediate | Y                           | 53                         | 3                   | 64       | TQFP, QFN    |

| dsPIC33EV128GM006 | 128K                 | 8K         | 0   |              | Ŭ                  | -             |               |                | 0.1.2 | -    | -   |                  | -    |             |            |                    |      |              | .<br>                       |                            |                     | <u> </u> | ,            |

| dsPIC33EV128GM106 |                      | 513        | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM006 | 256K                 | 16K        | 0   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| dsPIC33EV256GM106 | 2001                 | IUIX       | 1   |              |                    |               |               |                |       |      |     |                  |      |             |            |                    |      |              |                             |                            |                     |          |              |

| TABLE 1-1: PINO                                                                                                                             |             | D DESC         | RIPTI   | ONS (CONTINUED)                                                            |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|---------|----------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                                                                                    | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                |  |  |  |  |

| SCK2                                                                                                                                        | I/O         | ST             | Yes     | Synchronous serial clock input/output for SPI2.                            |  |  |  |  |

| SDI2                                                                                                                                        | I           | ST             | Yes     | SPI2 data in.                                                              |  |  |  |  |

| SDO2                                                                                                                                        | 0           | —              | Yes     | SPI2 data out.                                                             |  |  |  |  |

| SS2                                                                                                                                         | I/O         | ST             | Yes     | SPI2 slave synchronization or frame pulse I/O.                             |  |  |  |  |

| SCL1                                                                                                                                        | I/O         | ST             | No      | Synchronous serial clock input/output for I2C1.                            |  |  |  |  |

| SDA1                                                                                                                                        | I/O         | ST             | No      | Synchronous serial data input/output for I2C1.                             |  |  |  |  |

| ASCL1                                                                                                                                       | I/O         | ST             | No      | Alternate synchronous serial clock input/output for I2C1.                  |  |  |  |  |

| ASDA1                                                                                                                                       | I/O         | ST             | No      | Alternate synchronous serial data input/output for I2C1.                   |  |  |  |  |

| C1RX                                                                                                                                        | I.          | ST             | Yes     | CAN1 bus receive pin.                                                      |  |  |  |  |

| C1TX                                                                                                                                        | 0           | —              | Yes     | CAN1 bus transmit pin.                                                     |  |  |  |  |

| SENT1TX                                                                                                                                     | 0           | —              | Yes     | SENT1 transmit pin.                                                        |  |  |  |  |

| SENT1RX                                                                                                                                     | 1           | —              | Yes     | SENT1 receive pin.                                                         |  |  |  |  |

| SENT2TX                                                                                                                                     | 0           | —              | Yes     | SENT2 transmit pin.                                                        |  |  |  |  |

| SENT2RX                                                                                                                                     | I.          | —              | Yes     | SENT2 receive pin.                                                         |  |  |  |  |

| CVREF                                                                                                                                       | 0           | Analog         | No      | Comparator Voltage Reference output.                                       |  |  |  |  |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3-                                                                                                           | I           | Analog         | No      | Comparator 1 inputs.                                                       |  |  |  |  |

| C1OUT                                                                                                                                       | 0           | _              | Yes     | Comparator 1 output.                                                       |  |  |  |  |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3-                                                                                                           | I           | Analog         | No      | Comparator 2 inputs.                                                       |  |  |  |  |

|                                                                                                                                             | 0           | —              | Yes     | Comparator 2 output.                                                       |  |  |  |  |

| C2OUT     O     —     Yes     Comparator 2 output.       C3IN1+, C3IN2-,<br>C2IN1-, C3IN3-     I     Analog     No     Comparator 3 inputs. |             |                |         |                                                                            |  |  |  |  |

| C3OUT                                                                                                                                       | 0           |                | Yes     | Comparator 3 output.                                                       |  |  |  |  |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3-                                                                                                           | Ι           | Analog         | No      | Comparator 4 inputs.                                                       |  |  |  |  |

| C4OUT                                                                                                                                       | 0           | —              | Yes     | Comparator 4 output.                                                       |  |  |  |  |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3-                                                                                                           | I           | Analog         | No      | Comparator 5 inputs.                                                       |  |  |  |  |

| C5OUT                                                                                                                                       | 0           | —              | Yes     | Comparator 5 output.                                                       |  |  |  |  |

| FLT1-FLT2                                                                                                                                   | 1           | ST             | Yes     | PWM Fault Inputs 1 and 2.                                                  |  |  |  |  |

| FLT3-FLT8                                                                                                                                   | 1           | ST             | NO      | PWM Fault Inputs 3 to 8.                                                   |  |  |  |  |

| FLT32                                                                                                                                       | 1           | ST             | NO      | PWM Fault Input 32.                                                        |  |  |  |  |

| DTCMP1-DTCMP3                                                                                                                               | 1           | ST             | Yes     | PWM Dead-Time Compensation Inputs 1 to 3.                                  |  |  |  |  |

| PWM1L-PWM3L                                                                                                                                 | 0           | _              | No      | PWM Low Outputs 1 to 3.                                                    |  |  |  |  |

| PWM1H-PWM3H                                                                                                                                 | 0           | —              | No      | PWM High Outputs 1 to 3.                                                   |  |  |  |  |

| SYNCI1                                                                                                                                      | 1           | ST             | Yes     | PWM Synchronization Input 1.                                               |  |  |  |  |

| SYNCO1                                                                                                                                      | 0           | —              | Yes     | PWM Synchronization Output 1.                                              |  |  |  |  |

| PGED1                                                                                                                                       | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.            |  |  |  |  |

| PGEC1                                                                                                                                       | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1          |  |  |  |  |

| PGED2                                                                                                                                       | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.            |  |  |  |  |

| PGEC2                                                                                                                                       | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2          |  |  |  |  |

| PGED3                                                                                                                                       | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.            |  |  |  |  |

| PGEC3                                                                                                                                       | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel            |  |  |  |  |

| MCLR                                                                                                                                        | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |  |  |  |

| Legend: CMOS = C                                                                                                                            |             |                |         | or output Analog = Analog input P = Power                                  |  |  |  |  |

| ST = Schm                                                                                                                                   | itt Triaa   | er input w     | /ith CN | IOS levels O = Output I = Input                                            |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | / |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

## 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

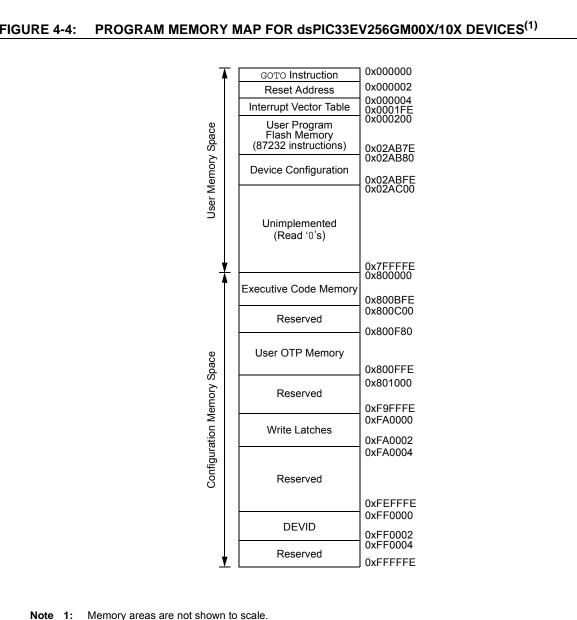

## FIGURE 4-4:

|             |       |           | -0.0.         |        |        |        | (0.0.1 |       | 0     |           |       |       |       | .0 (001 |       | ·)    |       |               |

|-------------|-------|-----------|---------------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|-------|---------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15    | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11SID  | 046C  | SID10     | SID9          | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | —     | EID17 | EID16 | xxxx          |

| C1RXF11EID  | 046E  |           | EID<15:0> xxx |        |        |        |        |       |       |           |       |       | xxxx  |         |       |       |       |               |

| C1RXF12SID  | 0470  | SID10     | SID9          | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF12EID  | 0472  |           | EID<15:0> x:  |        |        |        |        |       |       |           |       |       |       |         | xxxx  |       |       |               |

| C1RXF13SID  | 0474  | SID10     | SID9          | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF13EID  | 0476  |           |               |        |        |        |        |       | E     | EID<15:0> |       |       |       |         |       |       |       | xxxx          |

| C1RXF14SID  | 0478  | SID10     | SID9          | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF14EID  | 047A  |           |               |        |        |        |        |       | E     | ID<15:0>  |       |       |       |         |       |       |       | xxxx          |

| C1RXF15SID  | 047C  | SID10     | SID9          | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF15EID  | 047E  | EID<15:0> |               |        |        |        |        |       |       |           |       |       |       |         | xxxx  |       |       |               |

|             |       |           |               |        |        |        |        |       |       |           |       |       |       |         |       |       |       |               |

#### TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-12: SENT1 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                           | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8      | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|------------------------------------------------------------------|--------|---------|--------|--------|--------|-------------|------------|------------|-----------|-------|-------|--------|---------|---------|----------|---------------|

| SENT1CON1   | 0500  | SNTEN                                                            | —      | SNTSIDL | _      | RCVEN  | TXM    | TXPOL       | CRCEN      | PPP        | SPCEN     | _     | PS    | -      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT1CON2   | 0504  | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode)  |        |         |        |        |        |             |            |            |           |       |       |        |         |         | FFFF     |               |

| SENT1CON3   | 0508  | FRAMETIME<15:0> (Transmit modes) or SYNCMIN<15:0> (Receive mode) |        |         |        |        |        |             |            |            |           |       |       |        |         | FFFF    |          |               |

| SENT1STAT   | 050C  | _                                                                | _      | _       | _      | _      | _      | _           | _          | PAUSE      | NIB2      | NIB1  | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT1SYNC   | 0510  |                                                                  |        |         |        |        | Synchr | onization - | Time Perio | d Register | (Transmit | mode) |       |        |         |         |          | 0000          |

| SENT1DATL   | 0514  | DATA4<3:0> DATA5<3:0> DATA6<3:0> CRC<3:0> (                      |        |         |        |        |        |             |            |            |           |       |       | 0000   |         |         |          |               |

| SENT1DATH   | 0516  |                                                                  |        |         |        |        |        |             |            |            |           |       |       | 0000   |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: SENT2 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                                          | Bit 14                                                           | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8      | Bit 7     | Bit 6       | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|---------------------------------------------------------------------------------|------------------------------------------------------------------|---------|--------|--------|--------|------------|------------|-----------|-------------|-------|-------|--------|---------|---------|----------|---------------|

| SENT2CON1   | 0520  | SNTEN                                                                           | —                                                                | SNTSIDL |        | RCVEN  | TXM    | TXPOL      | CRCEN      | PPP       | SPCEN       | -     | PS    | —      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT2CON2   | 0524  |                                                                                 | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode)  |         |        |        |        |            |            |           |             |       |       |        |         |         | FFFF     |               |

| SENT2CON3   | 0528  |                                                                                 | FRAMETIME<15:0> (Transmit modes) or SYNCMIN<15:0> (Receive mode) |         |        |        |        |            |            |           |             |       |       |        |         | FFFF    |          |               |

| SENT2STAT   | 052C  | -                                                                               | _                                                                | _       |        | —      |        | —          | _          | PAUSE     | NIB2        | NIB1  | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT2SYNC   | 0530  |                                                                                 |                                                                  |         |        |        | Synchi | ronization | Time Peric | d Registe | r (Transmit | mode) |       |        |         |         |          | 0000          |

| SENT2DATL   | 0534  | DATA4<3:0> DATA5<3:0> DATA6<3:0> CRC<3:0> 00                                    |                                                                  |         |        |        |        |            |            |           |             |       | 0000  |        |         |         |          |               |

| SENT2DATH   | 0536  | STAT<3:0>         DATA1<3:0>         DATA2<3:0>         DATA3<3:0>         0000 |                                                                  |         |        |        |        |            |            |           |             | 0000  |       |        |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70005144E-page 49

## TABLE 4-14: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM002/102 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|------------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      | _      | RP35R5     | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | _     | RP20R5  | RP20R4  | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  |        | _      | RP37R5     | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  |       | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  |        | _      | RP39R5     | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  |       | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  |        | _      | RP41R5     | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  |       | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  |        | _      | RP43R5     | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  |       | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR10      | 0684  |        | _      |            |         | RP176   | R<5:0>  |         |         |       | _     | _       | _       | _       | _       | _       | _       | 0000          |

| RPOR11      | 0686  |        | _      | RP178R5    | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |       | _     | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | _      | _      | RP180R5    | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | _     | —     | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  | _      | _      | - <u> </u> |         |         |         |         |         |       |       |         | 0000    |         |         |         |         |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-15: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM004/104 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | -     | RP20R5  | RP20R4  | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | -     | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | -     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | -     | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  | _      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | -     | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR5       | 067A  | _      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | -     | _     | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR6       | 067C  | _      | —      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | -     | _     | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR7       | 067E  | —      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     | _     | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR10      | 0684  | —      | _      |         |         | RP176   | R<5:0>  |         |         | _     | _     | _       | _       | _       | _       | _       | _       | 0000          |

| RPOR11      | 0686  | —      | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | _     | _     | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | _      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | _     | _     | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  |        |        | —       |         |         |         |         |         |       |       |         |         | RP181   | R<5:0>  |         |         | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

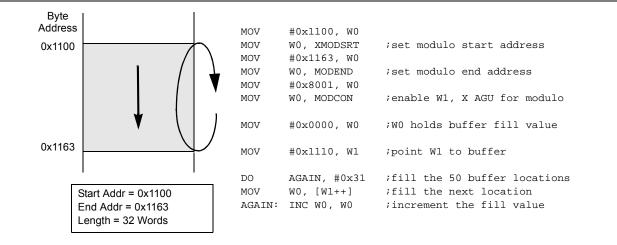

## 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the SFP and SSP, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit (MODCON<15>) is set

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

Figure 4-15 shows an example of Modulo Addressing operation.

Note: Y Data Space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

### FIGURE 4-15: MODULO ADDRESSING OPERATION EXAMPLE

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EVXXXGM00X/10X Product Families" section for the page sizes of each device.memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to era

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Table 30-13 in **Section 30.0 "Electrical Characteristics"** lists the typical erase and programming times.

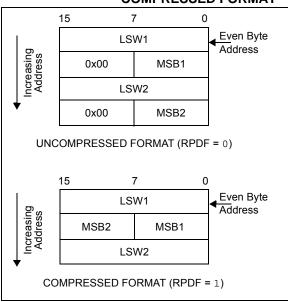

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. See Figure 4-1 to Figure 4-5 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

For more information on erasing and programming the Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

- Note 1: Before reprogramming either of the two words in a double-word pair, the user must erase the Flash memory page in which it is located.

- 2: Before reprogramming any word in a row, the user must erase the Flash memory page in which it is located.

#### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **"Flash Programming"** (DS70609) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and code examples on programming using RTSP.

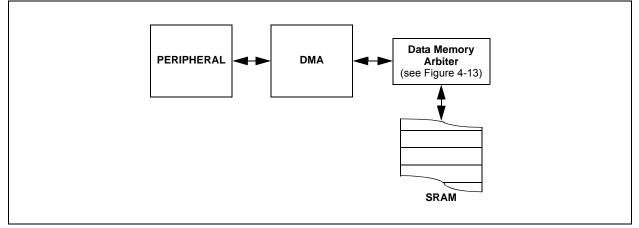

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| U-0          | U-0        | U-0              | U-0          | U-0                 | U-0              | U-0             | U-0    |

|--------------|------------|------------------|--------------|---------------------|------------------|-----------------|--------|

| —            |            | _                | —            | —                   | _                |                 | —      |

| bit 15       |            |                  |              |                     |                  |                 | bit 8  |

|              |            |                  |              |                     |                  |                 |        |

| U-0          | U-0        | U-0              | U-0          | R-0                 | R-0              | R-0             | R-0    |

| _            |            |                  | —            | RQCOL3              | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7        |            |                  |              |                     |                  |                 | bit 0  |

|              |            |                  |              |                     |                  |                 |        |

| Legend:      |            |                  |              |                     |                  |                 |        |

| R = Readab   | le bit     | W = Writable     | bit          | U = Unimpler        | nented bit, read | as '0'          |        |

| -n = Value a | t POR      | '1' = Bit is set |              | '0' = Bit is cle    | ared             | x = Bit is unkr | nown   |

|              |            |                  |              |                     |                  |                 |        |

| bit 15-4     | Unimplemer | nted: Read as '  | 0'           |                     |                  |                 |        |

| bit 3        | RQCOL3: Cl | nannel 3 Transfe | er Request C | Collision Flag bit  |                  |                 |        |

|              |            |                  |              | est collision is d  |                  |                 |        |

|              |            | •                | •            | est collision is n  |                  |                 |        |

| bit 2        |            |                  | •            | Collision Flag bit  |                  |                 |        |

|              |            |                  |              | est collision is de |                  |                 |        |

| L:1.4        |            | •                |              | est collision is no |                  |                 |        |

| bit 1        |            |                  | •            | Collision Flag bit  |                  |                 |        |

|              |            |                  |              | est collision is de |                  |                 |        |

| bit 0        |            | •                | •            | collision Flag bit  |                  |                 |        |

|              |            |                  | •            | est collision is d  |                  |                 |        |

|              |            |                  |              | est collision is n  |                  |                 |        |

|              |            |                  |              |                     |                  |                 |        |

## REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

## REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits <sup>(4)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111 = Reserved                                                                                                                                                           |

|         | 11110 = Reserved                                                                                                                                                           |

|         | 1110 = Reserved                                                                                                                                                            |

|         | 11100 = CTMU trigger is the source for the capture timer synchronization                                                                                                   |

|         | 11011 = ADC1 interrupt is the source for the capture timer synchronization <sup>(5)</sup>                                                                                  |

|         | 11010 = Analog Comparator 3 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11001 = Analog Comparator 2 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11000 = Analog Comparator 1 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10111 = Analog Comparator 5 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10110 = Analog Comparator 4 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10101 = Reserved                                                                                                                                                           |

|         | 10100 = Reserved                                                                                                                                                           |

|         | 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 01111 = GP Timer5 is the source for the capture timer synchronization                                                                                                      |

|         | 01110 = GP Timer4 is the source for the capture timer synchronization                                                                                                      |

|         | 01101 = GP Timer3 is the source for the capture timer synchronization                                                                                                      |

|         | 01100 = GP Timer2 is the source for the capture timer synchronization                                                                                                      |

|         | 01011 = GP Timer1 is the source for the capture timer synchronization                                                                                                      |

|         | 01010 = Reserved                                                                                                                                                           |

|         | 01001 = Reserved                                                                                                                                                           |

|         | 01000 = Input Capture 4 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00111 = Input Capture 3 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00101 = Input Capture 1 is the source for the capture timer synchronization <sup>(6)</sup><br>00100 = Output Compare 4 is the source for the capture timer synchronization |

|         | 00011 = Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00011 – Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00001 = Output Compare 1 is the source for the capture timer synchronization                                                                                               |

|         | 00000 = Reserved                                                                                                                                                           |

|         |                                                                                                                                                                            |

| Note 1: | The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.                                                                                              |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0 |

|---------------|----------------------|------------------|------------------|------------------|-------------------|-----------------|-------|

| F7BP3         | F7BP2                | F7BP1            | F7BP0            | F6BP3            | F6BP2             | F6BP1           | F6BP0 |

| bit 15        |                      | -                |                  |                  |                   |                 | bit 8 |

|               |                      |                  |                  |                  |                   |                 |       |

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0 |

| F5BP3         | F5BP2                | F5BP1            | F5BP0            | F4BP3            | F4BP2             | F4BP1           | F4BP0 |

| bit 7         |                      |                  |                  |                  |                   |                 | bit 0 |

|               |                      |                  |                  |                  |                   |                 |       |

| Legend:       |                      |                  |                  |                  |                   |                 |       |

| R = Readable  | e bit                | W = Writable     | bit              | U = Unimpler     | nented bit, read  | <b>as</b> '0'   |       |

| -n = Value at | POR                  | '1' = Bit is set |                  | '0' = Bit is cle | ared              | x = Bit is unkr | nown  |

|               |                      |                  |                  |                  |                   |                 |       |

| bit 15-12     | F7BP<3:0>:           | RX Buffer Masl   | k for Filter 7 b | its              |                   |                 |       |

|               | 1111 = Filter        | hits received in | NRX FIFO bu      | ffer             |                   |                 |       |

|               | 1110 <b>= Filter</b> | hits received in | RX Buffer 14     | 1                |                   |                 |       |

|               | •                    |                  |                  |                  |                   |                 |       |

|               | •                    |                  |                  |                  |                   |                 |       |

|               | •<br>0001 - Filtor   | hits received in |                  |                  |                   |                 |       |

|               | 0001                 | hits received in |                  |                  |                   |                 |       |

| bit 11-8      |                      |                  |                  | its (same value  | es as bits 15-12) |                 |       |

|               |                      |                  |                  | -                | -                 |                 |       |

| bit 7-4       | F3BP<3:0>:1          | KA Builer Masi   | CION FILTER 5 D  | its (same value  | es as bits 15-12) |                 |       |

## REGISTER 22-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

## REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 1 | <ul> <li>BUFM: Buffer Fill Mode Select bit</li> <li>1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt</li> <li>0 = Always starts filling the buffer from the Start address</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <ul> <li>ALTS: Alternate Input Sample Mode Select bit</li> <li>1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample</li> <li>0 = Always uses channel input selects for Sample MUX A</li> </ul>                         |

Note 1: The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

| Base<br>Instr<br># | Assembly<br>Mnemonic |                | Assembly Syntax | Description                                                            | # of<br>Words<br>1 | # of<br>Cycles | Status Flags<br>Affected<br>None |

|--------------------|----------------------|----------------|-----------------|------------------------------------------------------------------------|--------------------|----------------|----------------------------------|

| 53                 | MUL                  | MUL.SS         | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)                            |                    |                |                                  |

|                    |                      | MUL.SS         | Wb,Ws,Acc       | Accumulator = signed(Wb) * signed(Ws)                                  | 1                  | 1              | None                             |

|                    |                      | MUL.SU         | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                             | 1                  | 1              | None                             |

|                    |                      | MUL.SU         | Wb,Ws,Acc       | Accumulator = signed(Wb) *<br>unsigned(Ws)                             | 1                  | 1              | None                             |

|                    |                      | MUL.SU         | Wb,#lit5,Acc    | Accumulator = signed(Wb) * unsigned(lit5)                              | 1                  | 1              | None                             |

|                    |                      | MUL.US         | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)                             | 1                  | 1              | None                             |

|                    |                      | MUL.US         | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>signed(Ws)                             | 1                  | 1              | None                             |

|                    |                      | MUL.UU         | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)                        | 1                  | 1              | None                             |

|                    |                      | MUL.UU         | Wb,#lit5,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(lit5)                         | 1                  | 1              | None                             |

|                    |                      | MUL.UU         | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>unsigned(Ws)                           | 1                  | 1              | None                             |

|                    |                      | MULW.SS        | Wb,Ws,Wnd       | Wnd = signed(Wb) * signed(Ws)                                          | 1                  | 1              | None                             |

|                    |                      | MULW.SU        | Wb,Ws,Wnd       | Wnd = signed(Wb) * unsigned(Ws)                                        | 1                  | 1              | None                             |

|                    |                      | MULW.US        | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * signed(Ws)                                        | 1                  | 1              | None                             |

|                    |                      | MULW.UU        | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * unsigned(Ws)                                      | 1                  | 1              | None                             |

|                    |                      | MUL.SU         | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)                        | 1                  | 1              | None                             |

|                    |                      | MUL.SU         | Wb,#lit5,Wnd    | Wnd = signed(Wb) * unsigned(lit5)                                      | 1                  | 1              | None                             |

|                    |                      | MUL.UU         | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)                         | 1                  | 1              | None                             |

|                    |                      | MUL.UU         | Wb,#lit5,Wnd    | Wnd = unsigned(Wb) * unsigned(lit5)                                    | 1                  | 1              | None                             |

|                    |                      | MUL            | f               | W3:W2 = f * WREG                                                       | 1                  | 1              | None                             |

| 54                 | NEG                  | NEG            | Acc             | Negate Accumulator                                                     | 1                  | 1              | OA,OB,OAB,<br>SA,SB,SAB          |

|                    |                      | NEG            | f               | $f = \overline{f} + 1$                                                 | 1                  | 1              | C,DC,N,OV,Z                      |

|                    |                      | NEG            | f,WREG          | WREG = $\overline{f}$ + 1                                              | 1                  | 1              | C,DC,N,OV,Z                      |

|                    |                      | NEG            | Ws,Wd           | $Wd = \overline{Ws} + 1$                                               | 1                  | 1              | C,DC,N,OV,Z                      |

| 55                 | NOP                  | NOP            |                 | No Operation                                                           | 1                  | 1              | None                             |

|                    |                      | NOPR           |                 | No Operation                                                           | 1                  | 1              | None                             |

| 56                 | POP                  | POP            | f               | Pop f from Top-of-Stack (TOS)                                          | 1                  | 1              | None                             |

|                    |                      | POP<br>POP.D   | Wdo<br>Wnd      | Pop from Top-of-Stack (TOS) to Wdo<br>Pop from Top-of-Stack (TOS) to   | 1<br>1             | 1<br>2         | None<br>None                     |

|                    |                      |                |                 | W(nd):W(nd + 1)                                                        |                    |                |                                  |

|                    |                      | POP.S          |                 | Pop Shadow Registers                                                   | 1                  | 1              | All                              |

| 57                 | PUSH                 | PUSH           | f               | Push f to Top-of-Stack (TOS)                                           | 1                  | 1              | None                             |

|                    |                      | PUSH<br>PUSH.D | Wso<br>Wns      | Push Wso to Top-of-Stack (TOS)<br>Push W(ns):W(ns + 1) to Top-of-Stack | 1<br>1             | 1<br>2         | None<br>None                     |

|                    |                      | PUSH.S         |                 | (TOS) Push Shadow Registers                                            | 1                  | 1              | None                             |

| 58                 | PWRSAV               | PWRSAV         | #lit1           | Go into Sleep or Idle mode                                             | 1                  | 1              | WDTO,Sleep                       |

| 58<br>59           | RCALL                | RCALL          | Expr            | Relative Call                                                          | 1                  | 4              | SFA                              |

|                    | NCUTT                | RCALL          | Wn              | Computed Call                                                          | 1                  | 4              | SFA                              |

| 60                 | REPEAT               | REPEAT         | #lit15          | Repeat Next Instruction lit15 + 1 times                                | 1                  | 1              | None                             |

| 00                 |                      | REPEAT         | Wn              | Repeat Next Instruction (Wn) + 1 times                                 | 1                  | 1              | None                             |

| 61                 | RESET                | RESET          |                 | Software device Reset                                                  | 1                  | 1              | None                             |

| 62                 | RETFIE               | RETFIE         |                 | Return from interrupt                                                  | 1                  | 6 (5)          | SFA                              |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 30.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC