#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm102-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | ••    |           | •                 |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

|-------------|-------|-----------|-------------------|--------|--------|--------|--------|------------|-------------|---------------|---------------|-------------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15    | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7         | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |           |                   |        |        |        |        |            | Tim         | ner1 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR1         | 0102  |           |                   |        |        |        |        |            | Peri        | od Register   | 1             |             |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON       | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |           | Timer2 Register   |        |        |        |        |            |             |               |               | 0000        |        |       |       |       |       |               |

| TMR3HLD     | 0108  |           |                   |        |        |        | Time   | er3 Holdin | ig Register | · (For 32-bit | timer operat  | tions only) |        |       |       |       |       | 0000          |

| TMR3        | 010A  |           |                   |        |        |        |        |            | Tim         | ner3 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR2         | 010C  |           | Period Register 2 |        |        |        |        |            |             |               | FFFF          |             |        |       |       |       |       |               |

| PR3         | 010E  |           |                   |        |        |        |        |            | Peri        | od Register   | 3             |             |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON       | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON       | _                 | TSIDL  | _      | _      | _      | _          | —           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |           |                   |        |        |        |        |            | Tim         | ner4 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116  |           |                   |        |        |        | Т      | imer5 Hol  | ding Regis  | ster (For 32- | bit operation | ns only)    |        |       |       |       |       | 0000          |

| TMR5        | 0118  |           |                   |        |        |        |        |            | Tim         | ner5 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR4         | 011A  |           |                   |        |        |        |        |            | Peri        | od Register   | 4             |             |        |       |       |       |       | FFFF          |

| PR5         | 011C  |           |                   |        |        |        |        |            | Peri        | od Register   | 5             |             |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON       | _                 | TSIDL  | —      | —      | —      | —          | —           | —             | TGATE         | TCKPS1      | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON       | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| Lonondi     |       | nlamantad | 1 1-              |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE       | E 4-23 | 3: IN  | ITERRU   | ЈРТ СО   | NTROL    | LER RE  | GISTER    | MAP FO     | R dsPIC   | 33EVXX   | XGM00>   | K/10X FA    | MILY D   | EVICES  | (CONTI    | NUED)       |           |               |

|-------------|--------|--------|----------|----------|----------|---------|-----------|------------|-----------|----------|----------|-------------|----------|---------|-----------|-------------|-----------|---------------|

| SFR<br>Name | Addr.  | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10    | Bit 9      | Bit 8     | Bit 7    | Bit 6    | Bit 5       | Bit 4    | Bit 3   | Bit 2     | Bit 1       | Bit 0     | All<br>Resets |

| IPC19       | 0866   | -      | —        | —        | -        | —       | —         | —          | —         | —        |          | CTMUIP<2:0> | •        | _       | —         | —           | —         | 0040          |

| IPC23       | 086E   | _      | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2   | PWM1IP1    | PWM1IP0   | _        | _        | _           | _        | _       | _         | _           | _         | 4400          |

| IPC24       | 0870   | _      | _        | _        | _        | _       | _         | _          | _         | _        | _        | _           | _        | _       |           | PWM3IP<2:0> | •         | 0004          |

| IPC35       | 0886   | _      | _        | _        | _        | _       |           | ICDIP<2:0> |           | _        | _        | _           | _        | _       | _         | _           | _         | 0400          |

| IPC43       | 0896   | _      | _        | _        | _        | _       | _         | _          | _         | _        | l        | 2C1BCIP<2:0 | >        | _       | _         | _           | _         | 0040          |

| IPC45       | 089A   | _      | SENT1IP2 | SENT1IP1 | SENT1IP0 | _       | SENT1EIP2 | SENT1EIP1  | SENT1EIP0 | _        | _        | _           | _        | _       | _         | _           | _         | 4400          |

| IPC46       | 089C   | _      | _        | _        | _        | _       | ECCSBEIP2 | ECCSBEIP1  | ECCSBEIP0 | _        | SENT2IP2 | SENT2IP1    | SENT2IP0 | _       | SENT2EIP2 | SENT2EIP1   | SENT2EIP0 | 0444          |

| INTCON1     | 08C0   | NSTDIS | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE     | OVBTE      | COVTE     | SFTACERR | DIV0ERR  | DMACERR     | MATHERR  | ADDRERR | STKERR    | OSCFAIL     | _         | 0000          |

| INTCON2     | 08C2   | GIE    | DISI     | SWTRAP   | _        | _       | _         | _          | AIVTEN    | _        | _        | _           | _        | _       | INT2EP    | INT1EP      | INT0EP    | 0000          |

| INTCON3     | 08C4   | DMT    | —        | —        | —        | —       | —         | —          | —         | —        | —        | DAE         | DOOVR    | _       | —         | —           | —         | 0000          |

| INTCON4     | 08C6   | _      | —        | —        | —        | —       | —         | —          | —         | —        | —        | _           | —        | _       | —         | ECCDBE      | SGHT      | 0000          |

| INTTREG     | 08C8   | _      | _        | _        | _        | _       | ILR3      | ILR2       | ILR1      | VECNUM7  | VECNUM6  | VECNUM5     | VECNUM4  | VECNUM3 | VECNUM2   | VECNUM1     | VECNUM0   | 0000          |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: — = unimplemented, read as '0' Reset values are shown in hexadecimal. Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

#### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

x = Bit is unknown

| <b>Legend:</b><br>R = Readable | bit                   | C = Clearable<br>W = Writable I |       | U = Unimpler | nented bit, read | as '0' |       |

|--------------------------------|-----------------------|---------------------------------|-------|--------------|------------------|--------|-------|

| bit 7                          |                       |                                 |       |              |                  |        | bit 0 |

| IPL2 <sup>(2,3)</sup>          | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup>           | RA    | Ν            | OV               | Z      | С     |

| R/W-0                          | R/W-0                 | R/W-0                           | R-0   | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| bit 15                         |                       |                                 |       |              |                  |        | bit 8 |

|                                | UB                    | SA                              | 30    | UAB          | SAD              | DA     |       |

| OA                             | OB                    | SA                              | SB    | OAB          | SAB              | DA     | DC    |

| R/W-0                          | R/W-0                 | R/W-0                           | R/W-0 | R/C-0        | R/C-0            | R-0    | R/W-0 |

'0' = Bit is cleared

#### **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

'1' = Bit is set

**Note 1:** For complete register details, see Register 3-1.

-n = Value at POR

- **2:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

|              | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|--------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------|-------------------|------------------|--------------------|-------|--|

| IC2R7        | IC2R6                                                             | IC2R5                                                                                   | IC2R4                                        | IC2R3             | IC2R2            | IC2R1              | IC2R0 |  |

| oit 15       |                                                                   |                                                                                         |                                              |                   |                  |                    | bit 8 |  |

| R/W-0        | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

| IC1R7        | IC1R6                                                             | IC1R5                                                                                   | IC1R4                                        | IC1R3             | IC1R2            | IC1R1              | IC1R0 |  |

| it 7         |                                                                   |                                                                                         |                                              | -                 |                  |                    | bit 0 |  |

| .egend:      |                                                                   |                                                                                         |                                              |                   |                  |                    |       |  |

| R = Readable | e bit                                                             | W = Writable                                                                            | bit                                          | U = Unimpler      | nented bit, read | <b>d as</b> '0'    |       |  |

| n = Value at | POR                                                               | '1' = Bit is set                                                                        |                                              | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

|              | 10110101 -                                                        |                                                                                         |                                              |                   |                  |                    |       |  |

|              | •<br>•                                                            | <ul> <li>Input tied to RI</li> <li>Input tied to CI</li> </ul>                          |                                              |                   |                  |                    |       |  |

|              | •<br>•<br>000000001 =<br>00000000 =                               | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS                                    |                   |                  |                    |       |  |

| bit 7-0      | •<br>•<br>00000001 =<br>00000000 =<br>IC1R<7:0>:                  | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> <li>Assign Input Ca</li> </ul> | MP1<br>SS<br>apture 1 (IC1)                  |                   | onding RPn Pir   | n bits             |       |  |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

| vit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

## REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , <b>read as</b> '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP49R<5:0>:** Peripheral Output Function is Assigned to RP49 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits

(see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits 11111 = OCxRS compare event is used for synchronization 11110 = INT2 is the source for compare timer synchronization 11101 = INT1 is the source for compare timer synchronization 11100 = CTMU Trigger is the source for compare timer synchronization 11011 = ADC1 interrupt is the source for compare timer synchronization 11010 = Analog Comparator 3 is the source for compare timer synchronization 11001 = Analog Comparator 2 is the source for compare timer synchronization 11000 = Analog Comparator 1 is the source for compare timer synchronization 10111 = Analog Comparator 5 is the source for compare timer synchronization 10110 = Analog Comparator 4 is the source for compare timer synchronization 10101 = Capture timer is unsynchronized 10100 = Capture timer is unsynchronized 10011 = Input Capture 4 interrupt is the source for compare timer synchronization 10010 = Input Capture 3 interrupt is the source for compare timer synchronization 10001 = Input Capture 2 interrupt is the source for compare timer synchronization 10000 = Input Capture 1 interrupt is the source for compare timer synchronization 01111 = GP Timer5 is the source for compare timer synchronization 01110 = GP Timer4 is the source for compare timer synchronization 01101 = GP Timer3 is the source for compare timer synchronization 01100 = GP Timer2 is the source for compare timer synchronization 01011 = GP Timer1 is the source for compare timer synchronization 01010 = Compare timer is unsynchronized 01001 = Compare timer is unsynchronized 01000 = Capture timer is unsynchronized 00101 = Compare timer is unsynchronized 00100 = Output Compare 4 is the source for compare timer synchronization<sup>(1,2)</sup> 00011 = Output Compare 3 is the source for compare timer synchronization<sup>(1,2)</sup> 00010 = Output Compare 2 is the source for compare timer synchronization<sup>(1,2)</sup> 00001 = Output Compare 1 is the source for compare timer synchronization<sup>(1,2)</sup>

- 00000 = Compare timer is unsynchronized

- **Note 1:** Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

## 17.0 HIGH-SPEED PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM Generators

- Two PWM Outputs per PWM Generator

- Individual Period and Duty Cycle for each PWM Pair

- Duty Cycle, Dead Time, Phase Shift and Frequency Resolution of 8.32 ns

- Independent Fault and Current-Limit Inputs for Six PWM Outputs

- Redundant Output

- Center-Aligned PWM mode

- Output Override Control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for Input Clock

- PWMxL and PWMxH Output Pin Swapping

- Independent PWM Frequency, Duty Cycle and Phase-Shift Changes for each PWM Generator

- Dead-Time Compensation

- Enhanced Leading-Edge Blanking (LEB) Functionality

- Frequency Resolution Enhancement

- PWM Capture Functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns at 60 MIPS.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on the master time base.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin, that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 17-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 17.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs as follows:

- FLT1 and FLT2, available on 28-pin, 44-pin and 64-pin packages, which are remappable using the PPS feature

- FLT3, available on 44-pin and 64-pin packages, which is available as a fixed pin

- FLT4-FLT8, available on 64-pin packages, which are available as fixed pins

- · FLT32 is available on a fixed pin on all devices

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 17.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

**Note:** The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCONx<1:0>), regardless of the state of FLT32.

| R/W-1           | R/W-1            | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

|-----------------|------------------|-----------------------------------------------------------------------------------|--------------------------|----------------------|------------------------------|-----------------|--------|

| PENH            | PENL             | POLH                                                                              | POLL                     | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>         | OVRENH          | OVRENL |

| bit 15          |                  |                                                                                   |                          |                      |                              |                 | bit 8  |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| R/W-0           | R/W-0            | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

| OVRDAT1         | OVRDAT0          | FLTDAT1                                                                           | FLTDAT0                  | CLDAT1               | CLDAT0                       | SWAP            | OSYNC  |

| bit 7           |                  |                                                                                   |                          |                      |                              |                 | bit 0  |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| Legend:         |                  |                                                                                   |                          |                      |                              |                 |        |

| R = Readable    | bit              | W = Writable                                                                      | bit                      | U = Unimplei         | mented bit, read             | <b>as</b> '0'   |        |

| -n = Value at F | POR              | '1' = Bit is set                                                                  |                          | '0' = Bit is cle     | eared                        | x = Bit is unkr | nown   |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| bit 15          | PENH: PWM        | xH Output Pin                                                                     | Ownership bit            |                      |                              |                 |        |

|                 |                  | odule controls                                                                    |                          |                      |                              |                 |        |

|                 |                  | dule controls th                                                                  | •                        | ו                    |                              |                 |        |

| bit 14          |                  | L Output Pin                                                                      | •                        |                      |                              |                 |        |

|                 |                  | odule controls<br>dule controls th                                                |                          |                      |                              |                 |        |

| bit 13          |                  | xH Output Pin                                                                     | •                        | I                    |                              |                 |        |

| DIL 13          |                  | bin is active-low                                                                 | •                        |                      |                              |                 |        |

|                 |                  | pin is active-hig                                                                 |                          |                      |                              |                 |        |

| bit 12          |                  | <l f<="" output="" pin="" td=""><td></td><td></td><td></td><td></td><td></td></l> |                          |                      |                              |                 |        |

|                 |                  | in is active-low                                                                  |                          |                      |                              |                 |        |

|                 | 0 = PWMxL p      | in is active-hig                                                                  | h                        |                      |                              |                 |        |

| bit 11-10       | PMOD<1:0>:       | PWMx I/O Pin                                                                      | Mode bits <sup>(1)</sup> |                      |                              |                 |        |

|                 | 11 = Reserve     |                                                                                   |                          |                      |                              |                 |        |

|                 |                  | /O pin pair is ir<br>/O pin pair is ir                                            |                          |                      |                              |                 |        |

|                 |                  | O pin pair is in<br>O pin pair is ir                                              |                          | •                    |                              |                 |        |

| bit 9           |                  | verride Enable                                                                    | -                        |                      |                              |                 |        |

|                 | 1 = OVRDAT       | 1 controls the o                                                                  | output on the I          | PWMxH pin            |                              |                 |        |

|                 |                  | enerator contro                                                                   |                          |                      |                              |                 |        |

| bit 8           | OVRENL: Ov       | erride Enable                                                                     | for PWMxL Pi             | n bit                |                              |                 |        |

|                 |                  | 0 controls the o                                                                  | •                        |                      |                              |                 |        |

|                 | •                | nerator contro                                                                    |                          | •                    |                              |                 |        |

| bit 7-6         |                  |                                                                                   |                          |                      | ide is Enabled b             | its             |        |

|                 |                  | •                                                                                 |                          |                      | d by OVRDAT1.<br>by OVRDAT0. |                 |        |

| bit 5-4         |                  |                                                                                   |                          | •                    | TMOD is Enable               | d hits          |        |

|                 |                  | ve, PWMxH is                                                                      |                          |                      |                              |                 |        |

|                 |                  | ve, PWMxL is                                                                      |                          |                      |                              |                 |        |

| bit 3-2         |                  |                                                                                   |                          | •                    | /IOD is Enabled              | bits            |        |

|                 | If current limit | is active, PWI                                                                    | MxH is driven            | to the state sp      | ecified by CLDA              | T1.             |        |

|                 | If current limit | is active, PWI                                                                    | MxL is driven t          | o the state spe      | ecified by CLDA              | ГО.             |        |

| Note 1: The     | ese bits should  | not be change                                                                     | d after the PW           | /Mx module is        | enabled (PTEN                | = 1).           |        |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

**Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1). **2:** If the PWMI OCK Configuration bit (EDEVOPT<0>) is a '1' the IOCONy register can only be

2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                    | U-0                                                                  | R/W-0, HC                           | R/W-0                                                                    | R-0                 | R-1             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|---------------------|-----------------|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UTXISEL0                                                                                 | _                                                                    | UTXBRK                              | UTXEN <sup>(1)</sup>                                                     | UTXBF               | TRMT            |

| bit 15          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |                                                                      |                                     |                                                                          |                     | bit 8           |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                                      |                                     |                                                                          |                     |                 |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                    | R-1                                                                  | R-0                                 | R-0                                                                      | R/C-0               | R-0             |

| URXISEL1        | URXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADDEN                                                                                    | RIDLE                                                                | PERR                                | FERR                                                                     | OERR                | URXDA           |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                                      |                                     |                                                                          |                     | bit 0           |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | O Oleenskie                                                                              | L :4                                                                 |                                     |                                                                          |                     |                 |

| Legend:         | <b>L</b> :4                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C = Clearable                                                                            |                                                                      |                                     | are Clearable bit                                                        |                     |                 |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable                                                                             | DIT                                                                  | •                                   | mented bit, read                                                         |                     |                 |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                         |                                                                      | '0' = Bit is cle                    | ared                                                                     | x = Bit is unkr     | IOWN            |

| bit 15,13       | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>the trans</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                       | ed; do not use<br>t when a chara<br>smit buffer beco<br>t when the las<br>ns are complet | cter is transf<br>omes empty<br>it character<br>ed<br>cter is transf | is shifted out<br>Ferred to the Tra | election bits<br>ansmit Shift Reg<br>of the Transmit<br>ansmit Shift Reg | t Shift Registe     | r; all transmit |

| bit 14          | $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle}}$ $0 = \text{UxTX Idle}$ $\frac{\text{If IREN = 1:}}{1 = \text{IrDA}^{\textcircled{\ensuremath{\mathbb{R}}}} \text{ end}$ $0 = \text{IrDA ended}$                                                                                                                                                                                                                                                                                  | e state is '1'<br>coded UxTX Id<br>oded UxTX Idle                                        | le state is '1'<br>e state is '0'                                    |                                     |                                                                          |                     |                 |

| bit 12          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as 'o                                                                          | )'                                                                   |                                     |                                                                          |                     |                 |

| bit 11          | 1 = Sends Sy<br>bit; cleare<br>0 = Sync Bre                                                                                                                                                                                                                                                                                                                                                                                                                                         | ed by hardware<br>ak transmission                                                        | ext transmis<br>upon comp<br>n is disabled                           |                                     | followed by twe                                                          | elve '0' bits, foll | lowed by Stop   |

| bit 10          | UTXEN: UAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Tx Transmit Er                                                                           | nable bit <sup>(1)</sup>                                             |                                     |                                                                          |                     |                 |

|                 | 0 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                                                                      | ntrolled by UAR<br>ransmission is   | Tx<br>aborted and the                                                    | e buffer is rese    | t; UxTX pin is  |

| bit 9           | UTXBF: UAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Tx Transmit Bu                                                                           | iffer Full Stat                                                      | us bit (read-onl                    | y)                                                                       |                     |                 |

|                 | 1 = Transmit<br>0 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          | ll, at least on                                                      | e more charact                      | er can be writte                                                         | n                   |                 |

| bit 8           | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Shift Register is                                                                        | s empty and                                                          |                                     | ly)<br>s empty (the last<br>is in progress o                             |                     | as completed)   |

| bit 7-6         | URXISEL<1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0>: UARTx Red                                                                            | ceive Interrup                                                       | ot Mode Selecti                     | on bits                                                                  |                     |                 |

|                 | <ul> <li>URXISEL&lt;1:0&gt;: UARTx Receive Interrupt Mode Selection bits</li> <li>11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters</li> </ul> |                                                                                          |                                                                      |                                     |                                                                          |                     |                 |

#### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

#### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5   | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>               |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|         | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul> |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|         | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive<br/>FIFO)</li> </ul>                                            |

|         | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                             |

|         | 1 = Receive buffer has overflowed                                                                                                                                           |

|         | 0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) resets the receive buffer and the UxRSR to the empty state         |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                  |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/                                                                                 |

PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

## 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

## 27.3 On-Chip Voltage Regulator

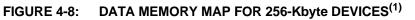

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

3: Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

## 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the Power-up Timer (PWRT) Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device should VDD fall below the BOR threshold voltage.

| DC CHARACT       | ERISTICS            |      | (unless oth      | perating Condition<br>erwise stated)<br>emperature -40°C =<br>-40°C = |              |           |  |  |  |

|------------------|---------------------|------|------------------|-----------------------------------------------------------------------|--------------|-----------|--|--|--|

| Parameter<br>No. | Typ. <sup>(2)</sup> | Max. | Units Conditions |                                                                       |              |           |  |  |  |

| Idle Current (li | dle) <sup>(1)</sup> |      |                  | ·                                                                     |              |           |  |  |  |

| DC40d            | 1.25                | 2    | mA               | -40°C                                                                 |              |           |  |  |  |

| DC40a            | 1.25                | 2    | mA               | +25°C                                                                 | 5.0V         | 10 MIPS   |  |  |  |

| DC40b            | 1.5                 | 2.6  | mA               | +85°C                                                                 | 5.00         |           |  |  |  |

| DC40c            | 1.5                 | 2.6  | mA               | +125°C                                                                |              |           |  |  |  |

| DC42d            | 2.3                 | 3    | mA               | -40°C                                                                 |              |           |  |  |  |

| DC42a            | 2.3                 | 3    | mA               | +25°C                                                                 | 5.0V         | 20 MIPS   |  |  |  |

| DC42b            | 2.6                 | 3.45 | mA               | +85°C                                                                 | 5.00         | 20 1011-5 |  |  |  |

| DC42c            | 2.6                 | 3.85 | mA               | +125°C                                                                | -            |           |  |  |  |

| DC44d            | 6.9                 | 8    | mA               | -40°C                                                                 |              |           |  |  |  |

| DC44a            | 6.9                 | 8    | mA               | +25°C                                                                 | 5.0V 70 MIPS |           |  |  |  |

| DC44b            | 7.25                | 8.6  | mA               | +85°C                                                                 | 1            |           |  |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

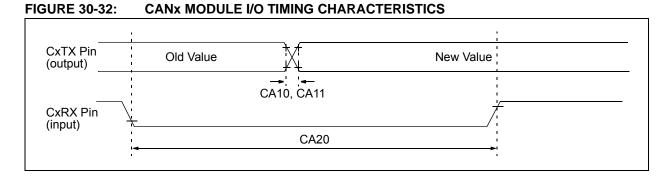

#### TABLE 30-48: CANx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                        |                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |  |

|--------------------|--------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param<br>No.       | Symbol Characteristic <sup>1</sup>                     |                       |                                                                                                                                                                                                                                                                                         | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| CA10               | TIOF                                                   | Port Output Fall Time | —                                                                                                                                                                                                                                                                                       | —                   |      | ns    | See Parameter DO32 |  |

| CA11               | TIOR                                                   | Port Output Rise Time | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 |  |