Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm103-e-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

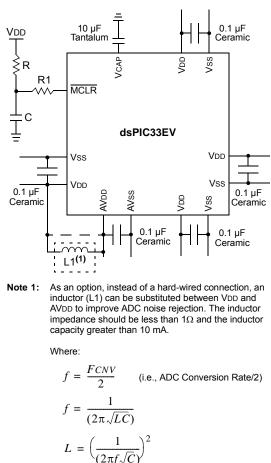

#### TANK CAPACITORS 2.2.1

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor** Connection (VCAP)

A low-ESR (<1 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a capacitor greater than 4.7 µF (10 µF is recommended), with at least a 16V rating connected to the ground. The type can be ceramic or tantalum. See Section 30.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length should not exceed one-quarter inch (6 mm).

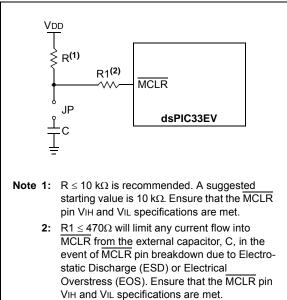

#### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- · Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-1, it is recommended that the capacitor, C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### EXAMPLE OF MCLR PIN CONNECTIONS

# REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = Overflow has not occurred for signed arithmetic                                                                                                                                                          |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                              |

| Note 1. | The IPI <2:0> hits are concatenated with the IPI 3 hit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                      |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

# **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------------|-------|-------|-------|-----------------|-------|-------|-------|

|                                                                       |       |       | PAD   | <15:8>          |       |       |       |

| bit 15                                                                |       |       |       |                 |       |       | bit 8 |

|                                                                       |       |       |       |                 |       |       |       |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|                                                                       |       |       | PAI   | )<7:0>          |       |       |       |

| bit 7                                                                 |       |       |       |                 |       |       | bit 0 |

|                                                                       |       |       |       |                 |       |       |       |

| Legend:                                                               |       |       |       |                 |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'  |       |       |       |                 |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       |       |       | x = Bit is unkr | nown  |       |       |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|------------------|-------|-------|

| —      | —   |       |       | CNT<  | 13:8> <b>(2)</b> |       |       |

| bit 15 |     |       |       |       |                  |       | bit 8 |

| R/W-0                   | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------------------|----------|-------|-------|-------|-------|-------|-------|--|--|

| CNT<7:0> <sup>(2)</sup> |          |       |       |       |       |       |       |  |  |

| bit 7                   | bit 7 bi |       |       |       |       |       |       |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

| U-0          | U-0        | U-0              | U-0          | U-0                 | U-0              | U-0             | U-0    |  |  |

|--------------|------------|------------------|--------------|---------------------|------------------|-----------------|--------|--|--|

| —            |            | _                | —            | —                   | _                |                 | —      |  |  |

| bit 15       |            |                  |              |                     |                  |                 | bit 8  |  |  |

|              |            |                  |              |                     |                  |                 |        |  |  |

| U-0          | U-0        | U-0              | U-0          | R-0                 | R-0              | R-0             | R-0    |  |  |

| _            |            |                  | —            | RQCOL3              | RQCOL2           | RQCOL1          | RQCOL0 |  |  |

| bit 7        |            |                  |              |                     |                  |                 | bit 0  |  |  |

|              |            |                  |              |                     |                  |                 |        |  |  |

| Legend:      |            |                  |              |                     |                  |                 |        |  |  |

| R = Readab   | le bit     | W = Writable     | bit          | U = Unimpler        | nented bit, read | as '0'          |        |  |  |

| -n = Value a | t POR      | '1' = Bit is set |              | '0' = Bit is cle    | ared             | x = Bit is unkr | nown   |  |  |

|              |            |                  |              |                     |                  |                 |        |  |  |

| bit 15-4     | Unimplemer | nted: Read as '  | 0'           |                     |                  |                 |        |  |  |

| bit 3        | RQCOL3: Cl | nannel 3 Transfe | er Request C | Collision Flag bit  |                  |                 |        |  |  |

|              |            |                  |              | est collision is d  |                  |                 |        |  |  |

|              |            | •                | •            | est collision is n  |                  |                 |        |  |  |

| bit 2        |            |                  | •            | Collision Flag bit  |                  |                 |        |  |  |

|              |            |                  |              | est collision is de |                  |                 |        |  |  |

| L:1.4        |            | •                |              | est collision is no |                  |                 |        |  |  |

| bit 1        |            |                  | •            | Collision Flag bit  |                  |                 |        |  |  |

|              |            |                  |              | est collision is de |                  |                 |        |  |  |

| bit 0        |            | •                | •            | collision Flag bit  |                  |                 |        |  |  |

|              |            |                  | •            | est collision is d  |                  |                 |        |  |  |

|              |            |                  |              | est collision is n  |                  |                 |        |  |  |

|              |            |                  |              |                     |                  |                 |        |  |  |

# REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

These modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 and Timer4/5 operate in the following three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules

- ADC1 Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. The T3CON and T5CON registers are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw). Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, the T3CON and T5CON control bits are ignored. Only the T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

Block diagrams for the Type B and Type C timers are shown in Figure 13-1 and Figure 13-2, respectively.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, Timer3, Timer4 and Timer5 can trigger a DMA data transfer.

# 20.3 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATH/L register. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data register before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 20-3.

### EQUATION 20-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME<15:0> = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |  |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |  |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |  |  |  |  |  |

### 20.3.1 RECEIVE MODE CONFIGURATION

#### 20.3.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period – 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATH/L register after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

| U-0             | R/W-x                                                                       | U-0                               | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x     |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------|-----------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|--|--|

| —               | WAKFIL                                                                      |                                   | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0   |  |  |  |  |

| bit 15          |                                                                             |                                   |                  |                  |                  |                 | bit 8     |  |  |  |  |

|                 |                                                                             |                                   |                  |                  |                  |                 |           |  |  |  |  |

| R/W-x           | R/W-x                                                                       | R/W-x                             | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x     |  |  |  |  |

| SEG2PHTS        | SAM                                                                         | SEG1PH2                           | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0    |  |  |  |  |

| bit 7           |                                                                             |                                   |                  |                  |                  |                 | bit 0     |  |  |  |  |

| Legend:         |                                                                             |                                   |                  |                  |                  |                 |           |  |  |  |  |

| R = Readable    | bit                                                                         | W = Writable                      | bit              | U = Unimpler     | nented bit, read | <b>d as</b> '0' |           |  |  |  |  |

| -n = Value at I | POR                                                                         | '1' = Bit is set                  |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown      |  |  |  |  |

| -               |                                                                             |                                   |                  |                  |                  |                 |           |  |  |  |  |

| bit 15          | Unimplemer                                                                  | nted: Read as '                   | כי               |                  |                  |                 |           |  |  |  |  |

| bit 14          | WAKFIL: Sel                                                                 | lect CAN Bus L                    | ine Filter for V | Vake-up bit      |                  |                 |           |  |  |  |  |

|                 |                                                                             | N bus line filter                 |                  |                  |                  |                 |           |  |  |  |  |

| 1.11.4.0.44     |                                                                             | line filter is not                |                  | e-up             |                  |                 |           |  |  |  |  |

| bit 13-11       | •                                                                           | nted: Read as '                   |                  |                  |                  |                 |           |  |  |  |  |

| bit 10-8        | <b>SEG2PH&lt;2:0&gt;:</b> Phase Segment 2 bits<br>111 = Length is 8 x TQ    |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           | ·                                 |                  |                  |                  |                 |           |  |  |  |  |

| L:1 7           | 000 = Length                                                                |                                   |                  | -1 1-11          |                  |                 |           |  |  |  |  |

| bit 7           | <b>SEG2PHTS:</b> Phase Segment 2 Time Select bit<br>1 = Freely programmable |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 |                                                                             | n of SEG1PH<2                     | :0> bits or Inf  | ormation Proce   | essing Time (IP  | T), whichever i | s greater |  |  |  |  |

| bit 6           | SAM: Sample                                                                 | e of the CAN B                    | us Line bit      |                  |                  |                 |           |  |  |  |  |

|                 |                                                                             | s sampled three<br>s sampled once |                  |                  |                  |                 |           |  |  |  |  |

| bit 5-3         |                                                                             | -                                 | -                |                  |                  |                 |           |  |  |  |  |

|                 | SEG1PH<2:0>: Phase Segment 1 bits<br>111 = Length is 8 x TQ                 |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | 000 = Length                                                                | n is 1 x Tq                       |                  |                  |                  |                 |           |  |  |  |  |

| bit 2-0         | -                                                                           | >: Propagation                    | Time Segmen      | t bits           |                  |                 |           |  |  |  |  |

|                 | 111 = Length                                                                |                                   | Ū                |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | •                                                                           |                                   |                  |                  |                  |                 |           |  |  |  |  |

|                 | 000 = Length                                                                | n is 1 x Tq                       |                  |                  |                  |                 |           |  |  |  |  |

|                 | - 3-                                                                        |                                   |                  |                  |                  |                 |           |  |  |  |  |

# REGISTER 22-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

| R/W-0         | R/W-0                                                                   | R/W-0                                                                                | R/W-0            | R/W-0                              | R/W-0                          | R/W-0              | R/W-0 |  |  |

|---------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------|------------------------------------|--------------------------------|--------------------|-------|--|--|

| F7BP3         | F7BP2                                                                   | F7BP1                                                                                | F7BP0            | F6BP3                              | F6BP2                          | F6BP1              | F6BP0 |  |  |

| bit 15        | bit 15                                                                  |                                                                                      |                  |                                    |                                |                    | bit 8 |  |  |

|               |                                                                         |                                                                                      |                  |                                    |                                |                    |       |  |  |

| R/W-0         | R/W-0                                                                   | R/W-0                                                                                | R/W-0            | R/W-0                              | R/W-0                          | R/W-0              | R/W-0 |  |  |

| F5BP3         | F5BP2                                                                   | F5BP1                                                                                | F5BP0            | F4BP3                              | F4BP2                          | F4BP1              | F4BP0 |  |  |

| bit 7         |                                                                         |                                                                                      |                  |                                    |                                |                    | bit 0 |  |  |

|               |                                                                         |                                                                                      |                  |                                    |                                |                    |       |  |  |

| Legend:       |                                                                         |                                                                                      |                  |                                    |                                |                    |       |  |  |

| R = Readable  | e bit                                                                   | W = Writable bit                                                                     |                  | U = Unimplemented bit, read as '0' |                                |                    |       |  |  |

| -n = Value at | POR                                                                     | '1' = Bit is set                                                                     |                  | '0' = Bit is cleared               |                                | x = Bit is unknown |       |  |  |

|               |                                                                         |                                                                                      |                  |                                    |                                |                    |       |  |  |

| bit 15-12     | F7BP<3:0>:                                                              | RX Buffer Masl                                                                       | k for Filter 7 b | its                                |                                |                    |       |  |  |

|               | 1111 = Filter                                                           | hits received in                                                                     | NRX FIFO bu      | ffer                               |                                |                    |       |  |  |

|               | 1110 <b>= Filter</b>                                                    | hits received in                                                                     | RX Buffer 14     | 1                                  |                                |                    |       |  |  |

|               | •                                                                       |                                                                                      |                  |                                    |                                |                    |       |  |  |

|               | •                                                                       |                                                                                      |                  |                                    |                                |                    |       |  |  |

|               | •<br>0001 - Filtor                                                      | hits received in                                                                     |                  |                                    |                                |                    |       |  |  |

|               | 0001                                                                    | hits received in                                                                     |                  |                                    |                                |                    |       |  |  |

| bit 11-8      |                                                                         |                                                                                      |                  | its (same value                    | $a_{\rm r}$ as hits $15_{-12}$ |                    |       |  |  |

|               |                                                                         | <b>F6BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 6 bits (same values as bits 15-12) |                  |                                    |                                |                    |       |  |  |

| bit 7-4       | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |                                                                                      |                  |                                    |                                |                    |       |  |  |

# REGISTER 22-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

| R/W-0         | R/W-0                                                                     | R/W-0            | R/W-0            | R/W-0                        | R/W-0            | R/W-0               | R/W-0        |  |  |

|---------------|---------------------------------------------------------------------------|------------------|------------------|------------------------------|------------------|---------------------|--------------|--|--|

| F15BP3        | F15BP2                                                                    | F15BP1           | F15BP0           | F14BP3                       | F14BP2           | F14BP1              | F14BP0       |  |  |

| bit 15        |                                                                           |                  |                  |                              | •                |                     | bit 8        |  |  |

|               |                                                                           |                  |                  |                              |                  |                     |              |  |  |

| R/W-0         | R/W-0                                                                     | R/W-0            | R/W-0            | R/W-0                        | R/W-0            | R/W-0               | R/W-0        |  |  |

| F13BP3        | F13BP2                                                                    | F13BP1           | F13BP0           | F12BP3                       | F12BP2           | F12BP1              | F12BP0       |  |  |

| bit 7         |                                                                           |                  |                  |                              |                  |                     | bit 0        |  |  |

|               |                                                                           |                  |                  |                              |                  |                     |              |  |  |

| Legend:       |                                                                           |                  |                  |                              |                  |                     |              |  |  |

| R = Readable  | e bit                                                                     | W = Writable     | bit              | U = Unimpler                 | mented bit, read | ed bit, read as '0' |              |  |  |

| -n = Value at | POR                                                                       | '1' = Bit is set |                  | '0' = Bit is cleared x = Bit |                  | x = Bit is unkr     | t is unknown |  |  |

|               |                                                                           |                  |                  |                              |                  |                     |              |  |  |

| bit 15-12     | F15BP<3:0>:                                                               | RX Buffer Ma     | sk for Filter 15 | 5 bits                       |                  |                     |              |  |  |

|               | 1111 = Filter                                                             | hits received in | n RX FIFO but    | ffer                         |                  |                     |              |  |  |

|               | 1110 <b>= Filter</b>                                                      | hits received in | n RX Buffer 14   | ļ.                           |                  |                     |              |  |  |

|               | •                                                                         |                  |                  |                              |                  |                     |              |  |  |

|               | •                                                                         |                  |                  |                              |                  |                     |              |  |  |

|               | 0001 <b>= Filter</b>                                                      | hits received ir | n RX Buffer 1    |                              |                  |                     |              |  |  |

|               | 0000 <b>= Filter</b>                                                      | hits received in | n RX Buffer 0    |                              |                  |                     |              |  |  |

| bit 11-8      | F14BP<3:0>:                                                               | RX Buffer Ma     | sk for Filter 14 | l bits (same va              | lues as bits 15- | 12)                 |              |  |  |

| bit 7-4       | F13BP<3:0>:                                                               | RX Buffer Ma     | sk for Filter 13 | 3 bits (same va              | lues as bits 15- | 12)                 |              |  |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12) |                  |                  |                              |                  |                     |              |  |  |

|               |                                                                           |                  |                  |                              |                  |                     |              |  |  |

## REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

| R/W-0         | R/W-0                                                                                                    | R/W-0                            | R/W-0    | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------|----------|-------------------|------------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                  | EDG1SEL3                         | EDG1SEL2 | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                          |                                  |          |                   |                  |                 | bit 8    |  |  |  |  |

|               |                                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                    | R/W-0                            | R/W-0    | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                  | EDG2SEL3                         | EDG2SEL2 | EDG2SEL1          | EDG2SEL0         | _               |          |  |  |  |  |

| bit 7         |                                                                                                          |                                  |          |                   |                  |                 | bit 0    |  |  |  |  |

|               |                                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

| Legend:       |                                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

| R = Readable  | e bit                                                                                                    | W = Writable                     | bit      | U = Unimplen      | nented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                 |          | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

| bit 15        |                                                                                                          | Edge 1 Edge Sa                   |          | Selection bit     |                  |                 |          |  |  |  |  |

|               | •                                                                                                        | s edge-sensitive                 |          |                   |                  |                 |          |  |  |  |  |

| hit 11        | -                                                                                                        | s level-sensitive                |          |                   |                  |                 |          |  |  |  |  |

| bit 14        |                                                                                                          | dge 1 Polarity                   |          | dae response      |                  |                 |          |  |  |  |  |

|               | Ų                                                                                                        | s programmed f                   |          | <b>v</b> .        |                  |                 |          |  |  |  |  |

| bit 13-10     | -                                                                                                        | :0>: Edge 1 So                   | -        | •                 |                  |                 |          |  |  |  |  |

|               | 1111 = Fosc                                                                                              | •                                |          |                   |                  |                 |          |  |  |  |  |

|               | 1110 = OSCI pin                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1101 = FRC Oscillator                                                                                    |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1100 = BFRC Oscillator                                                                                   |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1011 = Internal LPRC Oscillator<br>1010 = Reserved                                                       |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1001 = Reser                                                                                             |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1000 <b>= Rese</b> r                                                                                     |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 0111 = Reser                                                                                             |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 0110 = Reser                                                                                             |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 0100 = Resei                                                                                             |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 0011 = CTED                                                                                              | 01 pin                           |          |                   |                  |                 |          |  |  |  |  |

|               | 0010 = CTED2 pin                                                                                         |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 0001 = OC1 module<br>0000 = TMR1 module                                                                  |                                  |          |                   |                  |                 |          |  |  |  |  |

| bit 9         |                                                                                                          | Edge 2 Status b                  | .i+      |                   |                  |                 |          |  |  |  |  |

| bit 9         |                                                                                                          | -                                |          | vritten to contro | of the edge sour | rce             |          |  |  |  |  |

|               | Indicates the status of Edge 2 and can be written to control the edge source.<br>1 = Edge 2 has occurred |                                  |          |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                          | as not occurred                  | ł        |                   |                  |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: E                                                                                              | Edge 1 Status b                  | it       |                   |                  |                 |          |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the edge source.                            |                                  |          |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 1 h                                                                                             |                                  | J        |                   |                  |                 |          |  |  |  |  |

| hit 7         | -                                                                                                        | as not occurred                  |          | Coloction hit     |                  |                 |          |  |  |  |  |

| bit 7         |                                                                                                          | Edge 2 Edge Sa<br>edge-sensitive |          | Selection Dit     |                  |                 |          |  |  |  |  |

|               | •                                                                                                        | level-sensitive                  |          |                   |                  |                 |          |  |  |  |  |

| bit 6         | -                                                                                                        | dge 2 Polarity                   |          |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                          | s programmed f                   |          | dge response      |                  |                 |          |  |  |  |  |

|               |                                                                                                          | programmed f                     |          |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                          |                                  |          |                   |                  |                 |          |  |  |  |  |

# REGISTER 23-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0                 | R/W-0                                                                                                             | R/W-0             | U-0                 | U-0              | R/W-0                | R/W-0               | R-0                 |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------------------|----------------------|---------------------|---------------------|--|--|

| CON                   | COE                                                                                                               | CPOL              | _                   |                  | OPAEN <sup>(2)</sup> | CEVT                | COUT                |  |  |

| bit 15                |                                                                                                                   |                   |                     |                  |                      |                     | bit 8               |  |  |

|                       |                                                                                                                   |                   |                     |                  |                      |                     |                     |  |  |

| R/W-0                 | R/W-0                                                                                                             | U-0               | R/W-0               | U-0              | U-0                  | R/W-0               | R/W-0               |  |  |

| EVPOL1 <sup>(3)</sup> | EVPOL0 <sup>(3)</sup>                                                                                             | —                 | CREF <sup>(1)</sup> |                  |                      | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |

| bit 7                 |                                                                                                                   |                   |                     |                  |                      |                     | bit C               |  |  |

| Legend:               |                                                                                                                   |                   |                     |                  |                      |                     |                     |  |  |

| R = Readable          | bit                                                                                                               | W = Writable      | bit                 | U = Unimpler     | mented bit, read     | <b>as</b> '0'       |                     |  |  |

| -n = Value at I       | POR                                                                                                               | '1' = Bit is set  |                     | '0' = Bit is cle | ared                 | x = Bit is unkr     | nown                |  |  |

|                       |                                                                                                                   |                   |                     |                  |                      |                     |                     |  |  |

| bit 15                | CON: Op Am                                                                                                        | p/Comparator      | x Enable bit        |                  |                      |                     |                     |  |  |

|                       |                                                                                                                   | Comparator x is   |                     |                  |                      |                     |                     |  |  |

|                       |                                                                                                                   | Comparator x is   |                     |                  |                      |                     |                     |  |  |

| bit 14                |                                                                                                                   | rator x Output    |                     |                  |                      |                     |                     |  |  |

|                       |                                                                                                                   | tor output is pre |                     | xout pin         |                      |                     |                     |  |  |

| bit 13                | <ul> <li>0 = Comparator output is internal only</li> <li>CPOL: Comparator x Output Polarity Select bit</li> </ul> |                   |                     |                  |                      |                     |                     |  |  |

|                       | 1 = Comparator output is inverted                                                                                 |                   |                     |                  |                      |                     |                     |  |  |

|                       | 0 = Comparat                                                                                                      | tor output is no  | t inverted          |                  |                      |                     |                     |  |  |

| bit 12-11             | Unimplemen                                                                                                        | ted: Read as '    | 0'                  |                  |                      |                     |                     |  |  |

| bit 10                | <b>OPAEN:</b> Op Amp x Enable bit <sup>(2)</sup>                                                                  |                   |                     |                  |                      |                     |                     |  |  |

|                       | 1 = Op Amp ><br>0 = Op Amp >                                                                                      |                   |                     |                  |                      |                     |                     |  |  |

| bit 9                 | CEVT: Compa                                                                                                       | arator x Event    | bit                 |                  |                      |                     |                     |  |  |

|                       | interrupts                                                                                                        | until the bit is  | cleared             | POL<1:0> sett    | ings, occurred;      | disables future     | e triggers and      |  |  |

|                       | •                                                                                                                 | tor event did n   |                     |                  |                      |                     |                     |  |  |

| bit 8                 |                                                                                                                   | arator x Outpu    |                     |                  |                      |                     |                     |  |  |

|                       | $\frac{\text{When CPOL} = 0 \text{ (non-inverted polarity):}}{1 = 1 \text{ (non-inverted polarity):}}$            |                   |                     |                  |                      |                     |                     |  |  |

|                       | 1 = VIN+ > VIN- $0 = VIN+ < VIN-$                                                                                 |                   |                     |                  |                      |                     |                     |  |  |

|                       | When CPOL                                                                                                         | = 1 (inverted p   | olarity):           |                  |                      |                     |                     |  |  |

|                       | 1 = VIN + < VII                                                                                                   |                   | <u> </u>            |                  |                      |                     |                     |  |  |

|                       | 0 = VIN + > VII                                                                                                   | -                 |                     |                  |                      |                     |                     |  |  |

### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5)

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- **3:** After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

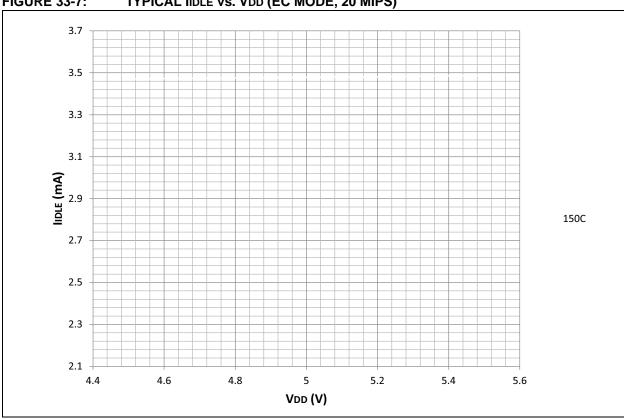

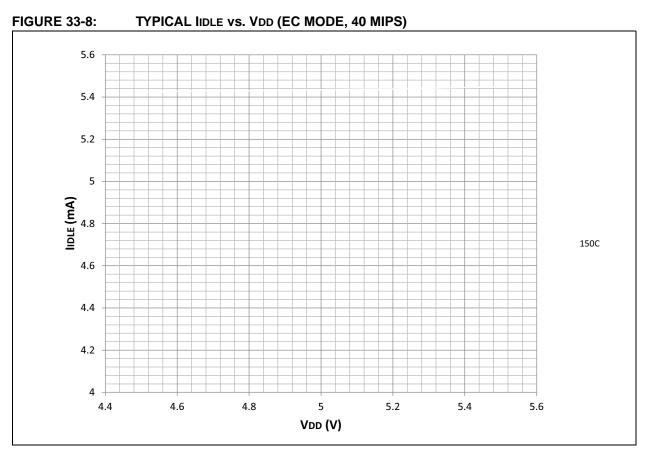

| DC CHARACT       | ERISTICS            |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |      |           |  |  |

|------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----------|--|--|

| Parameter<br>No. | Typ. <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                                                                                                                                                      |        |      |           |  |  |

| Idle Current (II | dle) <sup>(1)</sup> | •    | •                                                                                                                                                                                                                                                                                     | •      |      |           |  |  |

| DC40d            | 1.25                | 2    | mA                                                                                                                                                                                                                                                                                    | -40°C  |      |           |  |  |

| DC40a            | 1.25                | 2    | mA                                                                                                                                                                                                                                                                                    | +25°C  | 5.0V | 10 MIPS   |  |  |

| DC40b            | 1.5                 | 2.6  | mA                                                                                                                                                                                                                                                                                    | +85°C  | 5.00 |           |  |  |

| DC40c            | 1.5                 | 2.6  | mA                                                                                                                                                                                                                                                                                    | +125°C |      |           |  |  |

| DC42d            | 2.3                 | 3    | mA                                                                                                                                                                                                                                                                                    | -40°C  |      |           |  |  |

| DC42a            | 2.3                 | 3    | mA                                                                                                                                                                                                                                                                                    | +25°C  |      | 20 MIPS   |  |  |

| DC42b            | 2.6                 | 3.45 | mA                                                                                                                                                                                                                                                                                    | +85°C  | 5.0V | 20 1011-5 |  |  |

| DC42c            | 2.6                 | 3.85 | mA                                                                                                                                                                                                                                                                                    | +125°C | -    |           |  |  |

| DC44d            | 6.9                 | 8    | mA                                                                                                                                                                                                                                                                                    | -40°C  |      |           |  |  |

| DC44a            | 6.9                 | 8    | mA                                                                                                                                                                                                                                                                                    | +25°C  | 5.0V | 70 MIPS   |  |  |

| DC44b            | 7.25                | 8.6  | mA                                                                                                                                                                                                                                                                                    | +85°C  |      |           |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

# 30.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 4.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for ExtendedOperating voltage VDD range as described in Section 30.1 "DCCharacteristics". |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

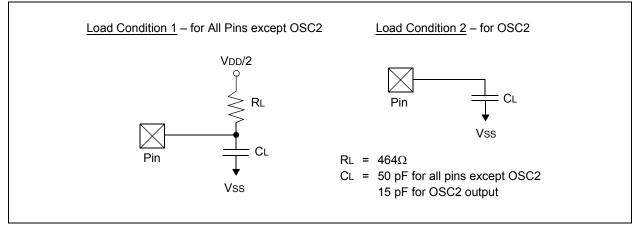

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              |      | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    |      | 400  | pF    | In I <sup>2</sup> C mode                                            |

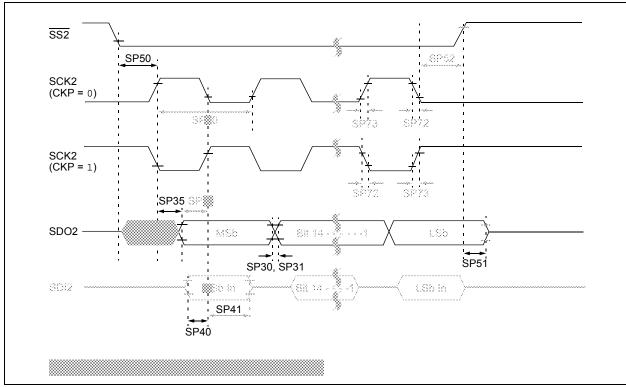

# TABLE 30-34:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА | ARACTERIS             | ΓΙCS                                            | Standard Op<br>(unless othe<br>Operating te | erwise st           | a <b>ted)</b><br>e -40° | C ≤ TA ≤ | <b>iV to 5.5V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------|-----------------------|-------------------------------------------------|---------------------------------------------|---------------------|-------------------------|----------|------------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                        | Typ. <sup>(2)</sup> | Max.                    | Units    | Conditions                                                       |

| SP70   | FscP                  | Maximum SCK2 Input Frequency                    | —                                           | —                   | 15                      | MHz      | See Note 3                                                       |

| SP72   | TscF                  | SCK2 Input Fall Time                            | —                                           | —                   | _                       | ns       | See Parameter DO32 and <b>Note 4</b>                             |

| SP73   | TscR                  | SCK2 Input Rise Time                            | —                                           | _                   | _                       | ns       | See Parameter DO31 and <b>Note 4</b>                             |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                      | —                                           | _                   | _                       | ns       | See Parameter DO32 and <b>Note 4</b>                             |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                      | —                                           | —                   | _                       | ns       | See Parameter DO31 and <b>Note 4</b>                             |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                           | 6                   | 20                      | ns       |                                                                  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                          | _                   | _                       | ns       |                                                                  |