Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·>>F

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

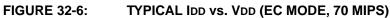

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

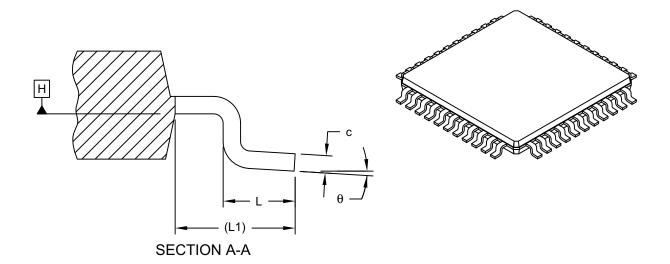

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm103-i-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

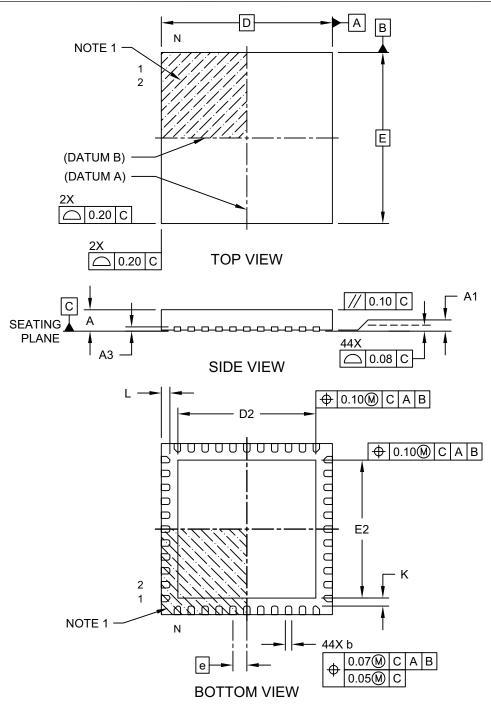

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

## FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

|             | ••    |        | •      |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

|-------------|-------|--------|--------|--------|--------|--------|--------|------------|-------------|---------------|---------------|-------------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7         | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |        |        |        |        |        |            | Tim         | ner1 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR1         | 0102  |        |        |        |        |        |        |            | Peri        | od Register   | 1             |             |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |        |        |        |        |        |        |            | Tim         | ner2 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108  |        |        |        |        |        | Time   | er3 Holdin | ig Register | · (For 32-bit | timer operat  | tions only) |        |       |       |       |       | 0000          |

| TMR3        | 010A  |        |        |        |        |        |        |            | Tim         | ner3 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR2         | 010C  |        |        |        |        |        |        |            | Peri        | od Register   | 2             |             |        |       |       |       |       | FFFF          |

| PR3         | 010E  |        |        |        |        |        |        |            | Peri        | od Register   | 3             |             |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON    | _      | TSIDL  | _      | _      | _      | _          | —           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |        |        |        |        |        |        |            | Tim         | ner4 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116  |        |        |        |        |        | Т      | imer5 Hol  | ding Regis  | ster (For 32- | bit operation | ns only)    |        |       |       |       |       | 0000          |

| TMR5        | 0118  |        |        |        |        |        |        |            | Tim         | ner5 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR4         | 011A  |        |        |        |        |        |        |            | Peri        | od Register   | 4             |             |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |        |        |        |        |        |            | Peri        | od Register   | 5             |             |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | _      | TSIDL  | —      | —      | —      | —          | —           | —             | TGATE         | TCKPS1      | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| Lonondi     |       |        | 1 1-   |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |  |

|------------------------------|---------------|----------|--------------------|--|

| External Interrupt 1         | INT1          | RPINR0   | INT1R<7:0>         |  |

| External Interrupt 2         | INT2          | RPINR1   | INT2R<7:0>         |  |

| Timer2 External Clock        | T2CK          | RPINR3   | T2CKR<7:0>         |  |

| Input Capture 1              | IC1           | RPINR7   | IC1R<7:0>          |  |

| Input Capture 2              | IC2           | RPINR7   | IC2R<7:0>          |  |

| Input Capture 3              | IC3           | RPINR8   | IC3R<7:0>          |  |

| Input Capture 4              | IC4           | RPINR8   | IC4R<7:0>          |  |

| Output Compare Fault A       | OCFA          | RPINR11  | OCFAR<7:0>         |  |

| PWM Fault 1                  | FLT1          | RPINR12  | FLT1R<7:0>         |  |

| PWM Fault 2                  | FLT2          | RPINR12  | FLT2R<7:0>         |  |

| UART1 Receive                | U1RX          | RPINR18  | U1RXR<7:0>         |  |

| UART2 Receive                | U2RX          | RPINR19  | U2RXR<7:0>         |  |

| SPI2 Data Input              | SDI2          | RPINR22  | SDI2R<7:0>         |  |

| SPI2 Clock Input             | SCK2          | RPINR22  | SCK2R<7:0>         |  |

| SPI2 Slave Select            | SS2           | RPINR23  | SS2R<7:0>          |  |

| CAN1 Receive                 | C1RX          | RPINR26  | C1RXR<7:0>         |  |

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |  |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<7:0>       |  |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<7:0>       |  |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<7:0>       |  |

| SENT1 Input                  | SENT1R        | RPINR44  | SENT1R<7:0>        |  |

| SENT2 Input                  | SENT2R        | RPINR45  | SENT2R<7:0>        |  |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

## 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

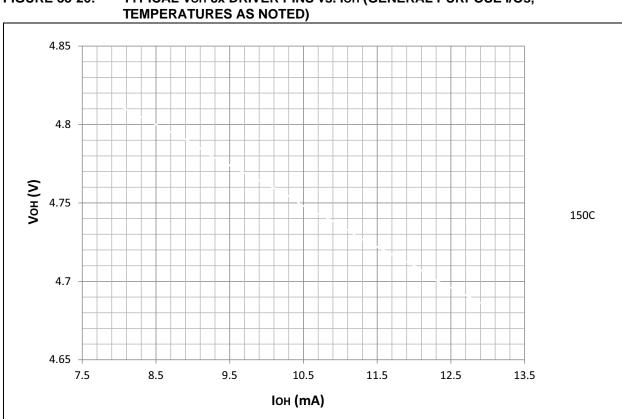

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

|              | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|--------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------|-------------------|------------------|--------------------|-------|--|

| IC2R7        | IC2R6                                                             | IC2R5                                                                                   | IC2R4                                        | IC2R3             | IC2R2            | IC2R1              | IC2R0 |  |

| oit 15       |                                                                   |                                                                                         |                                              |                   |                  |                    | bit 8 |  |

| R/W-0        | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

| IC1R7        | IC1R6                                                             | IC1R5                                                                                   | IC1R4                                        | IC1R3             | IC1R2            | IC1R1              | IC1R0 |  |

| it 7         |                                                                   |                                                                                         |                                              | -                 |                  |                    | bit 0 |  |

| .egend:      |                                                                   |                                                                                         |                                              |                   |                  |                    |       |  |

| R = Readable | e bit                                                             | W = Writable                                                                            | bit                                          | U = Unimpler      | nented bit, read | <b>d as</b> '0'    |       |  |

| n = Value at | POR                                                               | '1' = Bit is set                                                                        |                                              | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

|              | 10110101 -                                                        |                                                                                         |                                              |                   |                  |                    |       |  |

|              | •<br>•                                                            | <ul> <li>Input tied to RI</li> <li>Input tied to CI</li> </ul>                          |                                              |                   |                  |                    |       |  |

|              | •<br>•<br>000000001 =<br>00000000 =                               | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS                                    |                   |                  |                    |       |  |

| bit 7-0      | •<br>•<br>00000001 =<br>00000000 =<br>IC1R<7:0>:                  | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> <li>Assign Input Ca</li> </ul> | MP1<br>SS<br>apture 1 (IC1)                  |                   | onding RPn Pir   | n bits             |       |  |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

| vit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits             |       |  |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

#### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| bit 15 |     |     |     |     |     |     | bit 8 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| OCFAR<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 OCFAR<7:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

> 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

| R/W-0         | U-0                  | R/W-0                                                                                                                                  | U-0                       | R/W-0            | R/W-0                               | R/W-0                | R/W-0   |  |  |  |  |

|---------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|-------------------------------------|----------------------|---------|--|--|--|--|

| SNTEN         | —                    | SNTSIDL                                                                                                                                | —                         | RCVEN            | TXM <sup>(1)</sup>                  | TXPOL <sup>(1)</sup> | CRCEN   |  |  |  |  |

| bit 15        |                      |                                                                                                                                        |                           |                  |                                     |                      | bit     |  |  |  |  |

| R/W-0         | R/W-0                | U-0                                                                                                                                    | R/W-0                     | U-0              | R/W-0                               | R/W-0                | R/W-0   |  |  |  |  |

| PPP           | SPCEN <sup>(2)</sup> |                                                                                                                                        | PS                        | _                | NIBCNT2                             | NIBCNT1              | NIBCNT0 |  |  |  |  |

| bit 7         |                      |                                                                                                                                        |                           |                  |                                     |                      | bit     |  |  |  |  |

| Legend:       |                      |                                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

| R = Readable  | e bit                | W = Writable                                                                                                                           | bit                       | U = Unimple      | mented bit, read                    | <b>d as</b> '0'      |         |  |  |  |  |

| -n = Value at | POR                  | '1' = Bit is set                                                                                                                       |                           | '0' = Bit is cle | eared                               | x = Bit is unkr      | nown    |  |  |  |  |

|               |                      |                                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

| bit 15        | SNTEN: SEM           | NTx Enable bit                                                                                                                         |                           |                  |                                     |                      |         |  |  |  |  |

|               | 1 = SENTx is         |                                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

|               | 0 = SENTx is         |                                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

| bit 14        | -                    | nted: Read as                                                                                                                          |                           |                  |                                     |                      |         |  |  |  |  |

| bit 13        |                      | ENTx Stop in lo                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

|               |                      | nues module op<br>es module opera                                                                                                      |                           |                  | ers Idle mode                       |                      |         |  |  |  |  |

| bit 12        | Unimplemer           | nted: Read as                                                                                                                          | ʻ0'                       |                  |                                     |                      |         |  |  |  |  |

| bit 11        | RCVEN: SEI           | NTx Receive E                                                                                                                          | nable bit                 |                  |                                     |                      |         |  |  |  |  |

|               |                      | perates as a re                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

|               |                      | perates as a tr                                                                                                                        |                           | nsor)            |                                     |                      |         |  |  |  |  |

| bit 10        |                      | <b>TXM:</b> SENTx Transmit Mode bit <sup>(1)</sup><br>1 = SENTx transmits data frame only when triggered using the SYNCTXEN status bit |                           |                  |                                     |                      |         |  |  |  |  |

|               |                      | ransmits data fi<br>ransmits data fi                                                                                                   |                           |                  |                                     | KEN status bit       |         |  |  |  |  |

| bit 9         |                      | NTx Transmit P                                                                                                                         |                           |                  |                                     |                      |         |  |  |  |  |

| bit 5         |                      | lata output pin i                                                                                                                      | -                         | lle state        |                                     |                      |         |  |  |  |  |

|               |                      | lata output pin i                                                                                                                      |                           |                  |                                     |                      |         |  |  |  |  |

| bit 8         | CRCEN: CR            | C Enable bit                                                                                                                           |                           |                  |                                     |                      |         |  |  |  |  |

|               | 1 = SENTx p          |                                                                                                                                        | verification on           |                  | using the prefer                    | red J2716 meth       | od      |  |  |  |  |

|               |                      | loes not perforr<br>ansmit Mode (F                                                                                                     |                           | ation on receiv  |                                     |                      |         |  |  |  |  |

|               |                      |                                                                                                                                        |                           | using the pref   | erred J2716 me                      | thod                 |         |  |  |  |  |

|               |                      | loes not calcula                                                                                                                       |                           | 0 1              |                                     |                      |         |  |  |  |  |

| bit 7         | PPP: Pause           | Pulse Present                                                                                                                          | bit                       |                  |                                     |                      |         |  |  |  |  |

|               |                      |                                                                                                                                        |                           |                  | sages with paus<br>sages without pa |                      |         |  |  |  |  |

| bit 6         | SPCEN: Sho           | ort PWM Code                                                                                                                           | Enable bit <sup>(2)</sup> |                  |                                     |                      |         |  |  |  |  |

|               |                      | trol from exterr<br>trol from exterr                                                                                                   |                           |                  |                                     |                      |         |  |  |  |  |

| bit 5         | Unimplemer           | nted: Read as                                                                                                                          | ʻ0'                       |                  |                                     |                      |         |  |  |  |  |

| bit 4         | PS: SENTX I          | Module Clock F                                                                                                                         | Prescaler (divi           | der) bits        |                                     |                      |         |  |  |  |  |

|               | 1 = Divide-by        |                                                                                                                                        |                           |                  |                                     |                      |         |  |  |  |  |

|               | 0 = Divide-by        | /-1                                                                                                                                    |                           |                  |                                     |                      |         |  |  |  |  |

| Note 1: Th    | iis bit has no fur   | nction in Receiv                                                                                                                       | ve mode (RC\              | /EN = 1).        |                                     |                      |         |  |  |  |  |

| <b>2</b> • Th | us bit has no fur    | nction in Transr                                                                                                                       | nit mode (RC)             | VEN = 0          |                                     |                      |         |  |  |  |  |

#### REGISTER 20-1: SENTxCON1: SENTx CONTROL REGISTER 1

2: This bit has no function in Transmit mode (RCVEN = 0).

NOTES:

## REGISTER 22-22: CxRXFUL1: CANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0           | R/C-0                                                                     | R/C-0          | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|-----------------|---------------------------------------------------------------------------|----------------|------------------|-------------------|-----------------|-----------------|-------|

|                 |                                                                           |                | RXFU             | L<15:8>           |                 |                 |       |

| bit 15          |                                                                           |                |                  |                   |                 |                 | bit 8 |

|                 |                                                                           |                |                  |                   |                 |                 |       |

| R/C-0           | R/C-0                                                                     | R/C-0          | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|                 |                                                                           |                | RXFL             | JL<7:0>           |                 |                 |       |

| bit 7           |                                                                           |                |                  |                   |                 |                 | bit 0 |

|                 |                                                                           |                |                  |                   |                 |                 |       |

| Legend:         |                                                                           | C = Writable b | oit, but only '( | )' can be written | to clear the b  | it              |       |

| R = Readable    | bit                                                                       | W = Writable   | bit              | U = Unimplem      | nented bit, rea | <b>d as</b> '0' |       |

| -n = Value at F | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |                  |                   |                 |                 | nown  |

bit 15-0 RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 22-23: CxRXFUL2: CANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                                                                      | R/C-0 | R/C-0          | R/C-0           | R/C-0             | R/C-0           | R/C-0     | R/C-0 |

|----------------------------------------------------------------------------|-------|----------------|-----------------|-------------------|-----------------|-----------|-------|

|                                                                            |       |                | RXFU            | _<31:24>          |                 |           |       |

| bit 15                                                                     |       |                |                 |                   |                 |           | bit 8 |

|                                                                            |       |                |                 |                   |                 |           |       |

| R/C-0                                                                      | R/C-0 | R/C-0          | R/C-0           | R/C-0             | R/C-0           | R/C-0     | R/C-0 |

|                                                                            |       |                | RXFU            | _<23:16>          |                 |           |       |

| bit 7                                                                      |       |                |                 |                   |                 |           | bit 0 |

|                                                                            |       |                |                 |                   |                 |           |       |

| Legend:                                                                    |       | C = Writable b | it, but only '( | )' can be written | to clear the b  | bit       |       |

| R = Readable                                                               | bit   | W = Writable b | bit             | U = Unimplen      | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |                 |                   |                 | nown      |       |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| EVPOL1 <sup>(2)</sup> EV           bit 7         Event           Legend:         R = Readable bit           -n = Value at POR         1           bit 15         CO           bit 15         CO           bit 15         CO           bit 14         CO           bit 13         CP           bit 13         CP           bit 14         CO           1 =         0 =           bit 13         CP           bit 14         CO           1 =         0 =           bit 13         CP           1 =         0 =           bit 13         CP           0 =         0 =           bit 12-10         Uni           bit 9         CE                                                       | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             |                                                                                                                                 | 4 Enable bit<br>Enable bit<br>esent on the C                                                                          | '0' = Bit is cle                 | U-0<br>—<br>nented bit, rea<br>ared | R/W-0<br>CCH1 <sup>(1)</sup><br>d as '0'<br>x = Bit is unkn | COUT<br>bit (<br>R/W-0<br>CCH0 <sup>(1)</sup><br>bit ( |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| R/W-0         EVPOL1 <sup>(2)</sup> EV         bit 7         Legend:         R = Readable bit         -n = Value at POR         bit 15       CO         bit 15       CO         bit 14       CO         bit 13       CP0         bit 13       CP0         bit 12-10       Uni         bit 19       CEV                                                                                                                                                                                                                                                                                                                                                                               | /POL0 <sup>(2)</sup> N: Op Am Comparat Comparat Comparat Comparat Comparat                                                           | W = Writable<br>'1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre- | CREF <sup>(1)</sup><br>bit<br>4 Enable bit<br>Enable bit<br>esent on the C                                            | U = Unimpler<br>'0' = Bit is cle |                                     | CCH1 <sup>(1)</sup>                                         | R/W-0<br>CCH0 <sup>(1)</sup><br>bit (                  |  |  |  |

| EVPOL1 <sup>(2)</sup> EV           bit 7         Event           Legend:         R = Readable bit           -n = Value at POR         1           bit 15         CO           bit 14         CO           1 =         0 =           bit 13         CP           1 =         0 =           bit 13         CP           1 =         0 =           bit 12-10         Uni           bit 9         CE                                                                                                             | /POL0 <sup>(2)</sup> N: Op Am Comparat Comparat Comparat Comparat Comparat                                                           | W = Writable<br>'1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre- | CREF <sup>(1)</sup><br>bit<br>4 Enable bit<br>Enable bit<br>esent on the C                                            | U = Unimpler<br>'0' = Bit is cle |                                     | CCH1 <sup>(1)</sup>                                         | CCH0 <sup>(1)</sup><br>bit (                           |  |  |  |

| bit 7<br>Legend:<br>R = Readable bit<br>-n = Value at POR<br>bit 15 CO<br>1 =<br>0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CP(<br>1 =<br>0 =<br>bit 15 CO<br>1 =<br>0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CP(<br>1 =<br>0 =<br>0 =<br>bit 13 CP(<br>1 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 | N: Op Am<br>Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                 | '1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                  | bit<br>4 Enable bit<br>Enable bit<br>esent on the C                                                                   | '0' = Bit is cle                 |                                     | d as '0'                                                    | bit (                                                  |  |  |  |

| 1 =<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | '1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                  | 4 Enable bit<br>Enable bit<br>esent on the C                                                                          | '0' = Bit is cle                 |                                     |                                                             |                                                        |  |  |  |

| R = Readable bit<br>-n = Value at POR<br>bit 15 CO<br>1 =<br>0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0                                                                                                                                                                                                                                                                                                                                                                                                                    | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | '1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                  | 4 Enable bit<br>Enable bit<br>esent on the C                                                                          | '0' = Bit is cle                 |                                     |                                                             | iown                                                   |  |  |  |

| R = Readable bit<br>-n = Value at POR<br>bit 15 CO<br>1 =<br>0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>bit 13 CPO<br>1 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0 =<br>0                                                                                                                                                                                                                                                                                                                                                                                                                           | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | '1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                  | 4 Enable bit<br>Enable bit<br>esent on the C                                                                          | '0' = Bit is cle                 |                                     |                                                             | iown                                                   |  |  |  |

| bit 15 CO<br>1 =<br>0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CP4<br>1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | '1' = Bit is set<br>p/Comparator 4<br>tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                  | 4 Enable bit<br>Enable bit<br>esent on the C                                                                          | '0' = Bit is cle                 |                                     |                                                             | iown                                                   |  |  |  |

| 1 =<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                                                        | Enable bit<br>esent on the C                                                                                          | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| 1 =<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparat<br>Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                             | tor is enabled<br>tor is disabled<br>rator 4 Output<br>tor output is pre                                                        | Enable bit<br>esent on the C                                                                                          | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| 0 =<br>bit 14 CO<br>1 =<br>0 =<br>bit 13 CP4<br>1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparat<br>E: Compa<br>Comparat<br>Comparat                                                                                         | tor is disabled<br>rator 4 Output<br>tor output is pre                                                                          | esent on the C                                                                                                        | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| bit 14 CO<br>1 =<br>0 =<br>bit 13 CP<br>1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E: Compa<br>Comparat<br>Comparat                                                                                                     | rator 4 Output<br>tor output is pre                                                                                             | esent on the C                                                                                                        | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| 1 =<br>0 =<br>bit 13 CP0<br>1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Comparat<br>Comparat                                                                                                                 | tor output is pre                                                                                                               | esent on the C                                                                                                        | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| 0 =<br>bit 13 CP<br>1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Comparat                                                                                                                             |                                                                                                                                 |                                                                                                                       | C4OUT pin                        |                                     |                                                             |                                                        |  |  |  |

| 1 =<br>0 =<br>bit 12-10 Uni<br>bit 9 CEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OL: Comp                                                                                                                             |                                                                                                                                 | <ul> <li>1 = Comparator output is present on the C4OUT pin</li> <li>0 = Comparator output is internal only</li> </ul> |                                  |                                     |                                                             |                                                        |  |  |  |

| 0 =<br>bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CPOL: Comparator 4 Output Polarity Select bit                                                                                        |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| bit 12-10 Uni<br>bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 = Comparator output is inverted                                                                                                    |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| bit 9 CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      | tor output is no                                                                                                                |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Unimplemented: Read as '0'                                                                                                           |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>CEVT:</b> Comparator 4 Event bit<br>1 = Comparator event, according to EVPOL<1:0> settings, occurred; disables future triggers an |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | interrupts                                                                                                                           | tor event, acc<br>s until the bit is<br>tor event did n                                                                         | cleared                                                                                                               | POL<1:0> sett                    | ings, occurred                      | ; disables future                                           | e triggers an                                          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                      |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>COUT:</b> Comparator 4 Output bit<br>When CPOL = 0 (non-inverted polarity):                                                       |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{\text{Vnen CPOL} = 0}{1 = \text{Vin} + \text{Vin}}$                                                                           |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $0 = V_{IN+} < V_{IN-}$                                                                                                              |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| Wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | When CPOL = 1 (inverted polarity):                                                                                                   |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 = VIN + < VIN-                                                                                                                     |                                                                                                                                 |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

| 0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VIN+ > VII                                                                                                                           | N-                                                                                                                              |                                                                                                                       |                                  |                                     |                                                             |                                                        |  |  |  |

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

# dsPIC33EVXXXGM00X/10X FAMILY

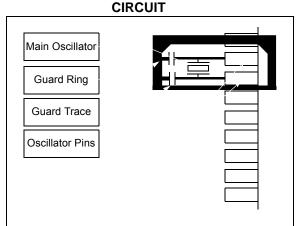

#### FIGURE 26-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# TABLE 30-34:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                      |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------|--|