Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

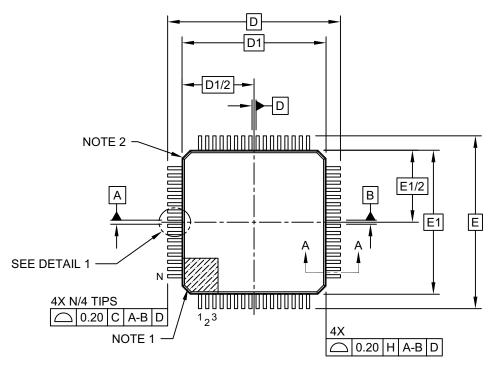

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm104-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

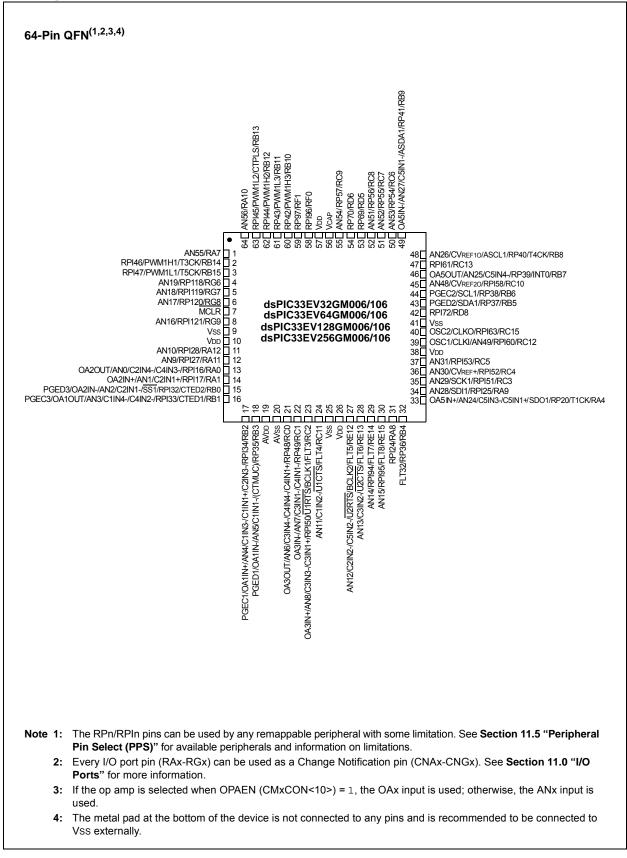

### Pin Diagrams (Continued)

| TABLE 1-1: PINO                   |             | D DESC         | RIPTI   | ONS (CONTINUED)                                                            |  |  |  |  |

|-----------------------------------|-------------|----------------|---------|----------------------------------------------------------------------------|--|--|--|--|

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                |  |  |  |  |

| SCK2                              | I/O         | ST             | Yes     | Synchronous serial clock input/output for SPI2.                            |  |  |  |  |

| SDI2                              | I           | ST             | Yes     | SPI2 data in.                                                              |  |  |  |  |

| SDO2                              | 0           | —              | Yes     | SPI2 data out.                                                             |  |  |  |  |

| SS2                               | I/O         | ST             | Yes     | SPI2 slave synchronization or frame pulse I/O.                             |  |  |  |  |

| SCL1                              | I/O         | ST             | No      | Synchronous serial clock input/output for I2C1.                            |  |  |  |  |

| SDA1                              | I/O         | ST             | No      | Synchronous serial data input/output for I2C1.                             |  |  |  |  |

| ASCL1                             | I/O         | ST             | No      | Alternate synchronous serial clock input/output for I2C1.                  |  |  |  |  |

| ASDA1                             | I/O         | ST             | No      | Alternate synchronous serial data input/output for I2C1.                   |  |  |  |  |

| C1RX                              | I           | ST             | Yes     | CAN1 bus receive pin.                                                      |  |  |  |  |

| C1TX                              | 0           | —              | Yes     | CAN1 bus transmit pin.                                                     |  |  |  |  |

| SENT1TX                           | 0           | —              | Yes     | SENT1 transmit pin.                                                        |  |  |  |  |

| SENT1RX                           | 1           | —              | Yes     | SENT1 receive pin.                                                         |  |  |  |  |

| SENT2TX                           | 0           | —              | Yes     | SENT2 transmit pin.                                                        |  |  |  |  |

| SENT2RX                           | I.          | —              | Yes     | SENT2 receive pin.                                                         |  |  |  |  |

| CVREF                             | 0           | Analog         | No      | Comparator Voltage Reference output.                                       |  |  |  |  |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | No      | Comparator 1 inputs.                                                       |  |  |  |  |

| C1OUT                             | 0           | _              | Yes     | Comparator 1 output.                                                       |  |  |  |  |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3- | I           | Analog         | No      | Comparator 2 inputs.                                                       |  |  |  |  |

| C2OUT                             | 0           | —              | Yes     | Comparator 2 output.                                                       |  |  |  |  |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3- | I           | Analog         | No      | Comparator 3 inputs.                                                       |  |  |  |  |

| C3OUT                             | 0           |                | Yes     | Comparator 3 output.                                                       |  |  |  |  |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3- | Ι           | Analog         | No      | Comparator 4 inputs.                                                       |  |  |  |  |

| C4OUT                             | 0           | —              | Yes     | Comparator 4 output.                                                       |  |  |  |  |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3- | I           | Analog         | No      | Comparator 5 inputs.                                                       |  |  |  |  |

| C5OUT                             | 0           | —              | Yes     | Comparator 5 output.                                                       |  |  |  |  |

| FLT1-FLT2                         | 1           | ST             | Yes     | PWM Fault Inputs 1 and 2.                                                  |  |  |  |  |

| FLT3-FLT8                         | 1           | ST             | NO      | PWM Fault Inputs 3 to 8.                                                   |  |  |  |  |

| FLT32                             | 1           | ST             | NO      |                                                                            |  |  |  |  |

| DTCMP1-DTCMP3                     | 1           | ST             | Yes     | PWM Dead-Time Compensation Inputs 1 to 3.                                  |  |  |  |  |

| PWM1L-PWM3L                       | 0           | _              | No      | PWM Low Outputs 1 to 3.                                                    |  |  |  |  |

| PWM1H-PWM3H                       | 0           | —              | No      | PWM High Outputs 1 to 3.                                                   |  |  |  |  |

| SYNCI1                            | 1           | ST             | Yes     |                                                                            |  |  |  |  |

| SYNCO1                            | 0           | —              | Yes     | PWM Synchronization Output 1.                                              |  |  |  |  |

| PGED1                             | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.            |  |  |  |  |

| PGEC1                             | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1          |  |  |  |  |

| PGED2                             | I/O         | ST             | No      |                                                                            |  |  |  |  |

| PGEC2                             | 1           | ST             | No      |                                                                            |  |  |  |  |

| PGED3                             | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.            |  |  |  |  |

| PGEC3                             | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel            |  |  |  |  |

| MCLR                              | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |  |  |  |

| Legend: CMOS = C                  |             |                |         | or output Analog = Analog input P = Power                                  |  |  |  |  |

| ST = Schm                         | itt Triaa   | er input w     | /ith CN | IOS levels O = Output I = Input                                            |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | / |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EVXXXGM00X/10X CPU. The Interrupt Vector Table (IVT) provides 246 interrupt sources (unused sources are reserved for future use) that can be programmed with different priority levels.

The interrupt controller has the following features:

- · Interrupt Vector Table with up to 246 Vectors

- Alternate Interrupt Vector Table (AIVT)

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- · Fixed Interrupt Entry and Return Latencies

- Software can Generate any Peripheral Interrupt

- Alternate Interrupt Vector Table (AIVT) is available if Boot Security is Enabled and AIVTEN = 1

## 7.1 Interrupt Vector Table

The dsPIC33EVXXXGM00X/10X family IVT, shown in Figure 7-2, resides in program memory, starting at location, 00004h. The IVT contains seven nonmaskable trap vectors and up to 187 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Alternate Interrupt Vector Table

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-1, is available if the Boot Segment (BS) is defined, the AIVTEN bit is set in the INTCON2 register and if the AIVTDIS Configuration bit is set to '1'. The AIVT begins at the start of the last page of the Boot Segment.

### REGISTER 8-5: DMAxSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0      | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|--------|-------|-------|-------|

| —        | —     | —     | —     | —      | —     | —     | —     |

| bit 15   |       |       |       |        | •     |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | STB<2 | 23:16> |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

|          |       |       |       |        |       |       |       |

| l egend. |       |       |       |        |       |       |       |

| Legenu.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

## REGISTER 8-6: DMAxSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                 | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|---------------------------------------|-------|-------|-------|

|                 |       |                  | STB   | <15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                       |       |       | bit 8 |

|                 |       |                  |       |                                       |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                 | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | STE   | 3<7:0>                                |       |       |       |

| bit 7           | 7     |                  |       |                                       |       |       | bit 0 |

|                 |       |                  |       |                                       |       |       |       |

| Legend:         |       |                  |       |                                       |       |       |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'    |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unkno |       | nown  |       |

bit 15-0 STB<15:0>: DMA Secondary Start Address bits (source or destination)

| R/W-0                                                                                                                   | U-0                                                                          | R/W-0                                   | R/W-0           | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|-----------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| ROON                                                                                                                    |                                                                              | ROSSLP                                  | ROSEL           | RODIV3 <sup>(1)</sup>              | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |  |

| bit 15                                                                                                                  |                                                                              |                                         |                 |                                    |                       |                       | bit 8                 |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

| U-0                                                                                                                     | U-0                                                                          | U-0                                     | U-0             | U-0                                | U-0                   | U-0                   | U-0                   |  |  |  |  |

|                                                                                                                         |                                                                              | _                                       | —               | —                                  | —                     | —                     | —                     |  |  |  |  |

| bit 7                                                                                                                   |                                                                              |                                         |                 |                                    |                       |                       | bit                   |  |  |  |  |

| Legend:                                                                                                                 |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

| R = Readab                                                                                                              | le bit                                                                       | W = Writable                            | bit             | U = Unimpler                       | mented bit, read      | l as '0'              |                       |  |  |  |  |

| -n = Value a                                                                                                            | t POR                                                                        | '1' = Bit is set                        |                 | '0' = Bit is cle                   | ared                  | x = Bit is unkr       | iown                  |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

| bit 15                                                                                                                  |                                                                              | rence Oscillato                         | •               |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 | on the REFCL                       | -K pin <sup>(2)</sup> |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | e oscillator out                        | 1               | 1                                  |                       |                       |                       |  |  |  |  |

| bit 14                                                                                                                  | -                                                                            | ted: Read as '                          |                 |                                    |                       |                       |                       |  |  |  |  |

| bit 13                                                                                                                  |                                                                              | eference Oscilla                        |                 | •                                  |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 | to run in Sleep<br>d in Sleep mode |                       |                       |                       |  |  |  |  |

| bit 12                                                                                                                  |                                                                              | erence Oscillato                        |                 | •                                  |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 1 = Oscillator                                                               | crystal is used                         | as the refere   | nce clock                          |                       |                       |                       |  |  |  |  |

|                                                                                                                         | -                                                                            | lock is used as                         |                 |                                    |                       |                       |                       |  |  |  |  |

| bit 11-8                                                                                                                | RODIV<3:0>                                                                   | : Reference Os                          | cillator Divide | er bits <sup>(1)</sup>             |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | rence clock divi                        |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | rence clock divi<br>rence clock divi    |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | rence clock divi                        | -               |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 1011 <b>= Refe</b> r                                                         | 1011 = Reference clock divided by 2,048 |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | 1010 = Reference clock divided by 1,024 |                 |                                    |                       |                       |                       |  |  |  |  |

| 1001 = Reference clock divided by 512<br>1000 = Reference clock divided by 256<br>0111 = Reference clock divided by 128 |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 0110 = Reference clock divided by 64                                         |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 0101 = Reference clock divided by 32<br>0100 = Reference clock divided by 16 |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | rence clock divi                        |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              | rence clock divi                        | •               |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 0001 = Refer                                                                 |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         |                                                                              |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

|                                                                                                                         | 0000 = Refer                                                                 |                                         |                 |                                    |                       |                       |                       |  |  |  |  |

### **REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.5 "Peripheral Pin Select (PPS)" for more information.

### 11.5.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one, and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

| Function     | RPnR<5:0> | Output Name                                   |

|--------------|-----------|-----------------------------------------------|

| Default Port | 000000    | RPn tied to Default Pin                       |

| U1TX         | 000001    | RPn tied to UART1 Transmit                    |

| U2TX         | 000011    | RPn tied to UART2 Transmit                    |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX         | 001110    | RPn tied to CAN1 Transmit                     |

| OC1          | 010000    | RPn tied to Output Compare 1 Output           |

| OC2          | 010001    | RPn tied to Output Compare 2 Output           |

| OC3          | 010010    | RPn tied to Output Compare 3 Output           |

| OC4          | 010011    | RPn tied to Output Compare 4 Output           |

| C10UT        | 011000    | RPn tied to Comparator Output 1               |

| C2OUT        | 011001    | RPn tied to Comparator Output 2               |

| C3OUT        | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1       | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output            |

| C4OUT        | 110010    | RPn tied to Comparator Output 4               |

| C5OUT        | 110011    | RPn tied to Comparator Output 5               |

| SENT1        | 111001    | RPn tied to SENT Out 1                        |

| SENT2        | 111010    | RPn tied to SENT Out 2                        |

|--|

#### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| bit 15 |     |     |     |     |     |     | bit 8 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| OCFAR<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 OCFAR<7:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

> 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

| R/W-1           | R/W-1            | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

|-----------------|------------------|-----------------------------------------------------------------------------------|--------------------------|----------------------|------------------------------|-----------------|--------|

| PENH            | PENL             | POLH                                                                              | POLL                     | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>         | OVRENH          | OVRENL |

| bit 15          |                  |                                                                                   |                          |                      |                              |                 | bit 8  |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| R/W-0           | R/W-0            | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

| OVRDAT1         | OVRDAT0          | FLTDAT1                                                                           | FLTDAT0                  | CLDAT1               | CLDAT0                       | SWAP            | OSYNC  |

| bit 7           |                  |                                                                                   |                          |                      |                              |                 | bit 0  |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| Legend:         |                  |                                                                                   |                          |                      |                              |                 |        |

| R = Readable    | bit              | W = Writable                                                                      | bit                      | U = Unimplei         | mented bit, read             | <b>as</b> '0'   |        |

| -n = Value at F | POR              | '1' = Bit is set                                                                  |                          | '0' = Bit is cle     | eared                        | x = Bit is unkr | nown   |

|                 |                  |                                                                                   |                          |                      |                              |                 |        |

| bit 15          | PENH: PWM        | xH Output Pin                                                                     | Ownership bit            |                      |                              |                 |        |

|                 |                  | odule controls                                                                    |                          |                      |                              |                 |        |

|                 |                  | dule controls th                                                                  | •                        | ו                    |                              |                 |        |

| bit 14          |                  | L Output Pin                                                                      | •                        |                      |                              |                 |        |

|                 |                  | odule controls<br>dule controls th                                                |                          |                      |                              |                 |        |

| bit 13          |                  | xH Output Pin                                                                     | •                        | I                    |                              |                 |        |

| DIL 13          |                  | bin is active-low                                                                 | •                        |                      |                              |                 |        |

|                 |                  | pin is active-hig                                                                 |                          |                      |                              |                 |        |

| bit 12          |                  | <l f<="" output="" pin="" td=""><td></td><td></td><td></td><td></td><td></td></l> |                          |                      |                              |                 |        |

|                 |                  | in is active-low                                                                  |                          |                      |                              |                 |        |

|                 | 0 = PWMxL p      | in is active-hig                                                                  | h                        |                      |                              |                 |        |

| bit 11-10       | PMOD<1:0>:       | PWMx I/O Pin                                                                      | Mode bits <sup>(1)</sup> |                      |                              |                 |        |

|                 | 11 = Reserve     |                                                                                   |                          |                      |                              |                 |        |

|                 |                  | /O pin pair is ir<br>/O pin pair is ir                                            |                          |                      |                              |                 |        |

|                 |                  | O pin pair is in<br>O pin pair is ir                                              |                          | •                    |                              |                 |        |

| bit 9           |                  | verride Enable                                                                    | •                        |                      |                              |                 |        |

|                 | 1 = OVRDAT       | 1 controls the o                                                                  | output on the I          | PWMxH pin            |                              |                 |        |

|                 |                  | enerator contro                                                                   |                          |                      |                              |                 |        |

| bit 8           | OVRENL: Ov       | erride Enable                                                                     | for PWMxL Pi             | n bit                |                              |                 |        |

|                 |                  | 0 controls the o                                                                  | •                        |                      |                              |                 |        |

|                 | •                | nerator contro                                                                    |                          | •                    |                              |                 |        |

| bit 7-6         |                  |                                                                                   |                          |                      | ide is Enabled b             | its             |        |

|                 |                  | •                                                                                 |                          |                      | d by OVRDAT1.<br>by OVRDAT0. |                 |        |

| bit 5-4         |                  |                                                                                   |                          | •                    | TMOD is Enable               | d hits          |        |

|                 |                  | ve, PWMxH is                                                                      |                          |                      |                              |                 |        |

|                 |                  | ve, PWMxL is                                                                      |                          |                      |                              |                 |        |

| bit 3-2         |                  |                                                                                   |                          | •                    | /IOD is Enabled              | bits            |        |

|                 | If current limit | is active, PW                                                                     | MxH is driven            | to the state sp      | ecified by CLDA              | T1.             |        |

|                 | If current limit | is active, PWI                                                                    | MxL is driven t          | o the state spe      | ecified by CLDA              | ГО.             |        |

| Note 1: The     | ese bits should  | not be change                                                                     | d after the PW           | /Mx module is        | enabled (PTEN                | = 1).           |        |

|                 |                  |                                                                                   |                          |                      | · -··                        | ,               |        |

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

**Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1). **2:** If the PWMI OCK Configuration bit (EDEVOPT<0>) is a '1' the IOCONy register can only be

2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1

SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to the PWMxL pin; PWMxL output signal is connected to the PWMxH pin

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0

OSYNC: Output Override Synchronization bit

1 = Output overrides through the OVRDAT<1:0> bits are synchronized to the PWMx time base

0 = Output overrides through the OVRDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

#### REGISTER 17-14: TRIGx: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|-----------------|-------|

|              |       |                  | TRGCI | MP<15:8>     |                  |                 |       |

| bit 15       |       |                  |       |              |                  |                 | bit 8 |

|              |       |                  |       |              |                  |                 |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|              |       |                  | TRGC  | MP<7:0>      |                  |                 |       |

| bit 7        |       |                  |       |              |                  |                 | bit 0 |

|              |       |                  |       |              |                  |                 |       |

| Legend:      |       |                  |       |              |                  |                 |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | <b>i as</b> '0' |       |

|              |       |                  |       |              |                  |                 |       |

bit 15-0 **TRGCMP<15:0>:** Trigger Control Value bits

'1' = Bit is set

When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| R/W-0           | R/W-0                                                                                                                                                                                                           | R/W-0                                                                                                                                                      | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                                                                | R/W-0                                                    | U-0                                          | U-0                          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|------------------------------|

| PHR             | PHF                                                                                                                                                                                                             | PLR                                                                                                                                                        | PLF                                                                                                                                                                                                  | FLTLEBEN                                                                                                                                             | CLLEBEN                                                  |                                              |                              |

| bit 15          |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      |                                                          |                                              | bit 8                        |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      |                                                          |                                              |                              |

| U-0             | U-0                                                                                                                                                                                                             | R/W-0                                                                                                                                                      | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                                                                | R/W-0                                                    | R/W-0                                        | R/W-0                        |

|                 |                                                                                                                                                                                                                 | BCH <sup>(1)</sup>                                                                                                                                         | BCL <sup>(1)</sup>                                                                                                                                                                                   | BPHH                                                                                                                                                 | BPHL                                                     | BPLH                                         | BPLL                         |

| bit 7           |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      |                                                          |                                              | bit (                        |

| Legend:         |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      |                                                          |                                              |                              |

| R = Readable t  | ait                                                                                                                                                                                                             | W = Writable                                                                                                                                               | hit                                                                                                                                                                                                  | II – Unimpler                                                                                                                                        | nented bit, read                                         | ae '0'                                       |                              |

| -n = Value at P |                                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                           | JIL                                                                                                                                                                                                  | '0' = Bit is cle                                                                                                                                     |                                                          | x = Bit is unkr                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | aicu                                                     |                                              |                              |

| bit 15          | PHR: PWMxH                                                                                                                                                                                                      | Rising Edge                                                                                                                                                | Frigger Enabl                                                                                                                                                                                        | e bit                                                                                                                                                |                                                          |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | Blanking count                                           | er                                           |                              |

|                 | 0 = Leading-E                                                                                                                                                                                                   | dge Blanking i                                                                                                                                             | gnores the ris                                                                                                                                                                                       | sing edge of PV                                                                                                                                      | VMxH                                                     |                                              |                              |

| bit 14          |                                                                                                                                                                                                                 | I Falling Edge                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                                                      |                                                          |                                              |                              |

|                 | •                                                                                                                                                                                                               | 0                                                                                                                                                          | 00                                                                                                                                                                                                   | 0 0                                                                                                                                                  | e Blanking coun                                          | ter                                          |                              |

| hit 12          | -                                                                                                                                                                                                               |                                                                                                                                                            | -                                                                                                                                                                                                    | Iling edge of P                                                                                                                                      |                                                          |                                              |                              |

| bit 13          |                                                                                                                                                                                                                 | Rising Edge T                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                                                                      | Blanking count                                           | ٥r                                           |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      | sing edge of PV                                                                                                                                      |                                                          |                                              |                              |

| bit 12          | PLF: PWMxL                                                                                                                                                                                                      | Falling Edge T                                                                                                                                             | rigger Enable                                                                                                                                                                                        | e bit                                                                                                                                                |                                                          |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | Blanking count                                           | er                                           |                              |

|                 | •                                                                                                                                                                                                               | •                                                                                                                                                          | •                                                                                                                                                                                                    | lling edge of P                                                                                                                                      |                                                          |                                              |                              |

| bit 11          |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      | anking Enable I                                                                                                                                      |                                                          |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      | he selected Fail<br>to the selected                                                                                                                  |                                                          |                                              |                              |

| bit 10          | •                                                                                                                                                                                                               | •                                                                                                                                                          |                                                                                                                                                                                                      | dge Blanking E                                                                                                                                       | •                                                        |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            | -                                                                                                                                                                                                    | he selected cur                                                                                                                                      |                                                          |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | current-limit in                                         | out                                          |                              |

| bit 9-6         | Unimplement                                                                                                                                                                                                     | ted: Read as 'o                                                                                                                                            | )'                                                                                                                                                                                                   |                                                                                                                                                      |                                                          |                                              |                              |

| bit 5           |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      | al High Enable                                                                                                                                       |                                                          |                                              |                              |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | als) when seled                                          | ted blanking s                               | ignal is high                |

| L:4 4           |                                                                                                                                                                                                                 | •                                                                                                                                                          |                                                                                                                                                                                                      | ng signal is hig                                                                                                                                     |                                                          |                                              |                              |

| bit 4           |                                                                                                                                                                                                                 | •                                                                                                                                                          | •••                                                                                                                                                                                                  | al Low Enable b                                                                                                                                      | DIC                                                      |                                              |                              |

|                 |                                                                                                                                                                                                                 | king (of curren                                                                                                                                            | t_limit_and/or                                                                                                                                                                                       | Equit input sign                                                                                                                                     |                                                          | tod blanking e                               | ianal is low                 |

|                 |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                                      | als) when seled                                          | ted blanking s                               | ignal is low                 |