Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm104-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Count Register                                    |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 3 | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                          |

|-------|---------------------------------------------------------------------------------------------------------|

|       | 1 = CPU Interrupt Priority Level is greater than 7                                                      |

|       | 0 = CPU Interrupt Priority Level is 7 or less                                                           |

| bit 2 | SFA: Stack Frame Active Status bit                                                                      |

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space                            |

| bit 1 | RND: Rounding Mode Select bit                                                                           |

|       | 1 = Biased (conventional) rounding is enabled                                                           |

|       | 0 = Unbiased (convergent) rounding is enabled                                                           |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit                                                    |

|       | 1 = Integer mode is enabled for DSP multiply                                                            |

|       | 0 = Fractional mode is enabled for DSP multiply                                                         |

|       |                                                                                                         |

**Note 1:** This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## TABLE 4-22: PMD REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1               | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|---------|--------|--------|--------|--------|-------|-------|--------|--------|--------|---------------------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD    | T1MD    | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD <sup>(1)</sup> | AD1MD | 0000          |

| PMD2        | 0762  | _      | —      | —      | —       | IC4MD   | IC3MD  | IC2MD  | IC1MD  |        | —     |       | _      | OC4MD  | OC3MD  | OC2MD               | OC1MD | 0000          |

| PMD3        | 0764  | —      | —      | —      | —       | —       | CMPMD  | _      | _      |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD4        | 0766  | —      | —      | —      | —       | —       | —      | _      | _      |        | —     |       | _      | REFOMD | CTMUMD | _                   | —     | 0000          |

| PMD6        | 076A  | —      | —      | —      | —       | —       | PWM3MD | PWM2MD | PWM1MD |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD7        | 076C  | _      | —      | —      | —       | -       | —      | —      | _      | -      | —     | -     | DMA0MD | —      | —      |                     | —     | 0000          |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA1MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA2MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA3MD |        |        |                     |       |               |

| PMD8        | 076E  | —      | —      | —      | SENT2MD | SENT1MD | —      | _      | DMTMD  |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

## TABLE 4-31: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISA       | 0E00  | —      | —      | —      |        |        | TRISA< | 12:7>  |       |       | —     | —     | TRISA4 | —     | _     | TRISA | <1:0>  | 1F93          |

| PORTA       | 0E02  | _      | —      | —      |        |        | RA<12  | 2:7>   |       |       |       | —     | RA4    | —     | -     | RA<   | 1:0>   | 0000          |

| LATA        | 0E04  | _      | —      | —      |        |        | LATA<1 | 2:7>   |       |       |       | —     | LATA4  | —     | -     | LATA  | <1:0>  | 0000          |

| ODCA        | 0E06  | —      | —      | —      |        |        | ODCA<  | 12:7>  |       |       |       | _     | ODCA4  | —     | -     | ODCA  | <1:0>  | 0000          |

| CNENA       | 0E08  | _      | _      | _      |        |        | CNIEA< | 12:7>  |       |       | _     | _     | CNIEA4 | _     | _     | CNIEA | <1:0>  | 0000          |

| CNPUA       | 0E0A  | —      | —      | —      |        |        | CNPUA< | :12:7> |       |       |       | _     | CNPUA4 | —     | -     | CNPU  | ۹<1:0> | 0000          |

| CNPDA       | 0E0C  | _      | _      | _      |        |        | CNPDA< | :12:7> |       |       | _     | _     | CNPDA4 | _     | _     | CNPD  | A<1:0> | 0000          |

| ANSELA      | 0E0E  | _      | —      | —      |        | ANSA<  | <12:9> |        |       | ANSA7 |       | —     | ANSA4  | —     | -     | ANSA  | <1:0>  | 1E93          |

| SR1A        | 0E10  | _      | —      | —      |        | —      | _      | SR1A9  |       |       |       | —     | SR1A4  | —     | -     |       |        | 0000          |

| SR0A        | 0E12  | _      | _      | —      |        | _      | _      | SR0A9  |       |       |       | —     | SR0A4  | —     | _     |       | _      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-32: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX04 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5   | Bit 4      | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|----------|--------|--------|-------|-------|---------|------------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  | _      | _      | _      | _      | _      |          | TRISA  | <10:7> |       | —     | —       |            | -     | TRISA<4:0> | >         |       | DF9F          |

| PORTA       | 0E02  | _      | _      | _      | _      | _      | RA<10:7> |        |        | —     | —     | RA<4:0> |            |       |            |           | 0000  |               |

| LATA        | 0E04  | —      | _      | _      | _      | _      |          | LATA<  | 10:7>  |       |       | —       |            |       | LATA<4:0>  |           |       | 0000          |

| ODCA        | 0E06  | —      | _      | _      | _      | _      |          | ODCA<  | <10:7> |       |       | —       |            | (     | ODCA<4:0>  | >         |       | 0000          |

| CNENA       | 0E08  | —      | —      | _      | _      |        |          | CNIEA  | <10:7> |       |       | —       |            | (     | CNIEA<4:0  | >         |       | 0000          |

| CNPUA       | 0E0A  | —      | —      | _      | _      |        |          | CNPUA  | <10:7> |       |       | —       | CNPUA<4:0> |       |            |           | 0000  |               |

| CNPDA       | 0E0C  | —      | —      | _      | _      |        |          | CNPDA  | <10:7> |       |       | —       |            | C     | NPDA<4:0   | >         |       | 0000          |

| ANSELA      | 0E0E  | —      | —      | _      | _      |        | ANSA<    | :10:9> | _      | ANSA7 |       | —       | ANSA4      | —     |            | ANSA<2:0> | •     | 1813          |

| SR1A        | 0E10  | —      | —      | _      | _      |        |          | SR1A9  | _      | _     |       | —       | SR1A4      | —     | —          |           |       | 0000          |

| SR0A        | 0E12  | —      | —      | _      | _      |        |          | SR0A9  | _      | _     |       | —       | SR0A4      | —     | —          |           |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

## REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

| U-0          | R-0                                     | R-0                                              | R-0              | U-0              | R/W-y                        | R/W-y                | R/W-y                |

|--------------|-----------------------------------------|--------------------------------------------------|------------------|------------------|------------------------------|----------------------|----------------------|

| _            | COSC2                                   | COSC1                                            | COSC0            | —                | NOSC2 <sup>(2)</sup>         | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15       |                                         |                                                  |                  |                  |                              |                      | bit 8                |

|              |                                         |                                                  |                  |                  |                              |                      |                      |

| R/W-0        | R/W-0                                   | R-0                                              | U-0              | R/C-0            | U-0                          | U-0                  | R/W-0                |

| CLKLOCK      | IOLOCK                                  | LOCK                                             | —                | CF               |                              |                      | OSWEN                |

| bit 7        |                                         |                                                  |                  |                  |                              |                      | bit (                |

| Legend:      |                                         | C = Clearable                                    | hit              | v = Value set    | from Configura               | tion hits on PO      | R                    |

| R = Readab   | le hit                                  | W = Writable                                     |                  | ,                | mented bit, read             |                      |                      |

| -n = Value a |                                         | '1' = Bit is set                                 |                  | '0' = Bit is cle |                              | x = Bit is unkr      | าดพุท                |

|              |                                         |                                                  |                  |                  |                              |                      | IOWIT                |

| bit 15       | Unimplemen                              | ted: Read as '                                   | 0'               |                  |                              |                      |                      |

| bit 14-12    | -                                       | Current Oscilla                                  |                  | bits (read-only  | ()                           |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | · · ·            | ,                            |                      |                      |

|              | 110 <b>= Fast R</b>                     | C Oscillator (F                                  | RC) with Divid   |                  |                              |                      |                      |

|              |                                         | ower RC Oscill                                   |                  |                  |                              |                      |                      |

|              |                                         | p FRC Oscillator<br>y Oscillator (X <sup>-</sup> |                  | ыры              |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  | II PLL           |                              |                      |                      |

|              |                                         | C Oscillator (F                                  | ,                | y N and PLL      |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | ,                |                              |                      |                      |

| bit 11       | -                                       | ted: Read as '                                   |                  |                  |                              |                      |                      |

| bit 10-8     | NOSC<2:0>:                              | New Oscillator                                   | r Selection bits | <sub>S</sub> (2) |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | le-by-16         |                              |                      |                      |

|              | 101 = Low-P                             | ower RC Oscill<br><sub>/ed</sub> (5)             |                  |                  |                              |                      |                      |

|              |                                         | y Oscillator (X <sup>-</sup>                     | Г, HS, EC) wit   | h PLL            |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | y N and PLL      |                              |                      |                      |

| hit 7        |                                         | C Oscillator (F                                  | ,                |                  |                              |                      |                      |

| bit 7        |                                         | Clock Lock Ena                                   |                  | onfigurations a  | re locked; if FCk            | (SM0 = 0  then)      | clock and Pl         |

|              |                                         | ations may be r                                  |                  |                  |                              |                      |                      |

|              |                                         |                                                  |                  | ked, configurat  | ions may be mo               | odified              |                      |

| bit 6        | IOLOCK: I/O                             | Lock Enable b                                    | oit              |                  |                              |                      |                      |

|              | 1 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

|              | 0 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

| bit 5        |                                         | ock Status bit                                   |                  |                  |                              |                      |                      |

|              |                                         | that PLL is in that PLL is ou                    |                  |                  | satisfied<br>progress or PLL | is disabled          |                      |

|              |                                         |                                                  |                  |                  | -                            |                      |                      |

|              | Vrites to this regis<br>dsPIC33/PIC24 F |                                                  |                  |                  |                              |                      | ils.                 |

|              | irect clock switch                      | -                                                | -                |                  | -                            | -                    |                      |

| te           | ed. This applies to                     | o clock switche                                  | s in either dire | ection. In these | instances, the               |                      |                      |

|              | RC mode as a tra                        |                                                  |                  |                  | L modes.                     |                      |                      |

|              | his register reset                      | -                                                |                  |                  |                              |                      |                      |

| <b>4</b> : C | OSC<2:0> bits w                         | viii be set to '0k                               | DIOU when H      | to fails.        |                              |                      |                      |

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

5: User cannot write '0b100' to NOSC<2:0>. COSC<2:0> will be set to '0b100' (BFRC) when the FRC fails.

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: CAN1 Module Disable bit<sup>(1)</sup>

- 1 = CAN1 module is disabled0 = CAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EVXXXGM10X devices only.

## REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | —   | —   | IC4MD | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | _   | —   | OC4MD | OC3MD | OC2MD | OC1MD |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | Unimplemented: Read as '0'                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------|

| bit 11-8  | <b>IC4MD:IC1MD:</b> Input Capture x (x = 1-4) Module Disable bits                                           |

|           | 1 = Input Capture x module is disabled                                                                      |

|           | 0 = Input Capture x module is enabled                                                                       |

| bit 7-4   | Unimplemented: Read as '0'                                                                                  |

| bit 3-0   | <b>OC4MD:OC1MD:</b> Output Compare x (x = 1-4) Module Disable bits                                          |

|           | <ul> <li>1 = Output Compare x module is disabled</li> <li>0 = Output Compare x module is enabled</li> </ul> |

## 11.8 Peripheral Pin Select Registers

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | INT1R | <7:0> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —     | —     | —     | —     |

| bit 7  |       |       |       |       |       |       | bit C |

|        |       |       |       |       |       |       |       |

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

## REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0           | U-0                             | U-0                                | U-0   | U-0                                | U-0             | U-0                | U-0   |  |  |  |

|---------------|---------------------------------|------------------------------------|-------|------------------------------------|-----------------|--------------------|-------|--|--|--|

| _             | —                               | —                                  | -     | _                                  | —               | —                  | —     |  |  |  |

| bit 15        |                                 |                                    |       |                                    |                 |                    | bit 8 |  |  |  |

|               |                                 |                                    |       |                                    |                 |                    |       |  |  |  |

| R/W-0         | R/W-0                           | R/W-0                              | R/W-0 | R/W-0                              | R/W-0           | R/W-0              | R/W-0 |  |  |  |

|               |                                 |                                    | INT2F | R<7:0>                             |                 |                    |       |  |  |  |

| bit 7         |                                 |                                    |       |                                    |                 |                    | bit 0 |  |  |  |

|               |                                 |                                    |       |                                    |                 |                    |       |  |  |  |

| Legend:       |                                 |                                    |       |                                    |                 |                    |       |  |  |  |

| R = Readable  | e bit                           | W = Writable                       | bit   | U = Unimplemented bit, read as '0' |                 |                    |       |  |  |  |

| -n = Value at | POR                             | '1' = Bit is set                   |       | '0' = Bit is cleared               |                 | x = Bit is unknown |       |  |  |  |

|               |                                 |                                    |       |                                    |                 |                    |       |  |  |  |

| bit 15-8      | Unimplemen                      | ted: Read as '                     | )'    |                                    |                 |                    |       |  |  |  |

| bit 7-0       |                                 | Assign Externa<br>-2 for input pin |       |                                    | orresponding RI | Pn Pin bits        |       |  |  |  |

|               | 10110101 = Input tied to RPI181 |                                    |       |                                    |                 |                    |       |  |  |  |

|               | •                               |                                    |       |                                    |                 |                    |       |  |  |  |

|               | •                               |                                    |       |                                    |                 |                    |       |  |  |  |

|               | •                               |                                    | -     |                                    |                 |                    |       |  |  |  |

|               |                                 | Input tied to CN                   |       |                                    |                 |                    |       |  |  |  |

|               | 00000000 = Input tied to Vss    |                                    |       |                                    |                 |                    |       |  |  |  |

## REGISTER 14-5: DMTCNTL: DEADMAN TIMER COUNT REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0           | R/W-0             | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|----------------------------------------|-----------------|-------------------|-------|-------|

|                                    |       |       | COUNT                                  | ER<15:8>        |                   |       |       |

| bit 15                             |       |       |                                        |                 |                   |       | bit 8 |

|                                    |       |       |                                        |                 |                   |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0           | R/W-0             | R/W-0 | R/W-0 |

|                                    |       |       | COUN                                   | ΓER<7:0>        |                   |       |       |

| bit 7                              |       |       |                                        |                 |                   |       | bit 0 |

|                                    |       |       |                                        |                 |                   |       |       |

| Legend:                            |       |       |                                        |                 |                   |       |       |

| R = Readable bit W = Writable bit  |       | oit   | U = Unimpler                           | mented bit, rea | i <b>d as</b> '0' |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknow |                 |                   | nown  |       |

bit 15-0 COUNTER<15:0>: Read Current Contents of Lower DMT Counter bits

## REGISTER 14-6: DMTCNTH: DEADMAN TIMER COUNT REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

|                                    |       |       | COUNT                                   | ER<31:24>                          |       |       |       |  |

| bit 15                             |       |       |                                         |                                    |       |       | bit 8 |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |       | COUNT                                   | ER<23:16>                          |       |       |       |  |

| bit 7                              |       |       |                                         |                                    |       |       | bit 0 |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| Legend:                            |       |       |                                         |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | it                                      | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |

bit 15-0 COUNTER<31:16>: Read Current Contents of Higher DMT Counter bits

## REGISTER 14-9: DMTPSINTVL: DMT POST CONFIGURE INTERVAL STATUS REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-----------------------------------------|----------|-------|-------|-------|

|                                    |       |       | PSIN                                    | FV<15:8> |       |       |       |

| bit 15                             |       |       |                                         |          |       |       | bit 8 |

|                                    |       |       |                                         |          |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | PSIN                                    | TV<7:0>  |       |       |       |

| bit 7                              |       |       |                                         |          |       |       | bit 0 |

|                                    |       |       |                                         |          |       |       |       |

| Legend:                            |       |       |                                         |          |       |       |       |

| R = Readable bit W = Writable bit  |       | oit   | U = Unimplemented bit, read as '0'      |          |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |          |       | nown  |       |

bit 15-0 **PSINTV<15:0>:** Lower DMT Window Interval Configuration Status bits This is always the value of the FDMTINTVL Configuration register.

## REGISTER 14-10: DMTPSINTVH: DMT POST CONFIGURE INTERVAL STATUS REGISTER HIGH

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |  |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|--|

|                                   |       |                  | PSINT                              | V<31:24>             |       |                    |       |  |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |  |

|                                   |       |                  |                                    |                      |       |                    |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |  |

|                                   |       |                  | PSINT                              | V<23:16>             |       |                    |       |  |

| bit 7                             |       |                  |                                    |                      |       |                    | bit C |  |

| Legend:                           |       |                  |                                    |                      |       |                    |       |  |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |  |

| -n = Value at POR '1'             |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |  |

bit 15-0 **PSINTV<31:16>:** Higher DMT Window Interval Configuration Status bits This is always the value of the FDMTINTVH Configuration register.

## REGISTER 17-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

|                                    |       | DAMA  |       | D/14/ 0                                 |       | D 44/ 0 |       |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|---------|-------|--|

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0   | R/W-0 |  |

|                                    |       |       | PDC   | x<15:8>                                 |       |         |       |  |

| bit 15                             |       |       |       |                                         |       |         | bit 8 |  |

|                                    |       |       |       |                                         |       |         | ]     |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0   | R/W-0 |  |

|                                    |       |       | PDC   | \$x<7:0>                                |       |         |       |  |

| bit 7                              |       |       |       |                                         |       |         | bit 0 |  |

|                                    |       |       |       |                                         |       |         |       |  |

| Legend:                            |       |       |       |                                         |       |         |       |  |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'      |       |         |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |         |       |  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

#### REGISTER 17-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

|                   |       |                  | PHAS  | Ex<15:8>         |                 |                    |       |  |

| bit 15            |       |                  |       |                  |                 |                    | bit 8 |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|                   |       |                  | PHAS  | Ex<7:0>          |                 |                    |       |  |

| bit 7             |       |                  |       |                  |                 |                    | bit 0 |  |

| Legend:           |       |                  |       |                  |                 |                    |       |  |

| R = Readable bit  |       | W = Writable bit |       | U = Unimpler     | nented bit, rea | ad as '0'          |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs.

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL.

## 24.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the ADxCSSL/ADxCSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using the DMA peripheral.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1.c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADCxBUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUX A selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. For configuration examples, refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual".

| Base<br>Instr<br># Assembly<br>Mnemonic<br>63 RETLW |        | Assembly Syntax |                         | Description                                       | # of<br>Words | # of<br>Cycles<br>6 (5) | Status Flags<br>Affected |

|-----------------------------------------------------|--------|-----------------|-------------------------|---------------------------------------------------|---------------|-------------------------|--------------------------|

|                                                     |        |                 |                         | Return with literal in Wn                         | 1             |                         | SFA                      |

| 64                                                  | RETURN | RETURN          |                         | Return from Subroutine                            | 1             | 6 (5)                   | SFA                      |

| 65 RLC                                              |        | RLC             | f                       | f = Rotate Left through Carry f                   | 1             | 1                       | C,N,Z                    |

|                                                     |        | RLC             | f,WREG                  | WREG = Rotate Left through Carry f                | 1             | 1                       | C,N,Z                    |

|                                                     |        | RLC             | Ws,Wd                   | Wd = Rotate Left through Carry Ws                 | 1             | 1                       | C,N,Z                    |

| 66                                                  | RLNC   | RLNC            | f                       | f = Rotate Left (No Carry) f                      | 1             | 1                       | N,Z                      |

|                                                     |        | RLNC            | f,WREG                  | WREG = Rotate Left (No Carry) f                   | 1             | 1                       | N,Z                      |

|                                                     |        | RLNC            | Ws,Wd                   | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                       | N,Z                      |

| 67                                                  | RRC    | RRC             | f                       | f = Rotate Right through Carry f                  | 1             | 1                       | C,N,Z                    |

|                                                     |        | RRC             | f,WREG                  | WREG = Rotate Right through Carry f               | 1             | 1                       | C,N,Z                    |

|                                                     |        | RRC             | Ws,Wd                   | Wd = Rotate Right through Carry Ws                | 1             | 1                       | C,N,Z                    |

| 68                                                  | RRNC   | RRNC            | f                       | f = Rotate Right (No Carry) f                     | 1             | 1                       | N,Z                      |

|                                                     |        | RRNC            | f,WREG                  | WREG = Rotate Right (No Carry) f                  | 1             | 1                       | N,Z                      |

|                                                     |        | RRNC            | Ws,Wd                   | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                       | N,Z                      |

| 69                                                  | SAC    | SAC             | Acc,#Slit4,Wdo          | Store Accumulator                                 | 1             | 1                       | None                     |

|                                                     |        | SAC.R           | Acc,#Slit4,Wdo          | Store Rounded Accumulator                         | 1             | 1                       | None                     |

| 70                                                  | SE     | SE              | Ws,Wnd                  | Wnd = sign-extended Ws                            | 1             | 1                       | C,N,Z                    |

| 71 SETM                                             | SETM   | SETM            | f                       | f = 0xFFFF                                        | 1             | 1                       | None                     |

|                                                     |        | SETM            | WREG                    | WREG = 0xFFFF                                     | 1             | 1                       | None                     |

|                                                     |        | SETM            | Ws                      | Ws = 0xFFFF                                       | 1             | 1                       | None                     |

| 72 SFTAC                                            | SFTAC  | SFTAC           | Acc,Wn                  | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                       | OA,OB,OAE<br>SA,SB,SAE   |

|                                                     |        | SFTAC           | Acc,#Slit6              | Arithmetic Shift Accumulator by Slit6             | 1             | 1                       | OA,OB,OAE<br>SA,SB,SAE   |

| 73                                                  | SL     | SL              | f                       | f = Left Shift f                                  | 1             | 1                       | C,N,OV,Z                 |

|                                                     |        | SL              | f,WREG                  | WREG = Left Shift f                               | 1             | 1                       | C,N,OV,Z                 |

|                                                     |        | SL              | Ws,Wd                   | Wd = Left Shift Ws                                | 1             | 1                       | C,N,OV,Z                 |

|                                                     |        | SL              | Wb,Wns,Wnd              | Wnd = Left Shift Wb by Wns                        | 1             | 1                       | N,Z                      |

|                                                     |        | SL              | Wb,#lit5,Wnd            | Wnd = Left Shift Wb by lit5                       | 1             | 1                       | N,Z                      |

| 74 SUB                                              | SUB    | SUB             | Acc                     | Subtract Accumulators                             | 1             | 1                       | OA,OB,OA<br>SA,SB,SA     |

|                                                     |        | SUB             | f                       | f = f – WREG                                      | 1             | 1                       | C,DC,N,OV,               |

|                                                     |        | SUB             | f,WREG                  | WREG = f – WREG                                   | 1             | 1                       | C,DC,N,OV,               |

|                                                     |        | SUB             | #lit10,Wn               | Wn = Wn – lit10                                   | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUB             | Wb,Ws,Wd                | Wd = Wb – Ws                                      | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUB             | Wb,#lit5,Wd             | Wd = Wb – lit5                                    | 1             | 1                       | C,DC,N,OV                |

| 75                                                  | SUBB   | SUBB            | f                       | $f = f - WREG - (\overline{C})$                   | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUBB            | f,WREG                  | WREG = $f - WREG - (\overline{C})$                | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUBB            | #lit10,Wn               | $Wn = Wn - lit10 - (\overline{C})$                | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUBB            | Wb,Ws,Wd                | $Wd = Wb - Ws - (\overline{C})$                   | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUBB            | Wb,#lit5,Wd             | $Wd = Wb - lit5 - (\overline{C})$                 | 1             | 1                       | C,DC,N,OV                |

| 76                                                  | SUBR   | SUBR            | f                       | f = WREG - f                                      | 1             | 1                       | C,DC,N,OV                |

| 76                                                  | DODIC  | SUBR            | f,WREG                  | WREG = WREG – f                                   | 1             | 1                       | C,DC,N,OV                |

|                                                     |        | SUBR            | Wb,Ws,Wd                | WkeG = WkeG = 1<br>Wd = Ws - Wb                   | 1             | 1                       | C,DC,N,OV                |

|                                                     |        |                 | WD,WS,Wd<br>WD,#lit5,Wd | Wd = VVS = VVD $Wd = lit5 - Wb$                   | 1             | 1                       | C,DC,N,OV                |

| 77                                                  | GUDDE  | SUBR            |                         |                                                   |               |                         |                          |

|                                                     | SUBBR  | SUBBR           | f                       | f = WREG - f - (C)                                | 1             | 1                       | C,DC,N,OV                |

|                                                     |        |                 | + MDEC                  | WREG = WREG $- f - (C)$                           | 1             | . 1                     | C,DC,N,OV                |

|                                                     |        | SUBBR           | f,WREG<br>Wb,Ws,Wd      | $WLC = WLC + (C)$ $Wd = Ws - Wb - (\overline{C})$ | 1             | 1                       | C,DC,N,OV                |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

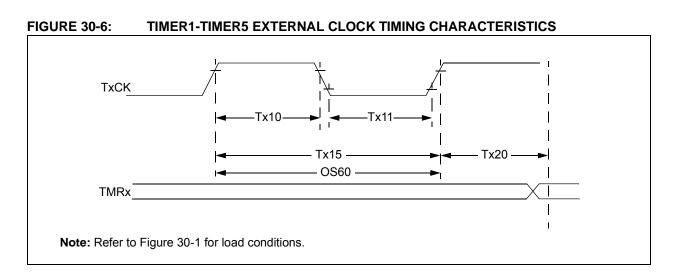

| AC CHARACTERISTICS |           |                                                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                                |  |

|--------------------|-----------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|--------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(2)</sup>                                                                     |                                                                                                                                                                                                                                                                                       | Min.                                   | Тур. | Max.          | Units | Conditions                                                                     |  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                 | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |  |

|                    |           |                                                                                                   | Asynchronous mode                                                                                                                                                                                                                                                                     | 35                                     | —    | _             | ns    |                                                                                |  |

| TA11               | ΤτxL      | T1CK Low<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   | _    |               | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |  |

|                    |           |                                                                                                   | Asynchronous mode                                                                                                                                                                                                                                                                     | 10                                     | _    | _             | ns    |                                                                                |  |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                              | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>40 or<br>(2 Tcy + 40)/N | —    | —             | ns    | N = Prescaler<br>Value<br>(1, 8, 64, 256)                                      |  |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting TCS<br>(T1CON<1>) bit) |                                                                                                                                                                                                                                                                                       | DC                                     | _    | 50            | kHz   |                                                                                |  |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                      |                                                                                                                                                                                                                                                                                       | 0.75 Tcy + 40                          |      | 1.75 Tcy + 40 | ns    |                                                                                |  |

## TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Timer1 is a Type A.

**2:** These parameters are characterized but not tested in manufacturing.

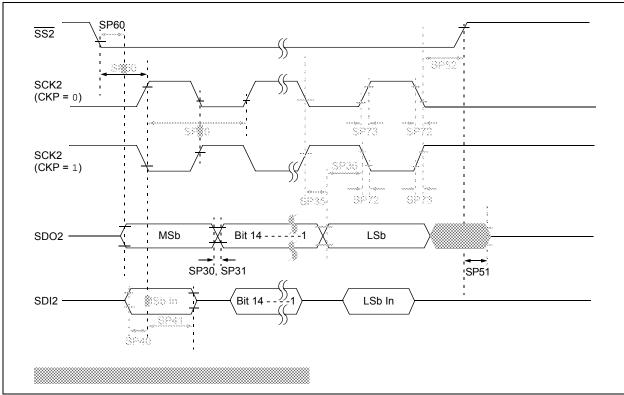

# FIGURE 30-16: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS                       |         |                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |            |  |  |  |

|------------------------------------------|---------|------------------------------------|------------------------------------------------------|---------------------|------|-------|------------|--|--|--|

| Param<br>No.                             | Symbol  | Characteristic                     | Min.                                                 | Тур. <sup>(1)</sup> | Max. | Units | Conditions |  |  |  |

| Comparator DC Characteristics            |         |                                    |                                                      |                     |      |       |            |  |  |  |

| HCM30                                    | VOFFSET | Comparator Offset Voltage          | -80                                                  | ±60                 | 80   | mV    |            |  |  |  |

| HCM31                                    | VHYST   | Input Hysteresis Voltage           | —                                                    | 30                  | _    | mV    |            |  |  |  |

| HCM34                                    | VICM    | Input Common-Mode Voltage          | AVss                                                 | —                   | AVdd | V     |            |  |  |  |

| Op Amp DC Characteristics <sup>(2)</sup> |         |                                    |                                                      |                     |      |       |            |  |  |  |

| HCM40                                    | VCMR    | Common-Mode Input<br>Voltage Range | AVss                                                 | —                   | AVdd | V     |            |  |  |  |

| HCM42                                    | VOFFSET | Op Amp Offset Voltage              | -50                                                  | ±6                  | 50   | mV    |            |  |  |  |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Resistances can vary by ±10% between op amps.

3: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter HBO10 in Table 31-10 for the minimum and maximum BOR values.

## TABLE 31-18: ADC MODULE SPECIFICATIONS (12-BIT MODE)

| AC CHARACTERISTICS |                            |                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |                                                  |                                                  |  |  |  |  |

|--------------------|----------------------------|---------------------------|------------------------------------------------------|------|------|--------------------------------------------------|--------------------------------------------------|--|--|--|--|

| Param<br>No.       | Symbol Characteristic      |                           | Min.                                                 | Тур. | Max. | Units                                            | Conditions                                       |  |  |  |  |

|                    | ADC Accuracy (12-Bit Mode) |                           |                                                      |      |      |                                                  |                                                  |  |  |  |  |

| HAD20a             | Nr                         | Resolution                | 12 data bits                                         |      | bits |                                                  |                                                  |  |  |  |  |

| HAD21a             | INL                        | Integral Nonlinearity     | -2 — +2                                              |      | LSb  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5.5V |                                                  |  |  |  |  |

| HAD22a             | DNL                        | Differential Nonlinearity | > -1                                                 | _    | < 1  | LSb                                              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5.5V |  |  |  |  |

| HAD23a             | Gerr                       | Gain Error                | -10                                                  | 4    | 10   | LSb                                              | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |  |  |  |  |

| HAD24a             | EOFF                       | Offset Error              | -10                                                  | 1.75 | 10   | LSb                                              | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |  |  |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

## dsPIC33EVXXXGM00X/10X FAMILY

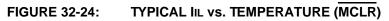

## 32.7 Leakage Current

NOTES:

NOTES: