Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Betans                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm104t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

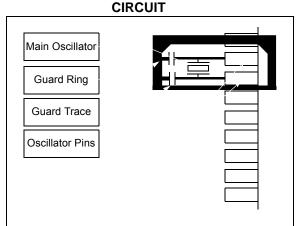

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

#### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

#### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

#### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

#### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

#### 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

#### 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

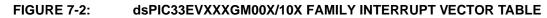

| ▲    | Reserved                                                                                  | BSLIM<12:0>(1) + 0x000000                 |                          |

|------|-------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------|

|      | Reserved                                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000002     |                          |

|      | Oscillator Fail Trap Vector                                                               | BSLIM<12:0>(1) + 0x000004                 |                          |

|      | Address Error Trap Vector                                                                 | BSLIM<12:0> <sup>(1)</sup> + 0x000006     |                          |

|      | Generic Hard Trap Vector                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000008     |                          |

|      | Stack Error Trap Vector                                                                   | BSLIM<12:0>(1) + 0x00000A                 |                          |

|      | Math Error Trap Vector                                                                    | BSLIM<12:0> <sup>(1)</sup> + 0x00000C     |                          |

|      | DMAC Error Trap Vector                                                                    | BSLIM<12:0> <sup>(1)</sup> + 0x00000E     |                          |

|      | Generic Soft Trap Vector                                                                  | BSLIM<12:0>(1) + 0x000010                 |                          |

|      | Reserved                                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000012     |                          |

|      | Interrupt Vector 0                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000014     |                          |

|      | Interrupt Vector 1                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000016     |                          |

|      | :                                                                                         | :                                         |                          |

|      | :                                                                                         | :                                         |                          |

|      | :                                                                                         | :                                         |                          |

| Σ    | Interrupt Vector 52                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x00007C     |                          |

|      | Interrupt Vector 53                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|      | Interrupt Vector 54                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x000080     | See Table 7-1 for        |

|      | :                                                                                         | :                                         | Interrupt Vector Details |

|      | :                                                                                         | :                                         | /                        |

|      | :                                                                                         | :                                         |                          |

|      | Interrupt Vector 116                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC     |                          |

|      | Interrupt Vector 117                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x00007E     |                          |

|      | Interrupt Vector 118                                                                      | BSLIM<12:0>(1) + 0x000100                 |                          |

|      | Interrupt Vector 119                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x000102     |                          |

|      | Interrupt Vector 120                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x000104     |                          |

|      | :                                                                                         | :                                         |                          |

|      | :                                                                                         | :                                         |                          |

|      | :                                                                                         | :                                         |                          |

|      | Interrupt Vector 244                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0001FC     |                          |

| V    | Interrupt Vector 245                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE     |                          |

| Note | <ol> <li>The address depends on the si<br/>[(BSLIM&lt;12:0&gt; – 1) x 0x400] +</li> </ol> | ze of the Boot Segment defined by Offset. | y BSLIM<12:0>:           |

| U-0                                                                        | U-0                             | U-0            | U-0 | U-0              | U-0              | U-0    | U-0    |  |  |

|----------------------------------------------------------------------------|---------------------------------|----------------|-----|------------------|------------------|--------|--------|--|--|

| _                                                                          | —                               | —              | —   | —                | —                | —      | —      |  |  |

| bit 15                                                                     |                                 |                |     |                  |                  |        | bit    |  |  |

|                                                                            |                                 |                |     |                  |                  |        |        |  |  |

| U-0                                                                        | U-0                             | U-0            | U-0 | R-0              | R-0              | R-0    | R-0    |  |  |

| _                                                                          | —                               | —              | —   | PWCOL3           | PWCOL2           | PWCOL1 | PWCOL0 |  |  |

| bit 7                                                                      |                                 |                |     |                  |                  |        | bit    |  |  |

|                                                                            |                                 |                |     |                  |                  |        |        |  |  |

| Legend:                                                                    |                                 |                |     |                  |                  |        |        |  |  |

| R = Readab                                                                 | le bit                          | W = Writable   | bit | U = Unimpler     | nented bit, read | as '0' |        |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                 |                |     |                  |                  |        | nown   |  |  |

|                                                                            |                                 |                |     |                  |                  |        |        |  |  |

| bit 15-4                                                                   | Unimplemen                      | ted: Read as ' | 0'  |                  |                  |        |        |  |  |

| bit 3                                                                      |                                 | annel 3 Periph |     | Ilision Flag bit |                  |        |        |  |  |

|                                                                            | 1 = Write collision is detected |                |     |                  |                  |        |        |  |  |

#### REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| 1 = Write collision is detected     |

|-------------------------------------|

| 0 = Write collision is not detected |

|                                     |

0 = Write collision is not detected

1 = Write collision is detected0 = Write collision is not detected

PWCOL2: Channel 2 Peripheral Write Collision Flag bit

PWCOL1: Channel 1 Peripheral Write Collision Flag bit

bit 0 PWCOL0: Channel 0 Peripheral Write Collision Flag bit

- 1 = Write collision is detected

- 0 = Write collision is not detected

bit 2

bit 1

| U-0                                                 | U-0                                                           | U-0            | U-0                        | U-0                                     | U-0 | U-0 | U-0   |  |  |

|-----------------------------------------------------|---------------------------------------------------------------|----------------|----------------------------|-----------------------------------------|-----|-----|-------|--|--|

| —                                                   | —                                                             | —              | —                          |                                         | —   | —   | —     |  |  |

| bit 15                                              |                                                               |                |                            |                                         |     |     | bit 8 |  |  |

|                                                     |                                                               |                |                            |                                         |     |     |       |  |  |

| U-0                                                 | U-0                                                           | U-0            | R/W-0                      | U-0                                     | U-0 | U-0 | U-0   |  |  |

| —                                                   | —                                                             | —              | DMA0MD <sup>(1)</sup>      | —                                       | —   | —   | —     |  |  |

|                                                     |                                                               |                | DMA1MD <sup>(1)</sup>      | -                                       |     |     |       |  |  |

|                                                     |                                                               |                | DMA2MD <sup>(1)</sup>      | -                                       |     |     |       |  |  |

|                                                     |                                                               |                | DMA3MD <sup>(1)</sup>      |                                         |     |     |       |  |  |

| bit 7                                               |                                                               |                |                            |                                         |     |     | bit 0 |  |  |

|                                                     |                                                               |                |                            |                                         |     |     |       |  |  |

| Legend:                                             |                                                               |                |                            |                                         |     |     |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented |                                                               |                |                            |                                         |     |     |       |  |  |

| -n = Value at POR '1' = Bit is set                  |                                                               |                |                            | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

|                                                     |                                                               |                |                            |                                         |     |     |       |  |  |

| bit 15-5                                            | Unimplement                                                   |                |                            |                                         |     |     |       |  |  |

| bit 4                                               | DMA0MD: DMA0 Module Disable bit <sup>(1)</sup>                |                |                            |                                         |     |     |       |  |  |

|                                                     | 1 = DMA0 module is disabled<br>0 = DMA0 module is enabled     |                |                            |                                         |     |     |       |  |  |

|                                                     | 0 = DMA0 module is enabled DMA1MD: DMA1 Module Disable bit(1) |                |                            |                                         |     |     |       |  |  |

|                                                     |                                                               |                |                            |                                         |     |     |       |  |  |

|                                                     | 1 = DMA1 module is disabled<br>0 = DMA1 module is enabled     |                |                            |                                         |     |     |       |  |  |

|                                                     | DMA2MD: DN                                                    | A2 Module I    | Disable bit <sup>(1)</sup> |                                         |     |     |       |  |  |

|                                                     | 1 = DMA2 mo                                                   |                |                            |                                         |     |     |       |  |  |

|                                                     | 0 = DMA2 mo                                                   | dule is enable |                            |                                         |     |     |       |  |  |

|                                                     | DMA3MD: DMA3 Module Disable bit <sup>(1)</sup>                |                |                            |                                         |     |     |       |  |  |

|                                                     | 1 = DMA3 mo<br>0 = DMA3 mo                                    |                |                            |                                         |     |     |       |  |  |

| bit 3-0                                             | Unimplement                                                   | ted: Read as   | <b>'</b> 0 <b>'</b>        |                                         |     |     |       |  |  |

|                                                     |                                                               |                |                            |                                         |     |     |       |  |  |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

**Note 1:** This single bit enables and disables all four DMA channels.

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |

|------------------------------|---------------|----------|--------------------|

| External Interrupt 1         | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2         | INT2          | RPINR1   | INT2R<7:0>         |

| Timer2 External Clock        | T2CK          | RPINR3   | T2CKR<7:0>         |

| Input Capture 1              | IC1           | RPINR7   | IC1R<7:0>          |

| Input Capture 2              | IC2           | RPINR7   | IC2R<7:0>          |

| Input Capture 3              | IC3           | RPINR8   | IC3R<7:0>          |

| Input Capture 4              | IC4           | RPINR8   | IC4R<7:0>          |

| Output Compare Fault A       | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1                  | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2                  | FLT2          | RPINR12  | FLT2R<7:0>         |

| UART1 Receive                | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART2 Receive                | U2RX          | RPINR19  | U2RXR<7:0>         |

| SPI2 Data Input              | SDI2          | RPINR22  | SDI2R<7:0>         |

| SPI2 Clock Input             | SCK2          | RPINR22  | SCK2R<7:0>         |

| SPI2 Slave Select            | SS2           | RPINR23  | SS2R<7:0>          |

| CAN1 Receive                 | C1RX          | RPINR26  | C1RXR<7:0>         |

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<7:0>       |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<7:0>       |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<7:0>       |

| SENT1 Input                  | SENT1R        | RPINR44  | SENT1R<7:0>        |

| SENT2 Input                  | SENT2R        | RPINR45  | SENT2R<7:0>        |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK2R6                                            | SCK2R5                                                                           | SCK2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SCK2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCK2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SCK2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCK2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SDI2R6                                            | SDI2R5                                                                           | SDI2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SDI2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDI2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit                                               | W = Writable                                                                     | bit                                                                                                                                                                                                                                                                                                                                                                                                           | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>d as</b> '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POR                                               | '1' = Bit is set                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                               | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •<br>•<br>000000001 =<br>00000000 =               | Input tied to Cl                                                                 | MP1<br>SS                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (see Table 1 <sup>-</sup><br>10110101 =<br>•<br>• | 1-2 for input pin<br>Input tied to RI                                            | selection num<br>PI181                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | esponding RPn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |