Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

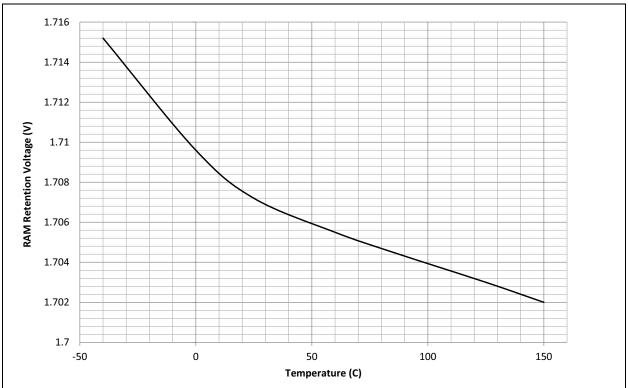

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

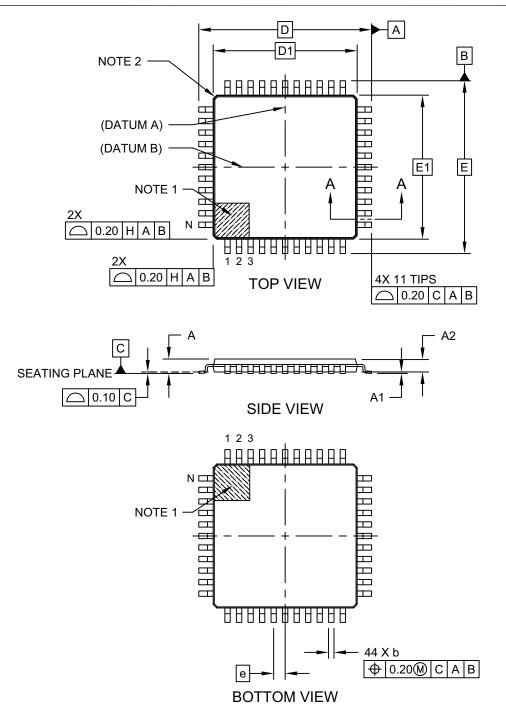

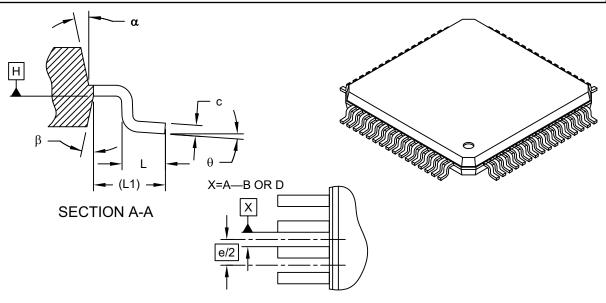

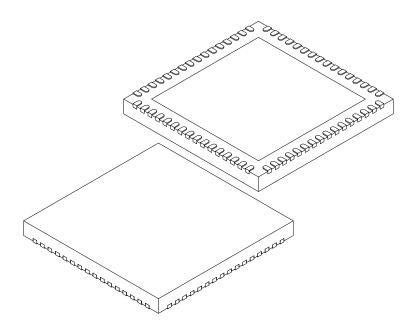

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm106-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Timers/Output Compare/Input Capture**

- Nine General Purpose Timers:

- Five 16-bit and up to two 32-bit timers/counters; Timer3 can provide ADC trigger

- Four Output Compare modules Configurable as Timers/Counters

- Four Input Capture modules

## **Communication Interfaces**

- Two Enhanced Addressable Universal Asynchronous Receiver/Transmitter (UART) modules (6.25 Mbps):

- With support for LIN/J2602 bus and IrDA®

- High and low speed (SCI)

- Two SPI modules (15 Mbps):

- 25 Mbps data rate without using PPS

- One I<sup>2</sup>C module (up to 1 Mbaud) with SMBus Support

- Two SENT J2716 (Single-Edge Nibble Transmission-Transmit/Receive) module for Automotive Applications

- One CAN module:

- 32 buffers, 16 filters and three masks

# **Direct Memory Access (DMA)**

- 4-Channel DMA with User-Selectable Priority Arbitration

- UART, Serial Peripheral Interface (SPI), ADC, Input Capture, Output Compare and Controller Area Network (CAN)

## Input/Output

- GPIO Registers to Support Selectable Slew Rate I/Os

- Peripheral Pin Select (PPS) to allow Function Remap

- Sink/Source: 8 mA or 12 mA, Pin-Specific for Standard VOH/VOL

- · Selectable Open-Drain, Pull-ups and Pull-Downs

- Change Notice Interrupts on All I/O Pins

## **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1: -40°C to +125°C) Compliant

- AEC-Q100 REVG (Grade 0: -40°C to +150°C) Compliant

- Class B Safety Library, IEC 60730

## **Class B Fault Handling Support**

- Backup FRC

- · Windowed WDT uses LPRC

- Windowed Deadman Timer (DMT) uses System Clock (System Windowed Watchdog Timer)

- H/W Clock Monitor Circuit

- Oscillator Frequency Monitoring through CTMU (OSCI, SYSCLK, FRC, BFRC, LPRC)

- Dedicated PWM Fault Pin

- Lockable Clock Configuration

## **Debugger Development Support**

- In-Circuit and In-Application Programming

- Three Complex and Five Simple Breakpoints

- Trace and Run-Time Watch

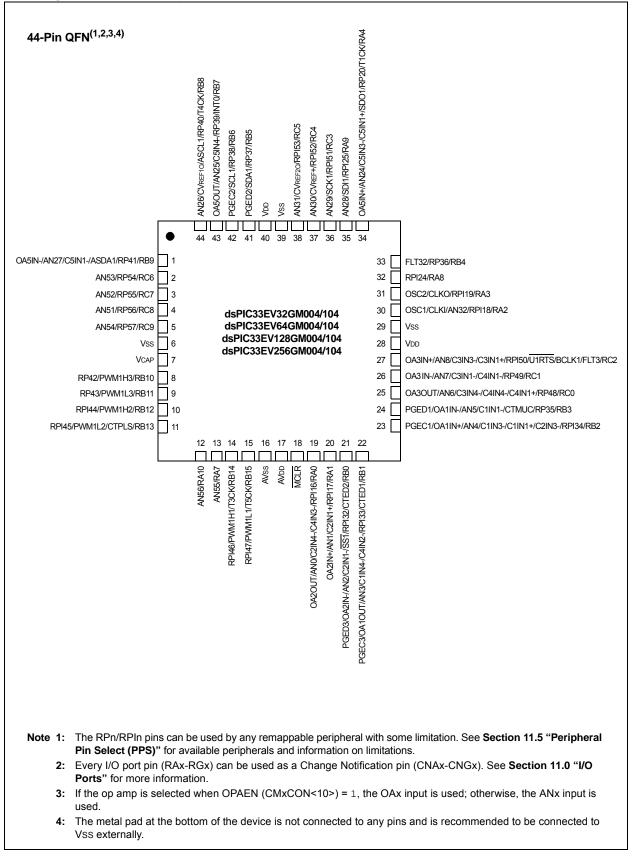

## **Pin Diagrams (Continued)**

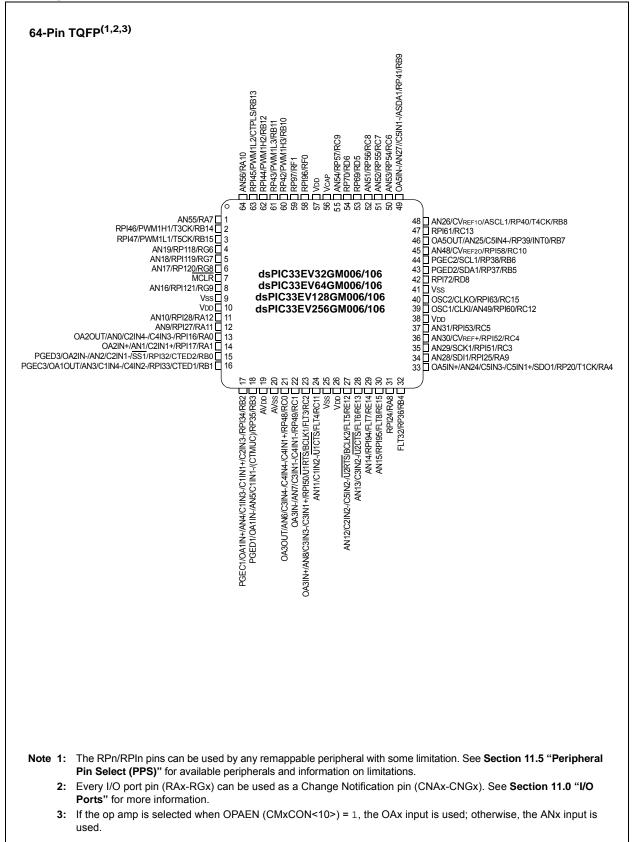

## **Pin Diagrams (Continued)**

| TABLE 1-1: PINO                   |             | D DESC         | RIPTI   | ONS (CONTINUED)                                                            |

|-----------------------------------|-------------|----------------|---------|----------------------------------------------------------------------------|

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                |

| SCK2                              | I/O         | ST             | Yes     | Synchronous serial clock input/output for SPI2.                            |

| SDI2                              | I           | ST             | Yes     | SPI2 data in.                                                              |

| SDO2                              | 0           | —              | Yes     | SPI2 data out.                                                             |

| SS2                               | I/O         | ST             | Yes     | SPI2 slave synchronization or frame pulse I/O.                             |

| SCL1                              | I/O         | ST             | No      | Synchronous serial clock input/output for I2C1.                            |

| SDA1                              | I/O         | ST             | No      | Synchronous serial data input/output for I2C1.                             |

| ASCL1                             | I/O         | ST             | No      | Alternate synchronous serial clock input/output for I2C1.                  |

| ASDA1                             | I/O         | ST             | No      | Alternate synchronous serial data input/output for I2C1.                   |

| C1RX                              | I           | ST             | Yes     | CAN1 bus receive pin.                                                      |

| C1TX                              | 0           | —              | Yes     | CAN1 bus transmit pin.                                                     |

| SENT1TX                           | 0           | —              | Yes     | SENT1 transmit pin.                                                        |

| SENT1RX                           | 1           | —              | Yes     | SENT1 receive pin.                                                         |

| SENT2TX                           | 0           | —              | Yes     | SENT2 transmit pin.                                                        |

| SENT2RX                           | I.          | —              | Yes     | SENT2 receive pin.                                                         |

| CVREF                             | 0           | Analog         | No      | Comparator Voltage Reference output.                                       |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | No      | Comparator 1 inputs.                                                       |

| C1OUT                             | 0           | _              | Yes     | Comparator 1 output.                                                       |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3- | I           | Analog         | No      | Comparator 2 inputs.                                                       |

| C2OUT                             | 0           | —              | Yes     | Comparator 2 output.                                                       |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3- | I           | Analog         | No      | Comparator 3 inputs.                                                       |

| C3OUT                             | 0           |                | Yes     | Comparator 3 output.                                                       |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3- | Ι           | Analog         | No      | Comparator 4 inputs.                                                       |

| C4OUT                             | 0           | —              | Yes     | Comparator 4 output.                                                       |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3- | I           | Analog         | No      | Comparator 5 inputs.                                                       |

| C5OUT                             | 0           | —              | Yes     | Comparator 5 output.                                                       |

| FLT1-FLT2                         | 1           | ST             | Yes     | PWM Fault Inputs 1 and 2.                                                  |

| FLT3-FLT8                         | 1           | ST             | NO      | PWM Fault Inputs 3 to 8.                                                   |

| FLT32                             | 1           | ST             | NO      | PWM Fault Input 32.                                                        |

| DTCMP1-DTCMP3                     | 1           | ST             | Yes     | PWM Dead-Time Compensation Inputs 1 to 3.                                  |

| PWM1L-PWM3L                       | 0           | _              | No      | PWM Low Outputs 1 to 3.                                                    |

| PWM1H-PWM3H                       | 0           | —              | No      | PWM High Outputs 1 to 3.                                                   |

| SYNCI1                            | 1           | ST             | Yes     | PWM Synchronization Input 1.                                               |

| SYNCO1                            | 0           | —              | Yes     | PWM Synchronization Output 1.                                              |

| PGED1                             | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.            |

| PGEC1                             | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1          |

| PGED2                             | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.            |

| PGEC2                             | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2          |

| PGED3                             | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.            |

| PGEC3                             | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel            |

| MCLR                              | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| Legend: CMOS = C                  |             |                |         | or output Analog = Analog input P = Power                                  |

| ST = Schm                         | itt Triaa   | er input w     | /ith CN | IOS levels O = Output I = Input                                            |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | 1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = Overflow has not occurred for signed arithmetic                                                                                                                                                          |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                              |

| Note 1. | The IPI <2:0> hits are concatenated with the IPI 3 hit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                      |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

| IABLE       | TABLE 4-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM006/106 DEVICES |        |        |         |         |         |         |         |         |       |       |         |         |         |         |         |         |               |

|-------------|-----------------------------------------------------------------------------------------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr.                                                                                   | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| RPOR0       | 0670                                                                                    | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | —     | —     | RP20R5  | RP20R4  | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672                                                                                    | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674                                                                                    | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676                                                                                    | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | _     | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678                                                                                    | —      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | _     |       | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR5       | 067A                                                                                    | —      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | _     |       | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR6       | 067C                                                                                    | —      | _      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | _     |       | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR7       | 067E                                                                                    | —      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     |       | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR8       | 0680                                                                                    | —      | _      | RP70R5  | RP70R4  | RP70R3  | RP70R2  | RP70R1  | RP70R0  | _     |       | RP69R5  | RP69R4  | RP69R3  | RP69R2  | RP69R1  | RP69R0  | 0000          |

| RPOR9       | 0682                                                                                    | —      | _      | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 | _     |       | RP97R5  | RP97R4  | RP97R3  | RP97R2  | RP97R1  | RP97R0  | 0000          |

| RPOR10      | 0684                                                                                    | —      | _      | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | _     |       | RP120R5 | RP120R4 | RP120R3 | RP120R2 | RP120R1 | RP120R0 | 0000          |

| RPOR11      | 0686                                                                                    | _      | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | _     |       | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688                                                                                    | —      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | —     |       | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A                                                                                    | —      | _      | _       | —       | _       | —       | _       | _       | —     |       |         |         | RP181   | R<5:0>  |         |         | 0000          |

#### TABLE 4-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM006/106 DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

|                   | VV VVIItable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

## REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

x = Bit is unknown

| U-0             | U-0 | U-0              | U-0   | U-0          | U-0              | U-0    | U-0   |

|-----------------|-----|------------------|-------|--------------|------------------|--------|-------|

| —               | —   | —                | —     | —            |                  | _      | —     |

| bit 15          |     |                  |       |              |                  |        | bit 8 |

|                 |     |                  |       |              |                  |        |       |

| R-0             | R-0 | R-0              | R-0   | R-0          | R-0              | R-0    | R-0   |

|                 |     |                  | DSADR | <23:16>      |                  |        |       |

| bit 7           |     |                  |       |              |                  |        | bit 0 |

|                 |     |                  |       |              |                  |        |       |

| Legend:         |     |                  |       |              |                  |        |       |

| R = Readable bi | it  | W = Writable bit |       | U = Unimpler | nented bit, read | as '0' |       |

'0' = Bit is cleared

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

'1' = Bit is set

## REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0               | R-0 | R-0              | R-0  | R-0                                     | R-0 | R-0 | R-0   |  |  |

|-------------------|-----|------------------|------|-----------------------------------------|-----|-----|-------|--|--|

|                   |     |                  | DSAI | DR<15:8>                                |     |     |       |  |  |

| bit 15            |     |                  |      |                                         |     |     | bit 8 |  |  |

|                   |     |                  |      |                                         |     |     |       |  |  |

| R-0               | R-0 | R-0              | R-0  | R-0                                     | R-0 | R-0 | R-0   |  |  |

|                   |     |                  | DSA  | DR<7:0>                                 |     |     |       |  |  |

| bit 7             |     |                  |      |                                         |     |     | bit 0 |  |  |

|                   |     |                  |      |                                         |     |     |       |  |  |

| Legend:           |     |                  |      |                                         |     |     |       |  |  |

| R = Readable bit  |     | W = Writable bit |      | U = Unimplemented bit, read as '0'      |     |     |       |  |  |

| -n = Value at POR | 2   | '1' = Bit is set |      | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

|                   |     |                  |      |                                         |     |     |       |  |  |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

- 6. The PPS pin mapping rules are as follows:

- Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin is disabled. Only the Analog Pin Select registers control the digital input buffer, not the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin; no exceptions.

# 21.2 UART Control Registers

## REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                     | DE: UARTx N                                                           |                                                             | TER                             |                                          |                  |                           |  |  |  |  |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|--|--|--|--|

| R/W-0                 | U-0                                                            | R/W-0                                                                 | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |  |  |  |  |

| UARTEN <sup>(1)</sup> |                                                                | USIDL                                                                 | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |  |  |  |  |

| bit 15                |                                                                |                                                                       |                                                             | ·                               |                                          |                  | bit 8                     |  |  |  |  |

| R/W-0, HC             | R/W-0                                                          | R/W-0, HC                                                             | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |  |  |  |  |

| WAKE                  | LPBACK                                                         | ABAUD                                                                 | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |  |  |  |  |

| bit 7                 |                                                                | 101100                                                                | Orodity                                                     | ыкоп                            | TDOLLI                                   | TDOLLO           | bit (                     |  |  |  |  |

|                       |                                                                |                                                                       |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| Legend:               |                                                                | HC = Hardwar                                                          | e Clearable bit                                             | t                               |                                          |                  |                           |  |  |  |  |

| R = Readable          | e bit                                                          | W = Writable I                                                        | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |  |  |  |  |

| -n = Value at         | POR                                                            | '1' = Bit is set                                                      |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |  |  |  |  |

| bit 15                | 1 = UARTx is                                                   | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U              | ARTx pins are                                               |                                 |                                          |                  |                           |  |  |  |  |

|                       | is minima                                                      |                                                                       |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 14                | •                                                              | ted: Read as '0                                                       |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 13                |                                                                | Tx Stop in Idle N                                                     |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       |                                                                | nues module op<br>es module opera                                     |                                                             |                                 | s Idle mode                              |                  |                           |  |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup>                                        | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup> |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       |                                                                | oder and decod                                                        |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 11                |                                                                | le Selection for                                                      |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       | 1 = UxRTS p                                                    | oin is in Simplex<br>oin is in Flow Co                                | mode                                                        |                                 |                                          |                  |                           |  |  |  |  |

| bit 10                |                                                                | ited: Read as '0                                                      |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 9-8               | -                                                              | IARTx Pin Enab                                                        |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                   | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a     | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |  |  |  |

| bit 7                 | WAKE: UAR                                                      | Tx Wake-up on                                                         | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |  |  |  |  |

|                       | in hardwa                                                      | ontinues to sam<br>are on the follow<br>is not enabled                |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |  |  |  |  |

| bit 6                 | -                                                              | RTx Loopback                                                          | Mode Select b                                               | it                              |                                          |                  |                           |  |  |  |  |

|                       |                                                                | k mode is enab                                                        |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       |                                                                | k mode is disab                                                       |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| "d:<br>tra            | efer to " <b>Univers</b><br>sPIC33/PIC24 F<br>insmit operation | amily Referenc                                                        | e <i>Manual"</i> for i                                      | nformation on e                 | enabling the U                           |                  |                           |  |  |  |  |

|                       | is feature is only                                             | -                                                                     |                                                             |                                 | )).                                      |                  |                           |  |  |  |  |

| <b>3:</b> Th          | is feature is only                                             | y available on 4                                                      | 4-pin and 64-p                                              | in devices.                     |                                          |                  |                           |  |  |  |  |

4: This feature is only available on 64-pin devices.

## REGISTER 22-8: CxEC: CANx TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0             | R-0 | R-0              | R-0  | R-0                  | R-0          | R-0             | R-0   |

|-----------------|-----|------------------|------|----------------------|--------------|-----------------|-------|

|                 |     |                  | TERR | CNT<7:0>             |              |                 |       |

| bit 15          |     |                  |      |                      |              |                 | bit 8 |

|                 |     |                  |      |                      |              |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                  | R-0          | R-0             | R-0   |

|                 |     |                  | RERR | CNT<7:0>             |              |                 |       |

| bit 7           |     |                  |      |                      |              |                 | bit 0 |

|                 |     |                  |      |                      |              |                 |       |

| Legend:         |     |                  |      |                      |              |                 |       |

| R = Readable I  | bit | W = Writable bi  | it   | U = Unimplemen       | ted bit, rea | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d            | x = Bit is unkr | nown  |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

## REGISTER 22-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0                 | U-0                                                                                                                                 | U-0                                                                                                                   | U-0                                                   | U-0          | U-0                                     | U-0           | U-0    |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|-----------------------------------------|---------------|--------|--|--|

| 0-0                 | 0-0                                                                                                                                 | 0-0                                                                                                                   | 0-0                                                   |              | 0-0                                     | 0-0           | 0-0    |  |  |

|                     |                                                                                                                                     |                                                                                                                       | _                                                     | _            |                                         |               |        |  |  |

| bit 15              |                                                                                                                                     |                                                                                                                       |                                                       |              |                                         |               | bit    |  |  |

|                     | 5444.6                                                                                                                              | 5.4.4.6                                                                                                               |                                                       |              | 54446                                   |               | 5444.6 |  |  |

| R/W-0               | R/W-0                                                                                                                               | R/W-0                                                                                                                 | R/W-0                                                 | R/W-0        | R/W-0                                   | R/W-0         | R/W-0  |  |  |

| SJW1                | SJW0                                                                                                                                | BRP5                                                                                                                  | BRP4                                                  | BRP3         | BRP2                                    | BRP1          | BRP0   |  |  |

| bit 7               |                                                                                                                                     |                                                                                                                       |                                                       |              |                                         |               | bit    |  |  |

|                     |                                                                                                                                     |                                                                                                                       |                                                       |              |                                         |               |        |  |  |

| Legend:             |                                                                                                                                     |                                                                                                                       |                                                       |              |                                         |               |        |  |  |

| R = Readable        | e bit                                                                                                                               | W = Writable                                                                                                          | bit                                                   | U = Unimplen | nented bit, read                        | <b>as</b> '0' |        |  |  |

| -n = Value at I     | POR                                                                                                                                 | -n = Value at POR '1' = Bit is set                                                                                    |                                                       |              | '0' = Bit is cleared x = Bit is unknown |               |        |  |  |

|                     | ••••                                                                                                                                | 1 Dit 10 001                                                                                                          | •                                                     |              |                                         |               |        |  |  |

|                     |                                                                                                                                     |                                                                                                                       | ·                                                     |              |                                         |               |        |  |  |

| bit 15-8            |                                                                                                                                     | ted: Read as '                                                                                                        |                                                       |              |                                         |               |        |  |  |

| bit 15-8<br>bit 7-6 | Unimplemen                                                                                                                          |                                                                                                                       | 0'                                                    | bits         |                                         |               | -      |  |  |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i                                                                                          | <b>ted:</b> Read as '<br>ynchronization<br>s 4 x Tq                                                                   | 0'                                                    | oits         |                                         |               | -      |  |  |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i                                                                         | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ                                                              | 0'                                                    | pits         |                                         |               |        |  |  |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i                                                        | ted: Read as '<br>ynchronization<br>s 4 x To<br>s 3 x To<br>s 2 x To                                                  | 0'                                                    | bits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i                                       | <b>ted:</b> Read as <sup>4</sup><br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 2 x TQ<br>s 1 x TQ       | 0'<br>I Jump Width I                                  | pits         |                                         |               | -      |  |  |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                        | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                        | <b>ted:</b> Read as <sup>4</sup><br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 2 x TQ<br>s 1 x TQ       | <sup>0'</sup><br>I Jump Width I<br>caler bits         | bits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                        | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                        | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B<br>11 1111 = T<br>•    | ted: Read as '<br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres<br>Q = 2 x 64 x 1/ | <sup>0'</sup><br>I Jump Width I<br>caler bits<br>FCAN | bits         |                                         |               | -      |  |  |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>00 = Length i<br>BRP<5:0>: B<br>11 1111 = T<br>•<br>•<br>00 0010 = T | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits<br>FCAN | bits         |                                         |               |        |  |  |

## 24.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the ADxCSSL/ADxCSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using the DMA peripheral.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1.c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADCxBUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUX A selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. For configuration examples, refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual".

| R/W-0         | U-0                                                                                                     | R/W-0                           | R/W-0                            | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|------------------|----------------------------------------|----------------|-------|--|--|--|

| HLMS          | 0-0                                                                                                     | OCEN                            | OCNEN                            | OBEN             | OBNEN                                  | OAEN           | OANEN |  |  |  |

|               |                                                                                                         | OCEN                            | OCINEIN                          | OBEN             | OBINEIN                                | UAEN           |       |  |  |  |

| bit 15        |                                                                                                         |                                 |                                  |                  |                                        |                | bit 8 |  |  |  |

| R/W-0         | R/W-0                                                                                                   | R/W-0                           | R/W-0                            | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |

| NAGS          | PAGS                                                                                                    | ACEN                            | ACNEN                            | ABEN             | ABNEN                                  | AAEN           | AANEN |  |  |  |

| bit 7         |                                                                                                         |                                 |                                  |                  |                                        |                | bit   |  |  |  |

|               |                                                                                                         |                                 |                                  |                  |                                        |                |       |  |  |  |

| Legend:       |                                                                                                         |                                 |                                  |                  |                                        |                |       |  |  |  |

| R = Readabl   | e bit                                                                                                   | W = Writable                    | bit                              | U = Unimple      | mented bit, read                       | <b>as</b> '0'  |       |  |  |  |

| -n = Value at | POR                                                                                                     | '1' = Bit is se                 | t                                | '0' = Bit is cle | eared                                  | x = Bit is unk | nown  |  |  |  |

| bit 15        | 1 = The mask                                                                                            | ing (blanking)                  |                                  | event any asse   | erted ('0') compa<br>erted ('1') compa |                |       |  |  |  |

| bit 14        | Unimplemen                                                                                              | ted: Read as                    | ·0'                              | -                |                                        | -              |       |  |  |  |

| bit 13        | OCEN: OR G                                                                                              | ate C Input E                   | nable bit                        |                  |                                        |                |       |  |  |  |

|               |                                                                                                         | nnected to OF                   | 0                                |                  |                                        |                |       |  |  |  |

| bit 12        |                                                                                                         |                                 | Inverted Enable                  | e bit            |                                        |                |       |  |  |  |

|               | 1 = Inverted I                                                                                          | MCI is connec                   | ted to OR gate                   |                  |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 | nected to OR g                   | jate             |                                        |                |       |  |  |  |

| bit 11        |                                                                                                         | ate B Input E                   |                                  |                  |                                        |                |       |  |  |  |

|               |                                                                                                         | nnected to OF<br>t connected to |                                  |                  |                                        |                |       |  |  |  |

| bit 10        | OBNEN: OR                                                                                               | Gate B Input                    | Inverted Enable                  | e bit            |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 | ted to OR gate<br>nected to OR g | ate              |                                        |                |       |  |  |  |

| bit 9         |                                                                                                         | ate A Input Ei                  | •                                |                  |                                        |                |       |  |  |  |

|               |                                                                                                         | nnected to OF                   | •                                |                  |                                        |                |       |  |  |  |

|               |                                                                                                         | t connected to                  | -                                |                  |                                        |                |       |  |  |  |

| bit 8         |                                                                                                         | •                               | Inverted Enable                  | e bit            |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 | ted to OR gate<br>nected to OR g | ate              |                                        |                |       |  |  |  |

| bit 7         | NAGS: AND                                                                                               | Gate Output I                   | nverted Enable                   | bit              |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 | cted to OR gate<br>nnected to OR |                  |                                        |                |       |  |  |  |

| bit 6         | <ul> <li>Inverted ANDI is not connected to OR gate</li> <li>PAGS: AND Gate Output Enable bit</li> </ul> |                                 |                                  |                  |                                        |                |       |  |  |  |

|               | 1 = ANDI is c                                                                                           | onnected to C<br>ot connected   | R gate                           |                  |                                        |                |       |  |  |  |

| bit 5         |                                                                                                         | Gate C Input I                  | -                                |                  |                                        |                |       |  |  |  |

|               | 1 = MCI is co                                                                                           | nnected to AN                   | ID gate                          |                  |                                        |                |       |  |  |  |

|               |                                                                                                         | t connected to                  | •                                |                  |                                        |                |       |  |  |  |

| bit 4         |                                                                                                         | -                               | t Inverted Enab                  |                  |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 | ted to AND gat<br>nected to AND  |                  |                                        |                |       |  |  |  |

|               |                                                                                                         |                                 |                                  |                  |                                        |                |       |  |  |  |

| R/W-0         | R/W-0                        | U-0                                                   | U-0                                | R/W-0                         | R/W-0            | U-0                | U-0        |

|---------------|------------------------------|-------------------------------------------------------|------------------------------------|-------------------------------|------------------|--------------------|------------|

| CVREN         | CVROE <sup>(1)</sup>         | _                                                     | _                                  | CVRSS                         | VREFSEL          | _                  | _          |

| bit 15        |                              |                                                       |                                    |                               |                  |                    | bit 8      |

| U-0           | R/W-0                        | R/W-0                                                 | R/W-0                              | R/W-0                         | R/W-0            | R/W-0              | R/W-0      |

| —             | CVR6                         | CVR5                                                  | CVR4                               | CVR3                          | CVR2             | CVR1               | CVR0       |

| bit 7         |                              |                                                       |                                    |                               |                  |                    | bit 0      |

| Legend:       |                              |                                                       |                                    |                               |                  |                    |            |

| R = Readable  | bit                          | W = Writable                                          | bit                                | U = Unimplei                  | mented bit, read | <b>as</b> '0'      |            |

| -n = Value at | POR                          | '1' = Bit is set                                      |                                    | '0' = Bit is cle              | eared            | x = Bit is unkr    | nown       |

| bit 15        | 1 = Comparat<br>0 = Comparat | parator Voltag<br>or voltage refe<br>or voltage refe  | rence circuit i<br>rence circuit i | s powered on<br>s powered dov |                  | (1)                |            |

| bit 14        | 1 = Voltage le               | parator Voltag<br>vel is output or<br>vel is disconne | n the CVREF2                       | o pin                         | (CVREF20 Pin)    | bit <sup>(1)</sup> |            |

| bit 13-12     | •                            | ted: Read as '                                        |                                    |                               |                  |                    |            |

| bit 11        | =                            | parator Voltag                                        |                                    | Source Selection              | on bit           |                    |            |

|               |                              | or reference so<br>or reference so                    |                                    |                               |                  |                    |            |

| bit 10        | VREFSEL: Vo                  | oltage Referen                                        | ce Select bit                      |                               |                  |                    |            |

|               | (CVR1CC                      | ON<10>) = 0                                           |                                    |                               | es inverting inp | -                  |            |

|               |                              | tor Reference<br>DN<10>) = 0                          | Source 1 (                         | CVR1) provide                 | es inverting inp | ut voltage wh      | en VREFSEL |

| bit 9-7       | Unimplemen                   | ted: Read as '                                        | 0'                                 |                               |                  |                    |            |

| bit 6-0       |                              | omparator Volt<br>27/128 x VREF                       | -                                  | e Value Select                | tion bits        |                    |            |

|               | •<br>0000000 = <b>0</b> .    | 0 volts                                               |                                    |                               |                  |                    |            |

| Note 1: CV    | ROE (CVR2CO                  |                                                       | available on t                     | he 28-pin devi                | ces.             |                    |            |

## REGISTER 26-2: CVR2CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 2

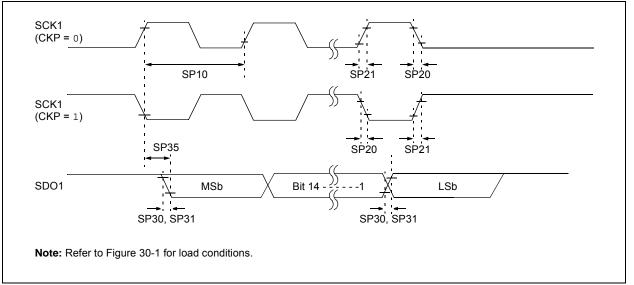

## TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS                                                                                      |             |                                            | Standard Operating<br>(unless otherwise<br>Operating temperation | <b>stated)</b><br>ure -40°C ≤ <sup>°</sup> | : <b>4.5V to 5.5V</b><br>TA ≤ +85°C for<br>TA ≤ +125°C fo |     |

|---------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------|------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------|-----|