Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm106-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:       PINOUT I/O DESCRIPTIONS (CONTINUED)                           |             |                |         |                                                                            |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------------|----------------|---------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Name                                                                       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                |  |  |  |  |  |  |  |

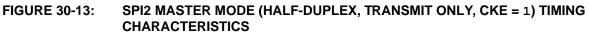

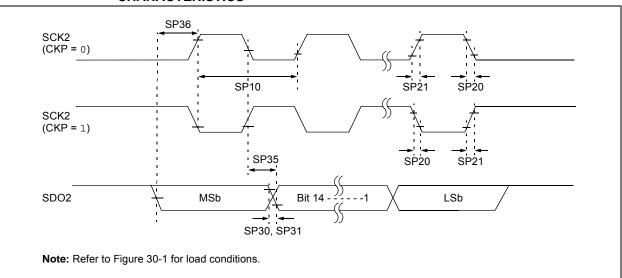

| SCK2                                                                           | I/O         | ST             | Yes     | Synchronous serial clock input/output for SPI2.                            |  |  |  |  |  |  |  |

| SDI2                                                                           | I           | ST             | Yes     | SPI2 data in.                                                              |  |  |  |  |  |  |  |

| SDO2                                                                           | 0           | —              | Yes     | SPI2 data out.                                                             |  |  |  |  |  |  |  |

| SS2                                                                            | I/O         | ST             | Yes     | SPI2 slave synchronization or frame pulse I/O.                             |  |  |  |  |  |  |  |

| SCL1                                                                           | I/O         | ST             | No      | Synchronous serial clock input/output for I2C1.                            |  |  |  |  |  |  |  |

| SDA1                                                                           | I/O         | ST             | No      | Synchronous serial data input/output for I2C1.                             |  |  |  |  |  |  |  |

| ASCL1                                                                          | I/O         | ST             | No      | Alternate synchronous serial clock input/output for I2C1.                  |  |  |  |  |  |  |  |

| ASDA1                                                                          | I/O         | ST             | No      | Alternate synchronous serial data input/output for I2C1.                   |  |  |  |  |  |  |  |

| C1RX                                                                           | I.          | ST             | Yes     | CAN1 bus receive pin.                                                      |  |  |  |  |  |  |  |

| C1TX                                                                           | 0           | —              | Yes     | CAN1 bus transmit pin.                                                     |  |  |  |  |  |  |  |

| SENT1TX                                                                        | 0           | —              | Yes     | SENT1 transmit pin.                                                        |  |  |  |  |  |  |  |

| SENT1RX                                                                        | 1           | —              | Yes     | SENT1 receive pin.                                                         |  |  |  |  |  |  |  |

| SENT2TX                                                                        | 0           | —              | Yes     | SENT2 transmit pin.                                                        |  |  |  |  |  |  |  |

| SENT2RX                                                                        | I.          | —              | Yes     | SENT2 receive pin.                                                         |  |  |  |  |  |  |  |

| CVREF                                                                          | 0           | Analog         | No      | Comparator Voltage Reference output.                                       |  |  |  |  |  |  |  |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3-                                              | I           | Analog         | No      | Comparator 1 inputs.                                                       |  |  |  |  |  |  |  |

| C1OUT                                                                          | 0           | _              | Yes     | Comparator 1 output.                                                       |  |  |  |  |  |  |  |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3-                                              | I           | Analog         | No      | Comparator 2 inputs.                                                       |  |  |  |  |  |  |  |

| C2OUT 0 -                                                                      |             |                |         | Comparator 2 output.                                                       |  |  |  |  |  |  |  |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3-                                              | I           | Analog         | No      | Comparator 3 inputs.                                                       |  |  |  |  |  |  |  |

| C3OUT                                                                          | 0           |                | Yes     | Comparator 3 output.                                                       |  |  |  |  |  |  |  |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3-                                              | Ι           | Analog         | No      | Comparator 4 inputs.                                                       |  |  |  |  |  |  |  |

| C4OUT                                                                          | 0           | —              | Yes     | Comparator 4 output.                                                       |  |  |  |  |  |  |  |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3-                                              | I           | Analog         | No      | Comparator 5 inputs.                                                       |  |  |  |  |  |  |  |

| C5OUT                                                                          | 0           | —              | Yes     | Comparator 5 output.                                                       |  |  |  |  |  |  |  |

| FLT1-FLT2                                                                      | 1           | ST             | Yes     | PWM Fault Inputs 1 and 2.                                                  |  |  |  |  |  |  |  |

| FLT3-FLT8                                                                      | 1           | ST             | NO      | PWM Fault Inputs 3 to 8.                                                   |  |  |  |  |  |  |  |

| FLT32                                                                          | 1           | ST             | NO      | PWM Fault Input 32.                                                        |  |  |  |  |  |  |  |

| DTCMP1-DTCMP3                                                                  | 1           | ST             | Yes     | PWM Dead-Time Compensation Inputs 1 to 3.                                  |  |  |  |  |  |  |  |

| PWM1L-PWM3L                                                                    | 0           | _              | No      | PWM Low Outputs 1 to 3.                                                    |  |  |  |  |  |  |  |

| PWM1H-PWM3H                                                                    | 0           | —              | No      | PWM High Outputs 1 to 3.                                                   |  |  |  |  |  |  |  |

| SYNCI1                                                                         | 1           | ST             | Yes     | PWM Synchronization Input 1.                                               |  |  |  |  |  |  |  |

| SYNCO1                                                                         | 0           | —              | Yes     | PWM Synchronization Output 1.                                              |  |  |  |  |  |  |  |

| PGED1                                                                          | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.            |  |  |  |  |  |  |  |

| PGEC1                                                                          | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1          |  |  |  |  |  |  |  |

| PGED2                                                                          | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.            |  |  |  |  |  |  |  |

| PGEC2                                                                          | 1           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2          |  |  |  |  |  |  |  |

| PGED3 I/O ST No Data I/O pin for Programming/Debugging Communication Channel 3 |             |                |         |                                                                            |  |  |  |  |  |  |  |

| PGEC3                                                                          | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel            |  |  |  |  |  |  |  |

| MCLR                                                                           | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |  |  |  |  |  |  |

| Legend: CMOS = C                                                               |             |                |         | or output Analog = Analog input P = Power                                  |  |  |  |  |  |  |  |

| ST = Schm                                                                      | itt Triaa   | er input w     | /ith CN | IOS levels O = Output I = Input                                            |  |  |  |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | 1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

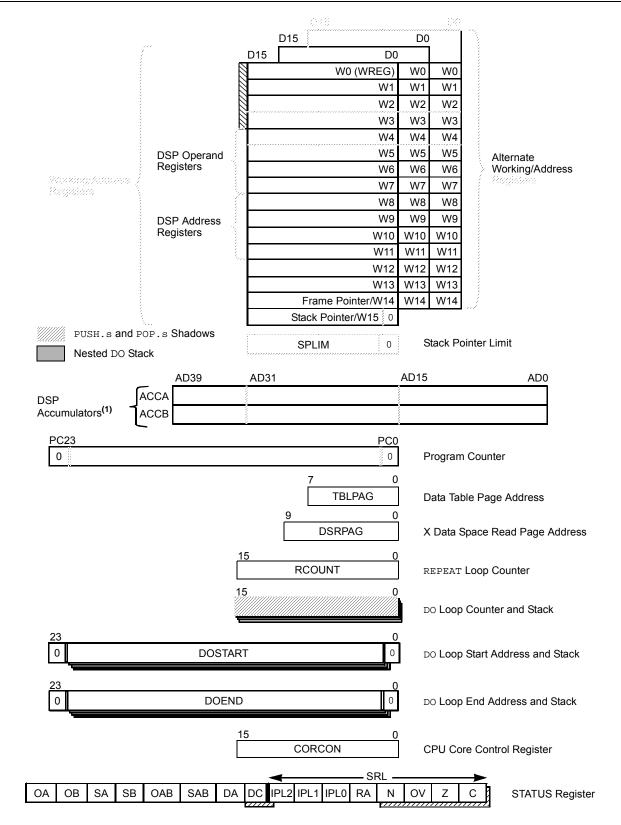

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

### 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

### FIGURE 3-2: PROGRAMMER'S MODEL

| -                          | GOTO Instruction                                     | 0x000000                         |  |

|----------------------------|------------------------------------------------------|----------------------------------|--|

|                            | Reset Address                                        | 0x000002                         |  |

|                            | Interrupt Vector Table                               | 0x000004<br>0x0001FE<br>0x000200 |  |

| Space                      | User Program<br>Flash Memory<br>(44736 instructions) | 0x000200<br>0x01577E<br>0x015780 |  |

| User Memory Space          | Device Configuration                                 | 0x015780<br>0x0157FE<br>0x015800 |  |

| C                          | Unimplemented<br>(Read '0's)                         |                                  |  |

|                            | Executive Code Memory                                | 0x7FFFE<br>0x800000<br>0x800BFE  |  |

|                            | Reserved                                             | 0x800C00<br>0x800F80             |  |

| ø                          | User OTP Memory                                      | 0x800FFE                         |  |

| ory Spac                   | Reserved                                             | 0x801000                         |  |

| on Mem                     | Write Latches                                        | 0xF9FFFE<br>0xFA0000<br>0xFA0002 |  |

| Configuration Memory Space | Reserved                                             | 0xFA0004                         |  |

|                            | DEVID                                                | 0xFEFFFE<br>0xFF0000<br>0xFF0002 |  |

| ,                          | Reserved                                             | 0xFF0004<br>0xFFFFFE             |  |

| TABLE       | ABLE 4-23: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES (CONTINUED) |        |          |          |          |         |           |            |           |          |          |             |          |         |           |             |           |               |

|-------------|---------------------------------------------------------------------------------------------------|--------|----------|----------|----------|---------|-----------|------------|-----------|----------|----------|-------------|----------|---------|-----------|-------------|-----------|---------------|

| SFR<br>Name | Addr.                                                                                             | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10    | Bit 9      | Bit 8     | Bit 7    | Bit 6    | Bit 5       | Bit 4    | Bit 3   | Bit 2     | Bit 1       | Bit 0     | All<br>Resets |

| IPC19       | 0866                                                                                              | -      | —        | —        | -        | —       | —         | —          | —         | —        |          | CTMUIP<2:0> | •        | _       | —         | —           | —         | 0040          |

| IPC23       | 086E                                                                                              | _      | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2   | PWM1IP1    | PWM1IP0   | _        | _        | _           | _        | _       | _         | _           | _         | 4400          |

| IPC24       | 0870                                                                                              | _      | _        | _        | _        | _       | _         | _          | _         | _        | _        | _           | _        | _       |           | PWM3IP<2:0> | •         | 0004          |

| IPC35       | 0886                                                                                              | _      | _        | _        | _        | _       |           | ICDIP<2:0> |           | _        | _        | _           | _        | _       | _         | _           | _         | 0400          |

| IPC43       | 0896                                                                                              | _      | _        | _        | _        | _       | _         | _          | _         | _        | l        | 2C1BCIP<2:0 | >        | _       | _         | _           | _         | 0040          |

| IPC45       | 089A                                                                                              | _      | SENT1IP2 | SENT1IP1 | SENT1IP0 | _       | SENT1EIP2 | SENT1EIP1  | SENT1EIP0 | _        | _        | _           | _        | _       | _         | _           | _         | 4400          |

| IPC46       | 089C                                                                                              | _      | _        | _        | _        | _       | ECCSBEIP2 | ECCSBEIP1  | ECCSBEIP0 | _        | SENT2IP2 | SENT2IP1    | SENT2IP0 | _       | SENT2EIP2 | SENT2EIP1   | SENT2EIP0 | 0444          |

| INTCON1     | 08C0                                                                                              | NSTDIS | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE     | OVBTE      | COVTE     | SFTACERR | DIV0ERR  | DMACERR     | MATHERR  | ADDRERR | STKERR    | OSCFAIL     | _         | 0000          |

| INTCON2     | 08C2                                                                                              | GIE    | DISI     | SWTRAP   | _        | _       | _         | _          | AIVTEN    | _        | _        | _           | _        | _       | INT2EP    | INT1EP      | INT0EP    | 0000          |

| INTCON3     | 08C4                                                                                              | DMT    | —        | —        | —        | —       | —         | —          | —         | —        | —        | DAE         | DOOVR    | _       | —         | —           | —         | 0000          |

| INTCON4     | 08C6                                                                                              | _      | —        | —        | —        | —       | —         | —          | —         | —        | —        | _           | —        | _       | —         | ECCDBE      | SGHT      | 0000          |

| INTTREG     | 08C8                                                                                              | _      | _        | _        | _        | _       | ILR3      | ILR2       | ILR1      | VECNUM7  | VECNUM6  | VECNUM5     | VECNUM4  | VECNUM3 | VECNUM2   | VECNUM1     | VECNUM0   | 0000          |

Legend: — = unimplemented, read as '0' Reset values are shown in hexadecimal. Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

# 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                                 | R/W-0                          | U-0             | U-0              | U-0                       | U-0                | U-0         |

|--------------------|-------------------------------------|--------------------------------|-----------------|------------------|---------------------------|--------------------|-------------|

| TON <sup>(1)</sup> | —                                   | TSIDL                          | —               | —                | _                         | —                  | —           |

| bit 15             |                                     |                                |                 |                  |                           |                    | bit 8       |

|                    |                                     |                                |                 |                  |                           |                    |             |

| U-0                | R/W-0                               | R/W-0                          | R/W-0           | U-0              | R/W-0                     | R/W-0              | U-0         |

|                    | TGATE                               | TCKPS1                         | TCKPS0          | —                | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |

| bit 7              |                                     |                                |                 |                  |                           |                    | bit 0       |

|                    |                                     |                                |                 |                  |                           |                    |             |

| Legend:            |                                     |                                |                 |                  |                           |                    |             |

| R = Readable       |                                     | W = Writable                   |                 | -                | mented bit, read          |                    |             |

| -n = Value at F    | POR                                 | '1' = Bit is set               |                 | '0' = Bit is cle | ared                      | x = Bit is unkr    | nown        |

|                    |                                     | o                              |                 |                  |                           |                    |             |

| bit 15             | TON: Timer1                         |                                |                 |                  |                           |                    |             |

|                    | 1 = Starts 16-<br>0 = Stops 16-     |                                |                 |                  |                           |                    |             |

| bit 14             | •                                   | ted: Read as '                 | י)              |                  |                           |                    |             |

| bit 13             | -                                   | 1 Stop in Idle N               |                 |                  |                           |                    |             |

| 2.1.10             |                                     | ues module op                  |                 | he device ente   | ers Idle mode             |                    |             |

|                    | 0 = Continues                       | s module opera                 | tion in Idle mo | ode              |                           |                    |             |

| bit 12-7           | Unimplemen                          | ted: Read as '                 | כי              |                  |                           |                    |             |

| bit 6              | TGATE: Time                         | r1 Gated Time                  | Accumulation    | Enable bit       |                           |                    |             |

|                    | When TCS =<br>This bit is igno      |                                |                 |                  |                           |                    |             |

|                    | When TCS =                          |                                |                 |                  |                           |                    |             |

|                    |                                     | e accumulation                 |                 |                  |                           |                    |             |

| bit 5-4            |                                     | e accumulation                 |                 | a Salaat hita    |                           |                    |             |

| DIL 3-4            | 11 = 1:256                          | : Timer1 Input                 |                 |                  |                           |                    |             |

|                    | 10 = 1:64                           |                                |                 |                  |                           |                    |             |

|                    | 01 = 1:8                            |                                |                 |                  |                           |                    |             |

|                    | 00 = 1:1                            |                                |                 |                  |                           |                    |             |

| bit 3              | -                                   | ted: Read as '                 |                 |                  | (1)                       |                    |             |

| bit 2              |                                     | er1 External Clo               | ock Input Synd  | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |

|                    | <u>When TCS =</u><br>1 = External c | <u>1:</u><br>clock input is sy | nchronized      |                  |                           |                    |             |

|                    |                                     | clock input is n               |                 | d                |                           |                    |             |

|                    | When TCS =                          | =                              | ,               |                  |                           |                    |             |

|                    | This bit is igno                    |                                |                 |                  |                           |                    |             |

| bit 1              |                                     | Clock Source S                 |                 |                  |                           |                    |             |

|                    | 1 = External c<br>0 = Internal cl   | clock is from pii<br>lock (FP) | n, T1CK (on th  | ne rising edge)  |                           |                    |             |

| bit 0              | Unimplemen                          | ted: Read as '                 | כי              |                  |                           |                    |             |

|                    | en Timer1 is en<br>mpts by user se  |                                |                 |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |

# 15.1 Input Capture Control Registers

## REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER     | 15-1: ICxCO                                                                                                                        | N1: INPUT C      | CAPTURE x CO                            | ONTROL REG           | ISTER 1          |                 |              |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|----------------------|------------------|-----------------|--------------|--|--|--|--|

| U-0          | U-0                                                                                                                                | R/W-0            | R/W-0                                   | R/W-0                | R/W-0            | U-0             | U-0          |  |  |  |  |

| _            |                                                                                                                                    | ICSIDL           | ICTSEL2                                 | ICTSEL1              | ICTSEL0          | —               | _            |  |  |  |  |

| bit 15       |                                                                                                                                    | •                |                                         |                      |                  |                 | bit          |  |  |  |  |

| U-0          | R/W-0                                                                                                                              | R/W-0            | R-0, HC, HS                             | R-0, HC, HS          | R/W-0            | R/W-0           | R/W-0        |  |  |  |  |

| _            | ICI1                                                                                                                               | ICI0             | ICOV                                    | ICBNE                | ICM2             | ICM1            | ICM0         |  |  |  |  |

| bit 7        |                                                                                                                                    |                  |                                         |                      |                  |                 | bit          |  |  |  |  |

| Legend:      |                                                                                                                                    | HC = Hardwa      | re Clearable bit                        | HS = Hardwar         | re Settable bit  |                 |              |  |  |  |  |

| R = Readab   | le bit                                                                                                                             | W = Writable     | bit                                     | U = Unimplem         | nented bit, read | <b>l as</b> '0' |              |  |  |  |  |

| -n = Value a | t POR                                                                                                                              | '1' = Bit is set |                                         | '0' = Bit is clea    | ared             | x = Bit is un   | known        |  |  |  |  |

| bit 15-14    | Unimplemen                                                                                                                         | ted: Read as '   | 0'                                      |                      |                  |                 |              |  |  |  |  |

| bit 13       | -                                                                                                                                  |                  | p in Idle Mode C                        | control bit          |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    | -                | t in CPU Idle mod                       |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    | -                | tinue to operate                        |                      | de               |                 |              |  |  |  |  |

| bit 12-10    |                                                                                                                                    |                  | e x Timer Select                        |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | is the clock sour                       | ce of the ICx        |                  |                 |              |  |  |  |  |

|              | 110 = Reserv                                                                                                                       |                  |                                         |                      |                  |                 |              |  |  |  |  |

|              | 101 = Reserv                                                                                                                       |                  | ource of the ICx (                      | only the synchr      | onous clock is   | supported)      |              |  |  |  |  |

|              | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx |                  |                                         |                      |                  |                 |              |  |  |  |  |

|              | 010 = T4CLK is the clock source of the ICx                                                                                         |                  |                                         |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | ource of the ICx                        |                      |                  |                 |              |  |  |  |  |

| bit 9-7      |                                                                                                                                    | ted: Read as '   |                                         |                      |                  |                 |              |  |  |  |  |

| bit 6-5      | ICI<1:0>: Nur                                                                                                                      | mber of Captur   | es per Interrupt S                      | Select bits (this fi | eld is not used  | if ICM<2:0> =   | 001 or 111   |  |  |  |  |

|              | 11 = Interrupt                                                                                                                     | t on every four  | th capture event                        |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | l capture event                         |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | ond capture ever                        | nt                   |                  |                 |              |  |  |  |  |

|              | -                                                                                                                                  | t on every cap   |                                         |                      |                  |                 |              |  |  |  |  |

| bit 4        | -                                                                                                                                  | -                | flow Status Flag                        |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | overflow has occu                       |                      |                  |                 |              |  |  |  |  |

| bit 3        |                                                                                                                                    | -                | fer Not Empty St                        |                      | nlv)             |                 |              |  |  |  |  |

|              | -                                                                                                                                  | -                | s not empty, at le                      | -                    | • •              | an be read      |              |  |  |  |  |

|              |                                                                                                                                    | pture x buffer i |                                         |                      |                  |                 |              |  |  |  |  |

| bit 2-0      | ICM<2:0>: In                                                                                                                       | put Capture x    | Mode Select bits                        |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | tions as an inter                       |                      | CPU Sleep an     | d Idle modes    | (rising edg  |  |  |  |  |

|              |                                                                                                                                    |                  | control bits are r                      | ot applicable)       |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    | ed (module is d  | ,                                       |                      | nturo modo)      |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | / 16th rising edge<br>/ 4th rising edge |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | / rising edge (Sir                      |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    |                  | / falling edge (Si                      |                      |                  |                 |              |  |  |  |  |

|              |                                                                                                                                    | re mode, every   | edge, rising and                        |                      |                  | CI<1:0>) is not | t used in th |  |  |  |  |

|              | ,                                                                                                                                  |                  | ule is turned off                       |                      |                  |                 |              |  |  |  |  |

000 = Input Capture x module is turned off

# REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1 (CONTINUED)

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                                                                                                                                                                                              |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                                                                                                                                                                                      |

|         | In I <sup>2</sup> C Slave mode only, used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                                                                                                                                                                                            |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                                                                                                                                                                                               |

|         | In I <sup>2</sup> C Master mode, during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.<br>In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent<br>0 = ACK is sent |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                                                                                                                                                                                                |

| bit 3   | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C, automatically cleared by hardware at the end of 8-bit receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                                                                                                                                                 |

| bit 2   | PEN: Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                                |

| bit 1   | RSEN: Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                          |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                              |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                                                                                                                                                                                          |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

| R/W-0           | R/W-0                                                        | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------------------|------------------|-----------------|---------|

| F15MSK1         | F15MSK0                                                      | F14MSK1                                            | F14MSK0                                               | F13MSK'                          | F13MSK0          | F12MSK1         | F12MSK0 |

| bit 15          |                                                              |                                                    |                                                       |                                  |                  |                 | bit 8   |

| R/W-0           | R/W-0                                                        | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0           | R/W-0   |

| F11MSK1         | F11MSK0                                                      | F10MSK1                                            | F10MSK0                                               | F9MSK1                           | F9MSK0           | F8MSK1          | F8MSK0  |

| bit 7           |                                                              |                                                    |                                                       |                                  |                  | 1               | bit (   |

| Legend:         |                                                              |                                                    |                                                       |                                  |                  |                 |         |

| R = Readable    | bit                                                          | W = Writable                                       | bit                                                   | U = Unimpler                     | mented bit, read | <b>l as</b> '0' |         |

| -n = Value at I | POR                                                          | '1' = Bit is set                                   |                                                       | '0' = Bit is cle                 | ared             | x = Bit is unkr | nown    |

| bit 15-14       | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta | nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg | gisters contain<br>gisters contain<br>gisters contain | the mask<br>the mask<br>the mask |                  |                 |         |

| bit 13-12       |                                                              |                                                    |                                                       | ,                                | es as bits 15-14 | ,               |         |

| bit 11-10       |                                                              |                                                    |                                                       | -                                | es as bits 15-14 |                 |         |

| bit 9-8         |                                                              |                                                    |                                                       |                                  | es as bits 15-14 |                 |         |

| bit 7-6         |                                                              |                                                    |                                                       | -                                | es as bits 15-14 | -               |         |

| bit 5-4         | F10MSK<1:0                                                   | >: Mask Sourc                                      | e for Filter 10                                       | bit (same valu                   | es as bits 15-14 | +)              |         |

| bit 3-2         | F9MSK<1:0>                                                   | : Mask Source                                      | for Filter 9 bit                                      | (same values                     | as bits 15-14)   |                 |         |

|                 |                                                              |                                                    |                                                       |                                  |                  |                 |         |

## REGISTER 22-19: CxFMSKSEL2: CANx FILTERS 15-8 MASK SELECTION REGISTER 2

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bits 15-14)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|----------------|-------|

|                 |       |                  | CSS   | <15:8>           |                 |                |       |

| bit 15          |       |                  |       |                  |                 |                | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|                 |       |                  | CSS   | <7:0>            |                 |                |       |

| bit 7           |       |                  |       |                  |                 |                | bit C |

| Legend:         |       |                  |       |                  |                 |                |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | nented bit, rea | ad as '0'      |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

bit 15-0 CSS<15:0>: ADCx Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

**2:** CSSx = ANx, where 'x' = 0-5.

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT **CONTROL REGISTER**

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | _   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| <b>s</b> '0' |

|--------------|

| ;            |

| bit 15-12 | Unimplemented: Read as '0'             |

|-----------|----------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits |

|           | 1111 <b>= FLT4</b>                     |

|           | 1110 = FLT2                            |

|           | 1101 = Reserved                        |

|           | 1100 = Reserved                        |

|           | 1011 = Reserved                        |

|           | 1010 = Reserved                        |

|           | 1001 = Reserved                        |

|           | 1000 = Reserved                        |

|           | 0111 = Reserved<br>0110 = Reserved     |

|           | 0110 = Reserved<br>0101 = PWM3H        |

|           | 0100 = PWM3L                           |

|           | 0011 = PWM2H                           |

|           | 0010 = PWM2L                           |

|           | 0001 = PWM1H                           |

|           | 0000 = PWM1L                           |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits |

|           | 1111 <b>= FLT4</b>                     |

|           | 1110 = FLT2                            |

|           | 1101 = Reserved                        |

|           | 1100 = Reserved                        |

|           | 1011 = Reserved                        |

|           | 1010 = Reserved                        |

|           | 1001 = Reserved                        |

|           | 1000 = Reserved<br>0111 = Reserved     |

|           | 0111 - Reserved                        |

|           | 0110 = PWM3H                           |

|           | 0100 = PWM3L                           |

|           | 0011 = PWM2H                           |

|           | 0010 = PWM2L                           |

|           | 0001 = PWM1H                           |

|           | 0000 = PWM1L                           |

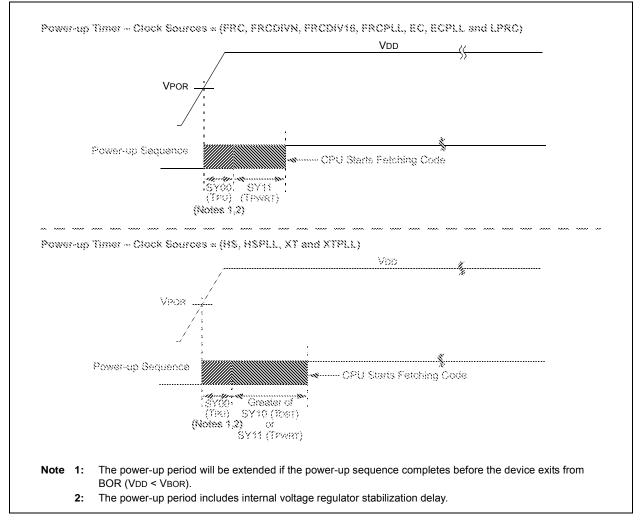

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                                 |  |  |

|--------------------|-----------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                                                                                              | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                      |  |  |

| SY00               | Tpu       | Power-up Period                                                   | _                                                                                                                                                                                                                                                                                 | 400                 | 600  | μs    |                                                                                                                 |  |  |

| SY10               | Tost      | Oscillator Start-up<br>Time                                       | —                                                                                                                                                                                                                                                                                 | 1024 Tos<br>C       | —    | —     | Tosc = OSC1 period                                                                                              |  |  |

| SY11               | TPWRT     | Power-up Timer<br>Period                                          | —                                                                                                                                                                                                                                                                                 | 1                   | —    | ms    | Using LPRC parameters indicated in F21a/F21b (see Table 30-20)                                                  |  |  |

| SY12               | Тwdt      | Watchdog Timer<br>Time-out Period                                 | 0.8                                                                                                                                                                                                                                                                               | _                   | 1.2  | ms    | WDTPRE = 0, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |  |

|                    |           |                                                                   | 3.2                                                                                                                                                                                                                                                                               | _                   | 4.8  | ms    | WDTPRE = 1, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer<br>Reset | 0.68                                                                                                                                                                                                                                                                              | 0.72                | 1.2  | μs    |                                                                                                                 |  |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                            | 2                                                                                                                                                                                                                                                                                 | —                   | -    | μs    |                                                                                                                 |  |  |

| SY30               | TBOR      | BOR Pulse Width<br>(low)                                          | 1                                                                                                                                                                                                                                                                                 | —                   | _    | ms    |                                                                                                                 |  |  |

| SY35               | TFSCM     | Fail-Safe Clock<br>Monitor Delay                                  | —                                                                                                                                                                                                                                                                                 | 500                 | 900  | μs    | -40°C to +85°C                                                                                                  |  |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active<br>mode Transition Time    | —                                                                                                                                                                                                                                                                                 | _                   | 30   | μs    |                                                                                                                 |  |  |

| SY37               | TOSCDFRC  | FRC Oscillator<br>Start-up Delay                                  | 46                                                                                                                                                                                                                                                                                | 48                  | 54   | μs    |                                                                                                                 |  |  |

| SY38               | TOSCDLPRC | LPRC Oscillator<br>Start-up Delay                                 | —                                                                                                                                                                                                                                                                                 | —                   | 70   | μs    |                                                                                                                 |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

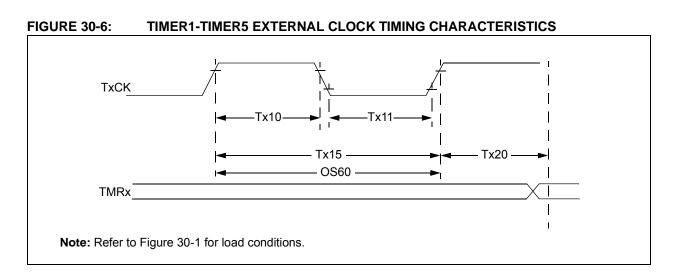

| AC CHARACTERISTICS |           |                                                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                                |

|--------------------|-----------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|--------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Charao                                                                                            | cteristic <sup>(2)</sup>                                                                                                                                                                                                                                                              | Min.                                   | Тур. | Max.          | Units | Conditions                                                                     |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                 | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |

|                    |           |                                                                                                   | Asynchronous mode                                                                                                                                                                                                                                                                     | 35                                     | —    | _             | ns    |                                                                                |

| TA11               | ΤτxL      | T1CK Low<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   | _    |               | ns    | Must also meet<br>Parameter TA15,<br>N = Prescaler<br>Value (1, 8, 64,<br>256) |

|                    |           |                                                                                                   | Asynchronous mode                                                                                                                                                                                                                                                                     | 10                                     | _    | _             | ns    |                                                                                |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                              | Synchronous<br>mode                                                                                                                                                                                                                                                                   | Greater of:<br>40 or<br>(2 Tcy + 40)/N | —    | —             | ns    | N = Prescaler<br>Value<br>(1, 8, 64, 256)                                      |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting TCS<br>(T1CON<1>) bit) |                                                                                                                                                                                                                                                                                       | DC                                     | _    | 50            | kHz   |                                                                                |

| TA20               | TCKEXTMRL |                                                                                                   |                                                                                                                                                                                                                                                                                       | 0.75 Tcy + 40                          |      | 1.75 Tcy + 40 | ns    |                                                                                |

# TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Timer1 is a Type A.

**2:** These parameters are characterized but not tested in manufacturing.

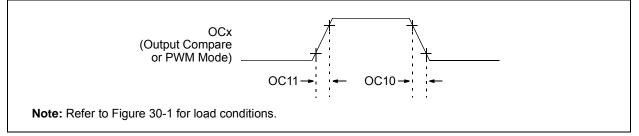

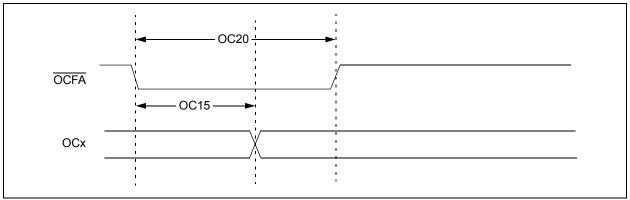

### FIGURE 30-8: OUTPUT COMPARE x (OCx) TIMING CHARACTERISTICS

### TABLE 30-27: OUTPUT COMPARE x (OCx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|