Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm106t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                               |     |

|-------|-------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers         | 17  |

| 3.0   | CPU                                                                           |     |

| 4.0   | Memory Organization                                                           |     |

| 5.0   | Flash Program Memory                                                          | 83  |

| 6.0   | Resets                                                                        |     |

| 7.0   | Interrupt Controller                                                          |     |

| 8.0   | Direct Memory Access (DMA)                                                    | 109 |

| 9.0   | Oscillator Configuration                                                      | 123 |

| 10.0  | Power-Saving Features                                                         | 133 |

| 11.0  | I/O Ports                                                                     | 143 |

| 12.0  | Timer1                                                                        | 173 |

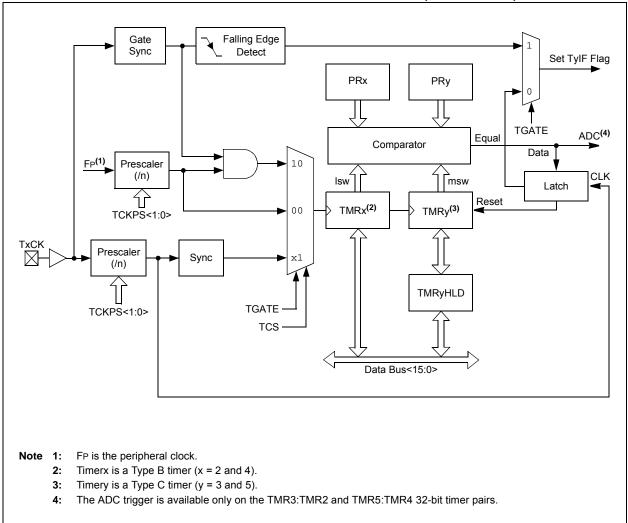

| 13.0  | Timer2/3 and Timer4/5                                                         | 175 |

| 14.0  | Deadman Timer (DMT)                                                           | 181 |

| 15.0  | Input Capture                                                                 | 189 |

| 16.0  | Output Compare                                                                | 193 |

| 17.0  | High-Speed PWM Module                                                         | 199 |

| 18.0  |                                                                               | 221 |

| 19.0  |                                                                               |     |

| 20.0  | Single-Edge Nibble Transmission (SENT)                                        | 237 |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART)                            |     |

| 22.0  | Controller Area Network (CAN) Module (dsPIC33EVXXXGM10X Devices Only)         | 253 |

| 23.0  | Charge Time Measurement Unit (CTMU)                                           | 279 |

| 24.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                               |     |

| 25.0  | Op Amp/Comparator Module                                                      | 301 |

| 26.0  | Comparator Voltage Reference                                                  | 313 |

|       | Special Features                                                              |     |

| 28.0  | Instruction Set Summary                                                       | 327 |

| 29.0  |                                                                               |     |

|       |                                                                               |     |

|       | High-Temperature Electrical Characteristics                                   |     |

|       | Characteristics for Industrial/Extended Temperature Devices (-40°C to +125°C) |     |

| 33.0  | Characteristics for High-Temperature Devices (+150°C)                         | 439 |

|       | Packaging Information                                                         |     |

|       | endix A: Revision History                                                     |     |

|       | Χ                                                                             |     |

|       | Microchip Web Site                                                            |     |

|       | omer Change Notification Service                                              |     |

|       | omer Support                                                                  |     |

| Produ | luct Identification System                                                    | 497 |

#### 4.3.1 PAGED MEMORY SCHEME

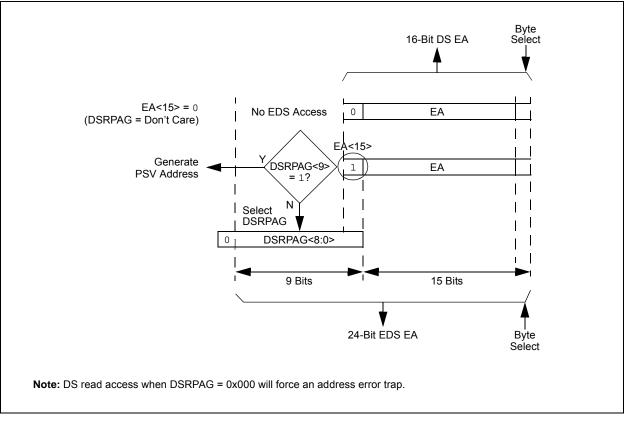

The dsPIC33EVXXXGM00X/10X family architecture extends the available DS through a paging scheme, which allows the available DS to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the Base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Data Space Read Page register (DSRPAG) or the 9-bit Data Space Write Page register (DSWPAG), to form an EDS address, or Program Space Visibility (PSV) address.

The Data Space Page registers are located in the SFR space. Construction of the EDS address is shown in Figure 4-9 and Figure 4-10. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS write address.

#### FIGURE 4-9: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

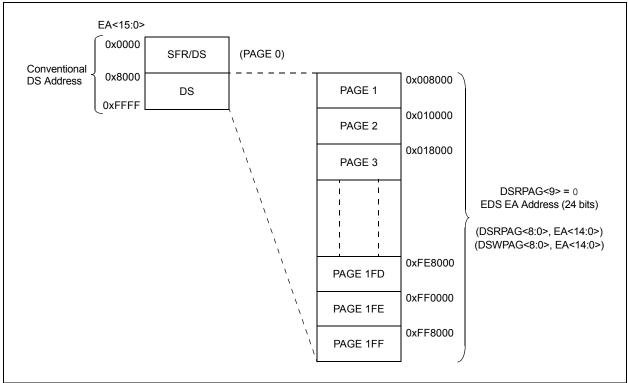

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

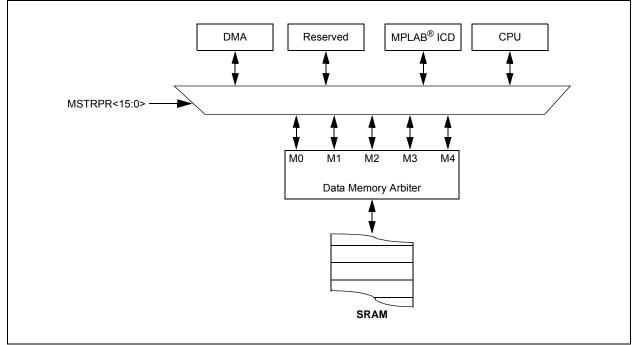

# 4.3.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the MPLAB<sup>®</sup> ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the MPLAB ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities

below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are listed in Table 4-44.

Figure 4-13 shows the arbiter architecture.

The bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

# TABLE 4-44:DATA MEMORY BUS<br/>ARBITER PRIORITY

| Driarity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |           |  |  |  |  |

|--------------|-----------------------------------------|-----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020    |  |  |  |  |

| M0 (highest) | CPU                                     | DMA       |  |  |  |  |

| M1           | Reserved                                | CPU       |  |  |  |  |

| M2           | Reserved                                | Reserved  |  |  |  |  |

| M3           | DMA                                     | Reserved  |  |  |  |  |

| M4 (lowest)  | MPLAB <sup>®</sup> ICD                  | MPLAB ICD |  |  |  |  |

Note 1: All other values of MSTRPR<15:0> are reserved.

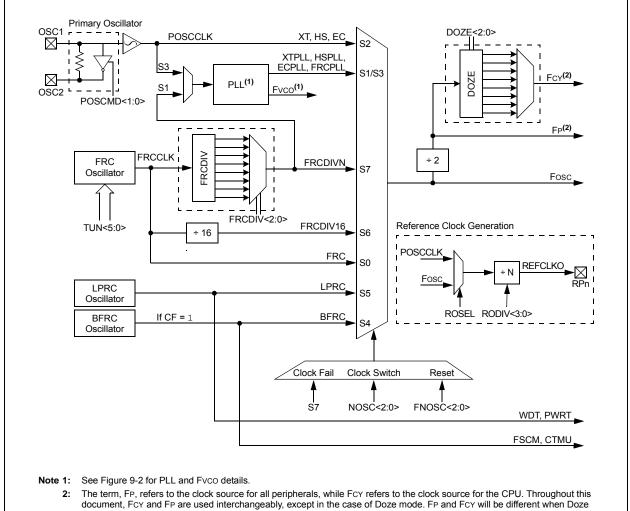

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

**OSCILLATOR SYSTEM DIAGRAM**

FIGURE 9-1:

The dsPIC33EVXXXGM00X/10X family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- · Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown.

- Backup FRC (BFRC) Function that Provides a System Clock when there is a Failure in the FRC Clock

- Configuration bits for Clock Source Selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

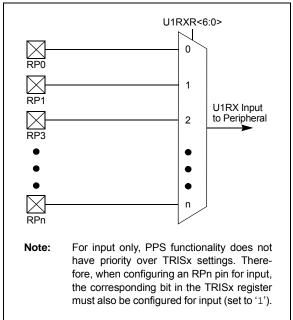

For example, Figure 11-2 shows the remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.5.4.1 Virtual Connections

dsPIC33EVXXXGM00X/10X family devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module").

These devices provide six virtual output pins (RPV0-RPV5) that correspond to the outputs of six peripheral pin output remapper blocks (RP176-RP181). The six virtual remapper outputs (RP176-RP181) are not connected to actual pins. The six virtual pins may be read by any of the input remappers as inputs, RP176-RP181. These virtual pins can be used to connect the internal peripherals, whose signals are of significant use to the other peripherals, but these output signals are not present on the device pin.

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<7:0> bits of the RPINR12 register to the value of 'b0000001', the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

# REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , <b>read as</b> '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP49R<5:0>:** Peripheral Output Function is Assigned to RP49 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits

(see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

# 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                                                                                                        | R/W-0            | U-0             | U-0              | U-0                       | U-0                | U-0         |

|--------------------|------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|---------------------------|--------------------|-------------|

| TON <sup>(1)</sup> | —                                                                                                          | TSIDL            | —               | —                | _                         | —                  | —           |

| bit 15             |                                                                                                            |                  |                 |                  |                           |                    | bit 8       |

|                    |                                                                                                            |                  |                 |                  |                           |                    |             |

| U-0                | R/W-0                                                                                                      | R/W-0            | R/W-0           | U-0              | R/W-0                     | R/W-0              | U-0         |

|                    | TGATE                                                                                                      | TCKPS1           | TCKPS0          | —                | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |

| bit 7              |                                                                                                            |                  |                 |                  |                           |                    | bit 0       |

|                    |                                                                                                            |                  |                 |                  |                           |                    |             |

| Legend:            |                                                                                                            |                  |                 |                  |                           |                    |             |

| R = Readable       |                                                                                                            | W = Writable     |                 | -                | mented bit, read          |                    |             |

| -n = Value at F    | POR                                                                                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared                      | x = Bit is unkr    | nown        |

|                    |                                                                                                            | o                |                 |                  |                           |                    |             |

| bit 15             | TON: Timer1                                                                                                |                  |                 |                  |                           |                    |             |

|                    | 1 = Starts 16-<br>0 = Stops 16-                                                                            |                  |                 |                  |                           |                    |             |

| bit 14             | •                                                                                                          | ted: Read as '   | י)              |                  |                           |                    |             |

| bit 13             | -                                                                                                          | 1 Stop in Idle N |                 |                  |                           |                    |             |

| 2.1.10             |                                                                                                            | ues module op    |                 | he device ente   | ers Idle mode             |                    |             |

|                    | 0 = Continues                                                                                              | s module opera   | tion in Idle mo | ode              |                           |                    |             |

| bit 12-7           | Unimplemented: Read as '0'                                                                                 |                  |                 |                  |                           |                    |             |

| bit 6              | TGATE: Time                                                                                                | r1 Gated Time    | Accumulation    | Enable bit       |                           |                    |             |

|                    | When TCS =<br>This bit is igno                                                                             |                  |                 |                  |                           |                    |             |

|                    | When TCS =                                                                                                 |                  |                 |                  |                           |                    |             |

|                    |                                                                                                            | e accumulation   |                 |                  |                           |                    |             |

| bit 5-4            |                                                                                                            | e accumulation   |                 | a Salaat hita    |                           |                    |             |

| DIL 3-4            | 11 = 1:256                                                                                                 | : Timer1 Input   |                 |                  |                           |                    |             |

|                    | 10 = 1:64                                                                                                  |                  |                 |                  |                           |                    |             |

|                    | 01 = 1:8                                                                                                   |                  |                 |                  |                           |                    |             |

|                    | 00 = 1:1                                                                                                   |                  |                 |                  |                           |                    |             |

| bit 3              | -                                                                                                          | ted: Read as '   |                 |                  | (1)                       |                    |             |

| bit 2              |                                                                                                            | er1 External Clo | ock Input Synd  | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |

|                    | <u>When TCS =</u><br>1 = External c                                                                        |                  | nchronized      |                  |                           |                    |             |

|                    | <ol> <li>External clock input is synchronized</li> <li>External clock input is not synchronized</li> </ol> |                  |                 |                  |                           |                    |             |

|                    | When TCS =                                                                                                 | =                | ,               |                  |                           |                    |             |

|                    | This bit is igno                                                                                           |                  |                 |                  |                           |                    |             |

| bit 1              |                                                                                                            | Clock Source S   |                 |                  |                           |                    |             |

|                    | 1 = External clock is from pin, T1CK (on the rising edge)<br>0 = Internal clock (FP)                       |                  |                 |                  |                           |                    |             |

| bit 0              | Unimplemen                                                                                                 | ted: Read as '   | כי              |                  |                           |                    |             |

|                    | en Timer1 is en<br>mpts by user se                                                                         |                  |                 |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |

| U-0                                      | U-0        | U-0            | U-0   | U-0                                     | U-0   | U-0   | U-0   |

|------------------------------------------|------------|----------------|-------|-----------------------------------------|-------|-------|-------|

| —                                        | —          | —              |       | —                                       | —     | —     | —     |

| bit 15                                   |            |                |       |                                         |       |       | bit 8 |

|                                          |            |                |       |                                         |       |       |       |

| R/W-0                                    | R/W-0      | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                          |            |                | STEP  | 2<7:0>                                  |       |       |       |

| bit 7                                    |            |                |       |                                         |       |       | bit 0 |

|                                          |            |                |       |                                         |       |       |       |

| Legend:                                  |            |                |       |                                         |       |       |       |

| R = Readable                             | bit        | W = Writable   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR '1' = Bit is set       |            |                |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

| <u> </u>                                 |            |                |       |                                         |       |       |       |

| bit 15-8                                 | Unimplemen | ted: Read as ' | 0'    |                                         |       |       |       |

| bit 7-0 STEP2<7:0>: DMT Clear Timer bits |            |                |       |                                         |       |       |       |

#### REGISTER 14-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if preceded by the correct loading of the STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading the DMTCNTL/H register and observing the counter being reset.

All Other

Write Patterns = Sets the BAD2 bit; the value of STEP1<7:0> will remain unchanged and the new value being written to STEP2<7:0> will be captured. These bits are cleared when a DMT Reset event occurs.

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-----|---------------------|

| _      | —   | —   | —   | —   | —   | —   | IC32 <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8               |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> | _   | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC32: Input Capture x 32-Bit Timer Mode Select bit (Cascade mode) <sup>(1)</sup>                                                                                                                                              |

|          | <ul> <li>1 = Odd ICx and even ICx form a single 32-bit input capture module</li> <li>0 = Cascade module operation is disabled</li> </ul>                                                                                      |

| bit 7    | ICTRIG: Input Capture x Trigger Operation Select bit <sup>(2)</sup>                                                                                                                                                           |

|          | <ul> <li>1 = Input source is used to trigger the input capture timer (Trigger mode)</li> <li>0 = Input source is used to synchronize the input capture timer to the timer of another module (Synchronization mode)</li> </ul> |

| bit 6    | TRIGSTAT: Timer Trigger Status bit <sup>(3)</sup>                                                                                                                                                                             |

|          | <ul> <li>1 = ICxTMR has been triggered and is running</li> <li>0 = ICxTMR has not been triggered and is being held clear</li> </ul>                                                                                           |

| bit 5    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note di  | The IC22 hit is both the odd and over ICy must be eat to enable Caseada mode                                                                                                                                                  |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 **FLTMD FLTOUT FLTTRIEN** OCINV \_\_\_\_ \_\_\_\_ OC32 \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0, HS R/W-0 R/W-0 R/W-1 R/W-1 R/W-0 R/W-0 OCTRIG OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 TRIGSTAT SYNCSEL1 SYNCSEL0 bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTMD: Fault Mode Select bit 1 = Fault mode is maintained until the Fault source is removed; the OCFLTA bit is cleared in software and a new PWM period starts 0 = Fault mode is maintained until the Fault source is removed and a new PWM period starts bit 14 FLTOUT: Fault Out bit 1 = PWM output is driven high on a Fault 0 = PWM output is driven low on a Fault bit 13 FLTTRIEN: Fault Output State Select bit 1 = OCx pin is tri-stated on a Fault condition 0 = OCx pin I/O state is defined by the FLTOUT bit on a Fault condition bit 12 **OCINV:** Output Compare x Invert bit 1 = OCx output is inverted 0 = OCx output is not inverted bit 11-9 Unimplemented: Read as '0' bit 8 OC32: Cascade Two OCx Modules Enable bit (32-bit operation) 1 = Cascade module operation is enabled 0 = Cascade module operation is disabled bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit 1 = Triggers OCx from the source designated by the SYNCSELx bits 0 = Synchronizes OCx with the source designated by the SYNCSELx bits bit 6 TRIGSTAT: Timer Trigger Status bit 1 = Timer source has been triggered and is running 0 = Timer source has not been triggered and is being held clear bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit 1 = Output Compare x is tri-stated 0 = Output Compare x module drives the OCx pin

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

**Note 1:** Do not use the OCx module as its own synchronization or trigger source.

2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

| R       | R                 | R |        | R<br>23:16> <sup>(1)</sup> | R         | R | R      |

|---------|-------------------|---|--------|----------------------------|-----------|---|--------|

|         |                   |   | DEVID  | 23.10/                     |           |   |        |

| bit 23  |                   |   |        |                            |           |   | bit 16 |

| R       | R                 | R | R      | R                          | R         | R | R      |

|         |                   |   | DEVID< | <15:8> <b>(1)</b>          |           |   |        |

| bit 15  |                   |   |        |                            |           |   | bit 8  |

| R       | R                 | R | R      | R                          | R         | R | R      |

|         |                   |   | DEVID  | <7:0> <sup>(1)</sup>       |           |   |        |

| bit 7   |                   |   |        |                            |           |   | bit 0  |

| Legend: | R = Read-Only bit |   |        | U = Unimplem               | ented bit |   |        |

#### REGISTER 27-1: DEVID: DEVICE ID REGISTER

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to "*dsPIC33EVXXXGM00X/10X Families Flash Programming Specification*" (DS70005137) for the list of Device ID values.

#### REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER

| Legend: | R = Read-only bit | Read-only bit U = Unimplemented bit |         |                        |   |   |        |  |

|---------|-------------------|-------------------------------------|---------|------------------------|---|---|--------|--|

| bit 7   |                   |                                     |         |                        |   |   | bit 0  |  |

|         |                   |                                     | DEVRE   | /<7:0> <sup>(1)</sup>  |   |   |        |  |

| R       | R                 | R                                   | R       | R                      | R | R | R      |  |

| bit 15  |                   |                                     |         |                        |   |   | bit 8  |  |

|         |                   |                                     | DEVREV  | <15:8> <sup>(1)</sup>  |   |   |        |  |

| R       | R                 | R                                   | R       | R                      | R | R | R      |  |

| bit 23  |                   |                                     |         |                        |   |   | bit 16 |  |

|         |                   |                                     | DEVREV< | <23:16> <sup>(1)</sup> |   |   |        |  |

| R       | R                 | R                                   | R       | R                      | R | R | R      |  |

#### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to "*dsPIC33EVXXXGM00X/10X Families Flash Programming Specification*" (DS70005137) for the list of device revision values.

| TABLE 31-4: | DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| DC CHARACT       | ERISTICS      |      |       | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |    |                         |  |  |

|------------------|---------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------|--|--|

| Parameter<br>No. | Typical       | Мах  | Units | Conditions                                                                                                                                              |    |                         |  |  |

| Power-Down (     | Current (IPD) |      |       |                                                                                                                                                         |    |                         |  |  |

| HDC60e           | 1300          | 2500 | μA    | +150°C                                                                                                                                                  | 5V | Base Power-Down Current |  |  |

| HDC61c           | 10            | 50   | μA    | +150°C 5V Watchdog Timer Current: ∆IwDT                                                                                                                 |    |                         |  |  |

#### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS |         |     |       | •                 |    | (unless otherwise stated)<br>for High Temperature |  |

|--------------------|---------|-----|-------|-------------------|----|---------------------------------------------------|--|

| Parameter<br>No.   | Typical | Max | Units | Conditions        |    |                                                   |  |

| HDC40e             | 2.6     | 5.0 | mA    | +150°C            | 5V | 10 MIPS                                           |  |

| HDC42e             | 3.6     | 7.0 | mA    | +150°C 5V 20 MIPS |    |                                                   |  |

#### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |         |      |       | •                 |    | V (unless otherwise stated)<br>C for High Temperature |  |

|--------------------|---------|------|-------|-------------------|----|-------------------------------------------------------|--|

| Parameter<br>No.   | Typical | Max  | Units | Conditions        |    |                                                       |  |

| HDC20e             | 5.9     | 8.0  | mA    | +150°C            | 5V | 10 MIPS                                               |  |

| HDC22e             | 10.3    | 15.0 | mA    | +150°C            | 5V | 20 MIPS                                               |  |

| HDC23e             | 19.0    | 25.0 | mA    | +150°C 5V 40 MIPS |    |                                                       |  |

#### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARAG        | CTERISTICS |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |            |    |           |  |

|------------------|------------|------|------------------------------------------------------|-------|------------|----|-----------|--|

| Parameter<br>No. | Typical    | Мах  | Doze Ratio                                           | Units | Conditions |    |           |  |

| HDC73a           | 18.5       | 22.0 | 1:2                                                  | mA    | +150°C     | 5V | 40 MIPS   |  |

| HDC73g           | 8.35       | 12.0 | 1:128                                                | mA    | +150 C     | 50 | 40 101195 |  |

### 32.12 VBOR

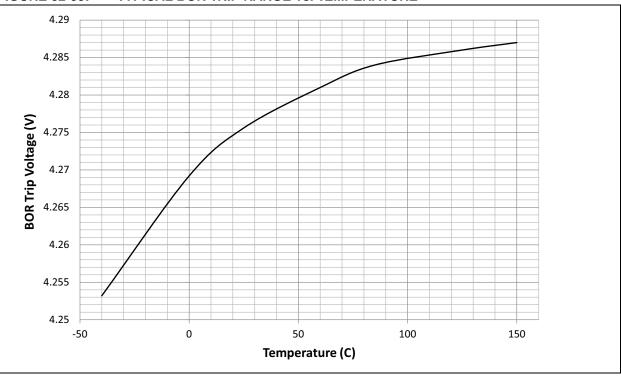

FIGURE 32-35: TYPICAL BOR TRIP RANGE vs. TEMPERATURE

# 32.13 RAM Retention

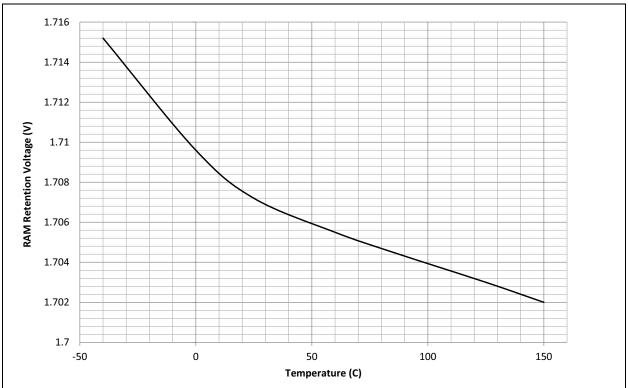

FIGURE 32-36: TYPICAL RAM RETENTION VOLTAGE vs. TEMPERATURE

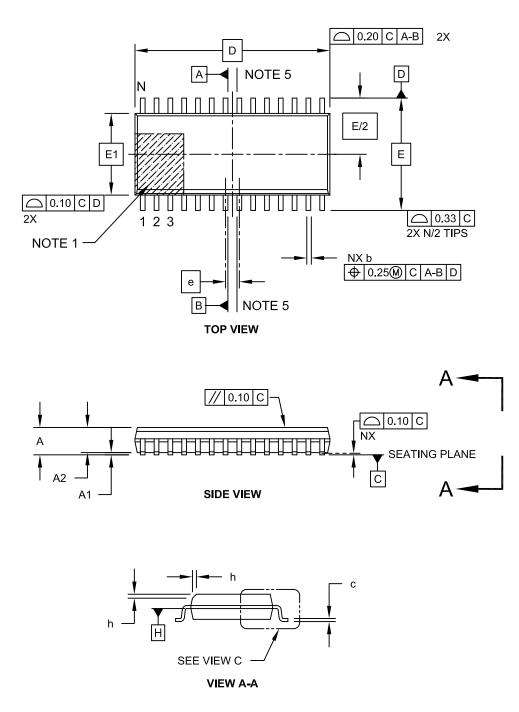

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

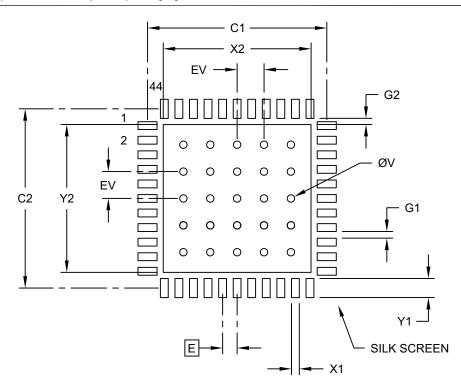

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |      |          |      |

|----------------------------------|-------------|------|----------|------|

| Dimension                        | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                    | E           |      | 0.65 BSC |      |

| Optional Center Pad Width        | X2          |      |          | 6.60 |

| Optional Center Pad Length       | Y2          |      |          | 6.60 |

| Contact Pad Spacing              | C1          |      | 8.00     |      |

| Contact Pad Spacing              | C2          |      | 8.00     |      |

| Contact Pad Width (X44)          | X1          |      |          | 0.35 |

| Contact Pad Length (X44)         | Y1          |      |          | 0.85 |

| Contact Pad to Contact Pad (X40) | G1          | 0.30 |          |      |

| Contact Pad to Center Pad (X44)  | G2          | 0.28 |          |      |

| Thermal Via Diameter             | V           |      | 0.33     |      |

| Thermal Via Pitch                | EV          |      | 1.20     |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

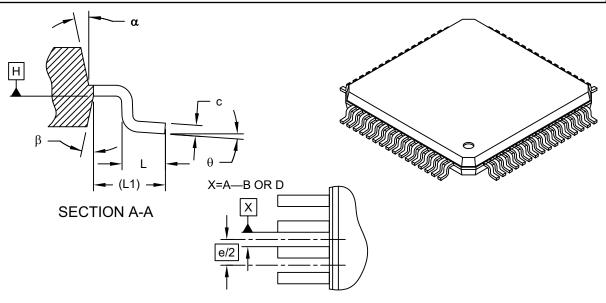

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### DETAIL 1

|                          | MILLIMETERS |             |           |      |  |

|--------------------------|-------------|-------------|-----------|------|--|

| Dimension                | MIN         | NOM         | MAX       |      |  |

| Number of Leads          | Ν           |             | 64        |      |  |

| Lead Pitch               | е           |             | 0.50 BSC  |      |  |

| Overall Height           | A           | -           | -         | 1.20 |  |

| Molded Package Thickness | A2          | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1          | 0.05        | -         | 0.15 |  |

| Foot Length              | L           | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1          | 1.00 REF    |           |      |  |

| Foot Angle               | ¢           | 0°          | 3.5°      | 7°   |  |

| Overall Width            | Е           |             | 12.00 BSC |      |  |

| Overall Length           | D           |             | 12.00 BSC |      |  |

| Molded Package Width     | E1          |             | 10.00 BSC |      |  |

| Molded Package Length    | D1          |             | 10.00 BSC |      |  |

| Lead Thickness           | С           | 0.09        | -         | 0.20 |  |

| Lead Width               | b           | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α           | 11° 12° 13° |           |      |  |

| Mold Draft Angle Bottom  | β           | 11°         | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

# APPENDIX A: REVISION HISTORY

# **Revision A (December 2013)**

This is the initial version of this document.

# Revision B (June 2014)

This revision incorporates the following updates:

- · Sections:

- Added Section 31.0 "High-Temperature Electrical Characteristics"

- Updated the "Power Management" section, the "Input/Output" section, Section 3.3

"Data Space Addressing", Section 4.2

"Data Address Space", Section 4.3.2

"Extended X Data Space", Section 4.6.1

"Bit-Reversed Addressing Implementation", Section 7.4.1 "INTCON1 through INTCON4", Section 11.7 "I/O Helpful Tips"

- Updated note in Section 17.0 "High-Speed PWM Module", Section 18.0 "Serial Peripheral Interface (SPI)", Section 27.8 "Code Protection and CodeGuard™ Security"

- Updated title of Section 20.0 "Single-Edge Nibble Transmission (SENT)"

- Updated Section 34.0 "Packaging Information". Deleted e3, Pb-free and Industrial (I) temperature range indication throughout the section, and updated the packaging diagrams

- Updated the "Product Identification System" section

- Registers:

- Updated Register 3-2, Register 7-2, Register 7-6, Register 9-2, Register 11-3, Register 14-1, Register 14-3, Register 14-11, Register 15-1, Register 22-4

- Figures:

- Added Figure 4-6, Figure 4-8, Figure 4-14, Figure 4-15, Figure 14-1, Figure 16-1, Figure 17-2, Figure 23-1, Figure 24-1

- Tables:

- Updated Table 1, Table 27-1, Table 27-2, Table 30-6, Table 30-7, Table 30-8, Table 30-9, Table 30-10, Table 30-11, Table 30-12, Table 30-38, Table 30-50, Table 30-53 and added Table 31-11,

- Changes to text and formatting were incorporated throughout the document

#### **Revision C (November 2014)**

This revision incorporates the following updates:

- · Sections:

- Added note in Section 5.2 "RTSP Operation"

- Updated "Section 5.4 "Error Correcting Code (ECC)"

- Deleted 44-Terminal Very Thin Leadless Array Package (TL) - 6x6x0.9 mm Body With Exposed Pad (VTLA).

- Registers

- Updated Register 7-6

- Figures:

- Updated Figure 4-1, Figure 4-3, Figure 4-4

- · Tables:

- Updated Table 27-2, Table 31-13, Table 31-14, Table 31-15

- Added Table 31-16, Table 31-17

# **Revision D (April 2015)**

This revision incorporates the following updates:

- Sections:

- Updated the Clock Management, Timers/ Output Compare/Input Capture, Communication Interfaces and Input/Output sections at the beginning of the data sheet (Page 1 and Page 2).

- Updated all pin diagrams at the beginning of the data sheet (Page 4 through Page 9).

- Added Section 11.6 "High-Voltage Detect (HVD)"

- Updated Section 13.0 "Timer2/3 and Timer4/5"

- Corrects all Buffer heading numbers in Section 22.4 "CAN Message Buffers"

- Registers

- Updated Register 3-2, Register 25-2, Register 26-2

- Figures

- Updated Figure 26-1, Figure 30-5, Figure 30-32

- Tables

- Updated Table 1, Table 4-25, Table 30-10, Table 30-22, Table 30-53 and Table 31-8

- Changes to text and formatting were incorporated throughout the document