Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev32gm106t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EVXXXGM00X/10X FAMILY

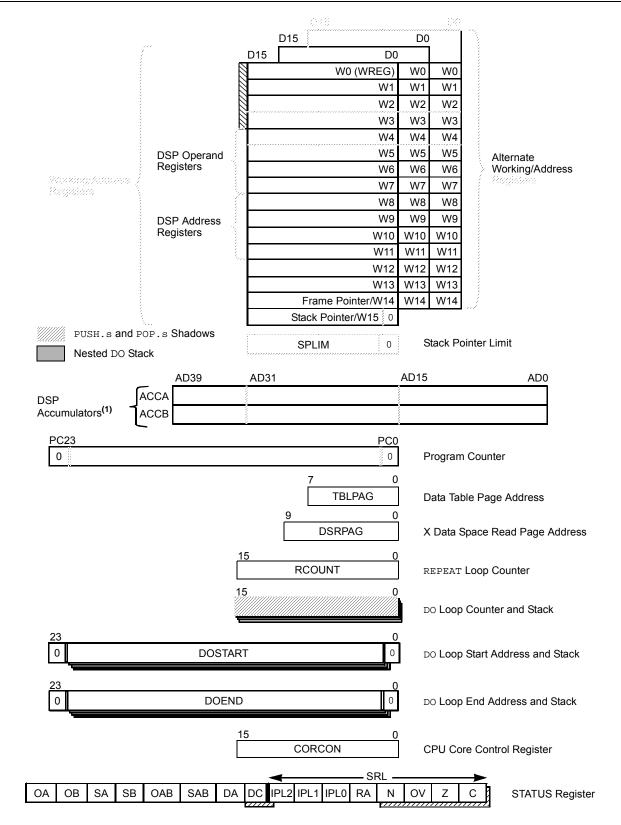

### FIGURE 3-2: PROGRAMMER'S MODEL

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = Overflow has not occurred for signed arithmetic                                                                                                                                                          |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                              |

| Note 1. | The IPI <2:0> hits are concatenated with the IPI 3 hit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                      |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

# TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|---------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------------|---------|--------|--------|--------|--------|--------|--------|---------------|

|             | 0400-<br>041E |        |        |        |        |        |        |        | See defin | ition when W | /IN = x |        |        |        |        |        |        |               |

| C1BUFPNT1   | 0420          | F3BP3  | F3BP2  | F3BP1  | F3BP0  | F2BP3  | F2BP2  | F2BP1  | F2BP0     | F1BP3        | F1BP2   | F1BP1  | F1BP0  | F0BP3  | F0BP2  | F0BP1  | F0BP0  | 0000          |

| C1BUFPNT2   | 0422          | F7BP3  | F7BP2  | F7BP1  | F7BP0  | F6BP3  | F6BP2  | F6BP1  | F6BP0     | F5BP3        | F5BP2   | F5BP1  | F5BP0  | F4BP3  | F4BP2  | F4BP1  | F4BP0  | 0000          |

| C1BUFPNT3   | 0424          | F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0    | F9BP3        | F9BP2   | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  | 0000          |

| C1BUFPNT4   | 0426          | F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0    | F13BP3       | F13BP2  | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 | 0000          |

| C1RXM0SID   | 0430          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | —      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM0EID   | 0432          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXM1SID   | 0434          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM1EID   | 0436          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | •      |        | xxxx          |

| C1RXM2SID   | 0438          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM2EID   | 043A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF0SID   | 0440          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF0EID   | 0442          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF1SID   | 0444          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF1EID   | 0446          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF2SID   | 0448          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | -      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF2EID   | 044A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF3SID   | 044C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF3EID   | 044E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF4SID   | 0450          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF4EID   | 0452          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF5SID   | 0454          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF5EID   | 0456          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF6SID   | 0458          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF6EID   | 045A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF7SID   | 045C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF7EID   | 045E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF8SID   | 0460          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF8EID   | 0462          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF9SID   | 0464          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF9EID   | 0466          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF10SID  | 0468          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF10EID  | 046A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        |        |        | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

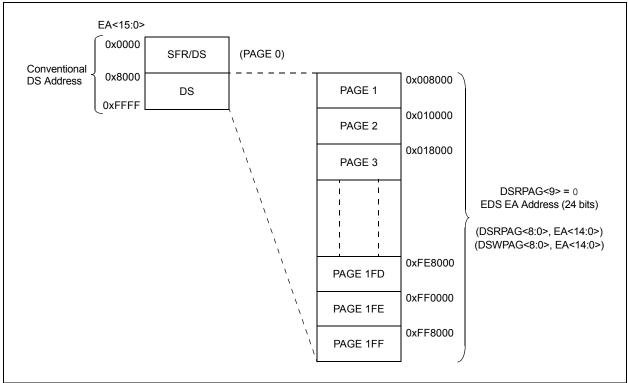

### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

# dsPIC33EVXXXGM00X/10X FAMILY

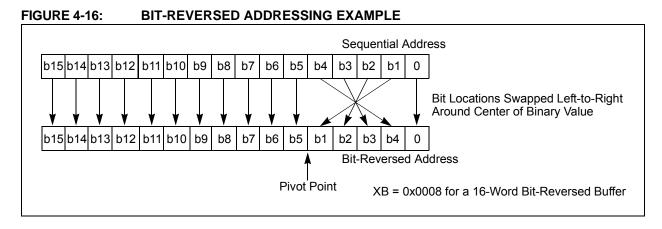

### TABLE 4-46: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | Idress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/SO-0            |                       | R/W-0                          | R/W-0                  | U-0                       | U-0                       | R/W-0                     | R/W-0                    |

|-------------------|-----------------------|--------------------------------|------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| WR <sup>(1)</sup> | WREN <sup>(1)</sup>   | WRERR <sup>(1)</sup>           | NVMSIDL <sup>(2)</sup> |                           |                           | RPDF                      | URERR                    |

| bit 15            |                       |                                |                        |                           |                           | •                         | bit 8                    |

|                   |                       |                                |                        |                           |                           |                           |                          |

| U-0               | U-0                   | U-0                            | U-0                    | R/W-0                     | R/W-0                     | R/W-0                     | R/W-0                    |

| —                 | —                     | —                              | —                      | NVMOP3 <sup>(1,3,4)</sup> | NVMOP2 <sup>(1,3,4)</sup> | NVMOP1 <sup>(1,3,4)</sup> | NVMOP0 <sup>(1,3,4</sup> |

| bit 7             |                       |                                |                        |                           |                           |                           | bit (                    |

| Legend:           |                       | SO = Settable                  | e Onlv bit             |                           |                           |                           |                          |

| R = Reada         | able bit              | W = Writable                   | 3                      | U = Unimplem              | ented bit, read a         | <b>as</b> '0'             |                          |

| -n = Value        | at POR                | '1' = Bit is set               | t                      | '0' = Bit is clea         |                           | x = Bit is unkn           | own                      |

|                   |                       |                                |                        |                           |                           |                           |                          |

| bit 15            | WR: Write C           | Control bit <sup>(1)</sup>     |                        |                           |                           |                           |                          |

|                   |                       |                                |                        |                           |                           | ion is self-time          | d and the bit is         |

|                   |                       |                                |                        | tion is complete          |                           |                           |                          |

| bit 14            | -                     | e Enable bit <sup>(1)</sup>    | ation is comp          | lete and inactive         | <del>J</del>              |                           |                          |

| 011 14            |                       | ogram or erase                 | operations a           | re enabled                |                           |                           |                          |

|                   |                       | ogram or erase                 |                        |                           |                           |                           |                          |

| bit 13            | =                     | rite Sequence I                |                        |                           |                           |                           |                          |

|                   |                       |                                |                        | nce attempt, or t         | termination has           | occurred (bit is s        | et automaticall          |

|                   |                       | set attempt of th              |                        |                           |                           |                           |                          |

| L:1 10            | -                     | -                              | -                      | npleted normally          | /                         |                           |                          |

| bit 12            |                       | NVM Stop in Idl                |                        |                           | ce enters Idle m          |                           |                          |

|                   |                       |                                |                        |                           | enters Idle mod           |                           |                          |

| bit 11-10         | -                     | nted: Read as                  |                        |                           |                           |                           |                          |

| bit 9             | RPDF: Row             | Programming                    | Data Format (          | Control bit               |                           |                           |                          |

|                   |                       |                                |                        | compressed fo             | rmat                      |                           |                          |

|                   | 0 = Row data          | a to be stored i               | in RAM is in a         | n uncompresse             | d format                  |                           |                          |

| bit 8             |                       | -                              | -                      | run Error Flag b          |                           |                           |                          |

|                   |                       | gramming ope<br>underrun has o |                        | en terminated du          | ue to a data unc          | lerrun error              |                          |

| bit 7-4           | Unimpleme             | nted: Read as                  | <b>'</b> 0'            |                           |                           |                           |                          |

| Note 1:           | These bits can c      | only be reset or               | n a POR                |                           |                           |                           |                          |

|                   | If this bit is set, t | -                              |                        | avings (lidle). a         | and upon exiting          | ldle mode, the            | re is a delav            |

|                   | (TVREG) before I      |                                |                        |                           |                           | ,,                        | · · · <b>,</b>           |

| ٥.                |                       |                                |                        |                           |                           |                           |                          |

- 3: All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- **5:** Two adjacent words on a 4-word boundary are programmed during execution of this operation.

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

- Illegal Address Mode Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this device data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in the other sections of this device data sheet.

**Note:** The status bits in the RCON register should be cleared after they are read. Therefore, the next RCON register value after a device Reset is meaningful.

Note: In all types of Resets, to select the device clock source, the contents of OSCCON are initialized from the FNOSCx Configuration bits in the FOSCSEL Configuration register.

|                   | -                             |                                    |                 |                                      |                   |                |         |

|-------------------|-------------------------------|------------------------------------|-----------------|--------------------------------------|-------------------|----------------|---------|

| R/W-0             | R/W-0                         | R/W-0                              | R/W-0           | R/W-0                                | R/W-0             | R/W-0          | R/W-0   |

| NSTDIS            | OVAERR                        | OVBERR                             | COVAERR         | COVBERR                              | OVATE             | OVBTE          | COVTE   |

| bit 15            |                               |                                    |                 |                                      |                   |                | bit 8   |

| Davio             |                               | <b>D</b> 444.0                     | <b>D</b> 444 0  | <b>D</b> 4440                        | <b>D</b> 444 0    | <b>D</b> 444 0 |         |

| R/W-0             | R-0, HC                       | R/W-0                              | R/W-0           | R/W-0                                | R/W-0             | R/W-0          | U-0     |

| SFTACERR<br>bit 7 | DIV0ERR                       | DMACERR                            | MATHERR         | ADDRERR                              | STKERR            | OSCFAIL        | — hit 0 |

|                   |                               |                                    |                 |                                      |                   |                | bit 0   |

| Legend:           |                               | HC = Hardwa                        | re Clearable bi | it                                   |                   |                |         |

| R = Readable      | bit                           | W = Writable                       | bit             | U = Unimplem                         | ented bit, read a | as '0'         |         |

| -n = Value at P   | OR                            | '1' = Bit is set                   |                 | '0' = Bit is clea                    | ired              | x = Bit is unk | nown    |

|                   |                               |                                    |                 |                                      |                   |                |         |

| bit 15            | NSTDIS: Inte                  | errupt Nesting                     | Disable bit     |                                      |                   |                |         |

|                   |                               | nesting is disa<br>nesting is ena  |                 |                                      |                   |                |         |

| bit 14            | •                             | ccumulator A (                     |                 | lag hit                              |                   |                |         |

| bit 14            |                               | s caused by ov                     |                 | •                                    |                   |                |         |

|                   |                               | s not caused b                     |                 |                                      |                   |                |         |

| bit 13            |                               | ccumulator B (                     |                 | 0                                    |                   |                |         |

|                   |                               | s caused by ov<br>s not caused b   |                 |                                      |                   |                |         |

| bit 12            | -                             |                                    | -               | Overflow Trap F                      | lag bit           |                |         |

| 51(12             |                               |                                    | •               | flow of Accumu                       | •                 |                |         |

|                   |                               |                                    |                 | overflow of Accu                     |                   |                |         |

| bit 11            |                               |                                    | -               | Overflow Trap F                      | -                 |                |         |

|                   | •                             | •                                  | •               | flow of Accumu                       |                   |                |         |

| bit 10            | -                             | umulator A Ov                      |                 |                                      |                   |                |         |

| 2.1.1.0           |                               | erflow of Accun                    | •               |                                      |                   |                |         |

|                   | 0 = Trap is d                 | lisabled                           |                 |                                      |                   |                |         |

| bit 9             |                               | cumulator B O                      | •               | able bit                             |                   |                |         |

|                   | 1 = Trap ove<br>0 = Trap is d | erflow of Accun                    | nulator B       |                                      |                   |                |         |

| bit 8             | •                             | tastrophic Over                    | flow Trap Fnat  | ole bit                              |                   |                |         |

|                   |                               |                                    |                 | mulator A or B i                     | s enabled         |                |         |

|                   | 0 = Trap is d                 | -                                  |                 |                                      |                   |                |         |

| bit 7             |                               | : Shift Accumu                     |                 |                                      |                   |                |         |

|                   |                               | •                                  | •               | alid accumulator<br>alid accumulator |                   |                |         |

| bit 6             |                               | )ivide-by-Zero                     | -               |                                      | Simi              |                |         |

|                   |                               | or trap was cal                    |                 |                                      |                   |                |         |

|                   | 0 = Math err                  | or trap was no                     | t caused by a d | livide-by-zero                       |                   |                |         |

| bit 5             |                               | DMAC Trap F                        | -               |                                      |                   |                |         |

|                   |                               | rap has occurre<br>rap has not occ |                 |                                      |                   |                |         |

| bit 4             |                               | Math Error Sta                     |                 |                                      |                   |                |         |

|                   |                               | or trap has occ                    |                 |                                      |                   |                |         |

|                   | 0 = Math err                  | or trap has not                    | occurred        |                                      |                   |                |         |

|                   |                               |                                    |                 |                                      |                   |                |         |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

© 2013-2016 Microchip Technology Inc.

| R/W-0           | R/W-0                                                                                                      | R/W-0                                  | U-0            | U-0            | U-0             | U-0              | U-0    |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|----------------|-----------------|------------------|--------|--|--|--|

| FRMEN           | SPIFSD                                                                                                     | FRMPOL                                 | _              | —              | —               | —                | —      |  |  |  |

| bit 15          |                                                                                                            |                                        |                |                |                 |                  | bit 8  |  |  |  |

|                 |                                                                                                            |                                        |                |                |                 |                  |        |  |  |  |

| U-0             | U-0                                                                                                        | U-0                                    | U-0            | U-0            | U-0             | R/W-0            | R/W-0  |  |  |  |

| _               |                                                                                                            |                                        |                |                | _               | FRMDLY           | SPIBEN |  |  |  |

| bit 7           |                                                                                                            |                                        |                |                |                 |                  | bit 0  |  |  |  |

|                 |                                                                                                            |                                        |                |                |                 |                  |        |  |  |  |

| Legend:         |                                                                                                            |                                        |                |                |                 |                  |        |  |  |  |

| R = Readable    | bit                                                                                                        | W = Writable                           | bit            | U = Unimpler   | mented bit, rea | <b>d as</b> '0'  |        |  |  |  |

| -n = Value at F | x = Bit is unkr                                                                                            | nown                                   |                |                |                 |                  |        |  |  |  |

|                 |                                                                                                            |                                        |                |                |                 |                  |        |  |  |  |

| bit 15          | FRMEN: Fran                                                                                                | med SPIx Supp                          | ort bit        |                |                 |                  |        |  |  |  |

|                 |                                                                                                            |                                        |                | pin is used as | the Frame Sy    | nc pulse input/o | utput) |  |  |  |

|                 |                                                                                                            | SPIx support is                        |                |                |                 |                  |        |  |  |  |

| bit 14          |                                                                                                            | x Frame Sync F                         |                | n Control bit  |                 |                  |        |  |  |  |

|                 |                                                                                                            | /nc pulse input                        |                |                |                 |                  |        |  |  |  |

| h:+ 40          | -                                                                                                          | /nc pulse outpu                        | . ,            |                |                 |                  |        |  |  |  |

| bit 13          |                                                                                                            | ame Sync Pulse                         | 5              |                |                 |                  |        |  |  |  |

|                 |                                                                                                            | /nc pulse is acti<br>/nc pulse is acti |                |                |                 |                  |        |  |  |  |

| bit 12-2        | -                                                                                                          | ited: Read as '                        |                |                |                 |                  |        |  |  |  |

| bit 1           | •                                                                                                          |                                        |                | hit            |                 |                  |        |  |  |  |

|                 | <b>FRMDLY:</b> Frame Sync Pulse Edge Select bit<br>1 = Frame Sync pulse coincides with the first bit clock |                                        |                |                |                 |                  |        |  |  |  |

|                 |                                                                                                            | /nc pulse prece                        |                |                |                 |                  |        |  |  |  |

| bit 0           | SPIBEN: SPI                                                                                                | x Enhanced Bu                          | iffer Enable b | it             |                 |                  |        |  |  |  |

|                 | 1 = Enhance                                                                                                | d buffer is enab                       | led            |                |                 |                  |        |  |  |  |

|                 | 0 = Enhance                                                                                                | d buffer is disab                      | led (Standard  | d mode)        |                 |                  |        |  |  |  |

|                 |                                                                                                            |                                        |                |                |                 |                  |        |  |  |  |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| U-0                                                                                                                                                                                                                                | U-0                                                                                                                               | U-0                                                                                                                                                                   | R/W-0                                                                                                                | R/W-0                                                                                                                           | R/W-0                                                                                                           | R/W-0                                                                        | R/W-0                                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--|

| _                                                                                                                                                                                                                                  | —                                                                                                                                 | _                                                                                                                                                                     | CH123SB2                                                                                                             | CH123SB1                                                                                                                        | CH123NB1                                                                                                        | CH123NB0                                                                     | CH123SB0                                 |  |

| bit 15                                                                                                                                                                                                                             |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              | bit 8                                    |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   | 11.0                                                                                                                                                                  | R/W-0                                                                                                                | D/M/ 0                                                                                                                          | R/W-0                                                                                                           |                                                                              |                                          |  |

| U-0                                                                                                                                                                                                                                | U-0                                                                                                                               | U-0                                                                                                                                                                   | CH123SA2                                                                                                             | R/W-0                                                                                                                           | CH123NA1                                                                                                        | R/W-0                                                                        | R/W-0                                    |  |

| <br>bit 7                                                                                                                                                                                                                          | _                                                                                                                                 | _                                                                                                                                                                     | CHI235AZ                                                                                                             | CH123SA1                                                                                                                        | CHIZSNAI                                                                                                        | CH123NA0                                                                     | CH123SA0                                 |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              | bit                                      |  |

| Legend:                                                                                                                                                                                                                            |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| R = Readab                                                                                                                                                                                                                         | le bit                                                                                                                            | W = Writable                                                                                                                                                          | e bit                                                                                                                | U = Unimpler                                                                                                                    | nented bit, read                                                                                                | as '0'                                                                       |                                          |  |

| -n = Value a                                                                                                                                                                                                                       | t POR                                                                                                                             | '1' = Bit is se                                                                                                                                                       | et                                                                                                                   | '0' = Bit is cle                                                                                                                | ared                                                                                                            | x = Bit is unkr                                                              | iown                                     |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| bit 15-13                                                                                                                                                                                                                          | -                                                                                                                                 | ted: Read as                                                                                                                                                          |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| bit 12-11                                                                                                                                                                                                                          |                                                                                                                                   |                                                                                                                                                                       | 1, 2, 3 Positive                                                                                                     | -                                                                                                                               | =                                                                                                               |                                                                              | 0110                                     |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   | s AN6 (Op An                                                                                                                                                          | s AN0 (Op Amp<br>an 3)                                                                                               | 2), CH2 posit                                                                                                                   | ive input is AN2                                                                                                | 25 (Op Amp 5)                                                                | , CH3 positiv                            |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       | AN3 (Op Amp 1                                                                                                        | I), CH2 positive                                                                                                                | e input is AN0 (0                                                                                               | Op Amp 2), CH3                                                               | B positive inp                           |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   | 25 (Op Amp 5)                                                                                                                                                         |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| <ul> <li>010 = CH1 positive input is AN3 (Op Amp 1), CH2 positive input is AN0 (Op Amp 2), CH3 pos<br/>is AN6 (Op Amp 3)</li> <li>001 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> </ul> |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| bit 10-9                                                                                                                                                                                                                           | CH123NB<1                                                                                                                         | :0>: Channels                                                                                                                                                         | 1, 2, 3 Negative                                                                                                     | e Input Select                                                                                                                  | for Sample B bi                                                                                                 | ts                                                                           |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       | AN9, CH2 nega                                                                                                        |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       | AN6, CH2 nega<br>tive inputs are \                                                                                   |                                                                                                                                 | N7, CH3 negati                                                                                                  | ve input is AN8                                                              |                                          |  |

| bit 8                                                                                                                                                                                                                              |                                                                                                                                   | -                                                                                                                                                                     | , 3 Positive Inpu                                                                                                    |                                                                                                                                 | mple B hit                                                                                                      |                                                                              |                                          |  |

| DILO                                                                                                                                                                                                                               |                                                                                                                                   | 11> for bit sele                                                                                                                                                      | •                                                                                                                    |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| bit 7-5                                                                                                                                                                                                                            |                                                                                                                                   | ited: Read as                                                                                                                                                         |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

| bit 4-3                                                                                                                                                                                                                            | -                                                                                                                                 |                                                                                                                                                                       | 1, 2, 3 Positive                                                                                                     | Input Select fo                                                                                                                 | or Sample A bits                                                                                                | 3                                                                            |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       | s AN0 (Op Amp                                                                                                        |                                                                                                                                 | -                                                                                                               |                                                                              | , CH3 positiv                            |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   | s AN6 (Op An                                                                                                                                                          |                                                                                                                      | <i>/</i> ·                                                                                                                      | •                                                                                                               |                                                                              |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                                                                       |                                                                                                                      |                                                                                                                                 |                                                                                                                 |                                                                              |                                          |  |

|                                                                                                                                                                                                                                    |                                                                                                                                   | ositive input is                                                                                                                                                      | AN3 (Op Amp 1                                                                                                        | I), CH2 positive                                                                                                                | e input is AN0 (0                                                                                               | Op Amp 2), CH3                                                               | -                                        |  |