Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm002-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

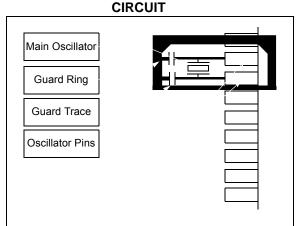

# 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

# FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

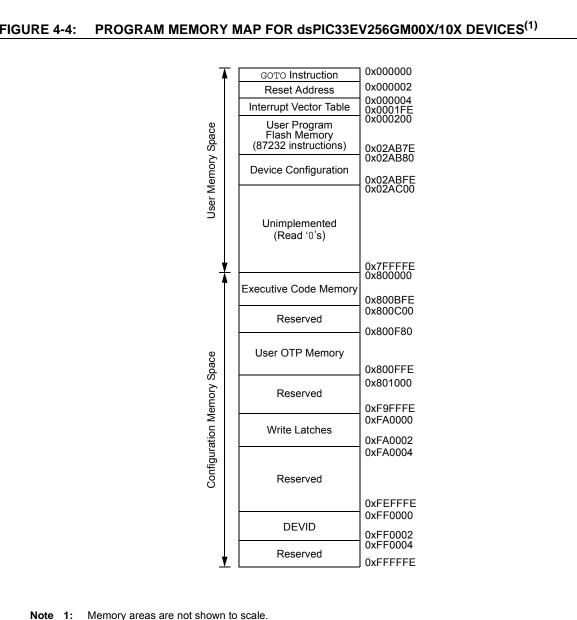

#### FIGURE 4-4:

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

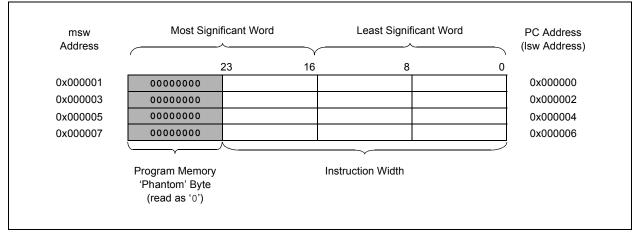

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-5).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with the Data Memory Space Addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EVXXXGM00X/10X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000 of Flash memory, with the actual address for the start of code at address, 0x000002 of Flash memory.

For more information on the Interrupt Vector Tables, see **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

| TABLE 4     | -9:   | CAN1     | I REGIS  | STER M   | AP WHE   | N WIN (  | C1CTR    | L<0>) =  | 0 <b>OR</b> 1 | FOR ds   | PIC33E   | VXXXGN   | 110X DE  | VICES    |            |          |          |               |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|---------------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8         | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1     | 0400  | _        | —        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0        | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | —          | -        | WIN      | 0480          |

| C1CTRL2     | 0402  | _        | —        | —        | —        | _        | —        | —        | —             | —        | —        | _        |          | l        | DNCNT<4:0> |          |          | 0000          |

| C1VEC       | 0404  | —        | _        | —        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0       | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0000          |

| C1FCTRL     | 0406  | DMABS2   | DMABS1   | DMABS0   | _        | _        | —        | —        | —             | _        | —        | FSA5     | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO      | 0408  | -        | —        | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0          | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF      | 040A  | -        | —        | ТХВО     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN         | IVRIF    | WAKIF    | ERRIF    | —        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE      | 040C  |          | —        | —        | -        | —        | —        | —        | —             | IVRIE    | WAKIE    | ERRIE    | —        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC        | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0      | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1      | 0410  |          | —        | —        | -        | —        | —        | —        | —             | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2      | 0412  |          | WAKFIL   | —        | -        | —        | SEG2PH2  | SEG2PH1  | SEG2PH0       | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1      | 0414  |          |          |          |          |          |          |          | FLTE          | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1  | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0        | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2  | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0       | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-10: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14                          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7       | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|---------------------------------|---------|--------|--------|--------|---------|---------------|-------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |        |                                 |         |        |        |        | Se      | ee definition | when WIN :  | = x     |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |        |                                 |         |        |        |        |         | RXFUL         | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C1RXFUL2    | 0422          |        |                                 |         |        |        |        |         | RXFUL         | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1RXOVF1    | 0428          |        |                                 |         |        |        |        |         | RXOVF         | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C1RXOVF2    | 042A          |        |                                 |         |        |        |        |         | RXOVF         | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1TR01CON   | 0430          | TXEN1  | TXABT1                          | TXLARB1 | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0       | TXEN0       | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3  | TXABT3                          | TXLARB3 | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0       | TXEN2       | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5  | TXABT5                          | TXLARB5 | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0       | TXEN4       | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7  | TXABT7                          | TXLARB7 | TXERR7 | TXREQ7 | RTREN7 | TX7PRI1 | TX7PRI0       | TXEN6       | TXABAT6 | TXLARB6 | TXERR6 | TXREQ6 | RTREN6 | TX6PRI1 | TX6PRI0 | xxxx          |

| C1RXD       | 0440          |        | CAN1 Receive Data Word Register |         |        |        |        |         |               |             |         | xxxx    |        |        |        |         |         |               |

| C1TXD       | 0442          |        |                                 |         |        |        |        | CAN1    | Transmit Da   | ata Word Re | egister |         |        |        |        |         |         | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

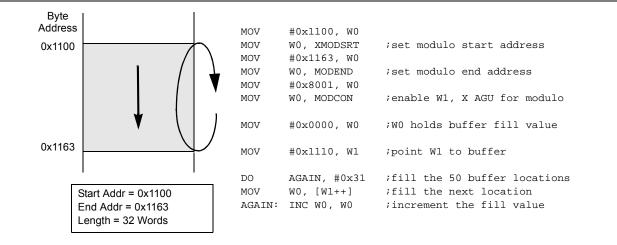

# 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the SFP and SSP, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit (MODCON<15>) is set

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

Figure 4-15 shows an example of Modulo Addressing operation.

Note: Y Data Space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

#### FIGURE 4-15: MODULO ADDRESSING OPERATION EXAMPLE

#### REGISTER 8-5: DMAxSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0      | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|--------|-------|-------|-------|

| —        | —     | —     | —     | —      | —     | —     | —     |

| bit 15   |       |       |       |        | •     |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | STB<2 | 23:16> |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

|          |       |       |       |        |       |       |       |

| l egend. |       |       |       |        |       |       |       |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

### REGISTER 8-6: DMAxSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                    |       |              | STB   | <15:8>                                  |       |       |       |  |  |

| bit 15                             |       |              |       |                                         |       |       | bit 8 |  |  |

|                                    |       |              |       |                                         |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |              | STE   | 3<7:0>                                  |       |       |       |  |  |

| bit 7                              |       |              |       |                                         |       |       | bit 0 |  |  |

|                                    |       |              |       |                                         |       |       |       |  |  |

| Legend:                            |       |              |       |                                         |       |       |       |  |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-0 STB<15:0>: DMA Secondary Start Address bits (source or destination)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | -   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0    | U-0 | U-0 | U-0 | R-0 | R-0 | R-0 | R-0   |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| U-0   | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                  |

|----------|---------------------------------------------------------------------------------------------|

| bit 3    | PPST3: Channel 3 Ping-Pong Mode Status Flag bit                                             |

|          | <ul><li>1 = DMA3STB register is selected</li><li>0 = DMA3STA register is selected</li></ul> |

| bit 2    | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                             |

|          | 1 = DMA2STB register is selected                                                            |

|          | 0 = DMA2STA register is selected                                                            |

| bit 1    | <b>PPST1:</b> Channel 1 Ping-Pong Mode Status Flag bit                                      |

|          | 1 = DMA1STB register is selected                                                            |

|          | 0 = DMA1STA register is selected                                                            |

| bit 0    | <b>PPST0:</b> Channel 0 Ping-Pong mode Status Flag bit                                      |

|          | 1 = DMA0STB register is selected                                                            |

|          | 0 = DMA0STA register is selected                                                            |

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits <sup>(4)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111 = Reserved                                                                                                                                                           |

|         | 11110 = Reserved                                                                                                                                                           |

|         | 1110 = Reserved                                                                                                                                                            |

|         | 11100 = CTMU trigger is the source for the capture timer synchronization                                                                                                   |

|         | 11011 = ADC1 interrupt is the source for the capture timer synchronization <sup>(5)</sup>                                                                                  |

|         | 11010 = Analog Comparator 3 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11001 = Analog Comparator 2 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11000 = Analog Comparator 1 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10111 = Analog Comparator 5 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10110 = Analog Comparator 4 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10101 = Reserved                                                                                                                                                           |

|         | 10100 = Reserved                                                                                                                                                           |

|         | 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 01111 = GP Timer5 is the source for the capture timer synchronization                                                                                                      |

|         | 01110 = GP Timer4 is the source for the capture timer synchronization                                                                                                      |

|         | 01101 = GP Timer3 is the source for the capture timer synchronization                                                                                                      |

|         | 01100 = GP Timer2 is the source for the capture timer synchronization                                                                                                      |

|         | 01011 = GP Timer1 is the source for the capture timer synchronization                                                                                                      |

|         | 01010 = Reserved                                                                                                                                                           |

|         | 01001 = Reserved                                                                                                                                                           |

|         | 01000 = Input Capture 4 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00111 = Input Capture 3 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00101 = Input Capture 1 is the source for the capture timer synchronization <sup>(6)</sup><br>00100 = Output Compare 4 is the source for the capture timer synchronization |

|         | 00011 = Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00011 – Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00001 = Output Compare 1 is the source for the capture timer synchronization                                                                                               |

|         | 00000 = Reserved                                                                                                                                                           |

|         |                                                                                                                                                                            |

| Note 1: | The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.                                                                                              |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

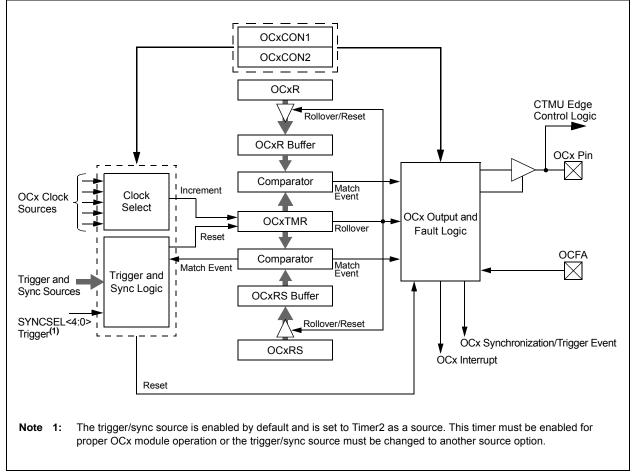

# 16.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70005157) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support up to 4 output compare modules. The output compare module can select one of eight available clock

sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Figure 16-1 shows a block diagram of the output compare module.

Note: For more information on OCxR and OCxRS register restrictions, refer to the "Output Compare" (DS70005157) section in the "dsPIC33/PIC24 Family Reference Manual".

| R/W-0         | U-0                                                                                                                                    | R/W-0                                | U-0                       | R/W-0            | R/W-0                               | R/W-0                | R/W-0   |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|------------------|-------------------------------------|----------------------|---------|--|--|--|--|

| SNTEN         | —                                                                                                                                      | SNTSIDL                              | —                         | RCVEN            | TXM <sup>(1)</sup>                  | TXPOL <sup>(1)</sup> | CRCEN   |  |  |  |  |

| bit 15        |                                                                                                                                        |                                      |                           |                  |                                     |                      | bit     |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                  | U-0                                  | R/W-0                     | U-0              | R/W-0                               | R/W-0                | R/W-0   |  |  |  |  |

| PPP           | SPCEN <sup>(2)</sup>                                                                                                                   |                                      | PS                        | _                | NIBCNT2                             | NIBCNT1              | NIBCNT0 |  |  |  |  |

| bit 7         |                                                                                                                                        |                                      |                           |                  |                                     |                      | bit     |  |  |  |  |

| Legend:       |                                                                                                                                        |                                      |                           |                  |                                     |                      |         |  |  |  |  |

| R = Readable  | e bit                                                                                                                                  | W = Writable                         | bit                       | U = Unimple      | mented bit, read                    | <b>d as</b> '0'      |         |  |  |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                     |                           | '0' = Bit is cle | eared                               | x = Bit is unkr      | nown    |  |  |  |  |

|               |                                                                                                                                        |                                      |                           |                  |                                     |                      |         |  |  |  |  |

| bit 15        | SNTEN: SEM                                                                                                                             | NTx Enable bit                       |                           |                  |                                     |                      |         |  |  |  |  |

|               | 1 = SENTx is                                                                                                                           |                                      |                           |                  |                                     |                      |         |  |  |  |  |

|               | 0 = SENTx is                                                                                                                           |                                      |                           |                  |                                     |                      |         |  |  |  |  |

| bit 14        | -                                                                                                                                      | nted: Read as                        |                           |                  |                                     |                      |         |  |  |  |  |

| bit 13        |                                                                                                                                        | ENTx Stop in lo                      |                           |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | nues module op<br>es module opera    |                           |                  | ers Idle mode                       |                      |         |  |  |  |  |

| bit 12        | Unimplemer                                                                                                                             | nted: Read as                        | ʻ0'                       |                  |                                     |                      |         |  |  |  |  |

| bit 11        | RCVEN: SEI                                                                                                                             | NTx Receive E                        | nable bit                 |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | perates as a re                      |                           |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | perates as a tr                      |                           | nsor)            |                                     |                      |         |  |  |  |  |

| bit 10        | <b>TXM:</b> SENTx Transmit Mode bit <sup>(1)</sup><br>1 = SENTx transmits data frame only when triggered using the SYNCTXEN status bit |                                      |                           |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | ransmits data fi<br>ransmits data fi |                           |                  |                                     | KEN status bit       |         |  |  |  |  |

| bit 9         |                                                                                                                                        | NTx Transmit P                       |                           |                  |                                     |                      |         |  |  |  |  |

| bit 5         |                                                                                                                                        | lata output pin i                    | -                         | lle state        |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | lata output pin i                    |                           |                  |                                     |                      |         |  |  |  |  |

| bit 8         | CRCEN: CR                                                                                                                              | C Enable bit                         |                           |                  |                                     |                      |         |  |  |  |  |

|               | 1 = SENTx p                                                                                                                            |                                      | verification on           |                  | using the prefer                    | red J2716 meth       | od      |  |  |  |  |

|               |                                                                                                                                        | loes not perforr<br>ansmit Mode (F   |                           | ation on receiv  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        |                                      |                           | using the pref   | erred J2716 me                      | thod                 |         |  |  |  |  |

|               |                                                                                                                                        | loes not calcula                     |                           | 0 1              |                                     |                      |         |  |  |  |  |

| bit 7         | PPP: Pause                                                                                                                             | Pulse Present                        | bit                       |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        |                                      |                           |                  | sages with paus<br>sages without pa |                      |         |  |  |  |  |

| bit 6         | SPCEN: Sho                                                                                                                             | ort PWM Code                         | Enable bit <sup>(2)</sup> |                  |                                     |                      |         |  |  |  |  |

|               |                                                                                                                                        | trol from exterr<br>trol from exterr |                           |                  |                                     |                      |         |  |  |  |  |

| bit 5         | Unimplemer                                                                                                                             | nted: Read as                        | ʻ0'                       |                  |                                     |                      |         |  |  |  |  |

| bit 4         | PS: SENTX I                                                                                                                            | Module Clock F                       | Prescaler (divi           | der) bits        |                                     |                      |         |  |  |  |  |

|               | 1 = Divide-by                                                                                                                          |                                      |                           |                  |                                     |                      |         |  |  |  |  |

|               | 0 = Divide-by                                                                                                                          | /-1                                  |                           |                  |                                     |                      |         |  |  |  |  |

| Note 1: Th    | iis bit has no fur                                                                                                                     | nction in Receiv                     | ve mode (RC\              | /EN = 1).        |                                     |                      |         |  |  |  |  |

| <b>2</b> • Th | us bit has no fur                                                                                                                      | nction in Transr                     | nit mode (RC)             | VEN = 0          |                                     |                      |         |  |  |  |  |

#### REGISTER 20-1: SENTxCON1: SENTx CONTROL REGISTER 1

2: This bit has no function in Transmit mode (RCVEN = 0).

| R/W-0                              | R/W-0                                                                                                                                                        | R/W-0                                                 | R/W-0                                   | R/W-0              | R/W-0                | R/W-0                | R/W-0                |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|--------------------|----------------------|----------------------|----------------------|

| CSS31                              | CSS30                                                                                                                                                        | CSS29                                                 | CSS28                                   | CSS27              | CSS26 <sup>(1)</sup> | CSS25 <sup>(1)</sup> | CSS24 <sup>(1)</sup> |

| bit 15                             |                                                                                                                                                              |                                                       |                                         |                    |                      |                      | bit 8                |

|                                    |                                                                                                                                                              |                                                       |                                         |                    |                      |                      |                      |

| U-0                                | U-0                                                                                                                                                          | U-0                                                   | U-0                                     | R/W-0              | R/W-0                | R/W-0                | R/W-0                |

|                                    | <u> </u>                                                                                                                                                     |                                                       |                                         | CSS19              | CSS18                | CSS17                | CSS16                |

| bit 7                              |                                                                                                                                                              |                                                       |                                         |                    |                      |                      | bit                  |

| Legend:                            |                                                                                                                                                              |                                                       |                                         |                    |                      |                      |                      |

| R = Readable                       | e bit                                                                                                                                                        | W = Writable                                          | bit                                     | U = Unimple        | mented bit, read     | <b>d as</b> '0'      |                      |

| -n = Value at POR '1' = Bit is set |                                                                                                                                                              | '0' = Bit is cleared                                  |                                         | x = Bit is unknown |                      |                      |                      |

| bit 15                             | 1 = Selects A                                                                                                                                                | x Input Scan S<br>Nx for input sc<br>x for input scar | an                                      |                    |                      |                      |                      |

| bit 14                             | <b>CSS30:</b> ADC<br>1 = Selects A                                                                                                                           | x Input Scan S<br>Nx for input sc<br>x for input scar | election bit<br>an                      |                    |                      |                      |                      |

| bit 13                             | CSS29: ADCx Input Scan Selection bits<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan                                                      |                                                       |                                         |                    |                      |                      |                      |

| bit 12                             | <b>CSS28:</b> ADC:<br>1 = Selects A                                                                                                                          | x Input Scan S<br>Nx for input sc<br>x for input scar | election bit<br>an                      |                    |                      |                      |                      |

| bit 11                             | <b>CSS27:</b> ADC<br>1 = Selects A                                                                                                                           | x Input Scan S<br>Nx for input sc<br>x for input scar | election bit<br>an                      |                    |                      |                      |                      |

| bit 10                             | <b>CSS26:</b> ADCx Input Scan Selection bit <sup>(1)</sup><br>1 = Selects OA3/AN6 for input scan<br>0 = Skips OA3/AN6 for input scan                         |                                                       |                                         |                    |                      |                      |                      |

| bit 9                              | <b>CSS25:</b> ADC:<br>1 = Selects O                                                                                                                          | x Input Scan S<br>A2/AN0 for inp<br>2/AN0 for inpu    | election bit <sup>(1)</sup><br>out scan |                    |                      |                      |                      |

| bit 8                              | <ul> <li>CSS24: ADCx Input Scan Selection bit<sup>(1)</sup></li> <li>1 = Selects OA1/AN3 for input scan</li> <li>0 = Skips OA1/AN3 for input scan</li> </ul> |                                                       |                                         |                    |                      |                      |                      |

| bit 7-4                            | •                                                                                                                                                            | ted: Read as '                                        |                                         |                    |                      |                      |                      |

| bit 3                              | CSS19: ADC                                                                                                                                                   | x Input Scan S                                        | election bit                            |                    |                      |                      |                      |

|                                    |                                                                                                                                                              | Nx for input sc<br>x for input scar                   |                                         |                    |                      |                      |                      |

| bit 2                              | <b>CSS18:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan                                                |                                                       |                                         |                    |                      |                      |                      |

# REGISTER 24-7: ADxCSSH: ADCx INPUT SCAN SELECT REGISTER HIGH<sup>(2)</sup>

2: All bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                                                                                                                 |  |

|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol Characteristic() |                                                                                                                                                                                                                                                                                       | Min. | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                      |  |

| SY00               | Tpu                     | Power-up Period                                                                                                                                                                                                                                                                       | —    | 400                 | 600  | μs    |                                                                                                                 |  |

| SY10               | Tost                    | Oscillator Start-up<br>Time                                                                                                                                                                                                                                                           | —    | 1024 Tos<br>c       | —    | —     | Tosc = OSC1 period                                                                                              |  |

| SY11               | TPWRT                   | Power-up Timer<br>Period                                                                                                                                                                                                                                                              | —    | 1                   | —    | ms    | Using LPRC parameters indicated in F21a/F21b (see Table 30-20)                                                  |  |

| SY12 Twdt          |                         | Watchdog Timer<br>Time-out Period                                                                                                                                                                                                                                                     | 0.8  | _                   | 1.2  | ms    | WDTPRE = 0, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |

|                    |                         |                                                                                                                                                                                                                                                                                       | 3.2  | _                   | 4.8  | ms    | WDTPRE = 1, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |

| SY13               | Tioz                    | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer<br>Reset                                                                                                                                                                                                                     | 0.68 | 0.72                | 1.2  | μs    |                                                                                                                 |  |

| SY20               | TMCLR                   | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                | 2    | —                   | -    | μs    |                                                                                                                 |  |

| SY30               | TBOR                    | BOR Pulse Width<br>(low)                                                                                                                                                                                                                                                              | 1    | —                   | _    | ms    |                                                                                                                 |  |

| SY35               | TFSCM                   | Fail-Safe Clock<br>Monitor Delay                                                                                                                                                                                                                                                      | —    | 500                 | 900  | μs    | -40°C to +85°C                                                                                                  |  |

| SY36               | TVREG                   | Voltage Regulator<br>Standby-to-Active<br>mode Transition Time                                                                                                                                                                                                                        | —    | —                   | 30   | μs    |                                                                                                                 |  |

| SY37               | TOSCDFRC                | FRC Oscillator<br>Start-up Delay                                                                                                                                                                                                                                                      | 46   | 48                  | 54   | μs    |                                                                                                                 |  |

| SY38               | Toscdlprc               | LPRC Oscillator<br>Start-up Delay                                                                                                                                                                                                                                                     | —    |                     | 70   | μs    |                                                                                                                 |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

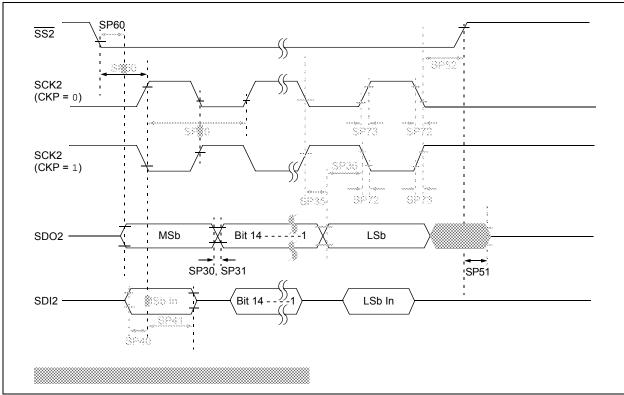

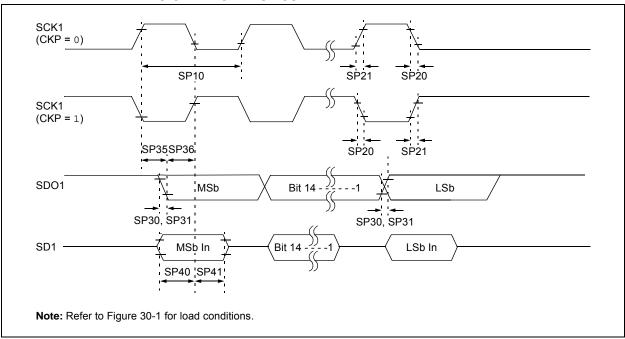

# FIGURE 30-16: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

#### TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                              | CKE | СКР | SMP |  |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |  |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |  |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |  |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |  |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |  |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |  |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |  |

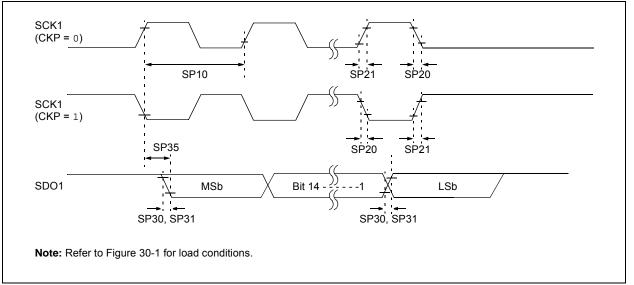

#### FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

#### FIGURE 30-23: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# dsPIC33EVXXXGM00X/10X FAMILY

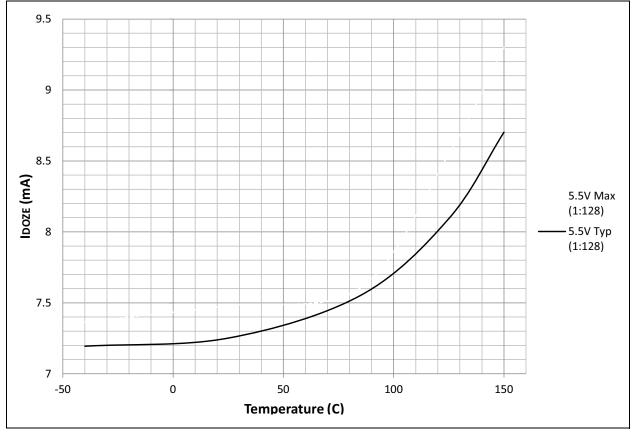

FIGURE 33-12: TYPICAL/MAXIMUM IDOZE vs. TEMPERATURE (DOZE 1:128, 70 MIPS)

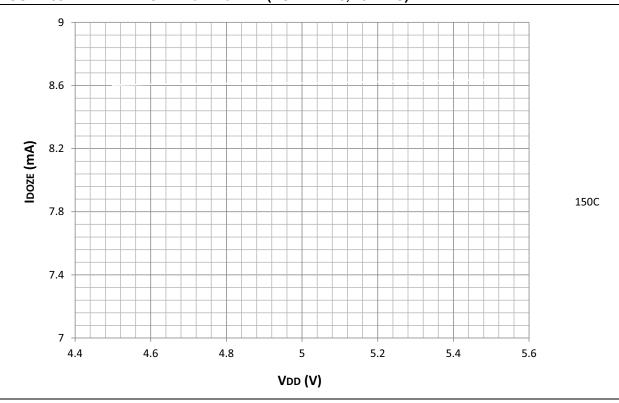

FIGURE 33-11: TYPICAL IDOZE vs. VDD (DOZE 1:128, 70 MIPS)

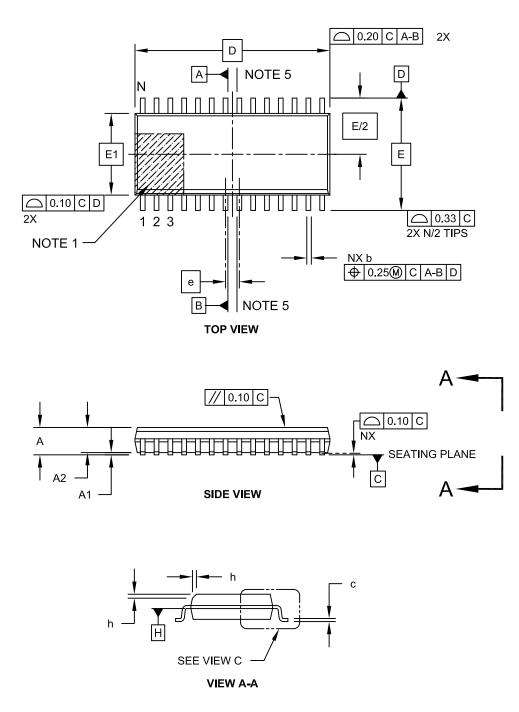

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

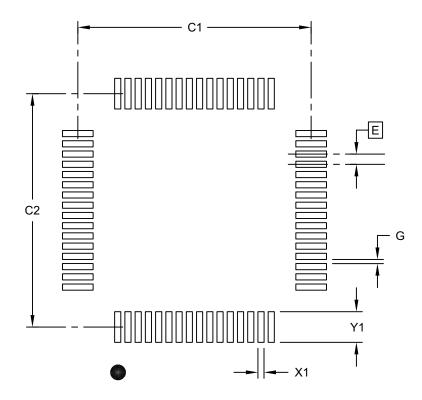

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension Limits         |             | MIN  | NOM      | MAX  |

| Contact Pitch            | E           |      | 0.50 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X28)  | X1          |      |          | 0.30 |

| Contact Pad Length (X28) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2085B Sheet 1 of 1

# **Revision E (September 2016)**

This revision incorporates the following updates:

- Sections:

- Added new Section 32.0 "Characteristics for Industrial/Extended Temperature Devices (-40°C to +125°C)" and Section 33.0 "Characteristics for High-Temperature Devices (+150°C)".

- Updated the Qualification and Class B Support section.

- Updated Section 27.6 "In-Circuit Serial Programming".

- Updated **Section 34.0** "**Packaging Information**" with the addition of the 28-Lead SSOP package information and new packaging diagram revisions.

- Updated the "**Product Identification System**" section with the addition of the 28-Lead SSOP package.

- · Figures:

- Updated Figure 4-6.

- Registers:

- Updated Register 25-2, Register 25-3, Register 27-1 and Register 27-2.

- Tables:

- Updated Table 30-7, Table 30-9, Table 30-39, Table 30-40, Table 30-41, Table 30-42, Table 30-43, Table 30-44 and Table 30-45.