#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm002-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | ••    |                   | •                 |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

|-------------|-------|-------------------|-------------------|--------|--------|--------|--------|------------|-------------|---------------|---------------|-------------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15            | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7         | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |                   | Timer1 Register   |        |        |        |        |            |             |               |               | 0000        |        |       |       |       |       |               |

| PR1         | 0102  |                   |                   |        |        |        |        |            | Peri        | od Register   | 1             |             |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON               | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |                   | Timer2 Register   |        |        |        |        |            |             |               | 0000          |             |        |       |       |       |       |               |

| TMR3HLD     | 0108  |                   |                   |        |        |        | Time   | er3 Holdin | ig Register | · (For 32-bit | timer operat  | tions only) |        |       |       |       |       | 0000          |

| TMR3        | 010A  |                   | Timer3 Register   |        |        |        |        |            |             | 0000          |               |             |        |       |       |       |       |               |

| PR2         | 010C  |                   | Period Register 2 |        |        |        |        |            |             | FFFF          |               |             |        |       |       |       |       |               |

| PR3         | 010E  | Period Register 3 |                   |        |        |        |        |            | FFFF        |               |               |             |        |       |       |       |       |               |

| T2CON       | 0110  | TON               | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON               | _                 | TSIDL  | _      | _      | _      | _          | —           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | —     | TCS   | _     | 0000          |

| TMR4        | 0114  |                   |                   |        |        |        |        |            | Tim         | ner4 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116  |                   |                   |        |        |        | Т      | imer5 Hol  | ding Regis  | ster (For 32- | bit operation | ns only)    |        |       |       |       |       | 0000          |

| TMR5        | 0118  |                   |                   |        |        |        |        |            | Tim         | ner5 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR4         | 011A  |                   |                   |        |        |        |        |            | Peri        | od Register   | 4             |             |        |       |       |       |       | FFFF          |

| PR5         | 011C  |                   |                   |        |        |        |        |            | Peri        | od Register   | 5             |             |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON               | _                 | TSIDL  | —      | —      | —      | —          | —           | —             | TGATE         | TCKPS1      | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON               | _                 | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| Lonondi     |       |                   |                   |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

|                   | VV VVIItable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

#### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

| R/W-1        | R/W-0         | R/W-0                                 | U-0          | U-0              | U-0              | U-0             | R/W-0  |

|--------------|---------------|---------------------------------------|--------------|------------------|------------------|-----------------|--------|

| GIE          | DISI          | SWTRAP                                |              |                  | —                | —               | AIVTEN |

| bit 15       |               |                                       |              |                  |                  |                 | bit 8  |

|              |               |                                       |              |                  |                  |                 |        |

| U-0          | U-0           | U-0                                   | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —            | —             | —                                     | _            |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7        |               |                                       |              |                  |                  |                 | bit 0  |

|              |               |                                       |              |                  |                  |                 |        |

| Legend:      |               |                                       |              |                  |                  |                 |        |

| R = Readab   | le bit        | W = Writable b                        | oit          | •                | mented bit, read | as '0'          |        |

| -n = Value a | t POR         | '1' = Bit is set                      |              | '0' = Bit is cle | eared            | x = Bit is unki | nown   |

|              |               |                                       |              |                  |                  |                 |        |

| bit 15       |               | Interrupt Enable                      |              |                  |                  |                 |        |

|              |               | s and associated<br>s are disabled, b |              |                  |                  |                 |        |

| bit 14       |               | Instruction Status                    | •            | Suil enabled     |                  |                 |        |

| DIL 14       |               | struction is active                   |              |                  |                  |                 |        |

|              |               | struction is not a                    | -            |                  |                  |                 |        |

| bit 13       | SWTRAP: S     | Software Trap Sta                     | atus bit     |                  |                  |                 |        |

|              |               | e trap is enabled                     |              |                  |                  |                 |        |

|              | 0 = Software  | e trap is disabled                    |              |                  |                  |                 |        |

| bit 12-9     | Unimpleme     | nted: Read as 'o                      | כ'           |                  |                  |                 |        |

| bit 8        | AIVTEN: Alt   | ernate Interrupt                      | Vector Table | is Enabled bit   |                  |                 |        |

|              | 1 = AIVT is e |                                       |              |                  |                  |                 |        |

| L:1 7 0      | 0 = AIVT is 0 |                                       | - 1          |                  |                  |                 |        |

| bit 7-3      | -             | nted: Read as '                       |              |                  |                  |                 |        |

| bit 2        |               | ternal Interrupt 2                    | •            | t Polarity Selec | ct bit           |                 |        |

|              |               | on negative edg                       |              |                  |                  |                 |        |

| bit 1        | •             | ternal Interrupt 1                    |              | t Polarity Selec | rt bit           |                 |        |

|              |               | on negative edg                       | •            |                  |                  |                 |        |

|              |               | on positive edg                       |              |                  |                  |                 |        |

| bit 0        | INTOEP: Ext   | ternal Interrupt 0                    | Edge Detec   | t Polarity Selec | ct bit           |                 |        |

|              |               | on negative edg                       |              |                  |                  |                 |        |

|              | 0 = Interrupt | on positive edg                       | е            |                  |                  |                 |        |

|              |               |                                       |              |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0         | R/W-0                                | R/W-0                  | R/W-0                | R/W-0                             | R/W-0            | R/W-0           | R/W-1          |  |  |  |  |

|---------------|--------------------------------------|------------------------|----------------------|-----------------------------------|------------------|-----------------|----------------|--|--|--|--|

| ROI           | DOZE2 <sup>(3)</sup>                 | DOZE1 <sup>(3)</sup>   | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>            | FRCDIV2          | FRCDIV1         | FRCDIV0        |  |  |  |  |

| bit 15        |                                      | •                      | -                    | -                                 |                  | •               | bit 8          |  |  |  |  |

|               |                                      |                        | DAMO                 | D/M/ 0                            |                  | R/W-0           | DAMA           |  |  |  |  |

| R/W-0         | R/W-0                                | U-0                    | R/W-0                | R/W-0                             | R/W-0            |                 | R/W-0          |  |  |  |  |

| PLLPOST1      | PLLPOST0                             | —                      | PLLPRE4              | PLLPRE3                           | PLLPRE2          | PLLPRE1         | PLLPRE0        |  |  |  |  |

| bit 7         |                                      |                        |                      |                                   |                  |                 | bit C          |  |  |  |  |

| Legend:       |                                      |                        |                      |                                   |                  |                 |                |  |  |  |  |

| R = Readable  | bit                                  | W = Writable           | bit                  | U = Unimpler                      | nented bit, read | l as '0'        |                |  |  |  |  |

| -n = Value at | POR                                  | '1' = Bit is set       |                      | '0' = Bit is cle                  | ared             | x = Bit is unkr | nown           |  |  |  |  |

| bit 15        |                                      | on Interrupt b         | i+                   |                                   |                  |                 |                |  |  |  |  |

|               |                                      | will clear the E       |                      |                                   |                  |                 |                |  |  |  |  |

|               |                                      | have no effect         |                      | N bit                             |                  |                 |                |  |  |  |  |

| bit 14-12     | •                                    | Processor Clo          |                      |                                   |                  |                 |                |  |  |  |  |

|               | 111 = FCY div                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 110 = FCY div                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 101 = FCY div                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 100 = FCY div<br>011 = FCY div       |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               |                                      | 010 = FCY divided by 4 |                      |                                   |                  |                 |                |  |  |  |  |

|               | 001 = FCY div                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               |                                      | vided by 1 (def        |                      |                                   |                  |                 |                |  |  |  |  |

| bit 11        |                                      | e Mode Enable          |                      |                                   |                  |                 |                |  |  |  |  |

|               |                                      |                        |                      | tween the peri<br>atio are forced |                  | nd the process  | or clocks      |  |  |  |  |

| bit 10-8      | FRCDIV<2:0>                          | -: Internal Fast       | RC Oscillator        | Postscaler bit                    | S                |                 |                |  |  |  |  |

|               | 111 <b>= FRC d</b> i                 | vided by 256           |                      |                                   |                  |                 |                |  |  |  |  |

|               | 110 <b>= FRC di</b>                  |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 101 = FRC di                         | •                      |                      |                                   |                  |                 |                |  |  |  |  |

|               | 100 = FRC di<br>011 = FRC di         |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 010 = FRC di                         |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               |                                      | vided by 2 (de         | fault)               |                                   |                  |                 |                |  |  |  |  |

|               | 000 <b>= FRC di</b>                  | •                      |                      |                                   |                  |                 |                |  |  |  |  |

| bit 7-6       | PLLPOST<1:                           | 0>: PLL VCO            | Output Divide        | r Select bits (al                 | so denoted as    | 'N2', PLL posts | caler)         |  |  |  |  |

|               | 11 = Output d                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 10 = Reserve<br>01 = Output d        |                        |                      |                                   |                  |                 |                |  |  |  |  |

|               | 00 = Output d                        |                        |                      |                                   |                  |                 |                |  |  |  |  |

| bit 5         | -                                    | ted: Read as '         | 0'                   |                                   |                  |                 |                |  |  |  |  |

| Note 1: Th    | is bit is cleared v                  | when the ROI           | bit is set and a     | an interrupt occ                  | urs.             |                 |                |  |  |  |  |

| <b>2:</b> Th  | is register resets                   | s only on a Pov        | wer-on Reset         | (POR).                            |                  |                 |                |  |  |  |  |

|               | )ZE<2:0> bits ca<br>)ZE<2:0> are igi |                        | en to when th        | e DOZEN bit is                    | clear. If DOZE   | N = 1, any wri  | tes to         |  |  |  |  |

|               | o DOZEN bit cou                      |                        | 075-2.05 -           |                                   | 2.0 > - 0.00 on  | attempt by up   | or ooftwara to |  |  |  |  |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0                               | U-0                        | U-0                                                       | U-0                        | U-0              | U-0              | U-0             | U-0   |  |  |  |

|-----------------------------------|----------------------------|-----------------------------------------------------------|----------------------------|------------------|------------------|-----------------|-------|--|--|--|

| —                                 | —                          | —                                                         | —                          |                  | —                | —               | —     |  |  |  |

| bit 15                            |                            |                                                           |                            |                  |                  |                 | bit 8 |  |  |  |

|                                   |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

| U-0                               | U-0                        | U-0                                                       | R/W-0                      | U-0              | U-0              | U-0             | U-0   |  |  |  |

| —                                 | —                          | —                                                         | DMA0MD <sup>(1)</sup>      | —                | —                | —               | —     |  |  |  |

|                                   |                            |                                                           | DMA1MD <sup>(1)</sup>      | -                |                  |                 |       |  |  |  |

|                                   |                            |                                                           | DMA2MD <sup>(1)</sup>      | -                |                  |                 |       |  |  |  |

|                                   |                            |                                                           | DMA3MD <sup>(1)</sup>      |                  |                  |                 |       |  |  |  |

| bit 7                             |                            |                                                           |                            |                  |                  |                 | bit 0 |  |  |  |

|                                   |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

| Legend:                           |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

| R = Readable bit W = Writable bit |                            |                                                           |                            | •                | nented bit, read |                 |       |  |  |  |

| -n = Value a                      | at POR                     | '1' = Bit is se                                           | et                         | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |  |  |  |

|                                   |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

| bit 15-5                          | Unimplement                |                                                           |                            |                  |                  |                 |       |  |  |  |

| bit 4                             | DMA0MD: DN                 |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   | 1 = DMA0 mo<br>0 = DMA0 mo |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   | DMA1MD: DN                 |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   |                            | 1 = DMA1 module is disabled<br>0 = DMA1 module is enabled |                            |                  |                  |                 |       |  |  |  |

|                                   | DMA2MD: DA                 | DMA2MD: DMA2 Module Disable bit <sup>(1)</sup>            |                            |                  |                  |                 |       |  |  |  |

|                                   | 1 = DMA2 mo                |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   | 0 = DMA2 module is enabled |                                                           |                            |                  |                  |                 |       |  |  |  |

|                                   | DMA3MD: DN                 | MA3 Module E                                              | Disable bit <sup>(1)</sup> |                  |                  |                 |       |  |  |  |

|                                   | 1 = DMA3 mo<br>0 = DMA3 mo |                                                           |                            |                  |                  |                 |       |  |  |  |

| bit 3-0                           | Unimplement                | ted: Read as                                              | <b>'</b> 0 <b>'</b>        |                  |                  |                 |       |  |  |  |

|                                   |                            |                                                           |                            |                  |                  |                 |       |  |  |  |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

**Note 1:** This single bit enables and disables all four DMA channels.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , <b>read as</b> '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP49R<5:0>:** Peripheral Output Function is Assigned to RP49 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits

(see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

#### REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. For more information, refer to the SPI specifications in Section 30.0 "Electrical Characteristics".

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

## 19.2 I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1

| R/W-0        | U-0 | R/W-0   | R/S-1                 | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------------|-----|---------|-----------------------|--------|-------|--------|-------|

| I2CEN        |     | I2CSIDL | SCLREL <sup>(1)</sup> | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 bit 8 |     |         |                       |        |       |        |       |

| R/W-0       | R/W-0 | R/W-0 | R/W-0, HC |  |

|-------------|-------|-------|-----------|-----------|-----------|-----------|-----------|--|

| GCEN        | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |  |

| bit 7 bit 0 |       |       |           |           |           |           |           |  |

| Legend:           | d: S = Settable bit HC = Hardware Clearable bit |                               |                    |

|-------------------|-------------------------------------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                | U = Unimplemented bit, read a | <b>as</b> '0'      |

| -n = Value at POR | '1' = Bit is set                                | '0' = Bit is cleared          | k = Bit is unknown |

| bit 15  | I2CEN: I2Cx Enable bit (writable from SW only)                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables the I<sup>2</sup>C module and configures the SDAx and SCLx pins as serial port pins</li> <li>0 = Disables the I<sup>2</sup>C module and all I<sup>2</sup>C pins are controlled by port functions</li> </ul> |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                       |

| bit 13  | I2CSIDL: I2Cx Stop in Idle Mode bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                      |

| bit 12  | SCLREL: SCLx Release Control bit (I <sup>2</sup> C Slave mode only) <sup>(1)</sup>                                                                                                                                               |

|         | Module resets and (I2CEN = 0) sets SCLREL = 1.                                                                                                                                                                                   |

|         | $\frac{\text{If STREN = }0}{2}$                                                                                                                                                                                                  |

|         | 1 = Releases clock                                                                                                                                                                                                               |

|         | 0 = Forces clock low (clock stretch)                                                                                                                                                                                             |

|         | If STREN = 1:<br>1 = Releases clock                                                                                                                                                                                              |

|         | 0 = Holds clock low (clock stretch); user may program this bit to '0', clock stretch at the next SCLx low                                                                                                                        |

| bit 11  | STRICT: Strict I <sup>2</sup> C Reserved Address Rule Enable bit                                                                                                                                                                 |

|         | 1 = Strict reserved addressing is enforced                                                                                                                                                                                       |

|         | In Slave mode, the device does not respond to reserved address space and addresses falling in that category are NACKed.                                                                                                          |

|         | 0 = Reserved addressing would be Acknowledged                                                                                                                                                                                    |

|         | In Slave mode, the device will respond to an address falling in the reserved address space. When there is a match with any of the reserved addresses, the device will generate an ACK.                                           |

| bit 10  | A10M: 10-Bit Slave Address Flag bit                                                                                                                                                                                              |

|         | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                                                                    |

| bit 9   | DISSLW: Slew Rate Control Disable bit                                                                                                                                                                                            |

|         | <ul> <li>1 = Slew rate control is disabled for Standard Speed mode (100 kHz, also disabled for 1 MHz mode)</li> <li>0 = Slew rate control is enabled for High-Speed mode (400 kHz)</li> </ul>                                    |

| bit 8   | SMEN: SMBus Input Levels Enable bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Enables the input logic so thresholds are compliant with the SMBus specification</li> <li>0 = Disables the SMBus-specific inputs</li> </ul>                                                                         |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                 |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

#### REGISTER 24-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:                                                                                                                                                         |

|         | 111 = Reserved<br>110 = Reserved                                                                                                                                      |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Reserved                                                                                                                                                        |

|         | 011 = Reserved                                                                                                                                                        |

|         | 010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | If SSRCG = 0:                                                                                                                                                         |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                             |

|         | 110 = CTMU ends sampling and starts conversion                                                                                                                        |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Timer5 compare ends sampling and starts conversion                                                                                                              |

|         | 011 = PWM primary Special Event Trigger ends sampling and starts conversion<br>010 = Timer3 compare ends sampling and starts conversion                               |

|         | 001 = Active transition on the INTO pin ends sampling and starts conversion                                                                                           |

|         | 000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)                                                                                |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                |

| 511 4   | See SSRC<2:0> for details.                                                                                                                                            |

| h # 0   |                                                                                                                                                                       |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                    |

|         | In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':<br>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x) or samples CH0 and CH1 |

|         | simultaneously (when CHPS<1:0> = 01)                                                                                                                                  |

|         | 0 = Samples multiple channels individually in sequence                                                                                                                |

| bit 2   | ASAM: ADCx Sample Auto-Start bit                                                                                                                                      |

|         | 1 = Sampling begins immediately after last conversion; SAMP bit is auto-set                                                                                           |

|         | 0 = Sampling begins when SAMP bit is set                                                                                                                              |

| bit 1   | SAMP: ADCx Sample Enable bit                                                                                                                                          |

|         | 1 = ADCx Sample-and-Hold amplifiers are sampling                                                                                                                      |

|         | 0 = ADCx Sample-and-Hold amplifiers are holding                                                                                                                       |

|         | If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If                                                                  |

|         | SSRC<2:0> = 000, software can write '0' to end sampling and start conversion. If SSRC<2:0> $\neq$ 000,                                                                |

|         | automatically cleared by hardware to end sampling and start conversion.                                                                                               |

| bit 0   | DONE: ADCx Conversion Status bit <sup>(1)</sup>                                                                                                                       |

|         | 1 = ADCx conversion cycle is completed.                                                                                                                               |

|         | 0 = ADCx conversion has not started or is in progress                                                                                                                 |

|         | Automatically set by hardware when conversion is complete. Software can write '0' to clear DONE bit                                                                   |

|         | status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress.                                                              |

|         | Automatically cleared by hardware at the start of a new conversion.                                                                                                   |

**Note 1:** Do not clear the DONE bit in software if auto-sample is enabled (ASAM = 1).

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |

|--------------------|----------------------|-----------------|----------------|---------------------------------------|---------------|----------------|--------------------------|--|

| 63                 | RETLW                | RETLW           | #lit10,Wn      | Return with literal in Wn             | 1             | 6 (5)          | SFA                      |  |

| 64                 | RETURN               | RETURN          |                | Return from Subroutine                | 1             | 6 (5)          | SFA                      |  |

| 65                 | RLC                  | RLC             | f              | f = Rotate Left through Carry f       | 1             | 1              | C,N,Z                    |  |

|                    |                      | RLC             | f,WREG         | WREG = Rotate Left through Carry f    | 1             | 1              | C,N,Z                    |  |

|                    |                      | RLC             | Ws,Wd          | Wd = Rotate Left through Carry Ws     | 1             | 1              | C,N,Z                    |  |

| 66                 | RLNC                 | RLNC            | f              | f = Rotate Left (No Carry) f          | 1             | 1              | N,Z                      |  |

|                    |                      | RLNC            | f,WREG         | WREG = Rotate Left (No Carry) f       | 1             | 1              | N,Z                      |  |

|                    |                      | RLNC            | Ws,Wd          | Wd = Rotate Left (No Carry) Ws        | 1             | 1              | N,Z                      |  |

| 67                 | RRC                  | RRC             | f              | f = Rotate Right through Carry f      | 1             | 1              | C,N,Z                    |  |

|                    |                      | RRC             | f,WREG         | WREG = Rotate Right through Carry f   | 1             | 1              | C,N,Z                    |  |

|                    |                      | RRC             | Ws,Wd          | Wd = Rotate Right through Carry Ws    | 1             | 1              | C,N,Z                    |  |

| 68                 | RRNC                 | RRNC            | f              | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |  |

|                    |                      | RRNC            | f,WREG         | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |  |

|                    |                      | RRNC            | Ws,Wd          | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |  |

| 69                 | SAC                  | SAC             | Acc,#Slit4,Wdo | Store Accumulator                     | 1             | 1              | None                     |  |

|                    |                      | SAC.R           | Acc,#Slit4,Wdo | Store Rounded Accumulator             | 1             | 1              | None                     |  |

| 70                 | SE                   | SE              | Ws,Wnd         | Wnd = sign-extended Ws                | 1             | 1              | C,N,Z                    |  |

| 71                 | SETM                 | SETM            | f              | f = 0xFFFF                            | 1             | 1              | None                     |  |

|                    |                      | SETM            | WREG           | WREG = 0xFFFF                         | 1             | 1              | None                     |  |

|                    |                      | SETM            | Ws             | Ws = 0xFFFF                           | 1             | 1              | None                     |  |

| 72                 | SFTAC                | SFTAC           | Acc,Wn         | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAI<br>SA,SB,SAI   |  |

|                    |                      | SFTAC           | Acc,#Slit6     | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OA<br>SA,SB,SA     |  |

| 73                 | SL                   | SL              | f              | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |  |

|                    |                      | SL              | f,WREG         | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |  |

|                    |                      | SL              | Ws,Wd          | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |  |

|                    |                      | SL              | Wb,Wns,Wnd     | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |  |

|                    |                      | SL              | Wb,#lit5,Wnd   | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |  |

| 74                 | SUB                  | SUB             | Acc            | Subtract Accumulators                 | 1             | 1              | OA,OB,OA<br>SA,SB,SA     |  |

|                    |                      | SUB             | f              | f = f – WREG                          | 1             | 1              | C,DC,N,OV,               |  |

|                    |                      | SUB             | f,WREG         | WREG = f – WREG                       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUB             | #lit10,Wn      | Wn = Wn – lit10                       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUB             | Wb,Ws,Wd       | Wd = Wb – Ws                          | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUB             | Wb,#lit5,Wd    | Wd = Wb – lit5                        | 1             | 1              | C,DC,N,OV                |  |

| 75                 | SUBB                 | SUBB            | f              | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBB            | f,WREG         | WREG = $f - WREG - (\overline{C})$    | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBB            | #lit10,Wn      | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBB            | Wb,Ws,Wd       | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBB            | Wb,#lit5,Wd    | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV                |  |

| 76                 | SUBR                 | SUBR            | f              | f = WREG – f                          | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBR            | f,WREG         | WREG = WREG – f                       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBR            | Wb,Ws,Wd       | Wd = Ws – Wb                          | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBR            | Wb,#lit5,Wd    | Wd = lit5 – Wb                        | 1             | 1              | C,DC,N,OV                |  |

| 77                 | SUBBR                | SUBBR           | f              | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBBR           | f,WREG         | WREG = WREG – f – $(\overline{C})$    | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBBR           | Wb,Ws,Wd       | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV                |  |

|                    |                      | SUBBR           | Wb,#lit5,Wd    | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV                |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACT                                                      | ERISTICS            |      | (unless oth | erwise state | $-40^{\circ}C \le TA \le$ | <b>V to 5.5V</b><br>+85°C for Industrial<br>+125°C for Extended |  |  |  |

|-----------------------------------------------------------------|---------------------|------|-------------|--------------|---------------------------|-----------------------------------------------------------------|--|--|--|

| Parameter<br>No.                                                | Typ. <sup>(2)</sup> | Max. | Units       | Conditions   |                           |                                                                 |  |  |  |

| Power-Down Current (IPD) – dsPIC33EVXXXGM00X/10X <sup>(1)</sup> |                     |      |             |              |                           |                                                                 |  |  |  |

| DC60d                                                           | 9.25                | 30   | μA          | -40°C        |                           |                                                                 |  |  |  |

| DC60a                                                           | 15.75               | 35   | μA          | +25°C        | E OV                      | Base Power-Down Current                                         |  |  |  |

| DC60b                                                           | 67.75               | 250  | μA          | +85°C        | 5.0V                      | Base Power-Down Current                                         |  |  |  |

| DC60c                                                           | 270                 | 750  | μA          | +125°C       |                           |                                                                 |  |  |  |

| DC61d                                                           | 1                   | 7    | μA          | -40°C        |                           |                                                                 |  |  |  |

| DC61a                                                           | 1.25                | 8    | μA          | +25°C        | 5.0V                      | Watchdog Timer Current: ∆IwDT <sup>(3)</sup>                    |  |  |  |

| DC61b                                                           | 3.5                 | 12   | μA          | +85°C        | 5.00                      |                                                                 |  |  |  |

| DC61c                                                           | 5                   | 15   | μA          | +125°C       |                           |                                                                 |  |  |  |

#### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** IPD (Sleep) current is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- **2:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

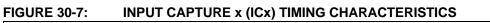

## TABLE 30-26: INPUT CAPTURE x (ICx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |    |                                  |                                   |

|--------------------|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----------------------------------|-----------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min. Max. Units Conditions                                                                                                                                                                                                                                                              |   |    |                                  | litions                           |

| IC10               | TCCL   | ICx Input Low Time             | Greater of:<br>12.5 + 25 or<br>(0.5 TCY/N) + 25                                                                                                                                                                                                                                         |   | ns | Must also meet<br>Parameter IC15 |                                   |

| IC11               | ТссН   | ICx Input High Time            | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                         | — | ns | Must also meet<br>Parameter IC15 | N = Prescaler<br>Value (1, 4, 16) |

| IC15               | ТссР   | ICx Input Period               | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                             | — | ns |                                  |                                   |

**Note 1:** These parameters are characterized but not tested in manufacturing.

## TABLE 30-36:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                      |

|--------------------|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                                                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                                                 | —                                                                                                                                                                                                                                                                                       |                     | 15   | MHz   | See Note 3                           |

| SP72               | TscF                  | SCK2 Input Fall Time                                                         | —                                                                                                                                                                                                                                                                                       | _                   |      | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCK2 Input Rise Time                                                         |                                                                                                                                                                                                                                                                                         | _                   |      | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                                                   | _                                                                                                                                                                                                                                                                                       | _                   |      | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                                                   | _                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                    | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                 | 30                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge                                   | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                      |