Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

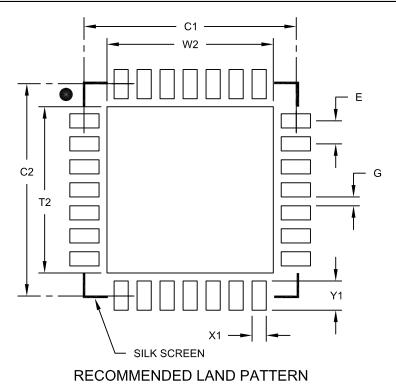

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm004-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = Overflow has not occurred for signed arithmetic                                                                                                                                                          |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                              |

| Note 1. | The IPI <2:0> hits are concatenated with the IPI 3 hit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                      |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using the bit operations.

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |                 |          |              |             |               |       | -     |           |       | -     |        |            |        |        | -      |               |

|-------------|-------|--------|-----------------|----------|--------------|-------------|---------------|-------|-------|-----------|-------|-------|--------|------------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13   | Bit 12       | Bit 11      | Bit 10        | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN            | WRERR    | NVMSIDL      | _           | _             | RPDF  | URERR | _         | —     | _     | _      | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        | NVMADR<15:0> 00 |          |              |             |               |       |       |           |       | 0000  |        |            |        |        |        |               |

| NVMADRU     | 072C  | _      | _               | _        | _            |             | _             | _     | _     |           |       |       | NVMAD  | RU<23:16>  |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _               | _        | _            |             | _             | _     | _     |           |       |       | NVMK   | EY<7:0>    |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |                 |          |              |             |               |       | NVMSF | RCADR<15: | 1>    |       |        |            |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _               | _        | _            |             | _             | _     | _     |           |       |       | NVMSRC | ADR<23:16> |        |        |        | 0000          |

| Lonondy     |       |        |                 | Desetual | an are chour | a in heaven | d a stress al |       |       |           |       |       |        |            |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       |         | _        | _        |        |           | TUN     | <5:0>   |         |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

# TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | _     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 9-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits <sup>(4)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111 = Reserved                                                                                                                                                           |

|         | 11110 = Reserved                                                                                                                                                           |

|         | 1110 = Reserved                                                                                                                                                            |

|         | 11100 = CTMU trigger is the source for the capture timer synchronization                                                                                                   |

|         | 11011 = ADC1 interrupt is the source for the capture timer synchronization <sup>(5)</sup>                                                                                  |

|         | 11010 = Analog Comparator 3 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11001 = Analog Comparator 2 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11000 = Analog Comparator 1 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10111 = Analog Comparator 5 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10110 = Analog Comparator 4 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10101 = Reserved                                                                                                                                                           |

|         | 10100 = Reserved                                                                                                                                                           |

|         | 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 01111 = GP Timer5 is the source for the capture timer synchronization                                                                                                      |

|         | 01110 = GP Timer4 is the source for the capture timer synchronization                                                                                                      |

|         | 01101 = GP Timer3 is the source for the capture timer synchronization                                                                                                      |

|         | 01100 = GP Timer2 is the source for the capture timer synchronization                                                                                                      |

|         | 01011 = GP Timer1 is the source for the capture timer synchronization                                                                                                      |

|         | 01010 = Reserved                                                                                                                                                           |

|         | 01001 = Reserved                                                                                                                                                           |

|         | 01000 = Input Capture 4 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00111 = Input Capture 3 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00101 = Input Capture 1 is the source for the capture timer synchronization <sup>(6)</sup><br>00100 = Output Compare 4 is the source for the capture timer synchronization |

|         | 00011 = Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00011 – Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00001 = Output Compare 1 is the source for the capture timer synchronization                                                                                               |

|         | 00000 = Reserved                                                                                                                                                           |

|         |                                                                                                                                                                            |

| Note 1: | The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.                                                                                              |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

# 16.1 Output Compare Control Registers

# REGISTER 16-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0          | U-0                                                                                                      | R/W-0                                                                                            | R/W-0                                                                                                           | R/W-0                                   | R/W-0            | U-0             | U-0   |

|--------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-----------------|-------|

| _            | —                                                                                                        | OCSIDL                                                                                           | OCTSEL2                                                                                                         | OCTSEL1                                 | OCTSEL0          | —               | —     |

| bit 15       |                                                                                                          |                                                                                                  |                                                                                                                 |                                         |                  |                 | bit 8 |

|              |                                                                                                          |                                                                                                  |                                                                                                                 |                                         |                  |                 |       |

| R/W-0        | U-0                                                                                                      | U-0                                                                                              | R/W-0, HSC                                                                                                      | R/W-0                                   | R/W-0            | R/W-0           | R/W-0 |

| ENFLTA       |                                                                                                          | _                                                                                                | OCFLTA                                                                                                          | TRIGMODE                                | OCM2             | OCM1            | OCM0  |

| bit 7        |                                                                                                          |                                                                                                  |                                                                                                                 |                                         |                  |                 | bit ( |

| Legend:      |                                                                                                          | HSC = Hardv                                                                                      | vare Settable/Cl                                                                                                | earable bit                             |                  |                 |       |

| R = Readabl  | e bit                                                                                                    | W = Writable                                                                                     | bit                                                                                                             | U = Unimplem                            | nented bit, read | <b>as</b> '0'   |       |

| n = Value at | POR                                                                                                      | '1' = Bit is set                                                                                 | t                                                                                                               | '0' = Bit is clea                       | ared             | x = Bit is unkn | iown  |

| bit 12-10    | OCTSEL<2:0<br>111 = Periphe<br>110 = Reserv<br>101 = Reserv<br>100 = T1CLK<br>011 = T5CLK<br>010 = T4CLK | >: Output Con<br>eral clock (FP)<br>red<br>is the clock so<br>is the clock so<br>is the clock so | inues to operate<br>npare x Clock S<br>purce of the OC<br>purce of the OC<br>purce of the OC<br>purce of the OC | elect bits<br>x (only the syn<br>x<br>x |                  | (is supported)  |       |

|              |                                                                                                          |                                                                                                  | ource of the OC                                                                                                 |                                         |                  |                 |       |

| bit 9-8      | Unimplemen                                                                                               | ted: Read as '                                                                                   | 0'                                                                                                              |                                         |                  |                 |       |

| bit 7        | 1 = Output C                                                                                             | ompare Fault                                                                                     | K Fault A Input E<br>A (OCFA) input<br>A (OCFA) input                                                           | is enabled                              |                  |                 |       |

| bit 6-5      | -                                                                                                        | ted: Read as '                                                                                   |                                                                                                                 |                                         |                  |                 |       |

| bit 4        | 1 = PWM Fa                                                                                               | ult A condition                                                                                  | ndition Status bit<br>on the OCFA pi<br>on the OCFA pi                                                          | in has occurred                         |                  |                 |       |

| bit 3        | 1 = TRIGSTA                                                                                              | AT (OCxCON2                                                                                      | Mode Select bit<br><6>) is cleared v<br>nly by software                                                         |                                         | = OCxTMR or i    | n software      |       |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

| R/W-0           | R/W-0                                      | R/W-0                                                                                                              | R/W-0                         | R/W-0                                           | R/W-0              | U-0             | U-0            |  |  |  |  |  |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------|--------------------|-----------------|----------------|--|--|--|--|--|

| PHR             | PHF                                        | PLR                                                                                                                | PLF                           | FLTLEBEN                                        | CLLEBEN            |                 | _              |  |  |  |  |  |

| bit 15          |                                            | L                                                                                                                  |                               | •                                               |                    |                 | bit 8          |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 |                    |                 |                |  |  |  |  |  |

| U-0             | U-0                                        | R/W-0                                                                                                              | R/W-0                         | R/W-0                                           | R/W-0              | R/W-0           | R/W-0          |  |  |  |  |  |

| —               |                                            | BCH <sup>(1)</sup>                                                                                                 | BCL <sup>(1)</sup>            | BPHH                                            | BPHL               | BPLH            | BPLL           |  |  |  |  |  |

| bit 7           |                                            |                                                                                                                    |                               |                                                 |                    |                 | bit (          |  |  |  |  |  |

| Legend:         |                                            |                                                                                                                    |                               |                                                 |                    |                 |                |  |  |  |  |  |

| R = Readable b  | nit                                        | W = Writable                                                                                                       | hit                           | II = I Inimpler                                 | mented bit, read   | as '0'          |                |  |  |  |  |  |

| -n = Value at P |                                            | '1' = Bit is set                                                                                                   |                               | '0' = Bit is cle                                |                    | x = Bit is unk  | nown           |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 |                    | X Bitle dill    |                |  |  |  |  |  |

| bit 15          | PHR: PWMxH                                 | Rising Edge                                                                                                        | Trigger Enabl                 | e bit                                           |                    |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 | Blanking count     | ter             |                |  |  |  |  |  |

|                 | 0 = Leading-E                              | Edge Blanking                                                                                                      | gnores the ri                 | sing edge of PV                                 | VMxH               |                 |                |  |  |  |  |  |

| bit 14          |                                            | I Falling Edge                                                                                                     |                               |                                                 |                    |                 |                |  |  |  |  |  |

|                 | 0                                          | 0                                                                                                                  | 00                            | e Leading-Edge<br>alling edge of P <sup>1</sup> | e Blanking coun    | ter             |                |  |  |  |  |  |

| bit 13          | -                                          | Rising Edge T                                                                                                      | -                             |                                                 |                    |                 |                |  |  |  |  |  |

| DIL 15          |                                            | • •                                                                                                                |                               |                                                 | Blanking count     | er              |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               | sing edge of PV                                 |                    |                 |                |  |  |  |  |  |

| bit 12          | PLF: PWMxL Falling Edge Trigger Enable bit |                                                                                                                    |                               |                                                 |                    |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 | Blanking count     | ter             |                |  |  |  |  |  |

|                 | •                                          | • •                                                                                                                | •                             | alling edge of P                                |                    |                 |                |  |  |  |  |  |

| bit 11          |                                            | .EBEN: Fault Input Leading-Edge Blanking Enable bit<br>eading-Edge Blanking is applied to the selected Fault input |                               |                                                 |                    |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               | to the selected Fa                              |                    |                 |                |  |  |  |  |  |

| bit 10          | •                                          | • •                                                                                                                |                               | Edge Blanking E                                 | •                  |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    | -                             | he selected cur                                 |                    |                 |                |  |  |  |  |  |

|                 | 0 = Leading-E                              | Edge Blanking                                                                                                      | s not applied                 | to the selected                                 | l current-limit in | put             |                |  |  |  |  |  |

| bit 9-6         | -                                          | ted: Read as '                                                                                                     |                               |                                                 |                    |                 |                |  |  |  |  |  |

| bit 5           |                                            |                                                                                                                    |                               | al High Enable                                  |                    |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               | Fault input sigr<br>ng signal is hig            | nals) when seled   | cted blanking s | signal is high |  |  |  |  |  |

| bit 4           |                                            | •                                                                                                                  |                               | al Low Enable b                                 |                    |                 |                |  |  |  |  |  |

|                 |                                            | •                                                                                                                  | •••                           |                                                 | nals) when seled   | cted blanking s | signal is low  |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               | ng signal is low                                |                    | 0               | 5              |  |  |  |  |  |

| bit 3           |                                            | ing in PWMxH                                                                                                       | -                             |                                                 |                    |                 |                |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 | nals) when the F   | PWMxH output    | is high        |  |  |  |  |  |

| h:# 0           |                                            | ng when the P                                                                                                      | -                             | -                                               |                    |                 |                |  |  |  |  |  |

| bit 2           |                                            | ng in PWMxH                                                                                                        |                               |                                                 | nals) when the F   |                 | ic low         |  |  |  |  |  |

|                 |                                            | ng when the P                                                                                                      |                               |                                                 |                    | www.kirioutput  | . 15 10 W      |  |  |  |  |  |

| bit 1           |                                            | ng in PWMxL I                                                                                                      |                               |                                                 |                    |                 |                |  |  |  |  |  |

|                 |                                            | -                                                                                                                  | -                             |                                                 | nals) when the F   | PWMxL output    | is hiah        |  |  |  |  |  |

|                 |                                            |                                                                                                                    |                               |                                                 |                    |                 |                |  |  |  |  |  |

|                 | 0 = No blankii                             | ng when the P                                                                                                      | WMxL output                   | is high                                         |                    |                 |                |  |  |  |  |  |

| bit 0           | BPLL: Blanki                               | ng when the P<br>ng in PWMxL L                                                                                     | ow Enable b                   | it                                              |                    |                 | -              |  |  |  |  |  |

| bit 0           | <b>BPLL:</b> Blankii<br>1 = State blan     | ng when the P<br>ng in PWMxL L                                                                                     | ow Enable b<br>t-limit and/or | it<br>Fault input sigr                          | nals) when the F   | PWMxL output    | -              |  |  |  |  |  |

Note 1: The blanking signal is selected through the BLANKSEL<3:0> bits in the AUXCONx register.

### REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>S: I2Cx Start bit</li> <li>Updated when Start, Reset or Stop is detected; cleared when the I<sup>2</sup>C module is disabled, I2CEN = 0.</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Indicates that a Start bit was not detected last</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                             |

|       | <ol> <li>= Read: Indicates that the data transfer is output from the slave</li> <li>= Write: Indicates that the data transfer is input to the slave</li> </ol>                                                                                                                                                |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                                           |

|       | <ol> <li>= Receive is complete, the I2CxRCV bit is full</li> <li>= Receive is not complete, the I2CxRCV bit is empty</li> </ol>                                                                                                                                                                               |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                   |

|       | <ul> <li>1 = Transmit is in progress, I2CxTRN is full (8 bits of data)</li> <li>0 = Transmit is complete, I2CxTRN is empty</li> </ul>                                                                                                                                                                         |

|       |                                                                                                                                                                                                                                                                                                               |

# REGISTER 19-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0      | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0    | R/W-0 |  |

|----------|-------|-------|-------|-------|-------|----------|-------|--|

| —        | —     | —     | —     | —     | —     | MSK<9:8> |       |  |

| bit 15   |       |       |       |       |       |          | bit 8 |  |

|          |       |       |       |       |       |          |       |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 |  |

| MSK<7:0> |       |       |       |       |       |          |       |  |

| Legend:           |                  |                                       |                    |  |

|-------------------|------------------|---------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | it U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |

bit 15-10 Unimplemented: Read as '0'

bit 7

bit 9-0 MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

bit 0

| R/W-0         | R/W-0                        | U-0                                                     | U-0                                  | R/W-0                         | R/W-0            | U-0                | U-0        |

|---------------|------------------------------|---------------------------------------------------------|--------------------------------------|-------------------------------|------------------|--------------------|------------|

| CVREN         | CVROE <sup>(1)</sup>         | _                                                       | _                                    | CVRSS                         | VREFSEL          | _                  | _          |

| bit 15        |                              |                                                         |                                      |                               |                  |                    | bit 8      |

| U-0           | R/W-0                        | R/W-0                                                   | R/W-0                                | R/W-0                         | R/W-0            | R/W-0              | R/W-0      |

| —             | CVR6                         | CVR5                                                    | CVR4                                 | CVR3                          | CVR2             | CVR1               | CVR0       |

| bit 7         |                              |                                                         |                                      |                               |                  |                    | bit 0      |

| Legend:       |                              |                                                         |                                      |                               |                  |                    |            |

| R = Readabl   | le bit                       | W = Writable                                            | bit                                  | U = Unimple                   | mented bit, read | <b>as</b> '0'      |            |

| -n = Value at | t POR                        | '1' = Bit is set                                        |                                      | '0' = Bit is cle              | eared            | x = Bit is unkr    | nown       |

| bit 15        | 1 = Comparat<br>0 = Comparat | parator Voltag<br>tor voltage refe<br>tor voltage refe  | erence circuit i<br>erence circuit i | s powered on<br>s powered dov |                  | (1)                |            |

| bit 14        | 1 = Voltage le               | nparator Voltag<br>evel is output o<br>evel is disconne | n the CVREF2                         | o pin                         | (CVREF20 Pin)    | bit <sup>(1)</sup> |            |

| bit 13-12     | •                            | ted: Read as '                                          |                                      |                               |                  |                    |            |

| bit 11        | =                            | parator Voltag                                          |                                      | Source Selection              | on bit           |                    |            |

|               |                              | tor reference s<br>tor reference s                      |                                      |                               |                  |                    |            |

| bit 10        | VREFSEL: Vo                  | oltage Referen                                          | ce Select bit                        |                               |                  |                    |            |

|               | (CVR1C0                      | ON<10>) = 0                                             |                                      |                               | es inverting inp | -                  |            |

|               |                              | itor Reference<br>ON<10>) = 0                           | Source 1 (                           | CVR1) provide                 | es inverting inp | ut voltage wh      | en VREFSEL |

| bit 9-7       | Unimplemen                   | ted: Read as '                                          | 0'                                   |                               |                  |                    |            |

| bit 6-0       |                              | omparator Vol<br>27/128 x VREF                          | -                                    | e Value Selec                 | tion bits        |                    |            |

|               | •<br>0000000 = 0             | 0 volts                                                 |                                      |                               |                  |                    |            |

| Note 4: 0     |                              |                                                         | evellekterer (                       | ha 00 m <sup>1</sup>          |                  |                    |            |

| Note 1: C     | VROE (CVR2CC                 | //////////////////////////////////////                  | available on t                       | ne 28-pin devi                | ces.             |                    |            |

## REGISTER 26-2: CVR2CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 2

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EVXXXGM00X/10X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EVXXXGM00X/10X family devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to ensure that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

| Note: | Performing a page erase operation on the |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | last page of program memory clears the   |  |  |  |  |  |  |

|       | Flash Configuration bytes, enabling code |  |  |  |  |  |  |

|       | protection as a result. Therefore, users |  |  |  |  |  |  |

|       | should avoid performing page erase       |  |  |  |  |  |  |

|       | operations on the last page of program   |  |  |  |  |  |  |

|       | memory.                                  |  |  |  |  |  |  |

The Configuration Flash bytes map is shown in Table 27-1.

| Bit Field   | Register | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP        | FSEC     | Boot Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                     |

| BSS<1:0>    | FSEC     | Boot Segment Code Flash Protection Level bits<br>11 = No protection (other than BWRP write protection)<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                             |

| BSEN        | FSEC     | Boot Segment Control bit<br>1 = No Boot Segment<br>0 = Boot Segment size is determined by BSLIM<12:0>                                                                                                                                                                                                                                                                              |

| GWRP        | FSEC     | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                  |

| GSS<1:0>    | FSEC     | General Segment Code Flash Protection Level bits<br>11 = No protection (other than GWRP write protection)<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                          |

| CWRP        | FSEC     | Configuration Segment Write-Protect bit<br>1 = Configuration Segment is not write-protected<br>0 = Configuration Segment is write-protected                                                                                                                                                                                                                                        |

| CSS<2:0>    | FSEC     | Configuration Segment Code Flash Protection Level bits<br>111 = No protection (other than CWRP write protection)<br>110 = Standard security<br>10x = Enhanced security<br>0xx = High security                                                                                                                                                                                      |

| AIVTDIS     | FSEC     | Alternate Interrupt Vector Table Disable bit<br>1 = Disables AIVT<br>0 = Enables AIVT                                                                                                                                                                                                                                                                                              |

| BSLIM<12:0> | FBSLIM   | Boot Segment Code Flash Page Address Limit bits<br>Contains the page address of the first active General Segment page. The<br>value to be programmed is the inverted page address, such that<br>programming additional '0's can only increase the Boot Segment size.<br>For example, 0x1FFD = 2 pages or 1024 instruction words.                                                   |

| FNOSC<2:0>  | FOSCSEL  | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) Oscillator with Postscaler<br>110 = Internal Fast RC (FRC) Oscillator with Divide-by-16<br>101 = LPRC Oscillator<br>100 = Reserved<br>011 = Primary (XT, HS, EC) Oscillator with PLL<br>010 = Primary (XT, HS, EC) Oscillator<br>001 = Internal Fast RC (FRC) Oscillator with PLL<br>000 = FRC Oscillator |

| ĪĒSO        | FOSCSEL  | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with user-selected oscillator source</li> </ul>                                                                                                                              |

| POSCMD<1:0> | FOSC     | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                  |

# TABLE 27-2: dsPIC33EVXXXGM00X/10X CONFIGURATION BITS DESCRIPTION

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax                       |                             | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------------------------------------|-----------------------------|----------------------------------------|---------------|----------------|--------------------------|

| 46 MAC             |                      | MAC Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB |                             | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC                                   | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square and Accumulate                  | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 47                 | MOV                  | MOV                                   | f,Wn                        | Move f to Wn                           | 1             | 1              | None                     |

|                    |                      | MOV                                   | f                           | Move f to f                            | 1             | 1              | None                     |

|                    |                      | MOV                                   | f,WREG                      | Move f to WREG                         | 1             | 1              | None                     |

|                    |                      | MOV                                   | #litl6,Wn                   | Move 16-bit literal to Wn              | 1             | 1              | None                     |

|                    |                      | MOV.b                                 | #lit8,Wn                    | Move 8-bit literal to Wn               | 1             | 1              | None                     |

|                    |                      | MOV                                   | Wn,f                        | Move Wn to f                           | 1             | 1              | None                     |

|                    |                      | MOV                                   | Wso,Wdo                     | Move Ws to Wd                          | 1             | 1              | None                     |

|                    |                      | MOV                                   | WREG, f                     | Move WREG to f                         | 1             | 1              | None                     |

|                    |                      | MOV.D                                 | Wns,Wd                      | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |

|                    |                      | MOV.D                                 | Ws,Wnd                      | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |

| 48                 | MOVPAG               | MOVPAG                                | #lit10,DSRPAG               | Move 10-bit literal to DSRPAG          | 1             | 1              | None                     |

|                    |                      | MOVPAG                                | #lit9,DSWPAG                | Move 9-bit literal to DSWPAG           | 1             | 1              | None                     |

|                    |                      | MOVPAG                                | #lit8,TBLPAG                | Move 8-bit literal to TBLPAG           | 1             | 1              | None                     |

|                    |                      | MOVPAGW                               | Ws, DSRPAG                  | Move Ws<9:0> to DSRPAG                 | 1             | 1              | None                     |

|                    |                      | MOVPAGW                               | Ws, DSWPAG                  | Move Ws<8:0> to DSWPAG                 | 1             | 1              | None                     |

|                    |                      | MOVPAGW                               | Ws, TBLPAG                  | Move Ws<7:0> to TBLPAG                 | 1             | 1              | None                     |

| 49                 | MOVSAC               | MOVSAC                                | Acc,Wx,Wxd,Wy,Wyd,AWB       | Prefetch and store accumulator         | 1             | 1              | None                     |

| 50                 | MPY                  | MPY                                   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | Multiply Wm by Wn to Accumulator       | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | MPY                                   | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square Wm to Accumulator               | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 51                 | MPY.N                | MPY.N                                 | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | -(Multiply Wm by Wn) to Accumulator    | 1             | 1              | None                     |

| 52                 | MSC                  | MSC                                   | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Subtract from Accumulator | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| TABI F 28-2- | INSTRUCTION SET OVERVIEW ( | (CONTINUED) |

|--------------|----------------------------|-------------|

|              |                            |             |

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### **30.1 DC Characteristics**

| Characteristic | VDD Range                     | Temperature Range | Maximum MIPS                 |  |  |

|----------------|-------------------------------|-------------------|------------------------------|--|--|

| Characteristic | (in Volts)                    | (in °C)           | dsPIC33EVXXXGM00X/10X Family |  |  |

| I-Temp         | 4.5V to 5.5V <sup>(1,2)</sup> | -40°C to +85°C    | 70                           |  |  |

| E-Temp         | 4.5V to 5.5V <sup>(1,2)</sup> | -40°C to +125°C   | 60                           |  |  |

#### TABLE 30-1: OPERATING MIPS vs. VOLTAGE

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, op amp/comparator and comparator voltage reference will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: When BOR is enabled, the device will work from 4.7V to 5.5V.

**Note 1:** Customer operating voltage range is specified as: 4.5V to 5.5V.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                            | Symbol | Min.                 | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------------------------|--------|----------------------|------|------|------|

| Industrial Temperature Devices:                                                                   |        |                      |      |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40                  | —    | +125 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40                  | —    | +85  | °C   |

| Extended Temperature Devices:                                                                     |        |                      |      |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40                  | —    | +140 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40                  | —    | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$       | PD     | D PINT + PI/O        |      |      | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} \times IOH) + \Sigma (VOL \times IOL)$ |        |                      |      |      |      |

| Maximum Allowed Power Dissipation                                                                 | PDMAX  | ОМАХ (ТЈ – ТА)/θЈА \ |      |      | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                       | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN, 9x9x0.9 mm   | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP, 10x10x1 mm  | θJA    | 48.3 | —    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN, 8x8 mm       | θJA    | 29.0 | —    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP, 10x10x1 mm  | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S, 6x6x0.9 mm | θJA    | 30.0 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC, 7.50 mm     | θJA    | 69.7 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP, 5.30 mm     | θJA    | 71.0 |      | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP, 300 mil    | θJA    | 60.0 | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |                       |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |

|--------------------|-----------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param<br>No.       | Symbol Characteristic |                                                                     | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions         |

| OS50               | Fplli                 | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 0.8                                                                                                                                                                                                                                                                                   |                     | 8.0  | MHz   | ECPLL, XTPLL modes |

| OS51               | Fsys                  | On-Chip VCO System<br>Frequency                                     | 120                                                                                                                                                                                                                                                                                   | —                   | 340  | MHz   |                    |

| OS52               | TLOCK                 | PLL Start-up Time (Lock Time)                                       | 0.9                                                                                                                                                                                                                                                                                   | 1.5                 | 3.1  | ms    |                    |

| OS53               | DCLK                  | CLKO Stability (Jitter) <sup>(2)</sup>                              | -3                                                                                                                                                                                                                                                                                    | 0.5                 | 3    | %     |                    |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$