Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 70 MIPs                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O             | 35                                                                               |

| Program Memory Size       | 64KB (22K x 24)                                                                  |

| Program Memory Type       | FLASH                                                                            |

| EEPROM Size               | -                                                                                |

| RAM Size                  | 8K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters           | A/D 24x10/12b                                                                    |

| Oscillator Type           | Internal                                                                         |

| Operating Temperature     | -40°C ~ 85°C (TA)                                                                |

| Mounting Type             | Surface Mount                                                                    |

| Package / Case            | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package   | 44-QFN (8x8)                                                                     |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm004t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EVXXXGM00X/10X family core has two Data Spaces: X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified, linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X DS is used by all instructions and supports all addressing modes. The X DS has separate read and write data buses. The X read data bus is the read data path for all instructions that view the DS as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y DS is used in concert with the X DS by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to the X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

### TABLE 4-5: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8                  | Bit 7         | Bit 6          | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | AII<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|-----------|------------------------|---------------|----------------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | -      | UEN1      | UEN0                   | WAKE          | LPBACK         | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT                   | URXISEL1      | URXISEL0       | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | ı      | _        | _      |        | ı      | _         |                        |               |                | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | ı      | _        | _      |        | ı      | _         |                        |               |                | UART1 | Receive Re  | egister |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        | U      | IART1 Baı | ud Rate G              | enerator Pres | scaler Registe | r     |             |         |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | 1      | USIDL    | IREN   | RTSMD  | 1      | UEN1      | UEN0                   | WAKE          | LPBACK         | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT                   | URXISEL1      | URXISEL0       | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _         |                        |               |                | UART2 | Transmit Re | egister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | ı      | _        | _      | _      | ı      | _         | UART2 Receive Register |               |                |       |             |         |        |        | 0000  |               |

| U2BRG       | 0238  |          | •      | •        |        | •      | U      | IART2 Baı | ıd Rate G              | enerator Pres | scaler Registe | r     |             |         | •      |        | •     | 0000          |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-6: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8        | Bit 7       | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|----------|--------------|-------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _        | -            | _           | _           | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tra | ansmit and R | Receive Buf | fer Registe | r      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | -      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _        | -            |             | _           | _      | _      |        | _      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  | •      | •      | •       |        | •      | •       | SPI2 Tra | ansmit and R | Receive Buf | fer Registe | r      |        |        | •      |        | •      | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|---------|---------|-------|-------|-------|

| NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE | OVBTE | COVTE |

| bit 15 |        |        |         |         |       |       | bit 8 |

| R/W-0    | R-0, HC | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|----------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7    |         |         |         |         |        |         | bit 0 |

| Legend:           | HC = Hardware Clearable b | it                          |                    |

|-------------------|---------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | NSTDIS: Interrupt Nesting Disable bit                              |

|--------|--------------------------------------------------------------------|

|        | 1 = Interrupt nesting is disabled                                  |

|        | 0 = Interrupt nesting is enabled                                   |

| bit 14 | OVAERR: Accumulator A Overflow Trap Flag bit                       |

|        | 1 = Trap was caused by overflow of Accumulator A                   |

|        | 0 = Trap was not caused by overflow of Accumulator A               |

| bit 13 | OVBERR: Accumulator B Overflow Trap Flag bit                       |

|        | 1 = Trap was caused by overflow of Accumulator B                   |

|        | 0 = Trap was not caused by overflow of Accumulator B               |

| bit 12 | COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit         |

|        | 1 = Trap was caused by catastrophic overflow of Accumulator A      |

|        | 0 = Trap was not caused by catastrophic overflow of Accumulator A  |

| bit 11 | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit         |

|        | 1 = Trap was caused by catastrophic overflow of Accumulator B      |

|        | 0 = Trap was not caused by catastrophic overflow of Accumulator B  |

| bit 10 | <b>OVATE:</b> Accumulator A Overflow Trap Enable bit               |

|        | 1 = Trap overflow of Accumulator A                                 |

|        | 0 = Trap is disabled                                               |

| bit 9  | <b>OVBTE:</b> Accumulator B Overflow Trap Enable bit               |

|        | 1 = Trap overflow of Accumulator B                                 |

|        | 0 = Trap is disabled                                               |

| bit 8  | COVTE: Catastrophic Overflow Trap Enable bit                       |

|        | 1 = Trap on catastrophic overflow of Accumulator A or B is enabled |

|        | 0 = Trap is disabled                                               |

| bit 7  | SFTACERR: Shift Accumulator Error Status bit                       |

|        | 1 = Math error trap was caused by an invalid accumulator shift     |

|        | 0 = Math error trap was caused by an invalid accumulator shift     |

| bit 6  | DIV0ERR: Divide-by-Zero Error Status bit                           |

|        | 1 = Math error trap was caused by a divide-by-zero                 |

|        | 0 = Math error trap was not caused by a divide-by-zero             |

| bit 5  | DMACERR: DMAC Trap Flag bit                                        |

|        | 1 = DMAC trap has occurred                                         |

|        | 0 = DMAC trap has not occurred                                     |

| bit 4  | MATHERR: Math Error Status bit                                     |

|        | 1 = Math error trap has occurred                                   |

|        | 0 = Math error trap has not occurred                               |

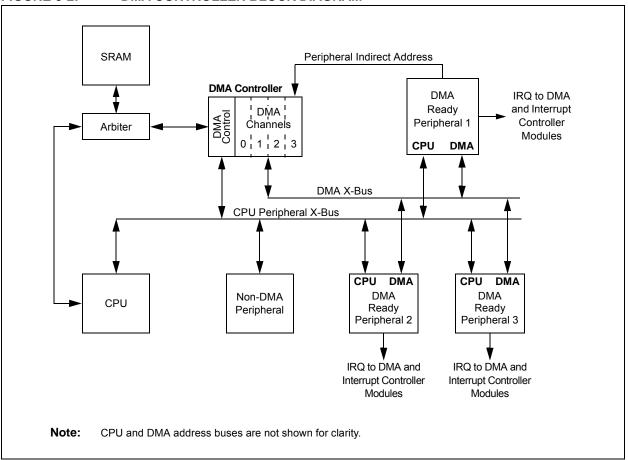

Figure 8-2 illustrates the DMA Controller block diagram.

FIGURE 8-2: DMA CONTROLLER BLOCK DIAGRAM

### 8.1 DMAC Controller Registers

Each DMAC Channel x (where x = 0 to 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A High/Low (DMAxSTAH/L)

- 32-Bit DMA Channel x Start Address Register B High/Low (DMAxSTBH/L)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRH/L) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The DMA Interrupt Flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding DMA Interrupt Enable bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding DMA Interrupt Priority bits (DMAxIP) are located in an IPCx register in the interrupt controller.

|        | DSPIC33EVXXXGWIUUX/1UX FAWILT |  |  |  |  |  |  |  |  |  |  |

|--------|-------------------------------|--|--|--|--|--|--|--|--|--|--|

| NOTES: |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 10-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

| U-0    | U-0 | U-0 | R/W-0   | R/W-0   | U-0 | U-0 | R/W-0 |

|--------|-----|-----|---------|---------|-----|-----|-------|

| _      | _   | _   | SENT2MD | SENT1MD | _   | _   | DMTMD |

| bit 15 |     |     |         |         |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 SENT2MD: SENT2 Module Disable bit

1 = SENT2 module is disabled 0 = SENT2 module is enabled

bit 11 SENT1MD: SENT1 Module Disable bit

1 = SENT1 module is disabled 0 = SENT1 module is enabled

bit 10-9 **Unimplemented:** Read as '0'

bit 8 **DMTMD:** Deadman Timer Disable bit

1 = Deadman Timer is disabled 0 = Deadman Timer is enabled

bit 7-0 **Unimplemented:** Read as '0'

### 11.8 Peripheral Pin Select Registers

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | INT1F | R<7:0> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | -   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **INT1R<7:0>:** Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| INT2R<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 INT2R<7:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

.

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

#### REGISTER 11-10: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SCK2R7 | SCK2R6 | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| SDI2R | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **SCK2R<7:0>:** Assign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

•

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

bit 7-0 **SDI2R<7:0>:** Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

•

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

## REGISTER 14-11: DMTHOLDREG: DMT HOLD REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| UPRCNT<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| UPRCNT<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 UPRCNT<15:0>: Value of the DMTCNTH register when DMTCNTL and DMTCNTH were Last Read bits

**Note 1:** The DMTHOLDREG register is initialized to '0' on Reset, and is only loaded when the DMTCNTL and DMTCNTH registers are read.

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup> bit 4-0 11111 = Reserved 11110 = Reserved 11101 = Reserved 11100 = CTMU trigger is the source for the capture timer synchronization 11011 = ADC1 interrupt is the source for the capture timer synchronization<sup>(5)</sup> 11010 = Analog Comparator 3 is the source for the capture timer synchronization (5) 11001 = Analog Comparator 2 is the source for the capture timer synchronization (5) 11000 = Analog Comparator 1 is the source for the capture timer synchronization (5) 10111 = Analog Comparator 5 is the source for the capture timer synchronization (5) 10110 = Analog Comparator 4 is the source for the capture timer synchronization<sup>(5)</sup> 10101 = Reserved 10100 = Reserved 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization 01111 = GP Timer5 is the source for the capture timer synchronization 01110 = GP Timer4 is the source for the capture timer synchronization 01101 = GP Timer3 is the source for the capture timer synchronization 01100 = GP Timer2 is the source for the capture timer synchronization 01011 = GP Timer1 is the source for the capture timer synchronization 01010 = Reserved 01001 = Reserved 01000 = Input Capture 4 is the source for the capture timer synchronization (6) 00111 = Input Capture 3 is the source for the capture timer synchronization (6) 00110 = Input Capture 2 is the source for the capture timer synchronization (6) 00101 = Input Capture 1 is the source for the capture timer synchronization (6) 00100 = Output Compare 4 is the source for the capture timer synchronization 00011 = Output Compare 3 is the source for the capture timer synchronization 00010 = Output Compare 2 is the source for the capture timer synchronization 00001 = Output Compare 1 is the source for the capture timer synchronization 00000 = Reserved

- Note 1: The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- **4:** Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- **6:** When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

### 19.2 I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0   | R/S-1                 | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------------------|--------|-------|--------|-------|

| I2CEN  | _   | I2CSIDL | SCLREL <sup>(1)</sup> | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |                       |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

| Legend:           | S = Settable bit | HC = Hardware Cleara  | ble bit                            |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 15 **I2CEN:** I2Cx Enable bit (writable from SW only)

1 = Enables the I<sup>2</sup>C module and configures the SDAx and SCLx pins as serial port pins

$0 = \text{Disables the } 1^2\text{C}$  module and all  $1^2\text{C}$  pins are controlled by port functions

bit 14 Unimplemented: Read as '0'

bit 13 I2CSIDL: I2Cx Stop in Idle Mode bit

1 = Discontinues module operation when the device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 SCLREL: SCLx Release Control bit (I<sup>2</sup>C Slave mode only)<sup>(1)</sup>

Module resets and (I2CEN = 0) sets SCLREL = 1.

If STREN = 0:(2)

1 = Releases clock

0 = Forces clock low (clock stretch)

#### If STREN = 1:

1 = Releases clock

0 = Holds clock low (clock stretch); user may program this bit to '0', clock stretch at the next SCLx low

bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

1 = Strict reserved addressing is enforced

In Slave mode, the device does not respond to reserved address space and addresses falling in that category are NACKed.

0 = Reserved addressing would be Acknowledged

In Slave mode, the device will respond to an address falling in the reserved address space. When there is a match with any of the reserved addresses, the device will generate an ACK.

bit 10 A10M: 10-Bit Slave Address Flag bit

1 = I2CxADD is a 10-bit slave address

0 = I2CxADD is a 7-bit slave address

bit 9 DISSLW: Slew Rate Control Disable bit

1 = Slew rate control is disabled for Standard Speed mode (100 kHz, also disabled for 1 MHz mode)

0 = Slew rate control is enabled for High-Speed mode (400 kHz)

bit 8 SMEN: SMBus Input Levels Enable bit

1 = Enables the input logic so thresholds are compliant with the SMBus specification

0 = Disables the SMBus-specific inputs

**Note 1:** Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.

**2:** Automatically cleared to '0' at the beginning of slave transmission.

#### BUFFER 22-3: CANX MESSAGE BUFFER WORD 2

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID5   | EID4  | EID3  | EID2  | EID1  | EID0  | RTR   | RB1   |

| bit 15 |       |       |       |       |       |       | bit 8 |

| U-x   | U-x | U-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | RB0   | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **EID<5:0>:** Extended Identifier bits

bit 9 RTR: Remote Transmission Request bit

When IDE = 1:

1 = Message will request remote transmission

0 = Normal message When IDE = 0:

The RTR bit is ignored.

bit 8 RB1: Reserved Bit 1

User must set this bit to '0' per CAN protocol.

bit 7-5 **Unimplemented:** Read as '0'

bit 4 RB0: Reserved Bit 0

User must set this bit to '0' per CAN protocol.

bit 3-0 **DLC<3:0>:** Data Length Code bits

#### BUFFER 22-4: CANx MESSAGE BUFFER WORD 3

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Byte 1<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |

|   | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|---|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Ī | Byte 0<7:0> |       |       |       |       |       |       |       |  |  |

|   | bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 1<15:8>:** CANx Message Byte 1 bits bit 7-0 **Byte 0<7:0>:** CANx Message Byte 0 bits

TABLE 30-13: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHA       | RACTER | ISTICS                            | (unless                            | otherw | ise state | <b>d)</b><br>-40°C ≤ | s: 4.5V to 5.5V<br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended |  |  |  |

|--------------|--------|-----------------------------------|------------------------------------|--------|-----------|----------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                    | Min. Typ. <sup>(1)</sup> Max. Unit |        | Units     | Conditions           |                                                                                                  |  |  |  |

|              |        | Program Flash Memory              |                                    |        |           |                      |                                                                                                  |  |  |  |

| D130         | EР     | Cell Endurance                    | 10,000                             | _      | _         | E/W                  | -40°C to +125°C                                                                                  |  |  |  |

| D131         | VPR    | VDD for Read                      | 4.5                                | _      | 5.5       | V                    |                                                                                                  |  |  |  |

| D132b        | VPEW   | VDD for Self-Timed Write          | 4.5                                | _      | 5.5       | V                    |                                                                                                  |  |  |  |

| D134         | TRETD  | Characteristic Retention          | 20                                 | _      | _         | Year                 | Provided no other specifications are violated, -40°C to +125°C                                   |  |  |  |

| D135         | IDDP   | Supply Current During Programming | _                                  | 10     | _         | mA                   |                                                                                                  |  |  |  |

| D136a        | TRW    | Row Write Cycle Time              | 0.657                              | _      | 0.691     | ms                   | TRW = 4965 FRC cycles,<br>TA = +85°C (see <b>Note 2</b> )                                        |  |  |  |

| D136b        | TRW    | Row Write Cycle Time              | 0.651                              | _      | 0.698     | ms                   | TRW = 4965 FRC cycles,<br>TA = +125°C (see <b>Note 2</b> )                                       |  |  |  |

| D137a        | TPE    | Page Erase Time                   | 19.44                              | _      | 20.44     | ms                   | TPE = 146893 FRC cycles,<br>TA = +85°C (see <b>Note 2</b> )                                      |  |  |  |

| D137b        | TPE    | Page Erase Time                   | 19.24                              | _      | 20.65     | ms                   | TPE = 146893 FRC cycles,<br>TA = +125°C (see <b>Note 2</b> )                                     |  |  |  |

| D138a        | Tww    | Word Write Cycle Time             | 45.78                              | _      | 48.15     | μs                   | Tww = 346 FRC cycles,<br>TA = +85°C (see <b>Note 2</b> )                                         |  |  |  |

| D138b        | Tww    | Word Write Cycle Time             | 45.33                              | _      | 48.64     | μs                   | Tww = 346 FRC cycles,<br>TA = +125°C (see <b>Note 2</b> )                                        |  |  |  |

Note 1: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

#### TABLE 30-14: ELECTRICAL CHARACTERISTICS: INTERNAL BAND GAP REFERENCE VOLTAGE

| DC CHARACTERISTICS |        |                                        |      | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |            |  |

|--------------------|--------|----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                         | Min. | Тур.                                                                                                                                                                                                                                             | Max. | Units | Conditions |  |

| DVR10              | VBG    | Internal Band Gap Reference<br>Voltage | 1.14 | 1.2                                                                                                                                                                                                                                              | 1.26 | V     |            |  |

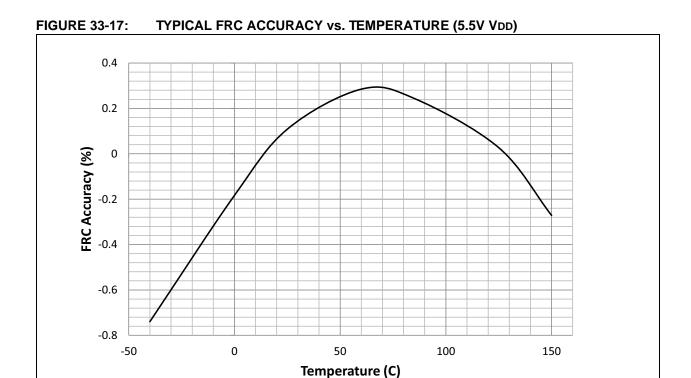

<sup>2:</sup> Other conditions: FRC = 7.3728 MHz, TUN<5:0> = b · 0111111 (for Min), TUN<5:0> = b · 100000 (for Max). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register.

TABLE 30-41: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS

| AC CHA | RACTERIST             | ICS                                           | Standard<br>(unless of<br>Operating | therwise            | <b>stated)</b><br>ture -40° | °C ≤ TA ≤ | V to 5.5V<br>+85°C for Industrial<br>+125°C for Extended |

|--------|-----------------------|-----------------------------------------------|-------------------------------------|---------------------|-----------------------------|-----------|----------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                | Typ. <sup>(2)</sup> | Max.                        | Units     | Conditions                                               |

| SP10   | FscP                  | Maximum SCK1 Frequency                        | _                                   | _                   | 25                          | MHz       | -40°C to +125°C and see <b>Note 3</b>                    |

| SP20   | TscF                  | SCK1 Output Fall Time                         | _                                   | _                   | _                           | ns        | See Parameter DO32 and <b>Note 4</b>                     |

| SP21   | TscR                  | SCK1 Output Rise Time                         | _                                   | _                   | _                           | ns        | See Parameter DO31 and <b>Note 4</b>                     |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                    | _                                   | _                   | _                           | ns        | See Parameter DO32 and <b>Note 4</b>                     |

| SP31   | TdoR                  | SDO1 Data Output Rise<br>Time                 | _                                   | _                   | _                           | ns        | See Parameter DO31 and <b>Note 4</b>                     |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | _                                   | 6                   | 20                          | ns        |                                                          |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge     | 20                                  | _                   | _                           | ns        |                                                          |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 20                                  | _                   | _                           | ns        |                                                          |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 20                                  | _                   | _                           | ns        |                                                          |

Note 1: These parameters are characterized but not tested in manufacturing.

- **2:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

#### 33.6 **LPRC**

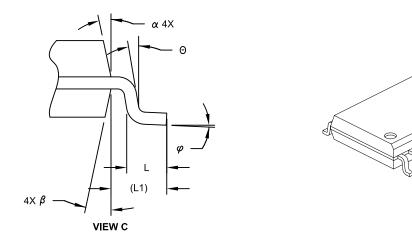

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N  | ILLIMETER | S         |      |  |  |  |

|--------------------------|----|-----------|-----------|------|--|--|--|

| Dimension Li             |    | MIN       | NOM       | MAX  |  |  |  |

| Number of Pins           | N  |           | 28        |      |  |  |  |

| Pitch                    | е  |           | 1.27 BSC  |      |  |  |  |

| Overall Height           | Α  | -         | -         | 2.65 |  |  |  |

| Molded Package Thickness | A2 | 2.05      | -         | -    |  |  |  |

| Standoff §               | A1 | 0.10      | -         | 0.30 |  |  |  |

| Overall Width            | Е  |           | 10.30 BSC |      |  |  |  |

| Molded Package Width     | E1 | 7.50 BSC  |           |      |  |  |  |

| Overall Length           | D  | 17.90 BSC |           |      |  |  |  |

| Chamfer (Optional)       | h  | 0.25      | ı         | 0.75 |  |  |  |

| Foot Length              | L  | 0.40      | ı         | 1.27 |  |  |  |

| Footprint                | L1 | 1.40 REF  |           |      |  |  |  |

| Lead Angle               | Θ  | 0°        | -         | -    |  |  |  |

| Foot Angle               | φ  | 0°        | -         | 8°   |  |  |  |

| Lead Thickness           | С  | 0.18      | -         | 0.33 |  |  |  |

| Lead Width               | b  | 0.31      | -         | 0.51 |  |  |  |

| Mold Draft Angle Top     | α  | 5°        | -         | 15°  |  |  |  |

| Mold Draft Angle Bottom  |    | 5°        | -         | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

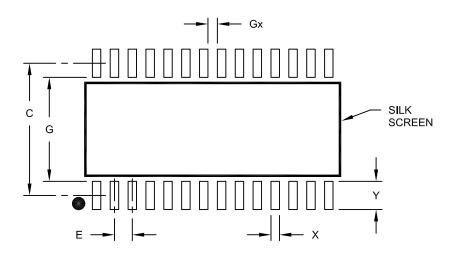

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | N               | <b>IILLIMETER</b> | S        |      |

|--------------------------|-----------------|-------------------|----------|------|

| Dimension Limits         |                 | MIN               | NOM      | MAX  |

| Contact Pitch            | Contact Pitch E |                   | 1.27 BSC |      |

| Contact Pad Spacing      | С               |                   | 9.40     |      |

| Contact Pad Width (X28)  | Х               |                   |          | 0.60 |

| Contact Pad Length (X28) | Υ               |                   |          | 2.00 |

| Distance Between Pads    | Gx              | 0.67              |          |      |

| Distance Between Pads    | G               | 7.40              |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

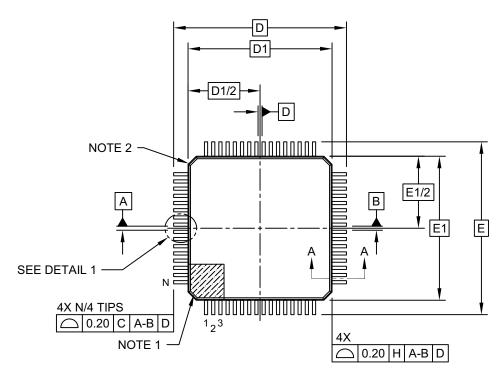

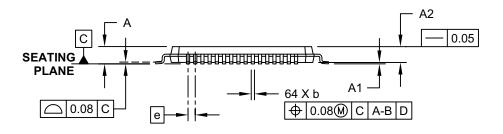

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

| SENTx Module                                      | 238 | D                                                                 |     |

|---------------------------------------------------|-----|-------------------------------------------------------------------|-----|

| Shared I/O Port Structure                         | 143 | Data Address Space                                                | 36  |

| SPIx Module                                       | 222 | Alignment                                                         |     |

| Type B Timer (Timer2 and Timer4)                  | 176 | <u> </u>                                                          |     |

| Type B/Type C Timer Pair (32-Bit Timer)           |     | Memory Map for 256-Kbyte Devices  Memory Map for 32-Kbyte Devices |     |

| Type C Timer (Timer3 and Timer5)                  |     | Memory Map for 64/128-Kbyte Devices                               |     |

| UARTx Module                                      | 247 | Near Data Space                                                   |     |

| User-Programmable Blanking Function               | 302 | SFR Space                                                         |     |

| Watchdog Timer (WDT)                              | 325 | Width                                                             |     |

| Brown-out Reset (BOR)                             |     | Data Space                                                        |     |

| •                                                 |     | Extended X                                                        | 73  |

| С                                                 |     | Memory Arbitration, Bus Master Priority                           |     |

| C Compilers                                       |     | Paged Memory Scheme                                               |     |

| MPLAB XC                                          | 338 | DC Characteristics                                                |     |

| CAN                                               |     | Brown-out Reset (BOR)                                             |     |

| CAN Module                                        |     | CTMU Current Source                                               |     |

| Control Registers                                 |     | Doze Current (IDOZE)                                              |     |

| Message Buffers                                   |     | Filter Capacitor (CEFC) Specifications                            |     |

| Word 0                                            |     | High Temperature                                                  |     |

| Word 1                                            |     | Brown-out Reset (BOR)                                             |     |

| Word 2                                            |     | CTMU Current Source                                               |     |

| Word 3                                            |     | I/O Pin Input Specifications                                      |     |

| Word 4                                            |     | I/O Pin Output Specifications                                     |     |

| Word 5                                            |     | Idle Current (IIDLE)                                              |     |

| Word 6                                            |     | Op Amp/ Comparator x                                              |     |

| Word 7                                            |     | Operating Current (IDD)                                           |     |

| Modes of Operation                                |     | Operating MIPS vs. Voltage                                        |     |

| Overview                                          | 253 | Power-Down Current (IPD)                                          |     |

| Characteristics for High-Temperature              | 420 | Program Memory                                                    |     |

| Devices (+150°C)                                  |     | Temperature and Voltage Specifications                            | 404 |

| Characteristics for Industrial/Extended Temperatu |     | Doze Current (IDOZE)                                              | 405 |

| Devices (-40°C to +125°C)                         |     | I/O Pin Input Specifications                                      | 348 |

| Charge Time Measurement Unit (CTMU)               | 279 | I/O Pin Output Specifications                                     | 349 |

| Code Examples                                     |     | Idle Current (IDLE)                                               | 345 |

| Port Write/Read                                   | 144 | Internal Band Gap Reference Voltage                               |     |

| PORTA Slew Selections                             |     | Op Amp/Comparator x Specifications                                | 392 |

| PWM1 Write-Protected Register                     | 143 | Op Amp/Comparator x Voltage Reference                             |     |

| Unlock Sequence                                   | 200 | Specifications                                                    |     |

| PWRSAV Instruction Syntax                         |     | Operating Current (IDD)                                           |     |

| Code Protection                                   |     | Operating MIPS vs. Voltage                                        |     |

| CodeGuard Security                                |     | Power-Down Current (IPD)                                          |     |

| Comparator Voltage Reference                      | ,   | Program Memory                                                    |     |

| Configuring                                       | 313 | Temperature and Voltage Specifications                            |     |

| Control Registers                                 |     | Thermal Operating Conditions                                      |     |

| Configuration Bits                                |     | Deadman Timer (DMT)                                               |     |

| Description                                       |     | Control Registers                                                 | 182 |

| Controller Area Network (CAN)                     |     | Deadman Timer. See DMT.                                           | 00- |

| Controller Area Network. See CAN.                 |     | Development Support                                               | 337 |

| CPU                                               | 21  | Direct Memory Access. See DMA.                                    |     |

| Addressing Modes                                  | 21  | DMA Controller                                                    | 440 |

| Arithmetic Logic Unit (ALU)                       | 30  | Channel to Peripheral Associations                                |     |

| Control Registers                                 |     | Control Registers                                                 |     |

| Data Space Addressing                             | 21  | Supported Peripherals                                             | 108 |

| DSP Engine                                        |     | DMAC Registers                                                    | 114 |

| Instruction Set                                   | 21  | DMAxCON                                                           |     |

| Programmer's Model                                | 23  | DMAXBAD                                                           |     |

| CTMU                                              |     | DMAxPAD<br>DMAxREQ                                                |     |

| Control Registers                                 | 281 | DMAxSTAH/L                                                        |     |

| Customer Change Notification Service              | 493 | DMAxSTBH/L                                                        |     |

| Customer Notification Service                     | 493 | DMT                                                               | 117 |

| Customer Support                                  | 493 | Doze Mode                                                         | 121 |

|                                                   |     | DOTE IMIORE                                                       | 130 |

| Peripheral Pin Select (PPS)                                                                                       | PPS Output for dsPIC33EVXXXGM002/102                              |                          |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|

| Control Registers                                                                                                 | Devices                                                           | 50                       |

| Input Sources, Maps Input to Function147                                                                          | PPS Output for dsPIC33EVXXXGM004/104                              |                          |

| Output Selection for Remappable Pins150                                                                           | Devices                                                           | 50                       |

| Pinout I/O Descriptions (table)14                                                                                 | PPS Output for dsPIC33EVXXXGM006/106                              |                          |

| Power-Saving Features133                                                                                          | Devices                                                           | 51                       |

| Clock Frequency and Switching133                                                                                  | PWM                                                               | 60                       |

| Instruction-Based Modes133                                                                                        | PWM Generator 1                                                   | 60                       |

| Idle134                                                                                                           | PWM Generator 2                                                   | 61                       |

| Sleep134                                                                                                          | PWM Generator 3                                                   | 61                       |

| Interrupts Coincident with Power Save                                                                             | Reference Clock                                                   | 53                       |

| Instructions                                                                                                      | SENT1 Receiver                                                    | 49                       |

| Program Address Space31                                                                                           | SENT2 Receiver                                                    | 49                       |

| Construction79                                                                                                    | SPI1 and SPI2                                                     | 45                       |

| Data Access from Program Memory Using                                                                             | System Control                                                    | 53                       |

| Table Instructions81                                                                                              | Timers                                                            |                          |

| Memory Map for dsPIC33EV128GM00X/10X                                                                              | UART1 and UART2                                                   | 45                       |

| Devices                                                                                                           | Registers                                                         |                          |

| Memory Map for dsPIC33EV256GM00X/10X                                                                              | ADxCHS0 (ADCx Input Channel 0 Select)                             | 296                      |

| Devices                                                                                                           | ADxCHS123 (ADCx Input                                             |                          |

| Memory Map for dsPIC33EV32GM00X/10X                                                                               | Channels 1, 2, 3 Select)2                                         | 295                      |

| Devices31                                                                                                         | ADxCON1 (ADCx Control 1)                                          |                          |

| Memory Map for dsPIC33EV64GM00X/10X                                                                               | ADxCON2 (ADCx Control 2)                                          |                          |

| Devices                                                                                                           | ADxCON3 (ADCx Control 3)                                          |                          |

| Table Read Instructions                                                                                           | ADxCON4 (ADCx Control 4)                                          |                          |

| TBLRDH81                                                                                                          | ADxCSSH (ADCx Input Scan Select High)                             |                          |

| TBLRDL                                                                                                            | ADxCSSL (ADCx Input Scan Select Low)                              |                          |

| Program Memory                                                                                                    | ALTDTRx (PWMx Alternate Dead-Time)                                |                          |

| Interrupt/Trap Vectors35                                                                                          | AUXCONx (PWMx Auxiliary Control)                                  |                          |

| Organization                                                                                                      | CHOP (PWMx Chop Clock Generator)                                  |                          |

| Reset Vector                                                                                                      | CLKDIV (Clock Divisor) 1                                          |                          |

| Programmer's Model                                                                                                | CM4CON (Comparator 4 Control)                                     |                          |

| Register Descriptions                                                                                             |                                                                   |                          |

| Register Descriptions23                                                                                           | CMSTAT (Op Amp/Comparator Status) 3 CMxCON (Comparator x Control, | ,03                      |

| R                                                                                                                 | x = 1, 2, 3  or  5)                                               | 004                      |

| Referenced Sources                                                                                                |                                                                   |                          |

| Register Maps                                                                                                     | CMxFLTR (Comparator x Filter Control)                             | )   2                    |

| ADC146                                                                                                            | CMxMSKCON (Comparator x Mask                                      | 110                      |

|                                                                                                                   | Gating Control)                                                   | 310                      |

| CAN1 (WIN (C1CTRL) = 0 or 1)                                                                                      | CMxMSKSRC (Comparator x Mask Source                               |                          |

| CAN1 (WIN (C1CTRL) = 0)                                                                                           | Select Control)                                                   |                          |

| CAN1 (WIN (C1CTRL) = 1)                                                                                           | CORCON (Core Control)                                             |                          |

| Configuration Words                                                                                               | CTMUCON1 (CTMU Control 1)                                         |                          |

| CPU Core41                                                                                                        | CTMUCON2 (CTMU Control 2)                                         |                          |

| CTMU                                                                                                              | CTMUICON (CTMU Current Control)                                   |                          |

| DMAC                                                                                                              | CTXTSTAT (CPU W Register Context Status)                          | 29                       |

| DMT                                                                                                               | CVR1CON (Comparator Voltage Reference                             |                          |

| 12C1                                                                                                              | Control 1) 3                                                      | 315                      |

| Input Capture 1 through Input Capture 444                                                                         | CVR2CON (Comparator Voltage Reference                             |                          |

| Interrupt Controller55                                                                                            | Control 2) 3                                                      | 316                      |

| NVM53                                                                                                             | CxBUFPNT1 (CANx Filters 0-3                                       |                          |

| Op Amp/Comparator58                                                                                               | Buffer Pointer 1)                                                 | 264                      |

| Output Compare57                                                                                                  | CxBUFPNT2 (CANx Filters 4-7                                       |                          |

| Peripheral Input Remap52                                                                                          | Buffer Pointer 2) 2                                               | 265                      |

| PMD54                                                                                                             | CxBUFPNT3 (CANx Filters 8-11                                      |                          |

| PORTA for dsPIC33EVXXXGMX02 Devices63                                                                             | Buffer Pointer 3) 2                                               | 266                      |

| PORTA for dsPIC33EVXXXGMX04 Devices62                                                                             | CxBUFPNT4 (CANx Filters 12-15                                     |                          |

| PORTA for dsPIC33EVXXXGMX06 Devices62                                                                             | Buffer Pointer 4)                                                 | 267                      |

| PORTB for dsPIC33EVXXXGMX02 Devices64                                                                             | CxCFG1 (CANx Baud Rate Configuration 1) 2                         | 262                      |

| PORTB for dsPIC33EVXXXGMX04 Devices64                                                                             | CxCFG2 (CANx Baud Rate Configuration 2) 2                         |                          |

| DODED (                                                                                                           | CACI OZ (CANA Daud Nate Configuration 2)                          |                          |

| PORTB for dsPIC33EVXXXGMX06 Devices63                                                                             |                                                                   | 255                      |

| PORTB for dsPIC33EVXXXGMX06 Devices63 PORTC for dsPIC33EVXXXGMX04 Devices65                                       | CxCTRL1 (CANx Control 1)2                                         |                          |

|                                                                                                                   | CxCTRL1 (CANx Control 1)                                          | 256                      |

| PORTC for dsPIC33EVXXXGMX04 Devices65                                                                             | CxCTRL1 (CANx Control 1)                                          | 256<br>262               |

| PORTC for dsPIC33EVXXXGMX04 Devices65 PORTC for dsPIC33EVXXXGMX06 Devices65                                       | CxCTRL1 (CANx Control 1)                                          | 256<br>262<br>258        |

| PORTC for dsPIC33EVXXXGMX04 Devices65 PORTC for dsPIC33EVXXXGMX06 Devices65 PORTD for dsPIC33EVXXXGMX06 Devices66 | CxCTRL1 (CANx Control 1)                                          | 256<br>262<br>258<br>264 |