Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm006-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-29: PWM GENERATOR 2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13       | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|--------------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT | CLSTAT  | TRGSTAT      | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | _        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH    | PENL    | POLH         | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2     | 0C44  | _       | CLSRC4  | CLSRC3       | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2        | 0C46  |         |         |              |         |           |           |           | PDC2             | <15:0>    |         |          |          |          |          |          |          | 0000          |

| PHASE2      | 0C48  |         |         |              |         |           |           |           | PHASE            | 2<15:0>   |         |          |          |          |          |          |          | 0000          |

| DTR2        | 0C4A  | -       | _       |              |         |           |           |           |                  | DTR2      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2     | 0C4C  |         |         |              |         |           |           |           |                  | ALTDTR    | 2<13:0> |          |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |         |         |              |         |           |           |           | TRGCN            | 1P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON2     | 0C54  | TRGDIV3 | TRGDIV2 | TRGDIV1      | TRGDIV0 | —         | —         | —         | —                |           |         | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP2     | 0C58  |         |         |              |         |           |           |           | PWMCA            | .P2<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON2     | 0C5A  | PHR     | PHF     | PLR          | PLF     | FLTLEBEN  | CLLEBEN   | —         | —                |           |         | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | -       | _       | _            |         |           |           |           |                  |           | LEB<    | :11:0>   |          |          |          |          |          | 0000          |

| AUXCON2     | 0C5E  | -       | -       | _            |         | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> |           | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

|             |       |         |         | (-) <b>D</b> |         |           |           |           |                  |           |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-30: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | —        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON3     | 0C64  | -       | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC3        | 0C66  |         |         |         |         |           |           |           | PDC              | 3<15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE3      | 0C68  |         |         |         |         |           |           |           | PHASI            | E3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR3        | 0C6A  | _       | —       |         |         |           |           |           |                  | DTR3      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR3     | 0C6C  | _       | —       |         |         |           |           |           |                  | ALTDTF    | 3<13:0> |          |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |         |         |         |         |           |           |           | TRGC             | /IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON3     | 0C74  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 |           | _         |           | —                | —         | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP3     | 0C78  |         |         |         |         |           |           |           | PWMCA            | AP3<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON3     | 0C7A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | -         | _                | —         | —       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY3     | 0C7C  | _       | _       | _       | _       |           |           |           |                  |           | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON3     | 0C7E  | _       | _       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | —         | —       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in the data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configure the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses an EDS or a PSV page.

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing. However, this does not include Register Offset Addressing.

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using the Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-43 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when an overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

# TABLE 4-43: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS AND PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| 0/11        |                     |                | Before       |                        |                | After        |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page Description       |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last Page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>Page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>Page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last Page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  | r 1                 | DSRPAG = 0x001 | 1            | PSV Page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>Page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ WII ]             | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>Page  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

**Note 1:** The Register Indirect Addressing now addresses a location in the Base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

**3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

4: Pseudolinear Addressing is not supported for large offsets.

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

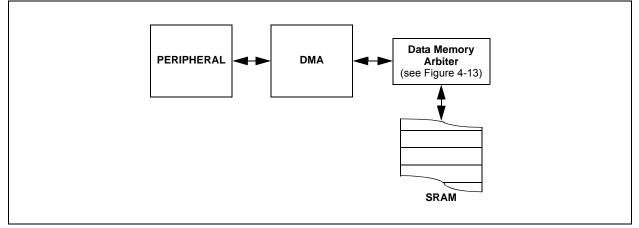

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| U-0          | U-0                  | U-0              | U-0 | U-0              | U-0              | U-0             | U-0    |

|--------------|----------------------|------------------|-----|------------------|------------------|-----------------|--------|

| _            | —                    | —                | —   | —                | —                | —               | —      |

| bit 15       |                      |                  |     |                  |                  |                 | bit    |

|              |                      |                  |     |                  |                  |                 |        |

| U-0          | U-0                  | U-0              | U-0 | R-0              | R-0              | R-0             | R-0    |

| _            | —                    | —                | —   | PWCOL3           | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7        |                      |                  |     |                  |                  |                 | bit    |

|              |                      |                  |     |                  |                  |                 |        |

| Legend:      |                      |                  |     |                  |                  |                 |        |

| R = Readab   | le bit               | W = Writable     | bit | U = Unimpler     | nented bit, read | as '0'          |        |

| -n = Value a | t POR                | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|              |                      |                  |     |                  |                  |                 |        |

| bit 15-4     | Unimplemen           | ted: Read as '   | 0'  |                  |                  |                 |        |

| bit 3        |                      | annel 3 Periph   |     | Ilision Flag bit |                  |                 |        |

|              | $\perp = vvrite col$ | ision is detecte | a   |                  |                  |                 |        |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| 1 = Write collision is detected     |

|-------------------------------------|

| 0 = Write collision is not detected |

|                                     |

0 = Write collision is not detected

1 = Write collision is detected0 = Write collision is not detected

PWCOL2: Channel 2 Peripheral Write Collision Flag bit

PWCOL1: Channel 1 Peripheral Write Collision Flag bit

bit 0 PWCOL0: Channel 0 Peripheral Write Collision Flag bit

- 1 = Write collision is detected

- 0 = Write collision is not detected

bit 2

bit 1

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS7000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. All the pins in the device are 5V tolerant pins.

## 11.1 Parallel I/O (PIO) Ports

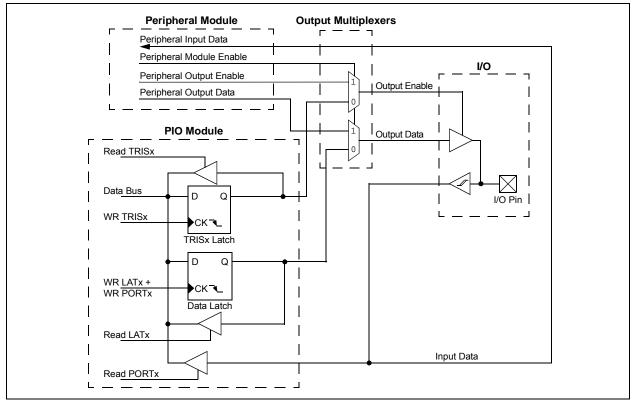

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch; writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means that the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port, because there is no other competing source of output.

### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2013-2016 Microchip Technology Inc.

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits 11111 = OCxRS compare event is used for synchronization 11110 = INT2 is the source for compare timer synchronization 11101 = INT1 is the source for compare timer synchronization 11100 = CTMU Trigger is the source for compare timer synchronization 11011 = ADC1 interrupt is the source for compare timer synchronization 11010 = Analog Comparator 3 is the source for compare timer synchronization 11001 = Analog Comparator 2 is the source for compare timer synchronization 11000 = Analog Comparator 1 is the source for compare timer synchronization 10111 = Analog Comparator 5 is the source for compare timer synchronization 10110 = Analog Comparator 4 is the source for compare timer synchronization 10101 = Capture timer is unsynchronized 10100 = Capture timer is unsynchronized 10011 = Input Capture 4 interrupt is the source for compare timer synchronization 10010 = Input Capture 3 interrupt is the source for compare timer synchronization 10001 = Input Capture 2 interrupt is the source for compare timer synchronization 10000 = Input Capture 1 interrupt is the source for compare timer synchronization 01111 = GP Timer5 is the source for compare timer synchronization 01110 = GP Timer4 is the source for compare timer synchronization 01101 = GP Timer3 is the source for compare timer synchronization 01100 = GP Timer2 is the source for compare timer synchronization 01011 = GP Timer1 is the source for compare timer synchronization 01010 = Compare timer is unsynchronized 01001 = Compare timer is unsynchronized 01000 = Capture timer is unsynchronized 00101 = Compare timer is unsynchronized 00100 = Output Compare 4 is the source for compare timer synchronization<sup>(1,2)</sup> 00011 = Output Compare 3 is the source for compare timer synchronization<sup>(1,2)</sup> 00010 = Output Compare 2 is the source for compare timer synchronization<sup>(1,2)</sup> 00001 = Output Compare 1 is the source for compare timer synchronization<sup>(1,2)</sup>

- 00000 = Compare timer is unsynchronized

- **Note 1:** Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

| U-0          | U-0           | U-0                                 | U-0              | U-0                                            | U-0             | U-0             | U-0            |

|--------------|---------------|-------------------------------------|------------------|------------------------------------------------|-----------------|-----------------|----------------|

|              | —             | _                                   | _                | _                                              |                 | _               |                |

| bit 15       |               |                                     |                  |                                                |                 |                 | bit 8          |

|              |               |                                     |                  |                                                |                 |                 |                |

| U-0          | R/W-0         | R/W-0                               | R/W-0            | R/W-0                                          | R/W-0           | R/W-0           | R/W-0          |

|              | PCIE          | SCIE                                | BOEN             | SDAHT                                          | SBCDE           | AHEN            | DHEN           |

| bit 7        |               |                                     |                  |                                                |                 |                 | bit 0          |

| Legend:      |               |                                     |                  |                                                |                 |                 |                |

| R = Readab   | le bit        | W = Writable I                      | oit              | U = Unimplem                                   | ented bit, read | as '0'          |                |

| -n = Value a | t POR         | '1' = Bit is set                    |                  | '0' = Bit is clea                              |                 | x = Bit is unkn | own            |

|              |               |                                     |                  |                                                |                 |                 |                |

| bit 15-7     | Unimplement   | ted: Read as '(                     | )'               |                                                |                 |                 |                |

| bit 6        | PCIE: Stop Co | ondition Interru                    | pt Enable bit (I | <sup>2</sup> C Slave mode                      | only).          |                 |                |

|              |               | nterrupt on detection interrupts    |                  | condition                                      |                 |                 |                |

| bit 5        |               | •                                   |                  | <sup>2</sup> C Slave mode                      | only)           |                 |                |

| bit 5        |               |                                     | •                | or Restart condi                               | • /             |                 |                |

|              |               | ction interrupts                    |                  |                                                |                 |                 |                |

| bit 4        |               | · Overwrite Ena                     | •                | • •                                            |                 |                 |                |

|              |               |                                     |                  | nd an ACK is g                                 |                 | received addre  | ess/data byte, |

|              |               |                                     |                  | <pre>if the RBF bit =<br/>ed when I2CO\</pre>  |                 |                 |                |

| bit 3        |               | x Hold Time Se                      |                  |                                                |                 |                 |                |

|              |               |                                     |                  | after the falling                              |                 |                 |                |

|              |               |                                     |                  | after the falling                              | -               |                 |                |

| bit 2        |               |                                     |                  | Enable bit (I <sup>2</sup> C<br>mpled low whei |                 | • /             | and state the  |

|              |               | • •                                 |                  | Detection mode                                 |                 |                 | •              |

|              | sequences.    | C                                   |                  |                                                | ,               | 0               |                |

|              |               | collision interr                    |                  |                                                |                 |                 |                |

| bit 1        |               | ss Hold Enable                      | •                |                                                |                 |                 |                |

|              |               |                                     | •                | x for a matchir                                | ng received ad  | dress byte; the | e SCLREL bit   |

|              | ·             | ,                                   |                  | he SCLx will be                                | held low        |                 |                |

| hit 0        |               | holding is disab<br>⊣old Enable bit |                  | do only)                                       |                 |                 |                |

| bit 0        |               |                                     |                  | or a received da                               | ata byte: slave | hardware clears | s the SCLRFI   |

|              | bit (I2CxC    | CON1<12>) and                       |                  |                                                |                 |                 |                |

|              | 0 = Data hold | ling is disabled                    |                  |                                                |                 |                 |                |

#### REGISTER 19-2: I2CxCON2: I2Cx CONTROL REGISTER 2

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0                              | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|----------------------|------------------|------------------|------------------------------------|------------------|-----------------|--------|--|--|

| F15BP3        | F15BP2               | F15BP1           | F15BP0           | F14BP3                             | F14BP2           | F14BP1          | F14BP0 |  |  |

| bit 15        |                      |                  |                  |                                    | •                |                 | bit 8  |  |  |

|               |                      |                  |                  |                                    |                  |                 |        |  |  |

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0                              | R/W-0            | R/W-0           | R/W-0  |  |  |

| F13BP3        | F13BP2               | F13BP1           | F13BP0           | F12BP3                             | F12BP2           | F12BP1          | F12BP0 |  |  |

| bit 7         |                      |                  |                  |                                    |                  |                 | bit 0  |  |  |

|               |                      |                  |                  |                                    |                  |                 |        |  |  |

| Legend:       |                      |                  |                  |                                    |                  |                 |        |  |  |

| R = Readable  | e bit                | W = Writable     | bit              | U = Unimplemented bit, read as '0' |                  |                 |        |  |  |

| -n = Value at | POR                  | '1' = Bit is set |                  | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown   |  |  |

|               |                      |                  |                  |                                    |                  |                 |        |  |  |

| bit 15-12     | F15BP<3:0>:          | RX Buffer Ma     | sk for Filter 15 | 5 bits                             |                  |                 |        |  |  |

|               | 1111 = Filter        | hits received in | n RX FIFO but    | ffer                               |                  |                 |        |  |  |

|               | 1110 = Filter        | hits received in | n RX Buffer 14   | ļ.                                 |                  |                 |        |  |  |

|               | •                    |                  |                  |                                    |                  |                 |        |  |  |

|               | •                    |                  |                  |                                    |                  |                 |        |  |  |

|               | 0001 <b>= Filter</b> | hits received ir | n RX Buffer 1    |                                    |                  |                 |        |  |  |

|               | 0000 <b>= Filter</b> | hits received in | n RX Buffer 0    |                                    |                  |                 |        |  |  |

| bit 11-8      | F14BP<3:0>:          | RX Buffer Ma     | sk for Filter 14 | l bits (same va                    | lues as bits 15- | 12)             |        |  |  |

| bit 7-4       | F13BP<3:0>:          | RX Buffer Ma     | sk for Filter 13 | 3 bits (same va                    | lues as bits 15- | 12)             |        |  |  |

| bit 3-0       | F12BP<3:0>:          | RX Buffer Ma     | sk for Filter 12 | 2 bits (same va                    | lues as bits 15- | 12)             |        |  |  |

|               |                      |                  |                  |                                    |                  |                 |        |  |  |

### REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

# REGISTER 22-26: CxTRmnCON: CANx TX/RX BUFFER mn CONTROL REGISTER

| R/W-0                          | R-0                            | R-0                              | R-0                            | R/W-0                   | R/W-0            | R/W-0           | R/W-0          |

|--------------------------------|--------------------------------|----------------------------------|--------------------------------|-------------------------|------------------|-----------------|----------------|

| TXENn                          | TXABTn                         | TXLARBn                          | TXERRn                         | TXREQn                  | RTRENn           | TXnPRI1         | TXnPRI0        |

| bit 15                         |                                |                                  |                                |                         |                  |                 | bit 8          |

| R/W-0                          | R-0                            | R-0                              | R-0                            | R/W-0                   | R/W-0            | R/W-0           | R/W-0          |

| TXENm                          | TXABTm <sup>(1)</sup>          | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm                  | RTRENm           | TXmPRI1         | TXmPRI0        |

| bit 7                          | 170 DTH                        | TXDARDIN                         | TXER R                         | IXILQIII                |                  |                 | bit (          |

| Logondy                        |                                |                                  |                                |                         |                  |                 |                |

| <b>Legend:</b><br>R = Readable | hit                            | W = Writable                     | hit                            | II – Unimplor           | monted bit read  |                 |                |

|                                |                                |                                  |                                | -                       | nented bit, read |                 |                |

| -n = Value at P                | OR                             | '1' = Bit is set                 |                                | '0' = Bit is cle        | ared             | x = Bit is unkr | lown           |

| bit 15-8                       | See Definition                 | n for bits 7-0, co               | ontrols Buffer n               | 1                       |                  |                 |                |

| bit 7                          |                                | RX Buffer Selec                  |                                |                         |                  |                 |                |

|                                |                                | RBm, is a transi                 |                                |                         |                  |                 |                |

|                                |                                | RBm, is a receiv                 |                                |                         |                  |                 |                |

| bit 6                          | TXABTm: Me                     | essage Abortec                   | l bit <sup>(1)</sup>           |                         |                  |                 |                |

|                                | 1 = Message<br>0 = Message     | was aborted completed trar       | smission succ                  | essfully                |                  |                 |                |

| bit 5                          | TXLARBm: N                     | /lessage Lost A                  | vrbitration bit <sup>(1)</sup> |                         |                  |                 |                |

|                                |                                | lost arbitration                 |                                |                         |                  |                 |                |

|                                | 0 = Message                    | did not lose arl                 | pitration while I              | being sent              |                  |                 |                |

| bit 4                          | TXERRm: Er                     | ror Detected D                   | uring Transmis                 | sion bit <sup>(1)</sup> |                  |                 |                |

|                                |                                | or occurred whi                  |                                |                         |                  |                 |                |

| bit 3                          | TXREQm: Me                     | essage Send R                    | equest bit                     |                         |                  |                 |                |

|                                | 1 = Requests sent              | s that a messag                  | je be sent; the                | bit automatica          | ally clears when | the message     | is successfull |

|                                | 0 = Clearing                   | the bit to '0' wh                | ile set request                | s a message             | abort            |                 |                |

| bit 2                          | RTRENm: Au                     | ito-Remote Tra                   | nsmit Enable b                 | oit                     |                  |                 |                |

|                                |                                | emote transmit<br>emote transmit |                                |                         |                  |                 |                |

| bit 1-0                        | TXmPRI<1:0                     | >: Message Tra                   | ansmission Pri                 | ority bits              |                  |                 |                |

|                                | 11 = Highest<br>10 = High inte | message priori                   |                                |                         |                  |                 |                |

Note: The buffers, SID, EID, DLC, Data Field and Receive Status registers, are located in DMA RAM.

| R/W-0                | U-0                                                        | U-0                                                                                          | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

|----------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|----------------------|----------------------|----------------------|

| ADRC                 |                                                            |                                                                                              | SAMC4 <sup>(1)</sup>                               | SAMC3 <sup>(1)</sup>            | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15               |                                                            |                                                                                              |                                                    |                                 |                      |                      | bit 8                |

| R/W-0                | R/W-0                                                      | R/W-0                                                                                        | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>                                       | ADCS5 <sup>(2)</sup>                                                                         | ADCS4 <sup>(2)</sup>                               | ADCS3 <sup>(2)</sup>            | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                |                                                            |                                                                                              |                                                    |                                 |                      |                      | bit C                |

| Legend:              |                                                            |                                                                                              |                                                    |                                 |                      |                      |                      |

| R = Readable         | bit                                                        | W = Writable I                                                                               | oit                                                | U = Unimplen                    | nented bit, rea      | <b>d as</b> '0'      |                      |

| -n = Value at F      | POR                                                        | '1' = Bit is set                                                                             |                                                    | '0' = Bit is clea               | ared                 | x = Bit is unkr      | nown                 |

| bit 14-13            | 0 = Clock der<br>Unimplemen                                | ernal RC clock<br>ived from syste<br><b>ted:</b> Read as '0                                  | )'                                                 |                                 |                      |                      |                      |

| bit 12-8             | SAMC<4:0>:<br>11111 = 31 T<br>00001 = 1 TA<br>00000 = 0 TA | D                                                                                            | īme bits <sup>(1)</sup>                            |                                 |                      |                      |                      |

| bit 7-0              | 11111111 = '<br>00000010 = '<br>0000001 = '                | ADCx Convers<br>TP • (ADCS<7<br>TP • (ADCS<7<br>TP • (ADCS<7<br>TP • (ADCS<7<br>TP • (ADCS<7 | 0> + 1) = TP •<br>0> + 1) = TP •<br>0> + 1) = TP • | 256 = TAD<br>3 = TAD<br>2 = TAD |                      |                      |                      |

|                      | ese bits are only<br>ese bits are not                      |                                                                                              | -                                                  |                                 | 1 and SSRCG          | 6 (ADxCON1<4         | >)=0.                |

### REGISTER 24-3: ADxCON3: ADCx CONTROL REGISTER 3

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax             | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------------|----------------------------------------|---------------|----------------|--------------------------|

| 46                 | MAC                  | MAC     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | MAC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square and Accumulate                  | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 47                 | MOV                  | MOV     | f,Wn                        | Move f to Wn                           | 1             | 1              | None                     |

|                    |                      | MOV     | f                           | Move f to f                            | 1             | 1              | None                     |

|                    |                      | MOV     | f,WREG                      | Move f to WREG                         | 1             | 1              | None                     |

|                    |                      | MOV     | #litl6,Wn                   | Move 16-bit literal to Wn              | 1             | 1              | None                     |

|                    |                      | MOV.b   | #lit8,Wn                    | Move 8-bit literal to Wn               | 1             | 1              | None                     |

|                    |                      | MOV     | Wn,f                        | Move Wn to f                           | 1             | 1              | None                     |

|                    |                      | MOV     | Wso,Wdo                     | Move Ws to Wd                          | 1             | 1              | None                     |

|                    |                      | MOV     | WREG, f                     | Move WREG to f                         | 1             | 1              | None                     |

|                    |                      | MOV.D   | Wns,Wd                      | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |

|                    |                      | MOV.D   | Ws,Wnd                      | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |

| 48                 | MOVPAG               | MOVPAG  | #lit10,DSRPAG               | Move 10-bit literal to DSRPAG          | 1             | 1              | None                     |

|                    |                      | MOVPAG  | #lit9,DSWPAG                | Move 9-bit literal to DSWPAG           | 1             | 1              | None                     |

|                    |                      | MOVPAG  | #lit8,TBLPAG                | Move 8-bit literal to TBLPAG           | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, DSRPAG                  | Move Ws<9:0> to DSRPAG                 | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, DSWPAG                  | Move Ws<8:0> to DSWPAG                 | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, TBLPAG                  | Move Ws<7:0> to TBLPAG                 | 1             | 1              | None                     |

| 49                 | MOVSAC               | MOVSAC  | Acc,Wx,Wxd,Wy,Wyd,AWB       | Prefetch and store accumulator         | 1             | 1              | None                     |

| 50                 | MPY                  | MPY     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | Multiply Wm by Wn to Accumulator       | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | MPY     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square Wm to Accumulator               | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 51                 | MPY.N                | MPY.N   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | -(Multiply Wm by Wn) to Accumulator    | 1             | 1              | None                     |

| 52                 | MSC                  | MSC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Subtract from Accumulator | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| TABI F 28-2- | INSTRUCTION SET OVERVIEW ( | (CONTINUED) |

|--------------|----------------------------|-------------|

|              |                            |             |

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# dsPIC33EVXXXGM00X/10X FAMILY

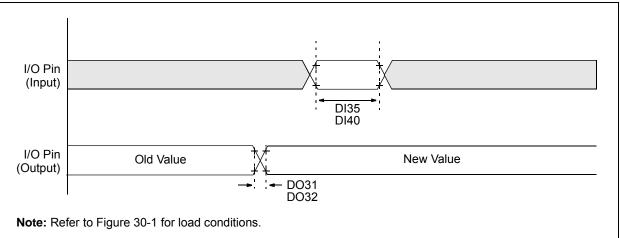

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |            |  |

|--------------------|--------|-----------------------------------|------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                 | Тур. <sup>(1)</sup> | Max. | Units | Conditions |  |

| DO31               | TioR   | Port Output Rise Time             | _                                                    | 5                   | 10   | ns    |            |  |

| DO32               | TIOF   | Port Output Fall Time             | _                                                    | 5                   | 10   | ns    |            |  |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                   | —                   | _    | ns    |            |  |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                    | —                   | _    | TCY   |            |  |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

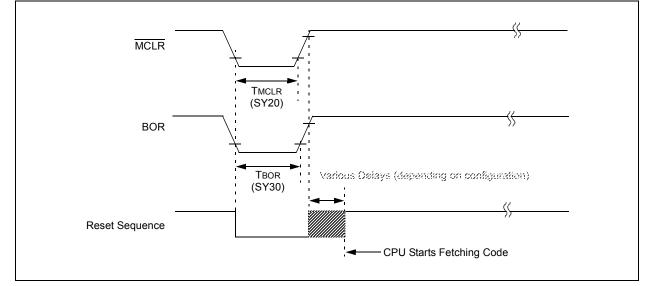

## FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

| AC CHARACTERISTICS |                           |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                                                       |  |  |

|--------------------|---------------------------|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol<br>TLO:SCL         | Characteristic <sup>(3)</sup> |                           | Min.                                                                                                                                                                                                                                                                              | Max. | Units | Conditions                                            |  |  |

| IS10               |                           | Clock Low Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                               |      | μS    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                               | —    | μs    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                               | —    | μS    |                                                       |  |  |

| IS11               | THI:SCL                   | Clock High Time               | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                               | —    | μS    | Device must operate at a minimum of 1.5 MHz           |  |  |

|                    |                           |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                               | _    | μS    | Device must operate at a minimum of 10 MHz            |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                               |      | μs    |                                                       |  |  |

| IS20               | TF:SCL                    | SDAx and SCLx<br>Fall Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                 | 300  | ns    | CB is specified to be from                            |  |  |

|                    |                           |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | 10 to 400 pF                                          |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                 | 100  | ns    |                                                       |  |  |

| IS21               | TR:SCL                    | SDAx and SCLx<br>Rise Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                 | 1000 | ns    | CB is specified to be from                            |  |  |

|                    |                           |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | 10 to 400 pF                                          |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                 | 300  | ns    |                                                       |  |  |

| IS25               | TSU:DAT                   | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                                                                                                                                               | —    | ns    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 100                                                                                                                                                                                                                                                                               | —    | ns    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                                                                               |      | ns    |                                                       |  |  |

| IS26               | THD:DAT                   | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                 |      | μs    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                 | 0.9  | μS    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                 | 0.3  | μs    |                                                       |  |  |

| IS30               | TSU:STA                   | Start Condition<br>Setup Time | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                               | —    | μS    | Only relevant for Repeate<br>Start condition          |  |  |

|                    |                           |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                               | —    | μS    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                              |      | μs    |                                                       |  |  |

| IS31               | THD:STA                   | Start Condition<br>Hold Time  | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                               | —    | μS    | After this period, the first clock pulse is generated |  |  |

|                    |                           |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                               | —    | μs    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                              | —    | μS    |                                                       |  |  |

| IS33               | Tsu:sto                   | Stop Condition<br>Setup Time  | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                               | _    | μS    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                               | _    | μS    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                                                                                                                               | —    | μS    |                                                       |  |  |

| IS34               | THD:STO                   | Stop Condition<br>Hold Time   | 100 kHz mode              | 4                                                                                                                                                                                                                                                                                 | —    | μS    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                               | —    | μs    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                              |      | μs    |                                                       |  |  |

| IS40               | TAA:SCL                   | Output Valid<br>From Clock    | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                 | 3500 | ns    |                                                       |  |  |

|                    |                           |                               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                 | 1000 | ns    |                                                       |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                 | 350  | ns    |                                                       |  |  |

| IS45               | TBF:SDA                   | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                               | —    | μS    | Time the bus must be free                             |  |  |

|                    |                           |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                               |      | μS    | before a new transmission                             |  |  |

|                    |                           |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                               | —    | μS    | can start                                             |  |  |

| IS50               | CB Bus Capacitive Loading |                               |                           | 400                                                                                                                                                                                                                                                                               | pF   |       |                                                       |  |  |

| IS51               | TPGD                      | Pulse Gobbler De              | lay                       | 65                                                                                                                                                                                                                                                                                | 390  | ns    | See Note 2                                            |  |  |

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: The typical value for this parameter is 130 ns.

**3:** These parameters are characterized but not tested in manufacturing.

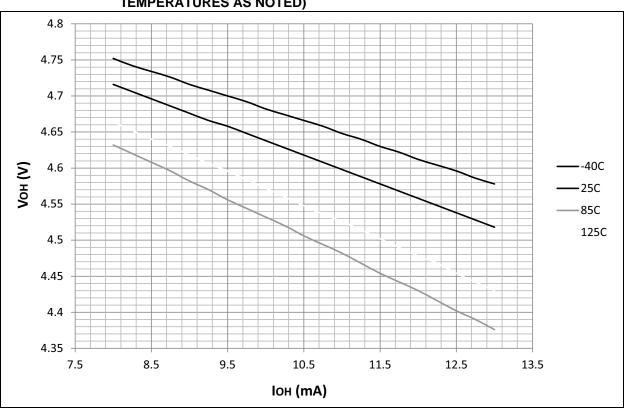

FIGURE 32-31: TYPICAL VOH 4x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

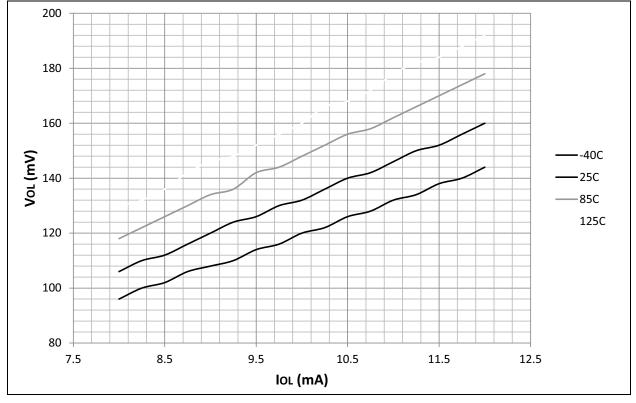

FIGURE 32-32: TYPICAL Vol 8x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

# dsPIC33EVXXXGM00X/10X FAMILY

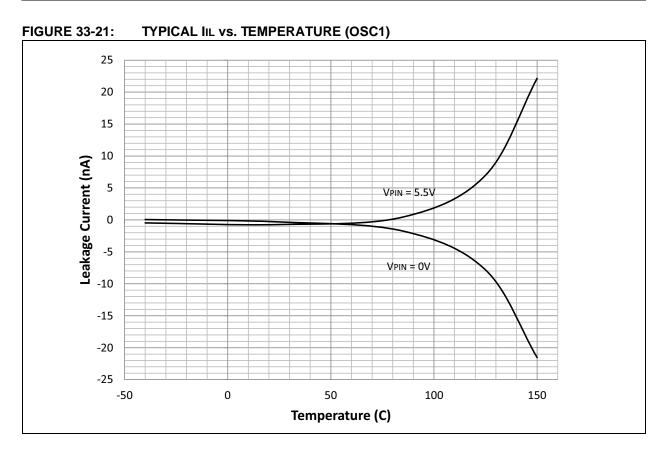

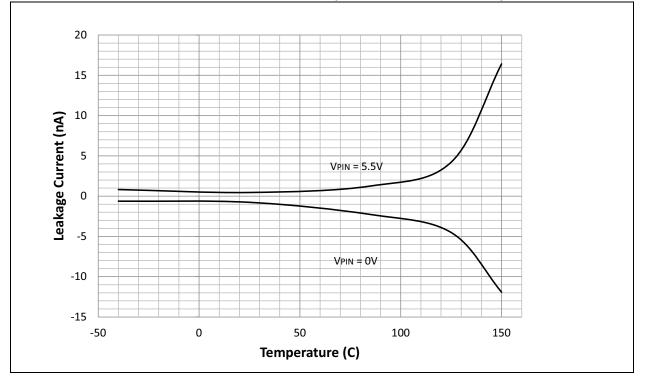

FIGURE 33-22: TYPICAL IIL vs. TEMPERATURE (GENERAL PURPOSE I/Os)

## 33.14 Comparator Op Amp Offset

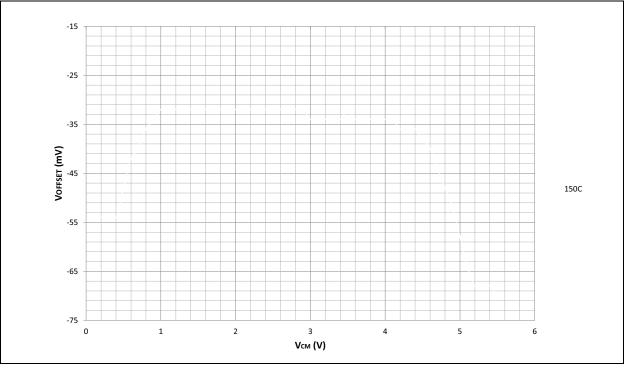

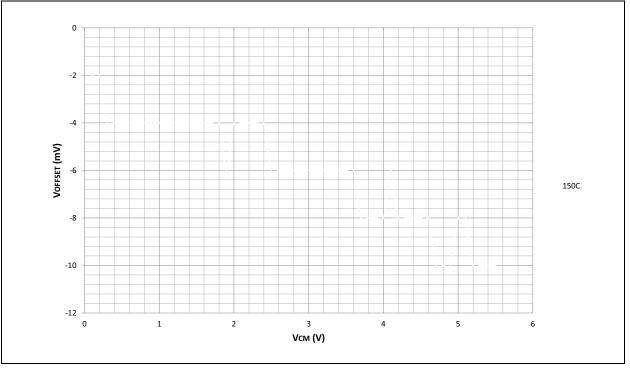

### FIGURE 33-33: TYPICAL COMPARATOR OFFSET vs. Vcm

#### 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |      |          |  |  |

|-------------------------|-------------|----------|------|----------|--|--|

| Dimension               | Limits      | MIN      | NOM  | MAX      |  |  |

| Number of Pins          | N           | 28       |      |          |  |  |

| Pitch                   | e           |          |      | 0.65 BSC |  |  |

| Overall Height          | A           | 0.80     | 0.90 | 1.00     |  |  |

| Standoff                | A1          | 0.00     | 0.02 | 0.05     |  |  |

| Terminal Thickness      | A3          | 0.20 REF |      |          |  |  |

| Overall Width           | E           | 6.00 BSC |      |          |  |  |

| Exposed Pad Width       | E2          | 3.65     | 3.70 | 4.70     |  |  |

| Overall Length          | D           | 6.00 BSC |      |          |  |  |

| Exposed Pad Length      | D2          | 3.65     | 3.70 | 4.70     |  |  |

| Terminal Width          | b           | 0.23     | 0.30 | 0.35     |  |  |

| Terminal Length         | L           | 0.30     | 0.40 | 0.50     |  |  |

| Terminal-to-Exposed Pad | K           | 0.20     | -    | -        |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

# APPENDIX A: REVISION HISTORY

## **Revision A (December 2013)**

This is the initial version of this document.

# Revision B (June 2014)