Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9×9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm006t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE       | 4-16: | PER    | PHERA  | L PIN S | ELECI   | OUIPU   | I REGIS |         | AP FOR  | dsPIC | 33EV) | XXXGMU  | 06/106 L | DEVICES | 5       |         |         |               |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|----------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| RPOR0       | 0670  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | —     | —     | RP20R5  | RP20R4   | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | _     | RP36R5  | RP36R4   | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4   | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | _     | _     | RP40R5  | RP40R4   | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  | —      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | _     |       | RP42R5  | RP42R4   | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR5       | 067A  | —      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | _     |       | RP48R5  | RP48R4   | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR6       | 067C  | —      | _      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | _     |       | RP54R5  | RP54R4   | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR7       | 067E  | —      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     |       | RP56R5  | RP56R4   | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR8       | 0680  | —      | _      | RP70R5  | RP70R4  | RP70R3  | RP70R2  | RP70R1  | RP70R0  | _     |       | RP69R5  | RP69R4   | RP69R3  | RP69R2  | RP69R1  | RP69R0  | 0000          |

| RPOR9       | 0682  | —      | _      | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 | _     |       | RP97R5  | RP97R4   | RP97R3  | RP97R2  | RP97R1  | RP97R0  | 0000          |

| RPOR10      | 0684  | —      | _      | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | _     |       | RP120R5 | RP120R4  | RP120R3 | RP120R2 | RP120R1 | RP120R0 | 0000          |

| RPOR11      | 0686  | _      | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | _     |       | RP177R5 | RP177R4  | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | —      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | —     |       | RP179R5 | RP179R4  | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  | —      | _      | _       | —       | _       | —       | _       | _       | —     |       |         |          | RP181   | R<5:0>  |         |         | 0000          |

#### TABLE 4-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM006/106 DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EVXXXGM00X/10X FAMILY

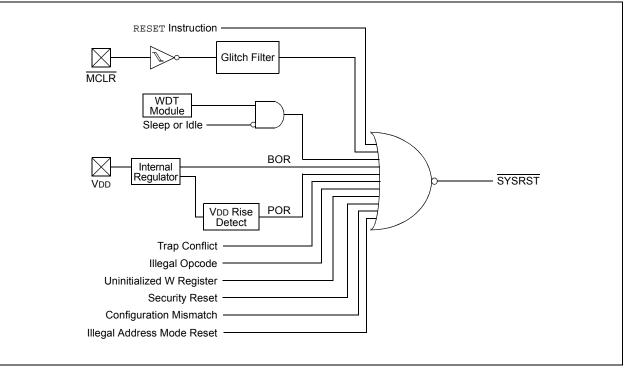

## FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

## REGISTER 14-5: DMTCNTL: DEADMAN TIMER COUNT REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | COUNT | ER<15:8>                                |       |       |       |  |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | COUN  | ΓER<7:0>                                |       |       |       |  |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-0 COUNTER<15:0>: Read Current Contents of Lower DMT Counter bits

## REGISTER 14-6: DMTCNTH: DEADMAN TIMER COUNT REGISTER HIGH

| R/W-0                                                                     | R/W-0                             | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|---------------------------------------------------------------------------|-----------------------------------|-------|-------|------------------------------------|-------|-------|-------|--|--|

|                                                                           |                                   |       | COUNT | ER<31:24>                          |       |       |       |  |  |

| bit 15                                                                    |                                   |       |       |                                    |       |       | bit 8 |  |  |

|                                                                           |                                   |       |       |                                    |       |       |       |  |  |

| R/W-0                                                                     | R/W-0                             | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                           |                                   |       | COUNT | ER<23:16>                          |       |       |       |  |  |

| bit 7                                                                     |                                   |       |       |                                    |       |       | bit 0 |  |  |

|                                                                           |                                   |       |       |                                    |       |       |       |  |  |

| Legend:                                                                   |                                   |       |       |                                    |       |       |       |  |  |

| R = Readable                                                              | R = Readable bit W = Writable bit |       |       | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |                                   |       |       |                                    | nown  |       |       |  |  |

bit 15-0 COUNTER<31:16>: Read Current Contents of Higher DMT Counter bits

## 17.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EVXXXGM00X/10X family devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FDEVOPT<0>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 17-1.

## EXAMPLE 17-1: PWM1 WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| ; FLT32 pin must be pulled lo<br>; Writing to FCLCON1 register                        | ow externally in order to clear and disable the fault<br>r requires unlock sequence                                                                                                                                                              |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mov #0x4321, wll; Loadmov #0x0000, w0; Loadmov w10, PWMKEY; Writmov w11, PWMKEY; Writ | l first unlock key to w10 register<br>l second unlock key to w11 register<br>l desired value of FCLCON1 register in w0<br>e first unlock key to PWMKEY register<br>e second unlock key to PWMKEY register<br>e desired value to FCLCON1 register |

| ; Set PWM ownership and polar<br>; Writing to IOCON1 register                         | rity using the IOCON1 register<br>requires unlock sequence                                                                                                                                                                                       |

| mov #0x4321, wll; Loadmov #0xF000, w0; Loadmov w10, PWMKEY; Writmov w11, PWMKEY; Writ | l first unlock key to w10 register<br>l second unlock key to w11 register<br>l desired value of IOCON1 register in w0<br>e first unlock key to PWMKEY register<br>e second unlock key to PWMKEY register<br>e desired value to IOCON1 register   |

## REGISTER 17-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

| R/W-1                             | R/W-1                              | R/W-1 | R/W-1 | R/W-1                              | R/W-1 | R/W-1           | R/W-1 |  |  |

|-----------------------------------|------------------------------------|-------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                   |                                    |       | PTPE  | R<15:8>                            |       |                 |       |  |  |

| bit 15                            |                                    |       |       |                                    |       |                 | bit 8 |  |  |

|                                   |                                    |       |       |                                    |       |                 |       |  |  |

| R/W-1                             | R/W-1                              | R/W-1 | R/W-1 | R/W-1                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                   |                                    |       | PTPE  | R<7:0>                             |       |                 |       |  |  |

| bit 7                             |                                    |       |       |                                    |       |                 | bit 0 |  |  |

|                                   |                                    |       |       |                                    |       |                 |       |  |  |

| Legend:                           |                                    |       |       |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit |                                    |       |       | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |  |

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

## REGISTER 17-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                                   | R/W-0                                                                                                 | R/W-0                                                                                                 | R/W-0                                                                                                               |  |  |  |

|------------------------------------|-------|----------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                    |       | SEVTC                            | MP<15:8>                                |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

|                                    |       |                                  |                                         |                                                                                                       |                                                                                                       | bit 8                                                                                                               |  |  |  |

|                                    |       |                                  |                                         |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                                   | R/W-0                                                                                                 | R/W-0                                                                                                 | R/W-0                                                                                                               |  |  |  |

|                                    |       | SEVTO                            | CMP<7:0>                                |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

|                                    |       |                                  |                                         |                                                                                                       |                                                                                                       | bit 0                                                                                                               |  |  |  |

|                                    |       |                                  |                                         |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

|                                    |       |                                  |                                         |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

| R = Readable bit W = Writable bit  |       |                                  |                                         | U = Unimplemented bit, read as '0'                                                                    |                                                                                                       |                                                                                                                     |  |  |  |

| -n = Value at POR '1' = Bit is set |       |                                  | '0' = Bit is cleared x = Bit is unknown |                                                                                                       |                                                                                                       |                                                                                                                     |  |  |  |

|                                    | R/W-0 | R/W-0 R/W-0<br>t W = Writable bi | SEVTC<br>R/W-0 R/W-0 R/W-0<br>SEVTC     | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         SEVTCMP<7:0> | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         SEVTCMP<7:0> | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         SEVTCMP<7:0> |  |  |  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

## REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## REGISTER 17-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

|                                    |                                   | DAMA  |       | D/14/ 0                                 |                                    | D 44/ 0 |       |  |  |  |

|------------------------------------|-----------------------------------|-------|-------|-----------------------------------------|------------------------------------|---------|-------|--|--|--|

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0   | R/W-0 |  |  |  |

|                                    |                                   |       | PDC   | x<15:8>                                 |                                    |         |       |  |  |  |

| bit 15                             |                                   |       |       |                                         |                                    |         | bit 8 |  |  |  |

|                                    |                                   |       |       |                                         |                                    |         | ]     |  |  |  |

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0   | R/W-0 |  |  |  |

|                                    |                                   |       | PDC   | \$x<7:0>                                |                                    |         |       |  |  |  |

| bit 7                              |                                   |       |       |                                         |                                    |         | bit 0 |  |  |  |

|                                    |                                   |       |       |                                         |                                    |         |       |  |  |  |

| Legend:                            |                                   |       |       |                                         |                                    |         |       |  |  |  |

| R = Readable                       | R = Readable bit W = Writable bit |       |       |                                         | U = Unimplemented bit, read as '0' |         |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |         |       |  |  |  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

#### REGISTER 17-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0                             | R/W-0            | R/W-0 | R/W-0            | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |  |

|-----------------------------------|------------------|-------|------------------|------------------------------------|--------------------|-------|-------|--|--|

|                                   |                  |       | PHAS             | Ex<15:8>                           |                    |       |       |  |  |

| bit 15                            |                  |       |                  |                                    |                    |       | bit 8 |  |  |

| R/W-0                             | R/W-0            | R/W-0 | R/W-0            | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |  |

|                                   |                  |       | PHAS             | Ex<7:0>                            |                    |       |       |  |  |

| bit 7                             |                  |       |                  |                                    |                    |       | bit 0 |  |  |

| Legend:                           |                  |       |                  |                                    |                    |       |       |  |  |

| R = Readable bit W = Writable bit |                  |       | it               | U = Unimplemented bit, read as '0' |                    |       |       |  |  |

| -n = Value at P                   | '1' = Bit is set |       | '0' = Bit is cle | ared                               | x = Bit is unknown |       |       |  |  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs.

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL.

# dsPIC33EVXXXGM00X/10X FAMILY

## REGISTER 17-12: TRGCONX: PWMx TRIGGER CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | —   | —   | —   | —     |

| bit 15  |         |         |         |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|-----|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| —     | —   | TRGSTRT5 <sup>(1)</sup> | TRGSTRT4 <sup>(1)</sup> | TRGSTRT3 <sup>(1)</sup> | TRGSTRT2 <sup>(1)</sup> | TRGSTRT1 <sup>(1)</sup> | TRGSTRT0 <sup>(1)</sup> |

| bit 7 |     |                         |                         |                         |                         |                         | bit 0                   |

| Legend:           |                  |                                                     |                    |  |  |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

#### bit 15-12 TRGDIV<3:0>: Trigger Output Divider bits

- 1111 = Triggers output for every 16th trigger event

- 1110 = Triggers output for every 15th trigger event

- 1101 = Triggers output for every 14th trigger event

- 1100 = Triggers output for every 13th trigger event

- 1011 = Triggers output for every 12th trigger event

- 1010 = Triggers output for every 11th trigger event

- 1001 = Triggers output for every 10th trigger event

- 1000 = Triggers output for every 9th trigger event

- 0111 = Triggers output for every 8th trigger event

- 0110 = Triggers output for every 7th trigger event

- 0101 = Triggers output for every 6th trigger event

- 0100 = Triggers output for every 5th trigger event 0011 = Triggers output for every 4th trigger event

- 0010 = Triggers output for every 3rd trigger event

- 0001 = Triggers output for every 2nd trigger event

- 0000 = Triggers output for every trigger event

- bit 11-6 **Unimplemented:** Read as '0'

## bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits<sup>(1)</sup>

111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled

- •

- •

000010 = Waits 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Waits 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Waits 0 PWM cycles before generating the first trigger event after the module is enabled

## **Note 1:** The secondary PWM generator cannot generate PWMx trigger interrupts.

## 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. For more information, refer to the SPI specifications in Section 30.0 "Electrical Characteristics".

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

# 21.2 UART Control Registers

## REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                                                                                                                                                                          | DE: UARTx N                                                       |                                                             | TER                             |                                          |                  |                           |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|--|--|--|

| R/W-0                 | U-0                                                                                                                                                                                                                 | R/W-0                                                             | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |  |  |  |

| UARTEN <sup>(1)</sup> |                                                                                                                                                                                                                     | USIDL                                                             | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |  |  |  |

| bit 15                |                                                                                                                                                                                                                     |                                                                   |                                                             | ·                               |                                          |                  | bit 8                     |  |  |  |

| R/W-0, HC             | R/W-0                                                                                                                                                                                                               | R/W-0, HC                                                         | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |  |  |  |

| WAKE                  | LPBACK                                                                                                                                                                                                              | ABAUD                                                             | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |  |  |  |

| bit 7                 |                                                                                                                                                                                                                     |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       |                                                                                                                                                                                                                     |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

| Legend:               |                                                                                                                                                                                                                     | HC = Hardwar                                                      | e Clearable bit                                             | t                               |                                          |                  |                           |  |  |  |

| R = Readable          | e bit                                                                                                                                                                                                               | W = Writable I                                                    | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |  |  |  |

| -n = Value at         | POR                                                                                                                                                                                                                 | '1' = Bit is set                                                  |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |  |  |  |

| bit 15                | 1 = UARTx is                                                                                                                                                                                                        | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U          | ARTx pins are                                               |                                 |                                          |                  |                           |  |  |  |

|                       | is minima                                                                                                                                                                                                           |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

| bit 14                | •                                                                                                                                                                                                                   | ted: Read as '0                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

| bit 13                |                                                                                                                                                                                                                     | Tx Stop in Idle N                                                 |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                         |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup>                                                                                                                                                                                             | Encoder and De                                                    | ecoder Enable                                               | bit <sup>(2)</sup>              |                                          |                  |                           |  |  |  |

|                       |                                                                                                                                                                                                                     | oder and decod                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |

| bit 11                |                                                                                                                                                                                                                     | le Selection for                                                  |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       | 1 = UxRTS p                                                                                                                                                                                                         | oin is in Simplex<br>oin is in Flow Co                            | mode                                                        |                                 |                                          |                  |                           |  |  |  |

| bit 10                |                                                                                                                                                                                                                     | ited: Read as '0                                                  |                                                             |                                 |                                          |                  |                           |  |  |  |

| bit 9-8               | -                                                                                                                                                                                                                   | IARTx Pin Enab                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                                                                                                                                                                        | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |  |  |

| bit 7                 | WAKE: UAR                                                                                                                                                                                                           | Tx Wake-up on                                                     | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |  |  |  |

|                       | in hardwa                                                                                                                                                                                                           | ontinues to sam<br>are on the follow<br>is not enabled            |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |  |  |  |

| bit 6                 | -                                                                                                                                                                                                                   | RTx Loopback                                                      | Mode Select b                                               | it                              |                                          |                  |                           |  |  |  |

|                       |                                                                                                                                                                                                                     | k mode is enab                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       |                                                                                                                                                                                                                     | k mode is disab                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

| "d:<br>tra            | Note 1: Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the<br>"dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for receive<br>transmit operation. |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |

|                       | is feature is only                                                                                                                                                                                                  | -                                                                 |                                                             |                                 | )).                                      |                  |                           |  |  |  |

| <b>3:</b> Th          | is feature is only                                                                                                                                                                                                  | y available on 4                                                  | 4-pin and 64-p                                              | in devices.                     |                                          |                  |                           |  |  |  |

4: This feature is only available on 64-pin devices.

## **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

- bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(3)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

$\frac{\text{If CPOL} = 1 \text{ (inverted polarity):}}{\text{Low-to-high transition of the comparator output.}}$  $\frac{\text{If CPOL} = 0 \text{ (non-inverted polarity):}}{\text{High-to-low transition of the comparator output.}}$

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

- If CPOL = 0 (non-inverted polarity):

- Low-to-high transition of the comparator output.

- 00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to the internal CVREFIN voltage

- 0 = VIN+ input connects to the CxIN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator x Channel Select bits<sup>(1)</sup>

- 11 = Inverting input of op amp/comparator connects to the CxIN4- pin

- 10 = Inverting input of op amp/comparator connects to the CxIN3- pin

- 01 = Inverting input of op amp/comparator connects to the CxIN2- pin

- 00 = Inverting input of op amp/comparator connects to the CxIN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- 3: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| DC CHA       | (unless | -                                    | ise state |                     |       |       |                                                                |

|--------------|---------|--------------------------------------|-----------|---------------------|-------|-------|----------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                       | Min.      | Typ. <sup>(1)</sup> | Max.  | Units | Conditions                                                     |

|              |         | Program Flash Memory                 |           |                     |       |       |                                                                |

| D130         | Eр      | Cell Endurance                       | 10,000    | —                   | _     | E/W   | -40°C to +125°C                                                |

| D131         | Vpr     | VDD for Read                         | 4.5       | —                   | 5.5   | V     |                                                                |

| D132b        | VPEW    | VDD for Self-Timed Write             | 4.5       | —                   | 5.5   | V     |                                                                |

| D134         | TRETD   | Characteristic Retention             | 20        | —                   | —     | Year  | Provided no other specifications are violated, -40°C to +125°C |

| D135         | IDDP    | Supply Current During<br>Programming | _         | 10                  | —     | mA    |                                                                |

| D136a        | Trw     | Row Write Cycle Time                 | 0.657     | —                   | 0.691 | ms    | Trw = 4965 FRC cycles,<br>Ta = +85°C (see <b>Note 2)</b>       |

| D136b        | Trw     | Row Write Cycle Time                 | 0.651     | _                   | 0.698 | ms    | Trw = 4965 FRC cycles,<br>Ta = +125°C (see <b>Note 2)</b>      |

| D137a        | TPE     | Page Erase Time                      | 19.44     | _                   | 20.44 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>     |

| D137b        | TPE     | Page Erase Time                      | 19.24     | —                   | 20.65 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>    |

| D138a        | Tww     | Word Write Cycle Time                | 45.78     | —                   | 48.15 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>        |

| D138b        | Tww     | Word Write Cycle Time                | 45.33     | _                   | 48.64 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>       |

## TABLE 30-13: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Other conditions: FRC = 7.3728 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register.

## TABLE 30-14: ELECTRICAL CHARACTERISTICS: INTERNAL BAND GAP REFERENCE VOLTAGE

| DC CHARACTERISTICS |        |                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |            |  |  |

|--------------------|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Param<br>No.       | Symbol | Characteristic                         | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions |  |  |

| DVR10              | Vbg    | Internal Band Gap Reference<br>Voltage | 1.14                                                                                                                                                                                                                                                                                    | 1.2  | 1.26 | V     |            |  |  |

## TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CH        | AC CHARACTERISTICS |                                         |                           |                                        | (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |               |       |                                                                             |  |  |  |

|--------------|--------------------|-----------------------------------------|---------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-----------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol             | Charac                                  | cteristic <sup>(1)</sup>  | Min.                                   | Тур.                                                                                                                                                             | Max.          | Units | Conditions                                                                  |  |  |  |

| TB10         | T⊤xH               | TxCK High<br>Time                       | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                                                  | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |  |  |  |

| TB11         | ΤτχL               | TxCK Low<br>Time                        | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                                                  | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |  |  |  |

| TB15         | ΤτχΡ               | TxCK Input<br>Period                    | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _                                                                                                                                                                | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |  |  |  |

| TB20         | TCKEXT-<br>MRL     | Delay from I<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                          |                                                                                                                                                                  | 1.75 Tcy + 40 | ns    |                                                                             |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

## TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA       | AC CHARACTERISTICS |                                         |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |               |       |                                        |  |

|--------------|--------------------|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|-------|----------------------------------------|--|

| Param<br>No. | Symbol             | Chara                                   | cteristic <sup>(1)</sup>       | Min. Typ. Max.                                                                                                                                                                                                                                                                        |   |               | Units | Conditions                             |  |

| TC10         | ТтхН               | TxCK High<br>Time                       | Synchronous                    | Tcy + 20                                                                                                                                                                                                                                                                              | — | _             | ns    | Must also meet<br>Parameter TC15       |  |

| TC11         | ΤτxL               | TxCK Low<br>Time                        | Synchronous                    | Tcy + 20                                                                                                                                                                                                                                                                              | _ | —             | ns    | Must also meet<br>Parameter TC15       |  |

| TC15         | ΤτχΡ               | TxCK Input<br>Period                    | Synchronous,<br>with Prescaler | 2 Tcy + 40                                                                                                                                                                                                                                                                            | _ | —             | ns    | N = Prescaler Value<br>(1, 8, 64, 256) |  |

| TC20         | TCKEXT-<br>MRL     | Delay from I<br>Clock Edge<br>Increment | External TxCK<br>to Timer      | 0.75 Tcy + 40                                                                                                                                                                                                                                                                         | — | 1.75 Tcy + 40 | ns    |                                        |  |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

# dsPIC33EVXXXGM00X/10X FAMILY

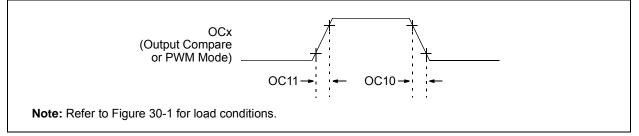

## FIGURE 30-8: OUTPUT COMPARE x (OCx) TIMING CHARACTERISTICS

## TABLE 30-27: OUTPUT COMPARE x (OCx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |  |

|--------------------|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                     | _    |      | ns    | See Parameter DO32 |  |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                     | _    | —    | ns    | See Parameter DO31 |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

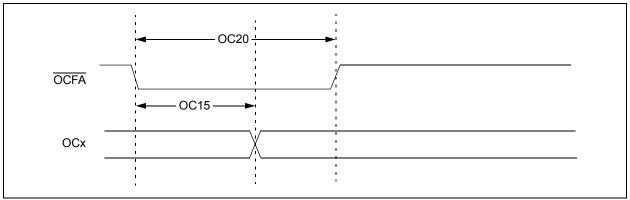

## FIGURE 30-9: OCx/PWMx MODULE TIMING CHARACTERISTICS

## TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                |          |    |            |  |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|----|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                                                                                                                                                                                                                                                    | Min. Typ. Max. |          |    | Conditions |  |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change | —                                                                                                                                                                                                                                                                                       | _              | Tcy + 20 | ns |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                                                                                                                                                                                                                                                                |                | —        | ns |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

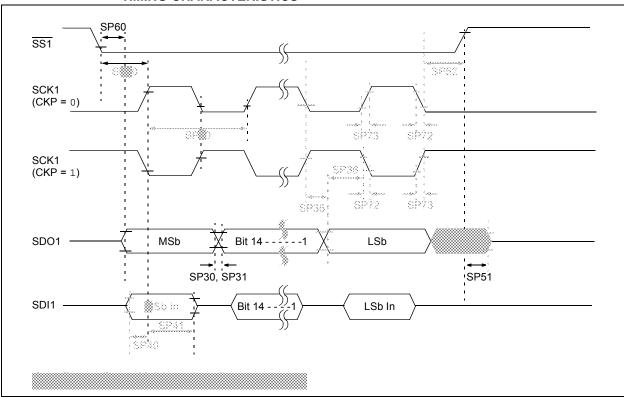

## FIGURE 30-24: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-42:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       |                                              |              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                      |  |  |  |

|--------|-----------------------|----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------|--|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                           |  |  |  |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                 | —            | —                                                                                                                                                                                                                                                                                     | 25   | MHz   | See Note 3                           |  |  |  |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |  |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —            | 6                                                                                                                                                                                                                                                                                     | 20   | ns    |                                      |  |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 20           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                      |  |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCK1 Edge   | 20           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                      |  |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 15           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                      |  |  |  |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120          | —                                                                                                                                                                                                                                                                                     | —    | ns    |                                      |  |  |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10           | —                                                                                                                                                                                                                                                                                     | 50   | ns    | See Note 4                           |  |  |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40 | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Note 4                           |  |  |  |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —            | —                                                                                                                                                                                                                                                                                     | 50   | ns    |                                      |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 40 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.