Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm006t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 3 | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                          |

|-------|---------------------------------------------------------------------------------------------------------|

|       | 1 = CPU Interrupt Priority Level is greater than 7                                                      |

|       | 0 = CPU Interrupt Priority Level is 7 or less                                                           |

| bit 2 | SFA: Stack Frame Active Status bit                                                                      |

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space                            |

| bit 1 | RND: Rounding Mode Select bit                                                                           |

|       | 1 = Biased (conventional) rounding is enabled                                                           |

|       | 0 = Unbiased (convergent) rounding is enabled                                                           |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit                                                    |

|       | 1 = Integer mode is enabled for DSP multiply                                                            |

|       | 0 = Fractional mode is enabled for DSP multiply                                                         |

|       |                                                                                                         |

**Note 1:** This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0             | U-0 | U-0              | U-0   | U-0                                     | U-0 | U-0 | U-0   |  |

|-----------------|-----|------------------|-------|-----------------------------------------|-----|-----|-------|--|

| —               | —   | —                | _     | —                                       | —   | —   | —     |  |

| bit 15          | •   |                  |       |                                         |     |     | bit 8 |  |

|                 |     |                  |       |                                         |     |     |       |  |

| W-0             | W-0 | W-0              | W-0   | W-0                                     | W-0 | W-0 | W-0   |  |

|                 |     |                  | NVMKE | Y<7:0>                                  |     |     |       |  |

| bit 7           |     |                  |       |                                         |     |     | bit 0 |  |

|                 |     |                  |       |                                         |     |     |       |  |

| Legend:         |     |                  |       |                                         |     |     |       |  |

| R = Readable    | bit | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |     |     |       |  |

| -n = Value at F | POR | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: NVM Key Register bits (write-only)

# **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                        | R/W-0 | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 | R/W-0 |

|--------------------------------------------------------------|-------|------------------|-----------------------------------------|-----------------|----------|-------|-------|

|                                                              |       |                  | PAD                                     | <15:8>          |          |       |       |

| bit 15                                                       |       |                  |                                         |                 |          |       | bit 8 |

|                                                              |       |                  |                                         |                 |          |       |       |

| R/W-0                                                        | R/W-0 | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 | R/W-0 |

|                                                              |       |                  | PAI                                     | )<7:0>          |          |       |       |

| bit 7                                                        |       |                  |                                         |                 |          |       | bit 0 |

|                                                              |       |                  |                                         |                 |          |       |       |

| Legend:                                                      |       |                  |                                         |                 |          |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea |       |                  |                                         | mented bit, rea | d as '0' |       |       |

| -n = Value at P                                              | POR   | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |       |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|--------------------------|-------|-------|-------|-------|--|--|--|

| —      | —   |       | CNT<13:8> <sup>(2)</sup> |       |       |       |       |  |  |  |

| bit 15 |     |       |                          |       |       |       | bit 8 |  |  |  |

| R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |  |

| bit 7                   |       |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

| U-0          | U-0                  | U-0              | U-0 | U-0                                     | U-0    | U-0    | U-0    |  |

|--------------|----------------------|------------------|-----|-----------------------------------------|--------|--------|--------|--|

| _            | —                    | —                | —   | —                                       | —      | —      | —      |  |

| bit 15       |                      |                  |     |                                         |        |        | bit    |  |

|              |                      |                  |     |                                         |        |        |        |  |

| U-0          | U-0                  | U-0              | U-0 | R-0                                     | R-0    | R-0    | R-0    |  |

| _            | —                    | —                | —   | PWCOL3                                  | PWCOL2 | PWCOL1 | PWCOL0 |  |

| bit 7        |                      |                  |     |                                         |        |        | bit    |  |

|              |                      |                  |     |                                         |        |        |        |  |

| Legend:      |                      |                  |     |                                         |        |        |        |  |

| R = Readab   | le bit               | W = Writable     | bit | U = Unimplemented bit, read as '0'      |        |        |        |  |

| -n = Value a | t POR                | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |        |        |        |  |

|              |                      |                  |     |                                         |        |        |        |  |

| bit 15-4     | Unimplemen           | ted: Read as '   | 0'  |                                         |        |        |        |  |

| bit 3        |                      | annel 3 Periph   |     | Ilision Flag bit                        |        |        |        |  |

|              | $\perp = vvrite col$ | ision is detecte | a   |                                         |        |        |        |  |

# REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| 1 = Write collision is detected     |

|-------------------------------------|

| 0 = Write collision is not detected |

|                                     |

0 = Write collision is not detected

1 = Write collision is detected0 = Write collision is not detected

PWCOL2: Channel 2 Peripheral Write Collision Flag bit

PWCOL1: Channel 1 Peripheral Write Collision Flag bit

bit 0 PWCOL0: Channel 0 Peripheral Write Collision Flag bit

- 1 = Write collision is detected

- 0 = Write collision is not detected

bit 2

bit 1

| R/W-0           | R/W-0                                  | R/W-0                          | R/W-0                         | R/W-0                                           | R/W-0              | U-0             | U-0            |

|-----------------|----------------------------------------|--------------------------------|-------------------------------|-------------------------------------------------|--------------------|-----------------|----------------|

| PHR             | PHF                                    | PLR                            | PLF                           | FLTLEBEN                                        | CLLEBEN            |                 | _              |

| bit 15          |                                        | L                              |                               |                                                 |                    |                 | bit 8          |

|                 |                                        |                                |                               |                                                 |                    |                 |                |

| U-0             | U-0                                    | R/W-0                          | R/W-0                         | R/W-0                                           | R/W-0              | R/W-0           | R/W-0          |

| —               |                                        | BCH <sup>(1)</sup>             | BCL <sup>(1)</sup>            | BPHH                                            | BPHL               | BPLH            | BPLL           |

| bit 7           |                                        |                                |                               |                                                 |                    |                 | bit (          |

| Legend:         |                                        |                                |                               |                                                 |                    |                 |                |

| R = Readable b  | nit                                    | W = Writable                   | hit                           | II = I Inimpler                                 | mented bit, read   | as '0'          |                |

| -n = Value at P |                                        | '1' = Bit is set               |                               | '0' = Bit is cle                                |                    | x = Bit is unk  | nown           |

|                 |                                        |                                |                               |                                                 |                    | X Bitle dill    |                |

| bit 15          | PHR: PWMxH                             | Rising Edge                    | Trigger Enabl                 | e bit                                           |                    |                 |                |

|                 |                                        |                                |                               |                                                 | Blanking count     | ter             |                |

|                 | 0 = Leading-E                          | Edge Blanking                  | gnores the ri                 | sing edge of PV                                 | VMxH               |                 |                |

| bit 14          |                                        | I Falling Edge                 |                               |                                                 |                    |                 |                |

|                 | 0                                      | 0                              | 00                            | e Leading-Edge<br>alling edge of P <sup>1</sup> | e Blanking coun    | ter             |                |

| bit 13          | -                                      | Rising Edge T                  | -                             |                                                 |                    |                 |                |

| DIL 15          |                                        | • •                            |                               |                                                 | Blanking count     | er              |                |

|                 |                                        |                                |                               | sing edge of PV                                 |                    |                 |                |

| bit 12          | PLF: PWMxL                             | Falling Edge 1                 | rigger Enable                 | e bit                                           |                    |                 |                |

|                 |                                        |                                |                               |                                                 | Blanking count     | ter             |                |

|                 | •                                      | • •                            | •                             | alling edge of P                                |                    |                 |                |

| bit 11          |                                        |                                |                               | anking Enable I                                 |                    |                 |                |

|                 |                                        |                                |                               | he selected Fa<br>to the selected               |                    |                 |                |

| bit 10          | •                                      | • •                            |                               | Edge Blanking E                                 | •                  |                 |                |

|                 |                                        |                                | -                             | he selected cur                                 |                    |                 |                |

|                 | 0 = Leading-E                          | Edge Blanking                  | s not applied                 | to the selected                                 | l current-limit in | put             |                |

| bit 9-6         | -                                      | ted: Read as '                 |                               |                                                 |                    |                 |                |

| bit 5           |                                        |                                |                               | al High Enable                                  |                    |                 |                |

|                 |                                        |                                |                               | Fault input sigr<br>ng signal is hig            | nals) when seled   | cted blanking s | signal is high |

| bit 4           |                                        | •                              |                               | al Low Enable b                                 |                    |                 |                |

|                 |                                        | •                              | •••                           |                                                 | nals) when seled   | cted blanking s | signal is low  |

|                 |                                        |                                |                               | ng signal is low                                |                    | 0               | 5              |

| bit 3           |                                        | ing in PWMxH                   | -                             |                                                 |                    |                 |                |

|                 |                                        |                                |                               |                                                 | nals) when the F   | PWMxH output    | is high        |

| h:# 0           |                                        | ng when the P                  | -                             | -                                               |                    |                 |                |

| bit 2           |                                        | ng in PWMxH                    |                               |                                                 | nals) when the F   |                 | ic low         |

|                 |                                        | ng when the P                  |                               |                                                 |                    | www.kirioutput  | . 15 10 W      |

| bit 1           |                                        | ng in PWMxL I                  |                               |                                                 |                    |                 |                |

|                 |                                        | -                              | -                             |                                                 | nals) when the F   | PWMxL output    | is hiah        |

|                 |                                        |                                |                               |                                                 |                    |                 |                |

|                 | 0 = No blankii                         | ng when the P                  | WMxL output                   | is high                                         |                    |                 |                |

| bit 0           | BPLL: Blanki                           | ng when the P<br>ng in PWMxL L | ow Enable b                   | it                                              |                    |                 | -              |

| bit 0           | <b>BPLL:</b> Blankii<br>1 = State blan | ng when the P<br>ng in PWMxL L | ow Enable b<br>t-limit and/or | it<br>Fault input sigr                          | nals) when the F   | PWMxL output    | -              |

Note 1: The blanking signal is selected through the BLANKSEL<3:0> bits in the AUXCONx register.

# 18.2 SPI Control Registers

### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0           | U-0                                                                                                | R/W-0                                  | U-0                             | U-0                | R/W-0                       | R/W-0                  | R/W-0          |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------|-----------------------------|------------------------|----------------|--|--|--|

| SPIEN           | _                                                                                                  | SPISIDL                                |                                 | _                  | SPIBEC2                     | SPIBEC1                | SPIBEC0        |  |  |  |

| bit 15          |                                                                                                    |                                        |                                 |                    |                             |                        | bit 8          |  |  |  |

|                 |                                                                                                    |                                        |                                 |                    |                             |                        |                |  |  |  |

| R/W-0           | R/C-0, HS                                                                                          | R/W-0                                  | R/W-0                           | R/W-0              | R/W-0                       | R-0, HS, HC            | R-0, HS, HC    |  |  |  |

| SRMPT           | SPIROV                                                                                             | SRXMPT                                 | SISEL2                          | SISEL1             | SISEL0                      | SPITBF                 | SPIRBF         |  |  |  |

| bit 7           |                                                                                                    |                                        |                                 |                    |                             |                        | bit C          |  |  |  |

|                 |                                                                                                    |                                        |                                 |                    |                             |                        |                |  |  |  |

| Legend:         |                                                                                                    | HC = Hardware                          | e Clearable bit                 |                    | are Settable b              |                        |                |  |  |  |

| R = Readable    |                                                                                                    | W = Writable b                         | pit                             | U = Unimple        | mented bit, re              | ead as '0'             |                |  |  |  |

| -n = Value at I | POR                                                                                                | '1' = Bit is set                       |                                 | '0' = Bit is cle   | eared                       | C = Clearable          | e bit          |  |  |  |

| bit 15          | SPIEN: SPIX                                                                                        | Enable bit                             |                                 |                    |                             |                        |                |  |  |  |

| bit 10          |                                                                                                    | he SPIx module                         | and configure                   | s SCKx SDO         | $c$ SDIx and $\overline{S}$ | <u>Sx</u> as serial po | rt pins        |  |  |  |

|                 |                                                                                                    | the SPIx module                        | •                               |                    |                             |                        | it pino        |  |  |  |

| bit 14          | Unimplemen                                                                                         | ted: Read as '0                        | ,                               |                    |                             |                        |                |  |  |  |

| bit 13          | SPISIDL: SP                                                                                        | Ix Stop in Idle M                      | ode bit                         |                    |                             |                        |                |  |  |  |

|                 |                                                                                                    | ues the SPIx mo<br>s the SPIx modu     |                                 |                    | vice enters Idl             | e mode                 |                |  |  |  |

| bit 12-11       |                                                                                                    | ted: Read as '0                        | -                               |                    |                             |                        |                |  |  |  |

| bit 10-8        | SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)                        |                                        |                                 |                    |                             |                        |                |  |  |  |

|                 | Master mode                                                                                        |                                        |                                 | ,                  |                             |                        |                |  |  |  |

|                 | Slave mode:                                                                                        | Plx transfers are                      |                                 |                    |                             |                        |                |  |  |  |

| bit 7           | SRMPT: SPIX                                                                                        | Shift Register                         | (SPIxSR) Empt                   | ty bit (valid in E | Enhanced But                | fer mode)              |                |  |  |  |

|                 | 1 = The SPIx                                                                                       | Shift register is<br>Shift register is | empty and rea                   | •                  |                             | -                      |                |  |  |  |

| bit 6           |                                                                                                    | x Receive Over                         |                                 |                    |                             |                        |                |  |  |  |

|                 | 1 = A new b<br>previous                                                                            | yte/word is com<br>data in the SPI     | pletely receive<br>BUF register | ed and discard     | led; the user               | application ha         | s not read the |  |  |  |

| L:4 F           |                                                                                                    | has not occurre                        |                                 | lid in Enhance     |                             | - )                    |                |  |  |  |

| bit 5           | <b>SRXMPT:</b> SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)<br>1 = RX FIFO is empty |                                        |                                 |                    |                             |                        |                |  |  |  |

|                 | 1 = RX FIFO<br>0 = RX FIFO                                                                         |                                        |                                 |                    |                             |                        |                |  |  |  |

| bit 4-2         |                                                                                                    | SPIx Buffer Inte                       | errupt Mode bit                 | s (valid in Enh    | anced Buffer                | mode)                  |                |  |  |  |

|                 |                                                                                                    | pt when the SP                         | -                               |                    |                             | /                      |                |  |  |  |

|                 | 110 = Interrupt when the last bit is shifted into SPIxSR, and as a result, the TX FIFO is empty    |                                        |                                 |                    |                             |                        |                |  |  |  |

|                 | 100 = Interru                                                                                      | pt when the las<br>pt when one da      |                                 |                    |                             |                        |                |  |  |  |

|                 |                                                                                                    | ry location<br>pt when the SP          | ly receive buffe                | er is full (SPIRI  | RF hit is set)              |                        |                |  |  |  |

|                 |                                                                                                    | pt when the SP                         |                                 |                    |                             |                        |                |  |  |  |

|                 | 001 = Interru                                                                                      | pt when data is                        | available in the                | e SPIx receive     | buffer (SRM                 |                        |                |  |  |  |

|                 | 000 = Interru                                                                                      |                                        |                                 |                    |                             |                        |                |  |  |  |

# 21.1 UART Helpful Tips

- In multi-node direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin, depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

2. The first character received on wake-up from Sleep mode, caused by activity on the UxRX pin of the UART module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid. This is to be expected.

| U-0           | R/W-x             | U-0                                     | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x     |

|---------------|-------------------|-----------------------------------------|------------------|------------------|------------------|-----------------|-----------|

| _             | WAKFIL            | _                                       | _                | _                | SEG2PH2          | SEG2PH1         | SEG2PH0   |

| bit 15        |                   |                                         |                  |                  |                  | •               | bit 8     |

|               | 5444              |                                         | <b>5</b> 444     |                  |                  | <b>—</b>        |           |

| R/W-x         | R/W-x             | R/W-x                                   | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x     |

| SEG2PHTS      | SAM               | SEG1PH2                                 | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0    |

| bit 7         |                   |                                         |                  |                  |                  |                 | bit 0     |

| Legend:       |                   |                                         |                  |                  |                  |                 |           |

| R = Readable  | e bit             | W = Writable                            | bit              | U = Unimplen     | nented bit, read | <b>l as</b> '0' |           |

| -n = Value at | POR               | '1' = Bit is set                        |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown      |

|               |                   |                                         |                  |                  |                  |                 |           |

| bit 15        | Unimplemer        | nted: Read as '                         | o'               |                  |                  |                 |           |

| bit 14        | WAKFIL: Sel       | lect CAN Bus Li                         | ine Filter for V | Vake-up bit      |                  |                 |           |

|               |                   | N bus line filter<br>line filter is not |                  |                  |                  |                 |           |

| bit 13-11     |                   | ine litter is not<br>ited: Read as '    |                  | e-up             |                  |                 |           |

| bit 10-8      | •                 | D>: Phase Segn                          |                  |                  |                  |                 |           |

| DIL 10-0      | 111 = Length      | -                                       |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               | •<br>000 = Length | is 1 x To                               |                  |                  |                  |                 |           |

| bit 7         | •                 | Phase Segmer                            | nt 2 Time Sele   | ect bit          |                  |                 |           |

|               | 1 = Freely pr     | -                                       |                  |                  | essing Time (IP  | T), whichever i | s greater |

| bit 6         | SAM: Sample       | e of the CAN Bu                         | us Line bit      |                  |                  |                 |           |

|               |                   | s sampled three<br>s sampled once       |                  |                  |                  |                 |           |

| bit 5-3       |                   | <b>)&gt;:</b> Phase Segr                | -                |                  |                  |                 |           |

|               | 111 = Length      | -                                       |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               | 000 = Length      | n is 1 x Tq                             |                  |                  |                  |                 |           |

| bit 2-0       | PRSEG<2:0         | - Propagation                           | Time Segmen      | t bits           |                  |                 |           |

|               | 111 = Length      | n is 8 x Tq                             |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               | •                 |                                         |                  |                  |                  |                 |           |

|               |                   |                                         |                  |                  |                  |                 |           |

## REGISTER 22-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

| R/W-0           | R/W-0                                                                                                                                                                                                                                        | R/W-0            | R/W-0           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------------|------------------|--------------------|---------|--|

| F15MSK1         | F15MSK0                                                                                                                                                                                                                                      | F14MSK1          | F14MSK0         | F13MSK'              | F13MSK0          | F12MSK1            | F12MSK0 |  |

| bit 15          |                                                                                                                                                                                                                                              |                  |                 |                      |                  |                    | bit 8   |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                        | R/W-0            | R/W-0           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |  |

| F11MSK1         | F11MSK0                                                                                                                                                                                                                                      | F10MSK1          | F10MSK0         | F9MSK1               | F9MSK0           | F8MSK1             | F8MSK0  |  |

| bit 7           |                                                                                                                                                                                                                                              |                  |                 |                      |                  |                    | bit C   |  |

| Legend:         |                                                                                                                                                                                                                                              |                  |                 |                      |                  |                    |         |  |

| R = Readable    | bit                                                                                                                                                                                                                                          | W = Writable bit |                 | U = Unimpler         | mented bit, read | <b>l as</b> '0'    |         |  |

| -n = Value at I | POR                                                                                                                                                                                                                                          | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |  |

| bit 15-14       | 5-14 <b>F15MSK&lt;1:0&gt;:</b> Mask Source for Filter 15 bit<br>11 = Reserved<br>10 = Acceptance Mask 2 registers contain the mask<br>01 = Acceptance Mask 1 registers contain the mask<br>00 = Acceptance Mask 0 registers contain the mask |                  |                 |                      |                  |                    |         |  |

| bit 13-12       |                                                                                                                                                                                                                                              |                  |                 | ,                    | es as bits 15-14 | ,                  |         |  |

| bit 11-10       |                                                                                                                                                                                                                                              |                  |                 |                      |                  |                    |         |  |

| bit 9-8         | F12MSK<1:0>: Mask Source for Filter 12 bit (same values as bits 15-14)                                                                                                                                                                       |                  |                 |                      |                  |                    |         |  |

| bit 7-6         | F11MSK<1:0>: Mask Source for Filter 11 bit (same values as bits 15-14)                                                                                                                                                                       |                  |                 |                      |                  |                    |         |  |

| bit 5-4         | F10MSK<1:0                                                                                                                                                                                                                                   | >: Mask Sourc    | e for Filter 10 | bit (same valu       | es as bits 15-14 | +)                 |         |  |

| bit 3-2         | F9MSK<1:0>: Mask Source for Filter 9 bit (same values as bits 15-14)                                                                                                                                                                         |                  |                 |                      |                  |                    |         |  |

|                 |                                                                                                                                                                                                                                              |                  |                 |                      |                  |                    |         |  |

# REGISTER 22-19: CxFMSKSEL2: CANx FILTERS 15-8 MASK SELECTION REGISTER 2

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bits 15-14)

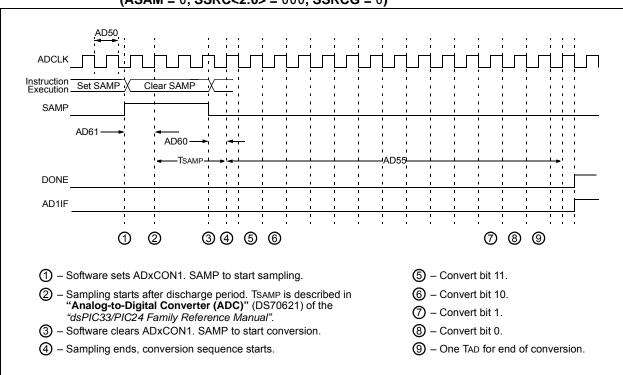

#### REGISTER 24-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:                                                                                                                                                         |

|         | 111 = Reserved<br>110 = Reserved                                                                                                                                      |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Reserved                                                                                                                                                        |

|         | 011 = Reserved                                                                                                                                                        |

|         | 010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | If SSRCG = 0:                                                                                                                                                         |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                             |

|         | 110 = CTMU ends sampling and starts conversion                                                                                                                        |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Timer5 compare ends sampling and starts conversion                                                                                                              |

|         | 011 = PWM primary Special Event Trigger ends sampling and starts conversion<br>010 = Timer3 compare ends sampling and starts conversion                               |

|         | 001 = Active transition on the INTO pin ends sampling and starts conversion                                                                                           |

|         | 000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)                                                                                |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                |

| 511 4   | See SSRC<2:0> for details.                                                                                                                                            |

| 1.1.0   |                                                                                                                                                                       |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                    |

|         | In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':<br>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x) or samples CH0 and CH1 |

|         | simultaneously (when CHPS<1:0> = 01)                                                                                                                                  |

|         | 0 = Samples multiple channels individually in sequence                                                                                                                |

| bit 2   | ASAM: ADCx Sample Auto-Start bit                                                                                                                                      |

|         | 1 = Sampling begins immediately after last conversion; SAMP bit is auto-set                                                                                           |

|         | 0 = Sampling begins when SAMP bit is set                                                                                                                              |

| bit 1   | SAMP: ADCx Sample Enable bit                                                                                                                                          |

|         | 1 = ADCx Sample-and-Hold amplifiers are sampling                                                                                                                      |

|         | 0 = ADCx Sample-and-Hold amplifiers are holding                                                                                                                       |

|         | If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If                                                                  |

|         | SSRC<2:0> = 000, software can write '0' to end sampling and start conversion. If SSRC<2:0> $\neq$ 000,                                                                |

|         | automatically cleared by hardware to end sampling and start conversion.                                                                                               |

| bit 0   | DONE: ADCx Conversion Status bit <sup>(1)</sup>                                                                                                                       |

|         | 1 = ADCx conversion cycle is completed.                                                                                                                               |

|         | 0 = ADCx conversion has not started or is in progress                                                                                                                 |

|         | Automatically set by hardware when conversion is complete. Software can write '0' to clear DONE bit                                                                   |

|         | status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress.                                                              |

|         | Automatically cleared by hardware at the start of a new conversion.                                                                                                   |

**Note 1:** Do not clear the DONE bit in software if auto-sample is enabled (ASAM = 1).

# dsPIC33EVXXXGM00X/10X FAMILY

#### FIGURE 30-34: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

#### TABLE 31-13: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |                     |      |       |                    |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min. | Тур. <sup>(1)</sup> | Max. | Units | Conditions         |

| HOS50              | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range                                                                 | 0.8  | _                   | 8.0  | MHz   | ECPLL, XTPLL modes |

| HOS51              | Fsys   | On-Chip VCO System<br>Frequency                                                                                                     | 120  | —                   | 340  | MHz   |                    |

| HOS52              | TLOCK  | PLL Start-up Time (Lock Time)                                                                                                       | 0.9  | 1.5                 | 3.1  | ms    |                    |

| HOS53              | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                                                                                              | -3   | 0.5                 | 3    | %     |                    |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{\sqrt{Time Base or Communication Clock}}}}$$

For example, if Fosc = 120 MHz and the SPI bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 31-14: INTERNAL FRC ACCURACY

| AC CHA                                             | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |     |       |                                                                        |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------------------------------------------------------------------|--|--|

| Param<br>No.                                       | Characteristic                                                                                                                 | Min | Тур | Max | Units | Conditions                                                             |  |  |

| Internal FRC Accuracy @ FRC Frequency = 7.3728 MHz |                                                                                                                                |     |     |     |       |                                                                        |  |  |

| HF20C                                              | FRC                                                                                                                            | -3  | 1   | +3  | %     | $-40^{\circ}C \leq TA \leq +150^{\circ}C  VDD = 4.5V \text{ to } 5.5V$ |  |  |

#### TABLE 31-15: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICSStandard Operating Conditions: 4.5V to 5.5V (unless otherwise state<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |                |     |     |     |       | otherwise stated)                         |                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----|-------|-------------------------------------------|--------------------|

| Param<br>No.                                                                                                                                           | Characteristic | Min | Тур | Max | Units | Conditions                                |                    |

| LPRC @ 32.768 kHz <sup>(1,2)</sup>                                                                                                                     |                |     |     |     |       |                                           |                    |

| HF21C                                                                                                                                                  | LPRC           | -30 | 10  | +30 | %     | $-40^{\circ}C \leq TA \leq +150^{\circ}C$ | VDD = 4.5V to 5.5V |

Note 1: Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TWDT1). See Section 27.5 "Watchdog Timer (WDT)" for more information.

© 2013-2016 Microchip Technology Inc.

# dsPIC33EVXXXGM00X/10X FAMILY

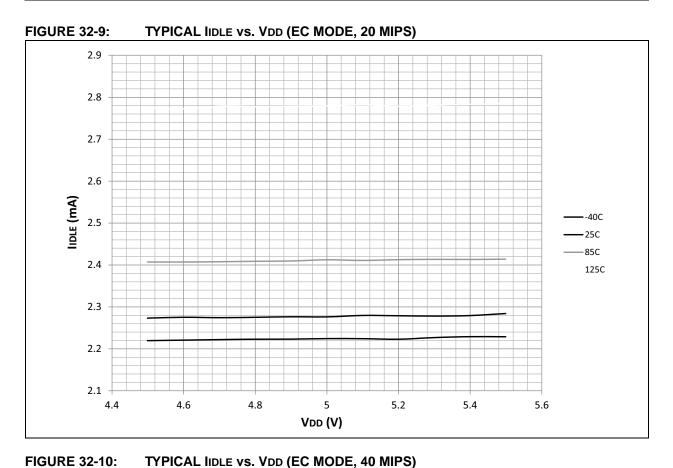

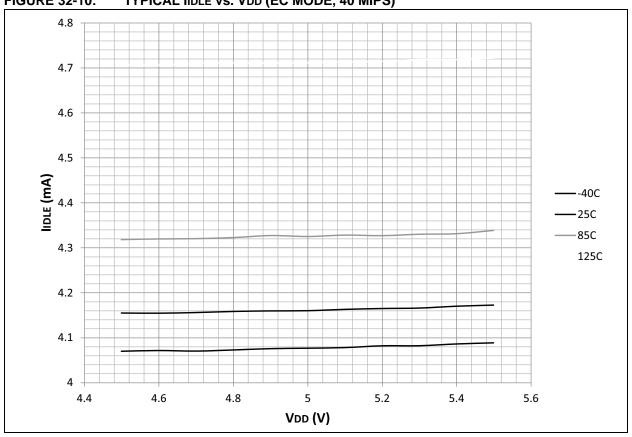

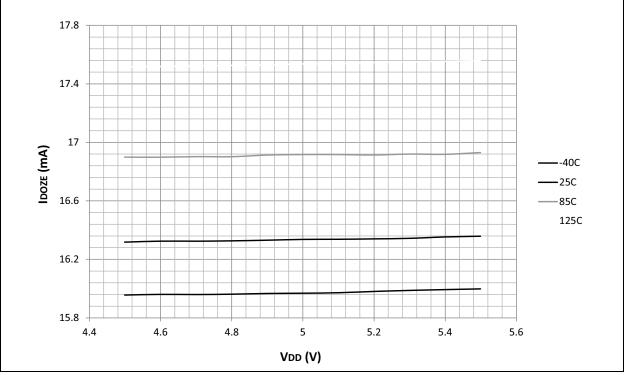

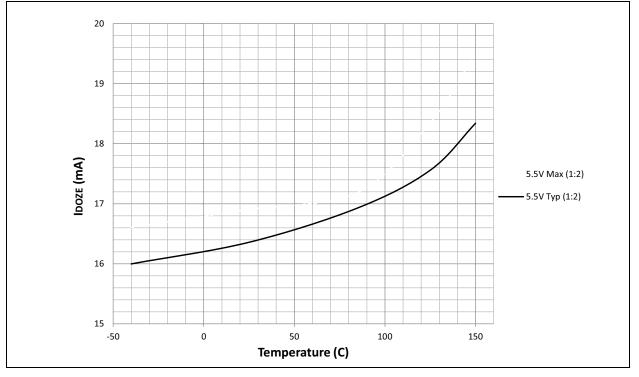

#### 32.3 IDOZE

FIGURE 32-13: TYPICAL IDOZE vs. VDD (DOZE 1:2, 70 MIPS)

FIGURE 32-14: TYPICAL/MAXIMUM IDOZE vs. TEMPERATURE (DOZE 1:2, 70 MIPS)

# dsPIC33EVXXXGM00X/10X FAMILY

# FIGURE 33-15: **TYPICAL/MAXIMUM** ∆IwDT vs. **TEMPERATURE** 12 10 8 IPD (NA) 6 5.5V Max <del>-</del> 5.5V Typ 4 2 0 -50 0 50 100 150 **Temperature (C)**

# 33.5 FRC

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N                | MILLIMETERS    |           |      |

|--------------------------|------------------|----------------|-----------|------|

| Dimension                | Dimension Limits |                | NOM       | MAX  |

| Number of Leads          | Ν                |                | 44        |      |

| Lead Pitch               | е                |                | 0.80 BSC  |      |

| Overall Height           | Α                | -              | -         | 1.20 |

| Standoff                 | A1               | 0.05           | -         | 0.15 |

| Molded Package Thickness | A2               | 0.95           | 1.00      | 1.05 |

| Overall Width            | Е                | 12.00 BSC      |           |      |

| Molded Package Width     | E1               | 10.00 BSC      |           |      |

| Overall Length           | D                | 12.00 BSC      |           |      |

| Molded Package Length    | D1               |                | 10.00 BSC |      |

| Lead Width               | b                | 0.30           | 0.37      | 0.45 |

| Lead Thickness           | С                | 0.09           | -         | 0.20 |

| Lead Length              | L                | 0.45 0.60 0.75 |           | 0.75 |

| Footprint                | L1               | 1.00 REF       |           |      |

| Foot Angle               | θ                | 0°             | 3.5°      | 7°   |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

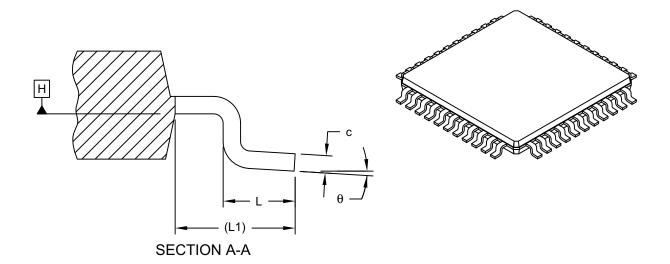

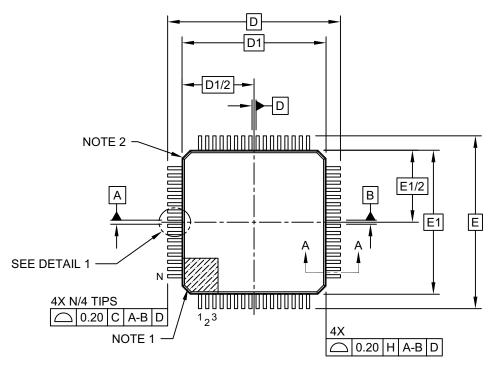

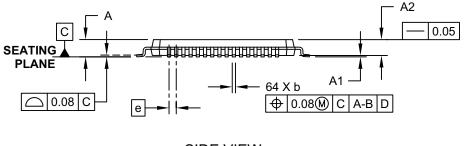

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

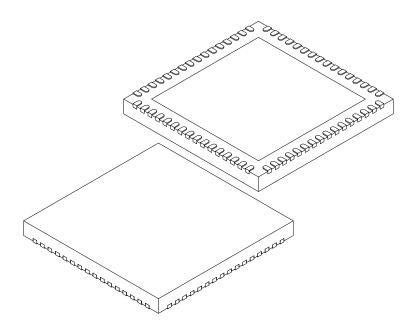

# 64-Lead Very Thin Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [VQFN] With 7.15 x 7.15 Exposed Pad [Also called QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  |      |          | S    |  |

|------------------------|--------|------|----------|------|--|

| Dimension              | Limits | MIN  | NOM      | MAX  |  |

| Number of Pins         | N      |      | 64       |      |  |

| Pitch                  | е      |      | 0.50 BSC |      |  |

| Overall Height         | Α      | 0.80 | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00 | 0.02     | 0.05 |  |

| Contact Thickness      | A3     |      | 0.20 REF |      |  |

| Overall Width          | E      |      | 9.00 BSC |      |  |

| Exposed Pad Width      | E2     | 7.05 | 7.15     | 7.25 |  |

| Overall Length         | D      |      | 9.00 BSC |      |  |

| Exposed Pad Length     | D2     | 7.05 | 7.15     | 7.25 |  |

| Contact Width          | b      | 0.18 | 0.25     | 0.30 |  |

| Contact Length         | L      | 0.30 | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20 | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149D [MR] Sheet 2 of 2

| CxFMSKSEL1 (CANx Filters 7-0 Mask                           |

|-------------------------------------------------------------|

| Selection 1)269                                             |

| CxFMSKSEL2 (CANx Filters 15-8 Mask                          |

| Selection 2)                                                |

| CxINTE (CANx Interrupt Enable)                              |

| CxINTF (CANx Interrupt Flag)                                |

| CxRXFnEID (CANx Acceptance Filter n                         |

| Extended Identifier)                                        |

| CxRXFnSID (CANx Acceptance Filter n<br>Standard Identifier) |

| CxRXFUL1 (CANx Receive Buffer Full 1)272                    |

| CxRXFUL2 (CANx Receive Buffer Full 2)                       |

| CxRXMnEID (CANx Acceptance Filter Mask n                    |

| Extended Identifier)                                        |

| CxRXMnSID (CANx Acceptance Filter Mask n                    |

| Standard Identifier)                                        |

| CxRXOVF1 (CANx Receive Buffer                               |

| Overflow 1)                                                 |

| CxRXOVF2 (CANx Receive Buffer                               |

| Overflow 2)                                                 |

| CxTRmnCON (CANx TX/RX Buffer mn Control) 274                |

| CxVEC (CANx Interrupt Code)257                              |

| DEVID (Device ID)                                           |

| DEVREV (Device Revision)                                    |

| DMALCA (DMA Last Channel Active Status) 120                 |

| DMAPPS (DMA Ping-Pong Status) 121                           |

| DMAPWC (DMA Peripheral Write                                |

| Collision Status)                                           |

| DMARQC (DMA Request Collision Status) 119                   |

| DMAxCNT (DMA Channel x Transfer Count)                      |

| DMAxCON (DMA Channel x Control)                             |

| DMAxPAD (DMA Channel x<br>Peripheral Address)               |

| DMAxREQ (DMA Channel x IRQ Select)                          |

| DMAXELQ (DMA Channel x RQ Select)                           |

| Start Address A, High) 114                                  |

| DMAxSTAL (DMA Channel x                                     |

| Start Address A, Low)                                       |

| DMAxSTBH (DMA Channel x                                     |

| Start Address B, High)                                      |

| DMAxSTBL (DMA Channel x                                     |

| Start Address B, Low) 115                                   |

| DMTCLR (Deadman Timer Clear) 183                            |

| DMTCNTH (Deadman Timer Count High)185                       |

| DMTCNTL (Deadman Timer Count Low) 185                       |

| DMTCON (Deadman Timer Control) 182                          |

| DMTHOLDREG (DMT Hold)188                                    |

| DMTPRECLR (Deadman Timer Preclear)                          |

| DMTPSCNTH (DMT Post Configure Count                         |

| Status High)                                                |

| DMTPSCNTL (DMT Post Configure Count                         |

| Status Low)                                                 |

| Status High)                                                |

| DMTPSINTVL (DMT Post Configure Interval                     |

| Status Low)                                                 |

| DMTSTAT (Deadman Timer Status)                              |

| DSADRH (DMA Most Recent RAM                                 |

| High Address)                                               |

| DSADRL (DMA Most Recent RAM                                 |

| Low Address)                                                |

| DTRx (PWMx Dead-Time)                                       |

| FCLCONx (PWMx Fault Current-Limit Control) 215              |

| I2CxCON1 (I2Cx Control 1)231                                |

| I2CxCON2 (I2Cx Control 2)                                   |

| , , , , , , , , , , , , , , , , , , ,                       |

| I2CxMSK (I2Cx Slave Mode Address Mask)                                               |      |

|--------------------------------------------------------------------------------------|------|

| I2CxSTAT (I2Cx Status)                                                               | 234  |

| ICxCON1 (Input Capture x Control 1)                                                  |      |

| ICxCON2 (Input Capture x Control 2)                                                  | 191  |

| INTCON1 (Interrupt Control 1)                                                        | 103  |

| INTCON2 (Interrupt Control 2)                                                        |      |

| INTCON3 (Interrupt Control 3)                                                        | 106  |

| INTCON4 (Interrupt Control 4)                                                        | 107  |

| INTTREG (Interrupt Control and Status)                                               | 108  |

| IOCONx (PWMx I/O Control)                                                            | 213  |

| LEBCONx (PWMx Leading-Edge Blanking                                                  |      |

| Control)                                                                             | 217  |

| LEBDLYx (PWMx Leading-Edge Blanking                                                  |      |

| Delay)                                                                               | 218  |

| MDC (PWMx Master Duty Cycle)                                                         |      |

| NVMADR (NVM Lower Address)                                                           |      |

| NVMADRU (NVM Upper Address)                                                          |      |

| NVMCON (NVM Control)                                                                 |      |

| NVMKEY (NVM Key)                                                                     |      |

| NVMSRCADRH (NVM Data Memory                                                          |      |

| Upper Address)                                                                       | . 90 |

| NVMSRCADRL (NVM Data Memory                                                          |      |

| Lower Address)                                                                       | . 90 |

| OCxCON1 (Output Compare x Control 1)                                                 |      |

| OCxCON2 (Output Compare x Control 2)                                                 |      |

| OSCCON (Oscillator Control)                                                          |      |

| OSCTUN (FRC Oscillator Tuning)                                                       |      |

| PDCx (PWMx Generator Duty Cycle)                                                     |      |

| PHASEx (PWMx Primary Phase-Shift)                                                    |      |

| PLLFBD (PLL Feedback Divisor)                                                        |      |

| PMD1 (Peripheral Module Disable Control 1)                                           |      |

| PMD2 (Peripheral Module Disable Control 2)                                           |      |

| PMD3 (Peripheral Module Disable Control 3)                                           |      |

| PMD4 (Peripheral Module Disable Control 4)                                           |      |

| PMD6 (Peripheral Module Disable Control 6)                                           |      |

| PMD7 (Peripheral Module Disable Control 7)                                           |      |

| PMD8 (Peripheral Module Disable Control 8)                                           |      |

| PTCON (PWMx Time Base Control)                                                       |      |

| PTCON2 (PWMx Primary Master Clock                                                    | -01  |

| Divider Select)                                                                      | 205  |

| PTPER (PWMx Primary Master Time Base                                                 | 200  |

| Period)                                                                              | 206  |

| PWMCONx (PWMx Control)                                                               |      |

| RCON (Reset Control)                                                                 |      |

| REFOCON (Reference Oscillator Control)                                               |      |

| RPINR0 (Peripheral Pin Select Input 0)                                               |      |

| RPINR1 (Peripheral Pin Select Input 1)                                               |      |

| RPINR11 (Peripheral Pin Select Input 1)                                              |      |

| RPINR12 (Peripheral Pin Select Input 12)                                             |      |

| RPINR18 (Peripheral Pin Select Input 12)                                             |      |

| RPINR19 (Peripheral Pin Select Input 19)                                             |      |

| RPINR22 (Peripheral Pin Select Input 19)                                             |      |

| RPINR23 (Peripheral Pin Select Input 23)                                             |      |

| RPINR26 (Peripheral Pin Select Input 26)                                             |      |

| RPINR3 (Peripheral Pin Select Input 20)                                              |      |

| RPINR37 (Peripheral Pin Select Input 37)                                             |      |

| RPINR38 (Peripheral Pin Select Input 38)                                             |      |

| RPINR39 (Peripheral Pin Select Input 39)                                             |      |

|                                                                                      |      |

| RPINR44 (Peripheral Pin Select Input 44)<br>RPINR45 (Peripheral Pin Select Input 45) |      |

|                                                                                      |      |

| RPINR7 (Peripheral Pin Select Input 7)                                               |      |

| RPINR8 (Peripheral Pin Select Input 8)                                               |      |

| RPOR0 (Peripheral Pin Select Output 0)                                               |      |

| DDOD1 (Deriphoral Dia Calant Outrant 4)                                              |      |