Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

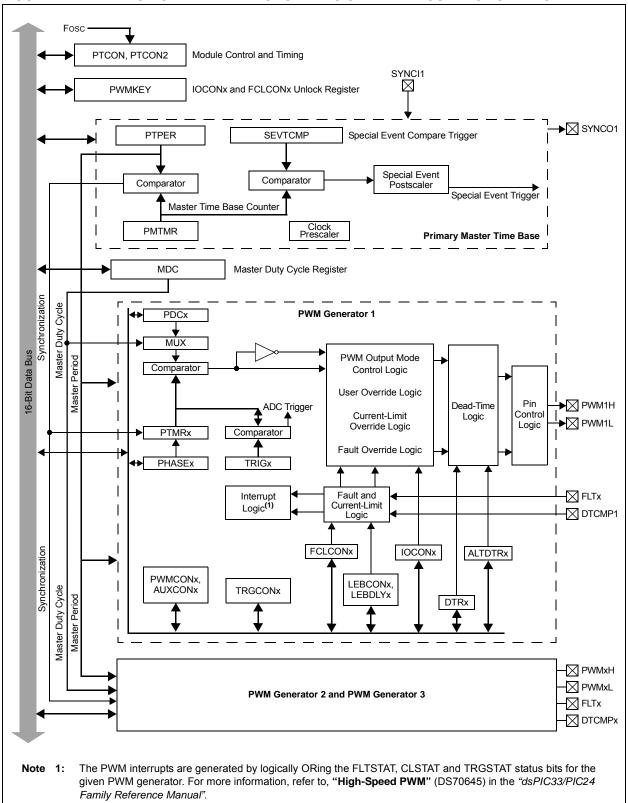

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm102-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Count Register                                    |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

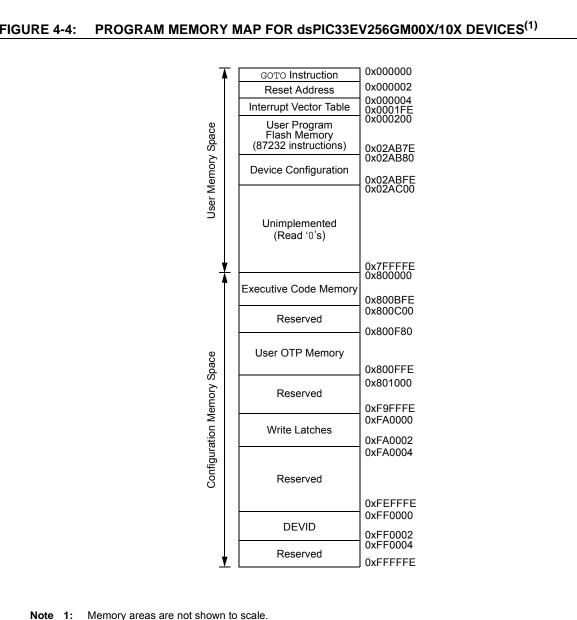

### FIGURE 4-4:

## TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|---------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------------|---------|--------|--------|--------|--------|--------|--------|---------------|

|             | 0400-<br>041E |        |        |        |        |        |        |        | See defin | ition when W | /IN = x |        |        |        |        |        |        |               |

| C1BUFPNT1   | 0420          | F3BP3  | F3BP2  | F3BP1  | F3BP0  | F2BP3  | F2BP2  | F2BP1  | F2BP0     | F1BP3        | F1BP2   | F1BP1  | F1BP0  | F0BP3  | F0BP2  | F0BP1  | F0BP0  | 0000          |

| C1BUFPNT2   | 0422          | F7BP3  | F7BP2  | F7BP1  | F7BP0  | F6BP3  | F6BP2  | F6BP1  | F6BP0     | F5BP3        | F5BP2   | F5BP1  | F5BP0  | F4BP3  | F4BP2  | F4BP1  | F4BP0  | 0000          |

| C1BUFPNT3   | 0424          | F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0    | F9BP3        | F9BP2   | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  | 0000          |

| C1BUFPNT4   | 0426          | F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0    | F13BP3       | F13BP2  | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 | 0000          |

| C1RXM0SID   | 0430          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | —      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM0EID   | 0432          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXM1SID   | 0434          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM1EID   | 0436          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | •      |        | xxxx          |

| C1RXM2SID   | 0438          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM2EID   | 043A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF0SID   | 0440          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF0EID   | 0442          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF1SID   | 0444          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF1EID   | 0446          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF2SID   | 0448          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | -      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF2EID   | 044A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF3SID   | 044C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF3EID   | 044E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF4SID   | 0450          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF4EID   | 0452          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF5SID   | 0454          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF5EID   | 0456          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF6SID   | 0458          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF6EID   | 045A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | _      |        | xxxx          |

| C1RXF7SID   | 045C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF7EID   | 045E          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | _      |        | xxxx          |

| C1RXF8SID   | 0460          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF8EID   | 0462          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF9SID   | 0464          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF9EID   | 0466          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF10SID  | 0468          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF10EID  | 046A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        |        |        | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|             |       |        | -0.0.     |        |        |        | (0.0.1 |       | 0     |           |       |       |       | .0 (001 |       | ·)    |       |               |

|-------------|-------|--------|-----------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|-------|---------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11SID  | 046C  | SID10  | SID9      | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | —     | EID17 | EID16 | xxxx          |

| C1RXF11EID  | 046E  |        | EID<15:0> |        |        |        |        |       |       |           |       |       | xxxx  |         |       |       |       |               |

| C1RXF12SID  | 0470  | SID10  | SID9      | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF12EID  | 0472  |        | EID<15:0> |        |        |        |        |       |       |           |       | xxxx  |       |         |       |       |       |               |

| C1RXF13SID  | 0474  | SID10  | SID9      | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF13EID  | 0476  |        |           |        |        |        |        |       | E     | EID<15:0> |       |       |       |         |       |       |       | xxxx          |

| C1RXF14SID  | 0478  | SID10  | SID9      | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF14EID  | 047A  |        | EID<15:0> |        |        |        |        |       |       |           |       | xxxx  |       |         |       |       |       |               |

| C1RXF15SID  | 047C  | SID10  | SID9      | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF15EID  | 047E  |        | EID<15:0> |        |        |        |        |       |       |           | xxxx  |       |       |         |       |       |       |               |

|             |       |        |           |        |        |        |        |       |       |           |       |       |       |         |       |       |       |               |

#### TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: SENT1 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                           | Bit 14                                                          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8      | Bit 7         | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|------------------------------------------------------------------|-----------------------------------------------------------------|---------|--------|--------|--------|-----------------------|------------|---------------|-----------|-------|-------|--------|---------|---------|----------|---------------|

| SENT1CON1   | 0500  | SNTEN                                                            | —                                                               | SNTSIDL | _      | RCVEN  | TXM    | TXPOL                 | CRCEN      | PPP           | SPCEN     | _     | PS    | -      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT1CON2   | 0504  |                                                                  | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode) |         |        |        |        |                       |            |               |           |       |       | FFFF   |         |         |          |               |

| SENT1CON3   | 0508  | FRAMETIME<15:0> (Transmit modes) or SYNCMIN<15:0> (Receive mode) |                                                                 |         |        |        |        |                       |            |               |           | FFFF  |       |        |         |         |          |               |

| SENT1STAT   | 050C  | _                                                                | _                                                               | _       | _      | _      | _      | _                     | _          | PAUSE         | NIB2      | NIB1  | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT1SYNC   | 0510  |                                                                  |                                                                 |         |        |        | Synchr | onization -           | Time Perio | d Register    | (Transmit | mode) |       |        |         |         |          | 0000          |

| SENT1DATL   | 0514  |                                                                  | DATA4<3:0> DATA5<3:0>                                           |         |        |        |        |                       |            | DATA6<3:0> CR |           |       |       | CRO    | C<3:0>  |         | 0000     |               |

| SENT1DATH   | 0516  | STAT<3:0> DATA1<3:0>                                             |                                                                 |         |        |        |        | DATA2<3:0> DATA3<3:0> |            |               |           |       |       | 0000   |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: SENT2 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                           | Bit 14                                                          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|------------------------------------------------------------------|-----------------------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|---------|---------|----------|---------------|

| SENT2CON1   | 0520  | SNTEN                                                            | —                                                               | SNTSIDL |        | RCVEN  | TXM    | TXPOL | CRCEN | PPP   | SPCEN | -     | PS    | —      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT2CON2   | 0524  |                                                                  | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode) |         |        |        |        |       |       |       |       |       | FFFF  |        |         |         |          |               |

| SENT2CON3   | 0528  | FRAMETIME<15:0> (Transmit modes) or SYNCMIN<15:0> (Receive mode) |                                                                 |         |        |        |        |       |       |       |       | FFFF  |       |        |         |         |          |               |

| SENT2STAT   | 052C  | -                                                                | _                                                               | _       |        | —      |        | —     | _     | PAUSE | NIB2  | NIB1  | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT2SYNC   | 0530  |                                                                  | Synchronization Time Period Register (Transmit mode)            |         |        |        |        |       |       | 0000  |       |       |       |        |         |         |          |               |

| SENT2DATL   | 0534  | DATA4<3:0> DATA5<3:0> DATA6<3:0> CRC<3:0>                        |                                                                 |         |        |        |        |       |       | 0000  |       |       |       |        |         |         |          |               |

| SENT2DATH   | 0536  | STAT<3:0> DATA1<3:0> DATA2<3:0> DATA3<3:0>                       |                                                                 |         |        |        |        | 0000  |       |       |       |       |       |        |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70005144E-page 49

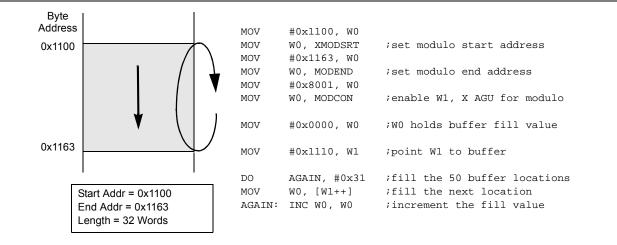

## 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the SFP and SSP, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit (MODCON<15>) is set

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

Figure 4-15 shows an example of Modulo Addressing operation.

Note: Y Data Space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

#### FIGURE 4-15: MODULO ADDRESSING OPERATION EXAMPLE

| R/W-0          | R/W-0                                     | U-0                                  | U-0             | R/W-0                        | U-0              | R/W-0            | R/W-0          |

|----------------|-------------------------------------------|--------------------------------------|-----------------|------------------------------|------------------|------------------|----------------|

| TRAPF          | R IOPUWR                                  |                                      | —               | VREGSF                       |                  | CM               | VREGS          |

| bit 15         |                                           |                                      |                 |                              |                  |                  | bit 8          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| R/W-0          | R/W-0                                     | R/W-0                                | R/W-0           | R/W-0                        | R/W-0            | R/W-1            | R/W-1          |

| EXTR           | SWR                                       | SWDTEN <sup>(2)</sup>                | WDTO            | SLEEP                        | IDLE             | BOR              | POR            |

| bit 7          |                                           |                                      |                 |                              |                  |                  | bit (          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Legend:        |                                           |                                      |                 |                              |                  |                  |                |

| R = Reada      |                                           | W = Writable                         | oit             | •                            | nented bit, read | d as '0'         |                |

| -n = Value     | at POR                                    | '1' = Bit is set                     |                 | '0' = Bit is cle             | ared             | x = Bit is unk   | nown           |

| 6:4 <i>4 C</i> |                                           | Deast Flag bit                       |                 |                              |                  |                  |                |

| bit 15         |                                           | D Reset Flag bit<br>onflict Reset ha | e occurrod      |                              |                  |                  |                |

|                |                                           | onflict Reset ha                     |                 | ed                           |                  |                  |                |

| bit 14         | •                                         | egal Opcode or                       |                 |                              | ess Reset Flag   | a bit            |                |

|                |                                           | al Opcode detec                      |                 | •                            | -                |                  | ter used as ar |

|                |                                           | Pointer caused                       |                 | · · · · · · · · · · · ·      |                  |                  |                |

|                |                                           | I Opcode Rese                        |                 | zed W Register               | Reset has not    | occurred         |                |

| bit 13-12      | -                                         | nted: Read as '                      |                 |                              |                  |                  |                |

| bit 11         |                                           | ash Voltage Reg                      |                 |                              | o bit            |                  |                |

|                |                                           | Itage regulator i                    |                 | •                            | ing Sleep mode   | 2                |                |

| bit 10         |                                           | nted: Read as '                      | -               |                              | ing cleep mout   |                  |                |

| bit 9          | -                                         | ration Mismatch                      |                 |                              |                  |                  |                |

|                | •                                         | uration Mismatc                      | •               | occurred.                    |                  |                  |                |

|                |                                           | uration Mismato                      |                 |                              |                  |                  |                |

| bit 8          | VREGS: Volt                               | age Regulator S                      | Standby Durii   | ng Sleep bit                 |                  |                  |                |

|                |                                           | regulator is activ                   |                 |                              |                  |                  |                |

|                | •                                         | regulator goes i                     |                 | mode during Sle              | еер              |                  |                |

| bit 7          |                                           | nal Reset (MCL                       | ,               |                              |                  |                  |                |

|                |                                           | Clear (pin) Res<br>Clear (pin) Res   |                 |                              |                  |                  |                |

| bit 6          |                                           | are RESET (Instr                     |                 |                              |                  |                  |                |

|                |                                           | instruction has                      |                 |                              |                  |                  |                |

|                | 0 = A reset                               | instruction has                      | not been exe    | ecuted                       |                  |                  |                |

| bit 5          | SWDTEN: So                                | oftware Enable/                      | Disable of W    | DT bit <b><sup>(2)</sup></b> |                  |                  |                |

|                | 1 = WDT is e                              |                                      |                 |                              |                  |                  |                |

|                | 0 = WDT is d                              |                                      |                 |                              |                  |                  |                |

| bit 4          |                                           | hdog Timer Tim                       | -               | it                           |                  |                  |                |

|                |                                           | e-out has occur<br>e-out has not oc  |                 |                              |                  |                  |                |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Note 1:        | All of the Reset sta<br>cause a device Re |                                      | set or cleare   | a in software. S             | etting one of th | ese bits in soft | ware does not  |

| 2:             | If the FWDTEN<1                           |                                      | n hits are '1 1 | ' (unprogramm                | ed) the WDT is   | always enable    | od rogardlaar  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | -   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0    | U-0 | U-0 | U-0 | R-0 | R-0 | R-0 | R-0   |

## REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| U-0   | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                  |

|----------|---------------------------------------------------------------------------------------------|

| bit 3    | PPST3: Channel 3 Ping-Pong Mode Status Flag bit                                             |

|          | <ul><li>1 = DMA3STB register is selected</li><li>0 = DMA3STA register is selected</li></ul> |

| bit 2    | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                             |

|          | 1 = DMA2STB register is selected                                                            |

|          | 0 = DMA2STA register is selected                                                            |

| bit 1    | <b>PPST1:</b> Channel 1 Ping-Pong Mode Status Flag bit                                      |

|          | 1 = DMA1STB register is selected                                                            |

|          | 0 = DMA1STA register is selected                                                            |

| bit 0    | <b>PPST0:</b> Channel 0 Ping-Pong mode Status Flag bit                                      |

|          | 1 = DMA0STB register is selected                                                            |

|          | 0 = DMA0STA register is selected                                                            |

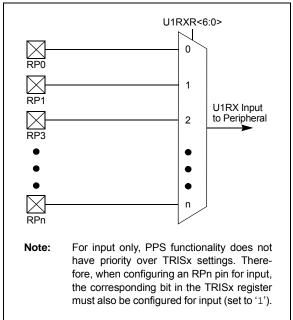

For example, Figure 11-2 shows the remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

## 11.5.4.1 Virtual Connections

dsPIC33EVXXXGM00X/10X family devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module").

These devices provide six virtual output pins (RPV0-RPV5) that correspond to the outputs of six peripheral pin output remapper blocks (RP176-RP181). The six virtual remapper outputs (RP176-RP181) are not connected to actual pins. The six virtual pins may be read by any of the input remappers as inputs, RP176-RP181. These virtual pins can be used to connect the internal peripherals, whose signals are of significant use to the other peripherals, but these output signals are not present on the device pin.

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<7:0> bits of the RPINR12 register to the value of 'b0000001', the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

## 15.1 Input Capture Control Registers

## REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER     | 15-1: ICxCO                                                                                                                        | N1: INPUT C                                                                                                                        | CAPTURE x CO       | ONTROL REG           | ISTER 1          |                 |              |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|------------------|-----------------|--------------|--|--|--|

| U-0          | U-0                                                                                                                                | R/W-0                                                                                                                              | R/W-0              | R/W-0                | R/W-0            | U-0             | U-0          |  |  |  |

| _            |                                                                                                                                    | ICSIDL                                                                                                                             | ICTSEL2            | ICTSEL1              | ICTSEL0          | —               | _            |  |  |  |

| bit 15       |                                                                                                                                    | •                                                                                                                                  |                    |                      |                  |                 | bit          |  |  |  |

| U-0          | R/W-0                                                                                                                              | R/W-0                                                                                                                              | R-0, HC, HS        | R-0, HC, HS          | R/W-0            | R/W-0           | R/W-0        |  |  |  |

| _            | ICI1                                                                                                                               | ICI0                                                                                                                               | ICOV               | ICBNE                | ICM2             | ICM1            | ICM0         |  |  |  |

| bit 7        |                                                                                                                                    |                                                                                                                                    |                    |                      |                  |                 | bit          |  |  |  |

| Legend:      |                                                                                                                                    | HC = Hardwa                                                                                                                        | re Clearable bit   | HS = Hardwar         | re Settable bit  |                 |              |  |  |  |

| R = Readab   | le bit                                                                                                                             | W = Writable                                                                                                                       | bit                | U = Unimplem         | nented bit, read | <b>l as</b> '0' |              |  |  |  |

| -n = Value a | t POR                                                                                                                              | '1' = Bit is set                                                                                                                   |                    | '0' = Bit is clea    | ared             | x = Bit is un   | known        |  |  |  |

| bit 15-14    | Unimplemen                                                                                                                         | ted: Read as '                                                                                                                     | 0'                 |                      |                  |                 |              |  |  |  |

| bit 13       | -                                                                                                                                  |                                                                                                                                    | p in Idle Mode C   | control bit          |                  |                 |              |  |  |  |

|              |                                                                                                                                    | -                                                                                                                                  | t in CPU Idle mod  |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | tinue to operate   |                      | de               |                 |              |  |  |  |

| bit 12-10    |                                                                                                                                    |                                                                                                                                    | e x Timer Select   |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | is the clock sour  | ce of the ICx        |                  |                 |              |  |  |  |

|              |                                                                                                                                    | 110 = Reserved                                                                                                                     |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | 101 = Reserved                                                                                                                     |                    |                      |                  |                 |              |  |  |  |

|              | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx |                                                                                                                                    |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | 010 = T4CLK is the clock source of the ICx                                                                                         |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | ource of the ICx   |                      |                  |                 |              |  |  |  |

| bit 9-7      |                                                                                                                                    | ted: Read as '                                                                                                                     |                    |                      |                  |                 |              |  |  |  |

| bit 6-5      | ICI<1:0>: Nur                                                                                                                      | mber of Captur                                                                                                                     | es per Interrupt S | Select bits (this fi | eld is not used  | if ICM<2:0> =   | 001 or 111   |  |  |  |

|              | 11 = Interrupt                                                                                                                     | 11 = Interrupt on every fourth capture event                                                                                       |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | 10 = Interrupt on every third capture event                                                                                        |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | 01 = Interrupt on every second capture event                                                                                       |                    |                      |                  |                 |              |  |  |  |

|              | -                                                                                                                                  | t on every cap                                                                                                                     |                    |                      |                  |                 |              |  |  |  |

| bit 4        | -                                                                                                                                  | -                                                                                                                                  | flow Status Flag   |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | overflow has occu  |                      |                  |                 |              |  |  |  |

| bit 3        |                                                                                                                                    | -                                                                                                                                  | fer Not Empty St   |                      | nlv)             |                 |              |  |  |  |

|              | -                                                                                                                                  | -                                                                                                                                  | s not empty, at le | -                    | • •              | an be read      |              |  |  |  |

|              |                                                                                                                                    | pture x buffer i                                                                                                                   |                    |                      |                  |                 |              |  |  |  |

| bit 2-0      | ICM<2:0>: In                                                                                                                       | put Capture x                                                                                                                      | Mode Select bits   |                      |                  |                 |              |  |  |  |

|              | 111 = Input Capture x functions as an interrupt pin only in CPU Sleep and Idle modes (rising edge                                  |                                                                                                                                    |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | detect only, all other control bits are not applicable)                                                                            |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | <ul> <li>110 = Unused (module is disabled)</li> <li>101 = Capture mode, every 16th rising edge (Prescaler Capture mode)</li> </ul> |                    |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | / 16th rising edge |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | / rising edge (Sir |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    |                                                                                                                                    | / falling edge (Si |                      |                  |                 |              |  |  |  |

|              |                                                                                                                                    | re mode, every                                                                                                                     | edge, rising and   |                      |                  | CI<1:0>) is not | t used in th |  |  |  |

|              | ,                                                                                                                                  |                                                                                                                                    | ule is turned off  |                      |                  |                 |              |  |  |  |

000 = Input Capture x module is turned off

| R/W-0           | R/W-0                                  | R/W-0                          | R/W-0                         | R/W-0                                           | R/W-0              | U-0             | U-0            |

|-----------------|----------------------------------------|--------------------------------|-------------------------------|-------------------------------------------------|--------------------|-----------------|----------------|

| PHR             | PHF                                    | PLR                            | PLF                           | FLTLEBEN                                        | CLLEBEN            |                 | _              |

| bit 15          |                                        | L                              |                               | •                                               |                    |                 | bit 8          |

|                 |                                        |                                |                               |                                                 |                    |                 |                |

| U-0             | U-0                                    | R/W-0                          | R/W-0                         | R/W-0                                           | R/W-0              | R/W-0           | R/W-0          |

| —               |                                        | BCH <sup>(1)</sup>             | BCL <sup>(1)</sup>            | BPHH                                            | BPHL               | BPLH            | BPLL           |

| bit 7           |                                        |                                |                               |                                                 |                    |                 | bit (          |

| Legend:         |                                        |                                |                               |                                                 |                    |                 |                |

| R = Readable b  | nit                                    | W = Writable                   | hit                           | II = I Inimpler                                 | mented bit, read   | as '0'          |                |

| -n = Value at P |                                        | '1' = Bit is set               |                               | '0' = Bit is cle                                |                    | x = Bit is unk  | nown           |

|                 |                                        |                                |                               |                                                 |                    | X Bitle dill    |                |

| bit 15          | PHR: PWMxH                             | Rising Edge                    | Trigger Enabl                 | e bit                                           |                    |                 |                |

|                 |                                        |                                |                               |                                                 | Blanking count     | ter             |                |

|                 | 0 = Leading-E                          | Edge Blanking                  | gnores the ri                 | sing edge of PV                                 | VMxH               |                 |                |

| bit 14          |                                        | I Falling Edge                 |                               |                                                 |                    |                 |                |

|                 | 0                                      | 0                              | 00                            | e Leading-Edge<br>alling edge of P <sup>1</sup> | e Blanking coun    | ter             |                |

| bit 13          | -                                      | Rising Edge T                  | -                             |                                                 |                    |                 |                |

| DIL 15          |                                        | • •                            |                               |                                                 | Blanking count     | er              |                |

|                 |                                        |                                |                               | sing edge of PV                                 |                    |                 |                |

| bit 12          | PLF: PWMxL                             | Falling Edge 1                 | rigger Enable                 | e bit                                           |                    |                 |                |

|                 |                                        |                                |                               |                                                 | Blanking count     | ter             |                |

|                 | •                                      | • •                            | •                             | alling edge of P                                |                    |                 |                |

| bit 11          |                                        |                                |                               | anking Enable I                                 |                    |                 |                |

|                 |                                        |                                |                               | he selected Fa<br>to the selected               |                    |                 |                |

| bit 10          | •                                      | • •                            |                               | Edge Blanking E                                 | •                  |                 |                |

|                 |                                        |                                | -                             | he selected cur                                 |                    |                 |                |

|                 | 0 = Leading-E                          | Edge Blanking                  | s not applied                 | to the selected                                 | l current-limit in | put             |                |

| bit 9-6         | -                                      | ted: Read as '                 |                               |                                                 |                    |                 |                |

| bit 5           |                                        |                                |                               | al High Enable                                  |                    |                 |                |

|                 |                                        |                                |                               | Fault input sigr<br>ng signal is hig            | nals) when seled   | cted blanking s | signal is high |

| bit 4           |                                        | •                              |                               | al Low Enable b                                 |                    |                 |                |

|                 |                                        | •                              | •••                           |                                                 | nals) when seled   | cted blanking s | signal is low  |

|                 |                                        |                                |                               | ng signal is low                                |                    | 0               | 0              |

| bit 3           |                                        | ing in PWMxH                   | -                             |                                                 |                    |                 |                |

|                 |                                        |                                |                               |                                                 | nals) when the F   | PWMxH output    | is high        |

| h:# 0           |                                        | ng when the P                  | -                             | -                                               |                    |                 |                |

| bit 2           |                                        | ng in PWMxH                    |                               |                                                 | nals) when the F   |                 | ic low         |

|                 |                                        | ng when the P                  |                               |                                                 |                    | www.kirioutput  | . 15 10 W      |

| bit 1           |                                        | ng in PWMxL I                  |                               |                                                 |                    |                 |                |

|                 |                                        | -                              | -                             |                                                 | nals) when the F   | PWMxL output    | is hiah        |

|                 |                                        |                                |                               |                                                 |                    |                 |                |

|                 | 0 = No blankii                         | ng when the P                  | WMxL output                   | is high                                         |                    |                 | is ingli       |

| bit 0           | BPLL: Blanki                           | ng when the P<br>ng in PWMxL L | ow Enable b                   | it                                              |                    |                 | -              |

| bit 0           | <b>BPLL:</b> Blankii<br>1 = State blan | ng when the P<br>ng in PWMxL L | ow Enable b<br>t-limit and/or | it<br>Fault input sigr                          | nals) when the F   | PWMxL output    | -              |

Note 1: The blanking signal is selected through the BLANKSEL<3:0> bits in the AUXCONx register.

## 21.2 UART Control Registers

## REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                                                                                                  | DE: UARTx N                                                       |                                                             | TER                             |                                          |                  |                           |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|--|--|

| R/W-0                 | U-0                                                                                                                                         | R/W-0                                                             | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |  |  |

| UARTEN <sup>(1)</sup> |                                                                                                                                             | USIDL                                                             | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |  |  |

| bit 15                |                                                                                                                                             |                                                                   |                                                             | ·                               |                                          |                  | bit 8                     |  |  |

| R/W-0, HC             | R/W-0                                                                                                                                       | R/W-0, HC                                                         | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |  |  |

| WAKE                  | LPBACK                                                                                                                                      | ABAUD                                                             | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |  |  |

| bit 7                 |                                                                                                                                             | 101100                                                            | Orodity                                                     | ыкоп                            | TDOLLI                                   | TDOLLO           | bit (                     |  |  |

|                       |                                                                                                                                             |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |

| Legend:               |                                                                                                                                             | HC = Hardwar                                                      | e Clearable bit                                             | t                               |                                          |                  |                           |  |  |

| R = Readable          | e bit                                                                                                                                       | W = Writable I                                                    | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |  |  |

| -n = Value at         | POR                                                                                                                                         | '1' = Bit is set                                                  |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |  |  |

| bit 15                | 1 = UARTx is                                                                                                                                | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U          | ARTx pins are                                               |                                 |                                          |                  |                           |  |  |

|                       | is minima                                                                                                                                   |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |

| bit 14                | •                                                                                                                                           | ted: Read as '0                                                   |                                                             |                                 |                                          |                  |                           |  |  |

| bit 13                |                                                                                                                                             | Tx Stop in Idle N                                                 |                                                             |                                 |                                          |                  |                           |  |  |

|                       | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                   |                                                             |                                 |                                          |                  |                           |  |  |

| bit 12                | IREN: IrDA <sup>®</sup>                                                                                                                     | Encoder and De                                                    | ecoder Enable                                               | bit <sup>(2)</sup>              |                                          |                  |                           |  |  |

|                       |                                                                                                                                             | oder and decod                                                    |                                                             |                                 |                                          |                  |                           |  |  |

| bit 11                |                                                                                                                                             | le Selection for                                                  |                                                             |                                 |                                          |                  |                           |  |  |

|                       | 1 = UxRTS p                                                                                                                                 | oin is in Simplex<br>oin is in Flow Co                            | mode                                                        |                                 |                                          |                  |                           |  |  |

| bit 10                |                                                                                                                                             | ited: Read as '0                                                  |                                                             |                                 |                                          |                  |                           |  |  |

| bit 9-8               | -                                                                                                                                           | IARTx Pin Enab                                                    |                                                             |                                 |                                          |                  |                           |  |  |

|                       | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                                                                                                | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |  |

| bit 7                 | WAKE: UAR                                                                                                                                   | Tx Wake-up on                                                     | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |  |  |

|                       | in hardwa                                                                                                                                   | ontinues to sam<br>are on the follow<br>is not enabled            |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |  |  |

| bit 6                 | -                                                                                                                                           | RTx Loopback                                                      | Mode Select b                                               | it                              |                                          |                  |                           |  |  |

|                       |                                                                                                                                             | k mode is enab                                                    |                                                             |                                 |                                          |                  |                           |  |  |

|                       |                                                                                                                                             | k mode is disab                                                   |                                                             |                                 |                                          |                  |                           |  |  |