#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

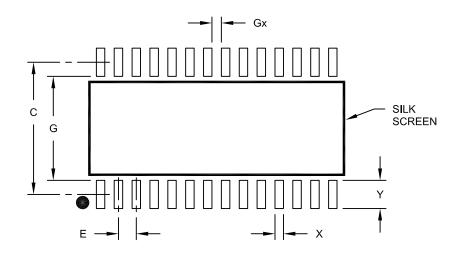

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm102-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EVXXXGM00X/10X FAMILY

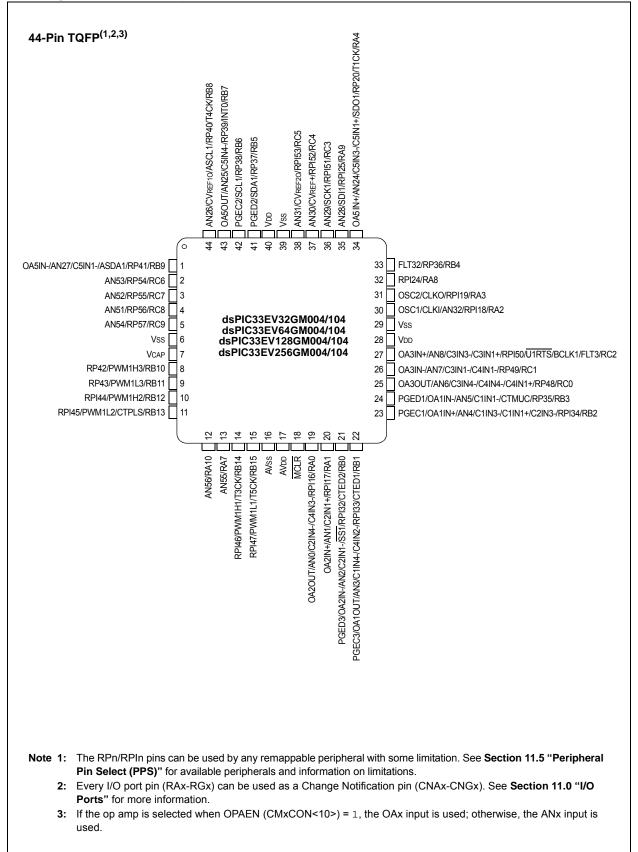

### **Pin Diagrams (Continued)**

NOTES:

|             | ••    |           | •      |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

|-------------|-------|-----------|--------|--------|--------|--------|--------|------------|-------------|---------------|---------------|-------------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15    | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7         | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |           |        |        |        |        |        |            | Tim         | ner1 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR1         | 0102  |           |        |        |        |        |        |            | Peri        | od Register   | 1             |             |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON       | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |           |        |        |        |        |        |            | Tim         | ner2 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108  |           |        |        |        |        | Time   | er3 Holdin | ig Register | · (For 32-bit | timer operat  | tions only) |        |       |       |       |       | 0000          |

| TMR3        | 010A  |           |        |        |        |        |        |            | Tim         | ner3 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR2         | 010C  |           |        |        |        |        |        |            | Peri        | od Register   | 2             |             |        |       |       |       |       | FFFF          |

| PR3         | 010E  |           |        |        |        |        |        |            | Peri        | od Register   | 3             |             |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON       | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON       | _      | TSIDL  | _      | _      | _      | _          | —           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |           |        |        |        |        |        |            | Tim         | ner4 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116  |           |        |        |        |        | Т      | imer5 Hol  | ding Regis  | ster (For 32- | bit operation | ns only)    |        |       |       |       |       | 0000          |

| TMR5        | 0118  |           |        |        |        |        |        |            | Tim         | ner5 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR4         | 011A  |           |        |        |        |        |        |            | Peri        | od Register   | 4             |             |        |       |       |       |       | FFFF          |

| PR5         | 011C  |           |        |        |        |        |        |            | Peri        | od Register   | 5             |             |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON       | _      | TSIDL  | —      | —      | —      | —          | —           | —             | TGATE         | TCKPS1      | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON       | _      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| Lonondi     |       | nlamantad | 1 1-   |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

#### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

#### REGISTER 5-5: NVMSRCADRH: NVM DATA MEMORY UPPER ADDRESS REGISTER

| U-0     | U-0   | U-0   | U-0      | U-0       | U-0   | U-0   | U-0   |

|---------|-------|-------|----------|-----------|-------|-------|-------|

| —       | _     | _     | _        | —         | _     | —     | —     |

| bit 15  |       |       |          |           |       |       | bit 8 |

|         |       |       |          |           |       |       |       |

| R/W-x   | R/W-x | R/W-x | R/W-x    | R/W-x     | R/W-x | R/W-x | R/W-x |

|         |       |       | NVMSRCAD | )R<23:16> |       |       |       |

| bit 7   |       |       |          |           |       |       | bit 0 |

|         |       |       |          |           |       |       |       |

| Legend: |       |       |          |           |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Data Memory Upper Address bits

#### REGISTER 5-6: NVMSRCADRL: NVM DATA MEMORY LOWER ADDRESS REGISTER

| R/W-x           | R/W-x | R/W-x            | R/W-x    | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|----------|------------------|-----------------|-----------------|-------|

|                 |       |                  | NVMSRC   | CADR<15:8>       |                 |                 |       |

| bit 15          |       |                  |          |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x    | R/W-x            | R/W-x           | R/W-x           | r-0   |

|                 |       | NV               | MSRCADR< | 7:1>             |                 |                 | —     |

| bit 7           |       |                  |          |                  |                 |                 | bit C |

| Legend:         |       | r = Reserved     | bit      |                  |                 |                 |       |

| R = Readable b  | bit   | W = Writable     | bit      | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-1 NVMSRCADRL<15:1>: Data Memory Lower Address bits

bit 0 Reserved: Maintain as '0'

| U-0          | R-0                                     | R-0                                              | R-0              | U-0              | R/W-y                        | R/W-y                | R/W-y                |

|--------------|-----------------------------------------|--------------------------------------------------|------------------|------------------|------------------------------|----------------------|----------------------|

| _            | COSC2                                   | COSC1                                            | COSC0            | —                | NOSC2 <sup>(2)</sup>         | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15       |                                         |                                                  |                  |                  |                              |                      | bit 8                |

|              |                                         |                                                  |                  |                  |                              |                      |                      |

| R/W-0        | R/W-0                                   | R-0                                              | U-0              | R/C-0            | U-0                          | U-0                  | R/W-0                |

| CLKLOCK      | IOLOCK                                  | LOCK                                             | —                | CF               |                              |                      | OSWEN                |

| bit 7        |                                         |                                                  |                  |                  |                              |                      | bit (                |

| Legend:      |                                         | C = Clearable                                    | hit              | v = Value set    | from Configura               | tion hits on PO      | R                    |

| R = Readab   | le hit                                  | W = Writable                                     |                  | ,                | mented bit, read             |                      |                      |

| -n = Value a |                                         | '1' = Bit is set                                 |                  | '0' = Bit is cle |                              | x = Bit is unkr      | าดพุท                |

|              |                                         |                                                  |                  |                  |                              |                      | IOWIT                |

| bit 15       | Unimplemen                              | ted: Read as '                                   | 0'               |                  |                              |                      |                      |

| bit 14-12    | -                                       | Current Oscilla                                  |                  | bits (read-only  | ()                           |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | · · ·            | ,                            |                      |                      |

|              | 110 <b>= Fast R</b>                     | C Oscillator (F                                  | RC) with Divid   |                  |                              |                      |                      |

|              |                                         | ower RC Oscill                                   |                  |                  |                              |                      |                      |

|              |                                         | p FRC Oscillator<br>y Oscillator (X <sup>-</sup> |                  | ыры              |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  | II PLL           |                              |                      |                      |

|              |                                         | C Oscillator (F                                  | ,                | y N and PLL      |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | ,                |                              |                      |                      |

| bit 11       | -                                       | ted: Read as '                                   |                  |                  |                              |                      |                      |

| bit 10-8     | NOSC<2:0>:                              | New Oscillator                                   | r Selection bits | <sub>S</sub> (2) |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | le-by-16         |                              |                      |                      |

|              | 101 = Low-P                             | ower RC Oscill<br><sub>/ed</sub> (5)             |                  |                  |                              |                      |                      |

|              |                                         | y Oscillator (X <sup>-</sup>                     | Г, HS, EC) wit   | h PLL            |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | y N and PLL      |                              |                      |                      |

| hit 7        |                                         | C Oscillator (F                                  | ,                |                  |                              |                      |                      |

| bit 7        |                                         | Clock Lock Ena                                   |                  | onfigurations a  | re locked; if FCk            | (SM0 = 0  then)      | clock and Pl         |

|              |                                         | ations may be r                                  |                  |                  |                              |                      |                      |

|              |                                         |                                                  |                  | ked, configurat  | ions may be mo               | odified              |                      |

| bit 6        | IOLOCK: I/O                             | Lock Enable b                                    | oit              |                  |                              |                      |                      |

|              | 1 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

|              | 0 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

| bit 5        |                                         | ock Status bit                                   |                  |                  |                              |                      |                      |

|              |                                         | that PLL is in that PLL is ou                    |                  |                  | satisfied<br>progress or PLL | is disabled          |                      |

|              |                                         |                                                  |                  |                  | -                            |                      |                      |

|              | Vrites to this regis<br>dsPIC33/PIC24 F |                                                  |                  |                  |                              |                      | ils.                 |

|              | irect clock switch                      | -                                                | -                |                  | -                            | -                    |                      |

| te           | ed. This applies to                     | o clock switche                                  | s in either dire | ection. In these | instances, the               |                      |                      |

|              | RC mode as a tra                        |                                                  |                  |                  | L modes.                     |                      |                      |

|              | his register reset                      | -                                                |                  |                  |                              |                      |                      |

| <b>4</b> : C | OSC<2:0> bits w                         | viii be set to '0k                               | DIOU when H      | to fails.        |                              |                      |                      |

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

5: User cannot write '0b100' to NOSC<2:0>. COSC<2:0> will be set to '0b100' (BFRC) when the FRC fails.

| Periphera<br>Select II<br>Register | nput | Input/<br>Output | Pin Assignment                 |

|------------------------------------|------|------------------|--------------------------------|

| 00                                 | 000  | I                | Vss                            |

| 00                                 | 001  | I                | CMP1 <sup>(1)</sup>            |

| 0 0                                | 010  | Ι                | CMP2 <sup>(1)</sup>            |

| 000 00                             | 011  | Ι                | CMP3 <sup>(1)</sup>            |

| 000 01                             | 100  | Ι                | CMP4 <sup>(1)</sup>            |

| 000 01                             | 101  | —                | —                              |

| 000 11                             | 100  | Ι                | CMP5 <sup>(1)</sup>            |

| 000 11                             | 101  | _                | _                              |

| 000 11                             | 110  | _                |                                |

| 000 11                             | 111  | _                | _                              |

| 001 00                             | 000  | Ι                | RPI16                          |

| 001 00                             | 001  | I                | RPI17                          |

| 001 00                             | 010  | I                | RPI18                          |

| 001 00                             | 011  | Ι                | RPI19                          |

| 001 01                             | 100  | I/O              | RP20                           |

| 001 01                             | 101  | _                |                                |

| 001 01                             | 110  | _                | _                              |

| 001 01                             | 111  | _                | _                              |

| 001 10                             | 000  | I                | RPI24                          |

| 001 10                             | 001  | I                | RPI25                          |

| 001 10                             | 010  | _                | —                              |

| 001 10                             | 011  | I                | RPI27                          |

| 001 11                             | 100  | Ι                | RPI28                          |

| 001 11                             | 101  |                  | _                              |

| 001 11                             | 110  |                  | _                              |

| 001 11                             | 111  |                  | _                              |

| 010 00                             |      | Ι                | RPI32                          |

| 010 00                             |      | Ι                | RPI33                          |

| 010 00                             |      | I                | RPI34                          |

| 010 00                             |      | I/O              | RP35                           |

| 010 01                             |      | I/O              | RP36                           |

| 010 01                             |      | I/O              | RP37                           |

| 010 01                             |      | I/O              | RP38                           |

| 010 01                             |      | 1/O              | RP39                           |

| 010 10                             |      | I/O              |                                |

| 010 10                             |      | 1/U              | RPI44                          |

| 010 11                             |      | -                | RPI45                          |

| 010 11                             |      |                  | RPI46                          |

| 010 11                             |      | 1                | RPI47                          |

|                                    |      | I/O              |                                |

| 011 00                             |      | -                | RP48<br>the PPS Input register |

## TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate the PPS Input register values that are unimplemented.

Note 1: These are virtual pins. See Section 11.5.4.1 "Virtual Connections" for more information on selecting this pin assignment.

| REGISTER 11-11: | <b>RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23</b> |

|-----------------|---------------------------------------------------------|

|-----------------|---------------------------------------------------------|

| U-0          | U-0                                                                                                                                                      | U-0             | U-0   | U-0                                     | U-0             | U-0             | U-0   |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----------------------------------------|-----------------|-----------------|-------|--|

| _            | —                                                                                                                                                        | —               | _     | —                                       | —               | —               | _     |  |

| bit 15       |                                                                                                                                                          |                 |       |                                         |                 |                 | bit 8 |  |

|              |                                                                                                                                                          |                 |       | =                                       |                 |                 |       |  |

| R/W-0        | R/W-0                                                                                                                                                    | R/W-0           | R/W-0 | R/W-0                                   | R/W-0           | R/W-0           | R/W-0 |  |

|              |                                                                                                                                                          |                 | SS2I  | R<7:0>                                  |                 |                 |       |  |

| bit 7        |                                                                                                                                                          |                 |       |                                         |                 |                 | bit C |  |

|              |                                                                                                                                                          |                 |       |                                         |                 |                 |       |  |

| Legend:      |                                                                                                                                                          |                 |       |                                         |                 |                 |       |  |

| R = Readab   | ole bit                                                                                                                                                  | W = Writable    | bit   | U = Unimpler                            | mented bit, rea | <b>d as</b> '0' |       |  |

| -n = Value a | at POR                                                                                                                                                   | '1' = Bit is se | t     | '0' = Bit is cleared x = Bit is unknown |                 |                 | nown  |  |

|              |                                                                                                                                                          |                 |       |                                         |                 |                 |       |  |

| bit 15-8     | Unimpleme                                                                                                                                                | nted: Read as   | ʻ0'   |                                         |                 |                 |       |  |

| bit 7-0      | <b>SS2R&lt;7:0&gt;:</b> Assign SPI2 Slave Select ( $\overline{SS2}$ ) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                 |       |                                         |                 |                 |       |  |

|              | 10110101 =                                                                                                                                               | Input tied to R | PI181 |                                         |                 |                 |       |  |

|              | •                                                                                                                                                        |                 |       |                                         |                 |                 |       |  |

|              | •                                                                                                                                                        |                 |       |                                         |                 |                 |       |  |

|              | -                                                                                                                                                        | Input tied to C | MP1   |                                         |                 |                 |       |  |

|              | 0000001 -                                                                                                                                                |                 |       |                                         |                 |                 |       |  |

00000000 = Input tied to Vss

#### REGISTER 11-12: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26

| U-0                               | U-0   | U-0   | U-0             | U-0                                | U-0   | U-0   | U-0   |

|-----------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

| —                                 | —     | —     |                 | —                                  | —     | —     | —     |

| bit 15                            |       |       |                 |                                    |       |       | bit 8 |

|                                   |       |       |                 |                                    |       |       |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                   |       |       | C1RX            | (R<7:0>                            |       |       |       |

| bit 7                             |       |       |                 |                                    |       |       | bit 0 |

|                                   |       |       |                 |                                    |       |       |       |

| Legend:                           |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

|                                   |       |       | x = Bit is unkr | nown                               |       |       |       |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-0  | <b>C1RXR&lt;7:0&gt;:</b> Assign CAN1 RX Input (C1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 10110101 = Input tied to RPI181                                                                                                         |

|          | •                                                                                                                                       |

|          | •                                                                                                                                       |

|          | •                                                                                                                                       |

|          | 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

#### REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>S: I2Cx Start bit</li> <li>Updated when Start, Reset or Stop is detected; cleared when the I<sup>2</sup>C module is disabled, I2CEN = 0.</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Indicates that a Start bit was not detected last</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                             |

|       | <ol> <li>= Read: Indicates that the data transfer is output from the slave</li> <li>= Write: Indicates that the data transfer is input to the slave</li> </ol>                                                                                                                                                |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                                           |

|       | <ol> <li>= Receive is complete, the I2CxRCV bit is full</li> <li>= Receive is not complete, the I2CxRCV bit is empty</li> </ol>                                                                                                                                                                               |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                   |

|       | <ul> <li>1 = Transmit is in progress, I2CxTRN is full (8 bits of data)</li> <li>0 = Transmit is complete, I2CxTRN is empty</li> </ul>                                                                                                                                                                         |

|       |                                                                                                                                                                                                                                                                                                               |

### REGISTER 19-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0      | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0    | R/W-0 |  |

|----------|-------|-------|-------|-------|-------|----------|-------|--|

| —        | —     | —     | —     | —     | —     | MSK<9:8> |       |  |

| bit 15   |       |       |       |       |       |          | bit 8 |  |

|          |       |       |       |       |       |          |       |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 |  |

| MSK<7:0> |       |       |       |       |       |          |       |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 7

bit 9-0 MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

bit 0

| <b>B</b> 8 4 4 4                             |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 |        |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------|--------|

| R/W-0                                        | R/W-0                                                                                                                                         | R/W-0                                                                                                                        | R/W-0                                                                                                                                                               | R/W-0                                                                                                            | R/W-0                                                                | R/W-0           | R/W-0  |

| F7MSK1                                       | F7MSK0                                                                                                                                        | F6MSK1                                                                                                                       | F6MSK0                                                                                                                                                              | F5MSK1                                                                                                           | F5MSK0                                                               | F4MSK1          | F4MSK0 |

| bit 15                                       |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 | bit 8  |

|                                              |                                                                                                                                               | <b>-</b>                                                                                                                     |                                                                                                                                                                     |                                                                                                                  | 5444.6                                                               | 5444.6          |        |

| R/W-0                                        | R/W-0                                                                                                                                         | R/W-0                                                                                                                        | R/W-0                                                                                                                                                               | R/W-0                                                                                                            | R/W-0                                                                | R/W-0           | R/W-0  |

| F3MSK1                                       | F3MSK0                                                                                                                                        | F2MSK1                                                                                                                       | F2MSK0                                                                                                                                                              | F1MSK1                                                                                                           | F1MSK0                                                               | F0MSK1          | F0MSK0 |

| bit 7                                        |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 | bit 0  |

|                                              |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 |        |

| Legend:                                      |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 |        |

| R = Readable                                 | e bit                                                                                                                                         | W = Writable                                                                                                                 | bit                                                                                                                                                                 | U = Unimpler                                                                                                     | nented bit, reac                                                     | <b>l as</b> '0' |        |

| -n = Value at                                | POR                                                                                                                                           | '1' = Bit is set                                                                                                             |                                                                                                                                                                     | '0' = Bit is cle                                                                                                 | ared                                                                 | x = Bit is unkr | nown   |

|                                              |                                                                                                                                               |                                                                                                                              |                                                                                                                                                                     |                                                                                                                  |                                                                      |                 |        |

| bit 15-14                                    | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                                                  | nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg                                                                           | gisters contain<br>gisters contain<br>gisters contain                                                                                                               | the mask<br>the mask<br>the mask                                                                                 |                                                                      |                 |        |

| bit 13-12                                    | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br><b>F6MSK&lt;1:0&gt;</b>                                                       | d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source                                                        | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit                                                                                         | the mask<br>the mask<br>the mask<br>(same values                                                                 |                                                                      |                 |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0>                                                                    | ed<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source                                      | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit                                                                   | the mask<br>the mask<br>the mask<br>(same values<br>(same values                                                 | as bits 15-14)                                                       |                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br><b>F6MSK&lt;1:0&gt;</b><br><b>F5MSK&lt;1:0&gt;</b><br><b>F4MSK&lt;1:0&gt;</b> | ed<br>nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg<br>: Mask Source<br>: Mask Source<br>: Mask Source                  | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit                                             | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values                                 | as bits 15-14)<br>as bits 15-14)                                     |                 |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br><b>F6MSK&lt;1:0&gt;</b><br><b>F5MSK&lt;1:0&gt;</b><br><b>F4MSK&lt;1:0&gt;</b> | ed<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source                                      | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit                                             | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values                                 | as bits 15-14)<br>as bits 15-14)                                     |                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0><br>F4MSK<1:0><br>F3MSK<1:0>                          | ed<br>nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg<br>: Mask Source<br>: Mask Source<br>: Mask Source                  | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit<br>e for Filter 3 bit                       | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values<br>(same values                 | as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)                   |                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0><br>F4MSK<1:0><br>F3MSK<1:0><br>F3MSK<1:0>            | ed<br>nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg<br>: Mask Source<br>: Mask Source<br>: Mask Source<br>: Mask Source | gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit<br>e for Filter 3 bit<br>e for Filter 2 bit | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values<br>(same values<br>(same values | as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)<br>as bits 15-14) |                 |        |

#### REGISTER 22-18: CxFMSKSEL1: CANx FILTERS 7-0 MASK SELECTION REGISTER 1

#### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 1 | <ul> <li>BUFM: Buffer Fill Mode Select bit</li> <li>1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt</li> <li>0 = Always starts filling the buffer from the Start address</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | ALTS: Alternate Input Sample Mode Select bit<br>1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample<br>0 = Always uses channel input selects for Sample MUX A                                                         |

Note 1: The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

| U-0             | U-0                                                                                                                                            | U-0                                                                       | U-0            | U-0               | U-0              | U-0            | U-0    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|-------------------|------------------|----------------|--------|

| _               | —                                                                                                                                              | —                                                                         | _              | _                 | —                | _              | _      |

| bit 15          | -                                                                                                                                              |                                                                           |                |                   |                  |                | bit 8  |

| U-0             | R/W-0                                                                                                                                          | R/W-0                                                                     | R/W-0          | R/W-0             | R/W-0            | R/W-0          | R/W-0  |

| _               | CFSEL2                                                                                                                                         | CFSEL1                                                                    | CFSEL0         | CFLTREN           | CFDIV2           | CFDIV1         | CFDIV0 |

| bit 7           |                                                                                                                                                |                                                                           |                |                   |                  | _              | bit (  |

| Legend:         |                                                                                                                                                |                                                                           |                |                   |                  |                |        |

| R = Readable    | bit                                                                                                                                            | W = Writable                                                              | bit            | U = Unimplem      | nented bit, read | <b>as</b> '0'  |        |

| -n = Value at F | POR                                                                                                                                            | '1' = Bit is set                                                          |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |

|                 | 111 = T5CLK<br>110 = T4CLK<br>101 = T3CLK<br>100 = T2CLK<br>011 = Reserv<br>010 = SYNCC<br>001 = Fosc <sup>(4</sup><br>000 = Fp <sup>(4)</sup> | (2)<br>(1)<br>(2)<br>/ed<br>D1 <sup>(3)</sup>                             |                |                   |                  |                |        |

| bit 3           | CFLTREN: Comparator x Filter Enable bit<br>1 = Digital filter is enabled<br>0 = Digital filter is disabled                                     |                                                                           |                |                   |                  |                |        |

| bit 2-0         | •                                                                                                                                              | Comparator x<br>divide 1:128<br>divide 1:64<br>divide 1:32<br>divide 1:16 | Filter Clock D | ivide Select bits | 5                |                |        |

# REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 2: See the Type B Timer Block Diagram (Figure 13-1).

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 17-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EVXXXGM00X/10X family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EVXXXGM00X/10X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                           | 40°C to +125°C |

|----------------------------------------------------------|----------------|

| Storage temperature                                      | 65°C to +160°C |

| Voltage on VDD with respect to Vss                       | 0.3V to +6.0V  |

| Voltage on VCAP with respect to Vss                      | 1.62V to 1.98V |

| Maximum current out of Vss pin                           | 350 mA         |

| Maximum current into Vod pin <sup>(2)</sup>              | 350 mA         |

| Maximum current sunk by any I/O pin                      | 20 mA          |

| Maximum current sourced by I/O pin                       | 18 mA          |

| Maximum current sourced/sunk by all ports <sup>(2)</sup> | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

#### TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | Standard Operating<br>(unless otherwise<br>Operating temperation | <b>stated)</b><br>ure -40°C ≤ <sup>°</sup> | : <b>4.5V to 5.5V</b><br>TA ≤ +85°C for<br>TA ≤ +125°C fo |     |

|----------------------|------------------------------------------|---------------------------------------------|------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                       | CKE                                        | СКР                                                       | SMP |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                | 0,1                                        | 0,1                                                       | 0,1 |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                | 1                                          | 0,1                                                       | 1   |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                | 0                                          | 0,1                                                       | 1   |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                      | 1                                          | 0                                                         | 0   |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                      | 1                                          | 1                                                         | 0   |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                      | 0                                          | 1                                                         | 0   |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                      | 0                                          | 0                                                         | 0   |

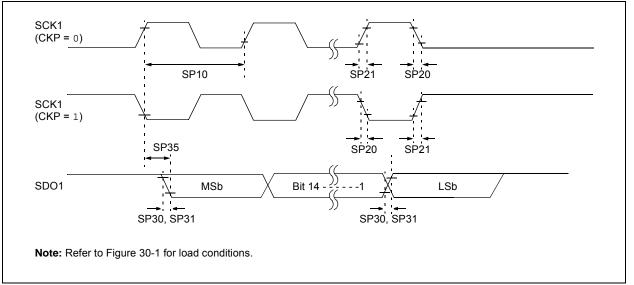

#### FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

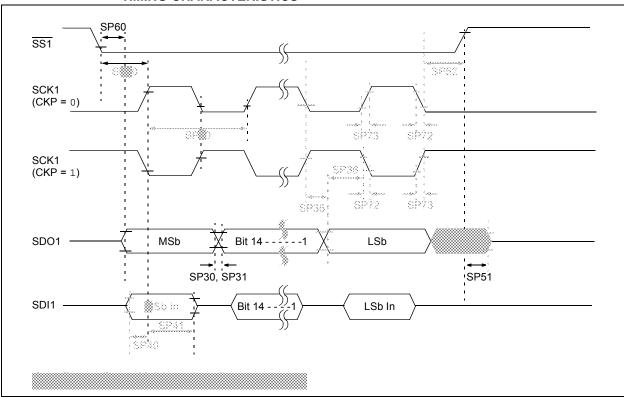

#### FIGURE 30-24: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        |                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |                                   |          |                                                                                                              |  |  |  |

|--------------------|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic                                       | Min.                                                                                                                                                                                                                                                                                                 | Тур.     | Max.                              | Units    | Conditions                                                                                                   |  |  |  |

| Device Supply      |        |                                                      |                                                                                                                                                                                                                                                                                                      |          |                                   |          |                                                                                                              |  |  |  |

| AD01               | AVDD   | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or VBOR                                                                                                                                                                                                                                                                  | _        | Lesser of:<br>VDD + 0.3<br>or 5.5 | V        |                                                                                                              |  |  |  |

| AD02               | AVss   | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                                                                                                            | _        | Vss + 0.3                         | V        |                                                                                                              |  |  |  |

|                    |        |                                                      | Refere                                                                                                                                                                                                                                                                                               | nce Inpu | ıts                               |          |                                                                                                              |  |  |  |

| AD05               | Vrefh  | Reference Voltage High                               | 4.5                                                                                                                                                                                                                                                                                                  | _        | 5.5                               | V        | VREFH = AVDD,<br>VREFL = AVSS = 0                                                                            |  |  |  |

| AD06               | VREFL  | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                                                                                 |          | AVDD - VBORMIN                    | V        | See Note 1                                                                                                   |  |  |  |

| AD06a              |        |                                                      | 0                                                                                                                                                                                                                                                                                                    | _        | 0                                 | V        | VREFH = AVDD,<br>VREFL = AVSS = 0                                                                            |  |  |  |

| AD07               | Vref   | Absolute Reference<br>Voltage                        | 4.5                                                                                                                                                                                                                                                                                                  | _        | 5.5                               | V        | Vref = Vrefh – Vrefl                                                                                         |  |  |  |

| AD08               | IREF   | Current Drain                                        | —                                                                                                                                                                                                                                                                                                    |          | 10<br>600                         | μA<br>μA | ADC off<br>ADC on                                                                                            |  |  |  |

| AD09               | lad    | Operating Current                                    | _                                                                                                                                                                                                                                                                                                    | 5<br>2   |                                   | mA<br>mA | ADC operating in 10-bit<br>mode (see <b>Note 1</b> )<br>ADC operating in 12-bit<br>mode (see <b>Note 1</b> ) |  |  |  |

|                    |        | •                                                    | Anal                                                                                                                                                                                                                                                                                                 | og Input |                                   |          | •                                                                                                            |  |  |  |

| AD12               | VINH   | Input Voltage Range Vinн                             | VINL                                                                                                                                                                                                                                                                                                 |          | VREFH                             | V        | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input              |  |  |  |

| AD13               | VINL   | Input Voltage Range Vın∟                             | VREFL                                                                                                                                                                                                                                                                                                | _        | AVss + 1V                         | V        | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input              |  |  |  |

| AD17               | Rin    | Recommended<br>Impedance of Analog<br>Voltage Source |                                                                                                                                                                                                                                                                                                      |          | 200                               | Ω        | Impedance to achieve<br>maximum performance of<br>ADC                                                        |  |  |  |

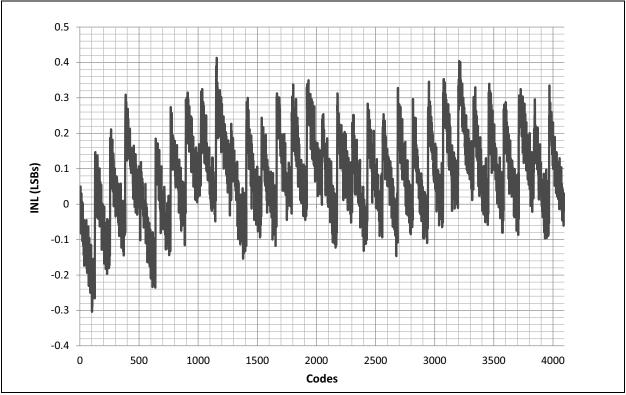

#### TABLE 30-54: ADC MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EVXXXGM00X/10X family electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.