Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | •                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm102-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                 | R/W-0                                                | EGISTER             | R-0             | R-0             | R-0        |

|---------------------|------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|-----------------|------------|

| VAR                 | 0-0                          | US1                                                   | US0                                                  | EDT <sup>(1)</sup>  | DL2             | DL1             | R-0<br>DL0 |

| pit 15              | _                            | 031                                                   | 030                                                  | EDI                 | DL2             |                 | bLU        |

| R/W-0               | R/W-0                        | R/W-1                                                 | R/W-0                                                | R/C-0               | R-0             | R/W-0           | R/W-0      |

| SATA                | SATB                         | SATDW                                                 | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA             | RND             | IF         |

| bit 7               | SAID                         | SAIDW                                                 | ACCOAL                                               | IF LOV /            | SFA             | RIND            | bit        |

| Legend:             |                              | C = Clearable                                         | - bit                                                |                     |                 |                 |            |

| R = Readable        | bit                          | W = Writable                                          |                                                      | U = Unimplem        | onted hit rea   | d as '0'        |            |

| -n = Value at F     |                              | '1' = Bit is set                                      |                                                      | '0' = Bit is clea   |                 | x = Bit is unkr |            |

|                     | -                            |                                                       |                                                      |                     |                 |                 |            |

| bit 15              | 1 = Variable e               | exception proce                                       | ocessing Later<br>essing latency                     | is enabled          |                 |                 |            |

| L:4 4 4             |                              |                                                       | sing latency is                                      | enabled             |                 |                 |            |

| bit 14<br>bit 13-12 | •                            | ted: Read as '                                        | 0<br>igned/Signed (                                  | Control hito        |                 |                 |            |

|                     | 01 = DSP eng<br>00 = DSP eng | gine multiplies<br>gine multiplies<br>gine multiplies | are signed                                           |                     |                 |                 |            |

| bit 11              |                              |                                                       | ation Control bi<br>e $DO$ loop at th                | e end of the cu     | rrent loop iter | ation           |            |

| bit 10-8            | 111 = 7 DO lo                | ops are active                                        |                                                      | ts                  |                 |                 |            |

| bit 7               |                              | Saturation En                                         |                                                      |                     |                 |                 |            |

|                     |                              | ator A saturatio<br>ator A saturatio                  |                                                      |                     |                 |                 |            |

| bit 6               | 1 = Accumula                 | Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |                 |                 |            |

| bit 5               | 1 = Data Space               | ce write satura                                       | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit      |                 |            |

| bit 4               | -                            | cumulator Satu                                        | ration Mode S                                        |                     |                 |                 |            |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 11.4 Slew Rate Selection

The slew rate selection feature allows the device to have control over the slew rate selection on the required I/O pin which supports this feature. For this purpose, for each I/O port, there are two registers: SR1x and SR0x, which configure the selection of the slew rate. The register outputs are directly connected to the associated I/O pins, which support the slew rate selection function. The SR1x register specifies the MSb and the SR0x register provides the LSb of the 2-bit field that selects the desired slew rate. For example, slew rate selections for PORTA are as follows:

### EXAMPLE 11-2: SLEW RATE SELECTIONS FOR PORTA

SR1Ax, SR0Ax = 00 = Fastest Slew rate SR1Ax, SR0Ax = 01 = 4x slower Slew rate SR1Ax, SR0Ax = 10 = 8x slower Slew rate SR1Ax, SR0Ax = 11 = 16x slower Slew rate

# 11.5 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping after it has been established.

# 11.5.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

### 11.5.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and Interrupt-on-Change (IOC) inputs.

In comparison, some digital only peripheral modules are never included in the PPS feature, because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between the remappable and nonremappable peripherals is that the remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, the non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all the other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 11.5.3 CONTROLLING PERIPHERAL PIN SELECT

The PPS features are controlled through two sets of SFRs: one to map the peripheral inputs and the other to map the outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# 11.5.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Table 11-1 and Register 11-1 through Register 11-17). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selects supported by the device.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP70R5 | RP70R4 | RP70R3 | RP70R2 | RP70R1 | RP70R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP69R5 | RP69R4 | RP69R3 | RP69R2 | RP69R1 | RP69R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

# REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup>

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP70R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP69R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP69 Output Pin bits (see Table 11-3 for peripheral function numbers) |

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|        | _   | RP97R5  | RP97R4  | RP97R3  | RP97R2  | RP97R1  | RP97R0  |

| bit 7  |     |         |         |         |         |         | bit 0   |

### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP118R<5:0>:** Peripheral Output Function is Assigned to RP118 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/106 devices only.

| R/W-0           | R/W-0                                                                                                      | R/W-0                                  | U-0            | U-0              | U-0             | U-0              | U-0    |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|------------------|-----------------|------------------|--------|--|--|

| FRMEN           | SPIFSD                                                                                                     | FRMPOL                                 | _              | —                | —               | —                | —      |  |  |

| bit 15          |                                                                                                            |                                        |                |                  |                 |                  | bit 8  |  |  |

|                 |                                                                                                            |                                        |                |                  |                 |                  |        |  |  |

| U-0             | U-0                                                                                                        | U-0                                    | U-0            | U-0              | U-0             | R/W-0            | R/W-0  |  |  |

| _               |                                                                                                            |                                        |                |                  | _               | FRMDLY           | SPIBEN |  |  |

| bit 7           |                                                                                                            |                                        |                |                  |                 |                  | bit 0  |  |  |

|                 |                                                                                                            |                                        |                |                  |                 |                  |        |  |  |

| Legend:         |                                                                                                            |                                        |                |                  |                 |                  |        |  |  |

| R = Readable    | bit                                                                                                        | W = Writable                           | bit            | U = Unimpler     | mented bit, rea | <b>d as</b> '0'  |        |  |  |

| -n = Value at F | POR                                                                                                        | '1' = Bit is set                       |                | '0' = Bit is cle | ared            | x = Bit is unkr  | nown   |  |  |

|                 |                                                                                                            |                                        |                |                  |                 |                  |        |  |  |

| bit 15          | FRMEN: Fran                                                                                                | med SPIx Supp                          | ort bit        |                  |                 |                  |        |  |  |

|                 |                                                                                                            |                                        |                | pin is used as   | the Frame Sy    | nc pulse input/o | utput) |  |  |

|                 |                                                                                                            | SPIx support is                        |                |                  |                 |                  |        |  |  |

| bit 14          |                                                                                                            | x Frame Sync F                         |                | n Control bit    |                 |                  |        |  |  |

|                 |                                                                                                            | /nc pulse input                        |                |                  |                 |                  |        |  |  |

| h:+ 40          | -                                                                                                          | /nc pulse outpu                        | . ,            |                  |                 |                  |        |  |  |

| bit 13          |                                                                                                            | ame Sync Pulse                         | 5              |                  |                 |                  |        |  |  |

|                 |                                                                                                            | /nc pulse is acti<br>/nc pulse is acti |                |                  |                 |                  |        |  |  |

| bit 12-2        | -                                                                                                          | ited: Read as '                        |                |                  |                 |                  |        |  |  |

| bit 1           | •                                                                                                          |                                        |                | hit              |                 |                  |        |  |  |

|                 | <b>FRMDLY:</b> Frame Sync Pulse Edge Select bit<br>1 = Frame Sync pulse coincides with the first bit clock |                                        |                |                  |                 |                  |        |  |  |

|                 | 0 = Frame Sync pulse precedes the first bit clock                                                          |                                        |                |                  |                 |                  |        |  |  |

| bit 0           | SPIBEN: SPI                                                                                                | x Enhanced Bu                          | iffer Enable b | it               |                 |                  |        |  |  |

|                 | 1 = Enhance                                                                                                | d buffer is enab                       | led            |                  |                 |                  |        |  |  |

|                 | 0 = Enhance                                                                                                | d buffer is disab                      | led (Standard  | d mode)          |                 |                  |        |  |  |

|                 |                                                                                                            |                                        |                |                  |                 |                  |        |  |  |

### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R-0, HSC               | R-0, HSC      | R-0, HSC                           | U-0            | U-0                             | R/C-0, HSC                    | R-0, HSC          | R-0, HSC         |  |  |  |  |

|------------------------|---------------|------------------------------------|----------------|---------------------------------|-------------------------------|-------------------|------------------|--|--|--|--|

| ACKSTAT                | TRSTAT        | ACKTIM                             | —              | _                               | BCL                           | GCSTAT            | ADD10            |  |  |  |  |

| bit 15                 |               |                                    |                |                                 |                               |                   | bit 8            |  |  |  |  |

|                        |               |                                    |                |                                 |                               |                   |                  |  |  |  |  |

| R/C-0, HS              | R/C-0, HS     | R-0, HSC                           | R/C-0, HSC     | R/C-0, HSC                      | R-0, HSC                      | R-0, HSC          | R-0, HSC         |  |  |  |  |

| IWCOL                  | I2COV         | D_A                                | Р              | S                               | R_W                           | RBF               | TBF              |  |  |  |  |

| bit 7 bit 0            |               |                                    |                |                                 |                               |                   |                  |  |  |  |  |

| 1                      |               | O Ola anali                        | I.a. Ia :4     | LICO Llaratur                   |                               | velete le it      |                  |  |  |  |  |

| Legend:<br>R = Readabl | a h:t         | C = Clearab                        |                |                                 | are Settable/Clear            |                   |                  |  |  |  |  |

|                        |               | W = Writabl                        |                | 0 = Unimpien                    | ented bit, read a             | HS = Hardware     | Cottoble bit     |  |  |  |  |

| -n = Value at          | PUR           | '1' = Bit is s                     | 51             |                                 | areu                          |                   | Settable bit     |  |  |  |  |

| bit 15                 | ACKSTAT: A    | Acknowledge                        | Status bit (up | dated in all Ma                 | ster and Slave m              | odes)             |                  |  |  |  |  |

|                        |               | edge was not                       |                |                                 |                               | ,                 |                  |  |  |  |  |

|                        | 0 = Acknowl   | edge was rec                       | eived from sla | ave                             |                               |                   |                  |  |  |  |  |

| bit 14                 |               |                                    |                | -                               | naster; applicable            | e to master trans | mit operation)   |  |  |  |  |

|                        |               | ransmit is in p<br>ransmit is not  |                | ts + ACK)                       |                               |                   |                  |  |  |  |  |

| bit 13                 | ACKTIM: Ad    | cknowledge T                       | ime Status bit | t (valid in I <sup>2</sup> C Sl | ave mode only)                |                   |                  |  |  |  |  |

|                        |               |                                    |                |                                 |                               | g edge of SCLx o  | lock             |  |  |  |  |

|                        |               | -                                  | -              | eared on 9 <sup>11</sup> risi   | ng edge of SCL>               | ( clock           |                  |  |  |  |  |

| bit 12-11              | -             | nted: Read a                       |                |                                 | 1 1 20                        |                   |                  |  |  |  |  |

| bit 10                 |               |                                    |                |                                 |                               | nodule is disable | d, 12CEN = 0)    |  |  |  |  |

|                        |               | ision has not l                    |                |                                 | or slave transm               | it operation      |                  |  |  |  |  |

| bit 9                  |               |                                    |                | ed after Stop de                | etection)                     |                   |                  |  |  |  |  |

|                        |               | call address v                     |                | ·                               | ,                             |                   |                  |  |  |  |  |

| bit 8                  |               |                                    |                | red after Stop o                | detection)                    |                   |                  |  |  |  |  |

| bit o                  |               | dress was m                        |                |                                 |                               |                   |                  |  |  |  |  |

|                        |               | dress was no                       |                |                                 |                               |                   |                  |  |  |  |  |

| bit 7                  | IWCOL: Wri    | te Collision D                     | etect bit      |                                 |                               |                   |                  |  |  |  |  |

|                        |               |                                    | the I2CxTRN    | I register failed               | because the I <sup>2</sup> C  | module is busy;   | must be cleared  |  |  |  |  |

|                        | In softw      | are<br>n has not occi              | irred          |                                 |                               |                   |                  |  |  |  |  |

| bit 6                  |               | Receive Ove                        |                | ł                               |                               |                   |                  |  |  |  |  |

| bit o                  |               |                                    | -              |                                 | s still holding the           | previous byte; 12 | 2COV is a "don't |  |  |  |  |

|                        | care" in      | Transmit mod                       | de, must be c  | leared in softwa                | -                             |                   |                  |  |  |  |  |

|                        |               | w has not occ                      |                |                                 |                               |                   |                  |  |  |  |  |

| bit 5                  |               |                                    |                | g as I <sup>2</sup> C slave)    |                               |                   |                  |  |  |  |  |

|                        |               | s that the last<br>s that the last |                |                                 | was an address                | i                 |                  |  |  |  |  |

| bit 4                  | P: I2Cx Stop  |                                    |                |                                 | -                             |                   |                  |  |  |  |  |

|                        | 1 = Indicates | s that a Stop b                    |                | letected last                   | d when the I <sup>2</sup> C r | nodule is disable | ed, I2CEN = 0.   |  |  |  |  |

# REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER

| U-0             | R/W-x                                                       | U-0                               | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x     |  |  |  |

|-----------------|-------------------------------------------------------------|-----------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|--|

| —               | WAKFIL                                                      |                                   | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0   |  |  |  |

| bit 15          |                                                             |                                   |                  |                  |                  |                 | bit 8     |  |  |  |

|                 |                                                             |                                   |                  |                  |                  |                 |           |  |  |  |

| R/W-x           | R/W-x                                                       | R/W-x                             | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x     |  |  |  |

| SEG2PHTS        | SAM                                                         | SEG1PH2                           | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0    |  |  |  |

| bit 7           |                                                             |                                   |                  |                  |                  |                 | bit 0     |  |  |  |

| Legend:         |                                                             |                                   |                  |                  |                  |                 |           |  |  |  |

| R = Readable    | bit                                                         | W = Writable                      | bit              | U = Unimpler     | nented bit, read | <b>d as</b> '0' |           |  |  |  |

| -n = Value at I | POR                                                         | '1' = Bit is set                  |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown      |  |  |  |

| -               |                                                             |                                   |                  |                  |                  |                 |           |  |  |  |

| bit 15          | Unimplemer                                                  | nted: Read as '                   | כי               |                  |                  |                 |           |  |  |  |

| bit 14          | WAKFIL: Sel                                                 | lect CAN Bus L                    | ine Filter for V | Vake-up bit      |                  |                 |           |  |  |  |

|                 |                                                             | N bus line filter                 |                  |                  |                  |                 |           |  |  |  |

| 1.11.4.0.44     |                                                             | line filter is not                |                  | e-up             |                  |                 |           |  |  |  |

| bit 13-11       | •                                                           | nted: Read as '                   |                  |                  |                  |                 |           |  |  |  |

| bit 10-8        | SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           | ·                                 |                  |                  |                  |                 |           |  |  |  |

| L:1 7           | 000 = Length                                                |                                   |                  | -1 1-11          |                  |                 |           |  |  |  |

| bit 7           |                                                             | Phase Segmer                      | nt 2 Time Sele   | ect bit          |                  |                 |           |  |  |  |

|                 | 1 = Freely pro<br>0 = Maximum                               | n of SEG1PH<2                     | ::0> bits or Inf | ormation Proce   | essing Time (IP  | T), whichever i | s greater |  |  |  |

| bit 6           | SAM: Sample                                                 | e of the CAN B                    | us Line bit      |                  |                  |                 |           |  |  |  |

|                 |                                                             | s sampled three<br>s sampled once |                  |                  |                  |                 |           |  |  |  |

| bit 5-3         |                                                             | 0>: Phase Segr                    | -                | •                |                  |                 |           |  |  |  |

|                 | 111 = Length                                                | -                                 |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | 000 = Length                                                | n is 1 x Tq                       |                  |                  |                  |                 |           |  |  |  |

| bit 2-0         | -                                                           | >: Propagation                    | Time Segmen      | t bits           |                  |                 |           |  |  |  |

|                 | 111 = Length                                                |                                   | Ū                |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | •                                                           |                                   |                  |                  |                  |                 |           |  |  |  |

|                 | 000 = Length                                                | n is 1 x Tq                       |                  |                  |                  |                 |           |  |  |  |

|                 | - 3-                                                        |                                   |                  |                  |                  |                 |           |  |  |  |

# REGISTER 22-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

### REGISTER 22-16: CxRXFnSID: CANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

|               |              | -                 | •            |                                         |                  |               |       |

|---------------|--------------|-------------------|--------------|-----------------------------------------|------------------|---------------|-------|

| R/W-x         | R/W-x        | R/W-x             | R/W-x        | R/W-x                                   | R/W-x            | R/W-x         | R/W-x |

| SID10         | SID9         | SID8              | SID7         | SID6                                    | SID5             | SID4          | SID3  |

| bit 15        |              |                   |              |                                         |                  |               | bit 8 |

|               |              |                   |              |                                         |                  |               |       |

| R/W-x         | R/W-x        | R/W-x             | U-0          | R/W-x                                   | U-0              | R/W-x         | R/W-x |

| SID2          | SID1         | SID0              |              | EXIDE                                   |                  | EID17         | EID16 |

| bit 7         |              |                   |              |                                         |                  |               | bit C |

|               |              |                   |              |                                         |                  |               |       |

| Legend:       |              |                   |              |                                         |                  |               |       |

| R = Readabl   | e bit        | W = Writable      | bit          | U = Unimpler                            | nented bit, read | <b>as</b> '0' |       |

| -n = Value at | POR          | '1' = Bit is set  |              | '0' = Bit is cleared x = Bit is unknown |                  |               | Iown  |

|               |              |                   |              |                                         |                  |               |       |

| bit 15-5      | SID<10:0>: S | Standard Identif  | ier bits     |                                         |                  |               |       |

|               | 0            |                   | •            | 1' to match filte                       |                  |               |       |

|               | 0            | -                 |              | 0' to match filte                       | er               |               |       |

| bit 4         | Unimplemen   | ted: Read as '    | 0'           |                                         |                  |               |       |

| bit 3         | EXIDE: Exter | nded Identifier I | Enable bit   |                                         |                  |               |       |

|               | If MIDE = 1: |                   |              |                                         |                  |               |       |

|               |              | , ,               |              | ed Identifier add                       |                  |               |       |

|               | 0 = Matches  | only messages     | with Standar | d Identifier add                        | resses           |               |       |

|               | Ignores EXID | )E bit.           |              |                                         |                  |               |       |

| bit 2         | •            | ted: Read as '    | 0'           |                                         |                  |               |       |

| bit 1-0       | •            | Extended Iden     |              |                                         |                  |               |       |

|               |              |                   |              | 1' to match filte                       | er               |               |       |

|               | 0            |                   | •            | 0' to match filte                       |                  |               |       |

|               | 0            |                   |              |                                         |                  |               |       |

### REGISTER 22-17: CxRXFnEID: CANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x           | R/W-x      | R/W-x              | R/W-x   | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|------------|--------------------|---------|-------------------|-----------------|-----------------|-------|

|                 |            |                    | EID     | <15:8>            |                 |                 |       |

| bit 15          |            |                    |         |                   |                 |                 | bit 8 |

| R/W-x           | R/W-x      | R/W-x              | R/W-x   | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |            |                    | EID     | )<7:0>            |                 |                 |       |

| bit 7           |            |                    |         |                   |                 |                 | bit 0 |

| Legend:         |            |                    |         |                   |                 |                 |       |

| R = Readable    | bit        | W = Writable b     | it      | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR        | '1' = Bit is set   |         | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|                 |            |                    |         |                   |                 |                 |       |

| bit 15-0        | EID<15:0>: | Extended Identifie | er bits |                   |                 |                 |       |

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

# dsPIC33EVXXXGM00X/10X FAMILY

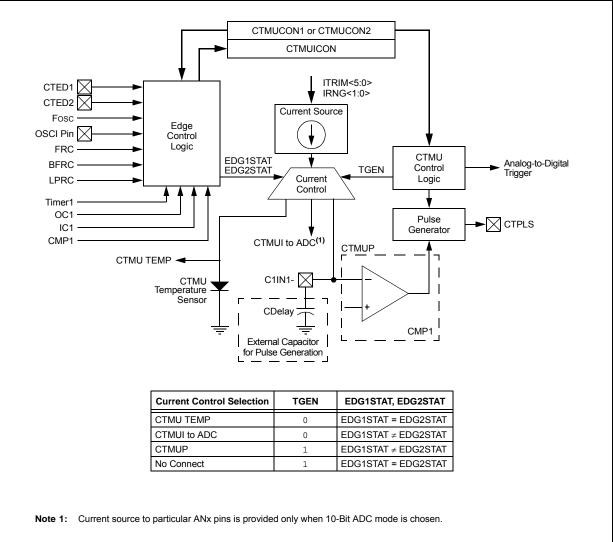

### REGISTER 23-2: CTMUCON2: CTMU CONTROL REGISTER 2 (CONTINUED)

- bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits

- 1111 = Fosc

- 1110 = OSCI pin

- 1101 = FRC Oscillator

- 1100 = BFRC Oscillator

- 1011 = Internal LPRC Oscillator

- 1010 = Reserved

- 1001 = Reserved

- 1000 = Reserved 0111 = Reserved

- 0111 = Reserved

- 0101 = Reserved

- 0100 = CMP1 module

- 0011 = CTED2 pin

- 0010 = CTED1 pin

- 0001 = OCMP1 module

- 0000 = IC1 module

- bit 1-0 Unimplemented: Read as '0'

| R/W-0        | R/W-0                                                                                                                      | R/W-0                                                                 | R/W-0                                                               | R/W-0                                                                                    | R/W-0                    | R/W-0                | R/W-0                |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|----------------------|----------------------|--|--|

| ITRIM5       | ITRIM4                                                                                                                     | ITRIM3                                                                | ITRIM2                                                              | ITRIM1                                                                                   | ITRIM0                   | IRNG1 <sup>(2)</sup> | IRNG0 <sup>(2)</sup> |  |  |

| bit 15       | - 1                                                                                                                        |                                                                       |                                                                     | 1                                                                                        | 1                        |                      | bit 8                |  |  |

|              |                                                                                                                            |                                                                       |                                                                     |                                                                                          |                          |                      |                      |  |  |

| U-0          | U-0                                                                                                                        | U-0                                                                   | U-0                                                                 | U-0                                                                                      | U-0                      | U-0                  | U-0                  |  |  |

| —            | —                                                                                                                          | —                                                                     | —                                                                   | —                                                                                        | —                        | —                    | —                    |  |  |

| bit 7        |                                                                                                                            |                                                                       |                                                                     |                                                                                          |                          |                      | bit (                |  |  |

| Legend:      |                                                                                                                            |                                                                       |                                                                     |                                                                                          |                          |                      |                      |  |  |

| R = Readab   | le bit                                                                                                                     | W = Writable                                                          | bit                                                                 | U = Unimplem                                                                             | nented bit, read         | d as '0'             |                      |  |  |

| -n = Value a | It POR                                                                                                                     | '1' = Bit is set                                                      |                                                                     | '0' = Bit is clea                                                                        | ared                     | x = Bit is unkn      | iown                 |  |  |

|              | 000001 = Mir<br>000000 = No<br>111111 = Mir<br>111110 = Mir<br>•                                                           | nimum positive<br>minal current o<br>nimum negative<br>nimum negative | change from r<br>output specified<br>e change from<br>e change from | nominal current<br>nominal current<br>d by IRNG<1:0><br>nominal curren<br>nominal curren | + 2%<br>t – 2%<br>t – 4% |                      |                      |  |  |

|              | 100010 = Maximum negative change from nominal current – 60%<br>100001 = Maximum negative change from nominal current – 62% |                                                                       |                                                                     |                                                                                          |                          |                      |                      |  |  |

| bit 9-8      | 11 = 100 × Ba<br>10 = 10 × Bas<br>01 = Base Cu<br>00 = 1000 × B                                                            | se Current<br>Irrent Level<br>Base Current <sup>(1)</sup>             | )                                                                   | bits <sup>(2)</sup>                                                                      |                          |                      |                      |  |  |

| bit 7-0      | Unimplemen                                                                                                                 | ted: Read as '                                                        | 0'                                                                  |                                                                                          |                          |                      |                      |  |  |

|              | This current range<br>Refer to the CTML                                                                                    |                                                                       |                                                                     |                                                                                          | -                        |                      |                      |  |  |

# REGISTER 23-3: CTMUICON: CTMU CURRENT CONTROL REGISTER<sup>(3)</sup>

for the current range selection values.3: Current sources are not generated when 12-Bit ADC mode is chosen. Current sources are active only when 10-Bit ADC mode is chosen.

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT **CONTROL REGISTER**

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | _   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>as</b> '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| <b>s</b> '0' |

|--------------|

| ;            |

| bit 15-12 | Unimplemented: Read as '0'             |

|-----------|----------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits |

|           | 1111 <b>= FLT4</b>                     |

|           | 1110 = FLT2                            |

|           | 1101 = Reserved                        |

|           | 1100 = Reserved                        |

|           | 1011 = Reserved                        |

|           | 1010 = Reserved                        |

|           | 1001 = Reserved                        |

|           | 1000 = Reserved                        |

|           | 0111 = Reserved<br>0110 = Reserved     |

|           | 0110 = Reserved<br>0101 = PWM3H        |

|           | 0100 = PWM3L                           |

|           | 0011 = PWM2H                           |

|           | 0010 = PWM2L                           |

|           | 0001 = PWM1H                           |

|           | 0000 = PWM1L                           |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits |

|           | 1111 <b>= FLT4</b>                     |

|           | 1110 = FLT2                            |

|           | 1101 = Reserved                        |

|           | 1100 = Reserved                        |

|           | 1011 = Reserved                        |

|           | 1010 = Reserved                        |

|           | 1001 = Reserved                        |

|           | 1000 = Reserved<br>0111 = Reserved     |

|           | 0111 - Reserved                        |

|           | 0110 = PWM3H                           |

|           | 0100 = PWM3L                           |

|           | 0011 = PWM2H                           |

|           | 0010 = PWM2L                           |

|           | 0001 = PWM1H                           |

|           | 0000 = PWM1L                           |

| Bit Field     | Register  | Description                                                                                                                                                                                                                                                                                                 |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIOFNC      | FOSC      | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is the general purpose digital I/O pin                                                                                                                                                                        |

| IOL1WAY       | FOSC      | Peripheral Pin Select Configuration bit<br>1 = Allows only one reconfiguration<br>0 = Allows multiple reconfigurations                                                                                                                                                                                      |

| FCKSM<1:0>    | FOSC      | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                           |

| PLLKEN        | FOSC      | PLL Lock Wait Enable bit<br>1 = Clock switches to the PLL source; will wait until the PLL lock signal is valid<br>0 = Clock switch will not wait for PLL lock                                                                                                                                               |

| WDTPS<3:0>    | FWDT      | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                       |

| WDTPRE        | FWDT      | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                       |

| FWDTEN<1:0>   | FWDT      | <ul> <li>Watchdog Timer Enable bits</li> <li>11 = WDT is enabled in hardware</li> <li>10 = WDT is controlled through the SWDTEN bit</li> <li>01 = WDT is enabled only while device is active and disabled in Sleep; the SWDTEN bit is disabled</li> <li>00 = WDT and the SWDTEN bit are disabled</li> </ul> |

| WINDIS        | FWDT      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer is in Non-Window mode<br>0 = Watchdog Timer is in Window mode                                                                                                                                                                                        |

| WDTWIN<1:0>   | FWDT      | Watchdog Timer Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                         |

| BOREN         | FPOR      | Brown-out Reset (BOR) Detection Enable bit<br>1 = BOR is enabled<br>0 = BOR is disabled                                                                                                                                                                                                                     |

| ICS<1:0>      | FICD      | ICD Communication Channel Select bits<br>11 = Communicates on PGEC1 and PGED1<br>10 = Communicates on PGEC2 and PGED2<br>01 = Communicates on PGEC3 and PGED3<br>00 = Reserved, do not use                                                                                                                  |

| DMTIVT<15:0>  | FDMTINTVL | Lower 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTIVT<31:16> | FDMTINTVH | Upper 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTCNT<15:0>  | FDMTCNTL  | Lower 16 Bits of 32-Bit Field that Configures the DMT Instruction Count Time-out Value bits                                                                                                                                                                                                                 |

| TABLE 27-2: | dsPIC33EVXXXGM00X/10X CONFIGURATION BITS DESCRIPTION (CONTINUED) |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

| Bit Field     | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMTCNT<31:16> | FDMCNTH  | Upper 16 Bits of 32-Bit Field that Configures the DMT Instruction Count Time-out Value bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMTEN         | FDMT     | Deadman Timer Enable bit<br>1 = Deadman Timer is enabled and cannot be disabled by software<br>0 = Deadman Timer is disabled and can be enabled by software                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWMLOCK       | FDEVOPT  | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ALTI2C1       | FDEVOPT  | Alternate I <sup>2</sup> C Pins for I2C1 bit<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CTXT1<2:0>    | FALTREG  | Specifies the Alternate Working Register Set 1 Association with<br>Interrupt Priority Level (IPL) bits<br>111 = Not assigned<br>110 = Alternate Register Set 1 is assigned to IPL Level 6<br>101 = Alternate Register Set 1 is assigned to IPL Level 5<br>100 = Alternate Register Set 1 is assigned to IPL Level 4<br>011 = Alternate Register Set 1 is assigned to IPL Level 3<br>010 = Alternate Register Set 1 is assigned to IPL Level 2<br>001 = Alternate Register Set 1 is assigned to IPL Level 2<br>001 = Alternate Register Set 1 is assigned to IPL Level 1 |

| CTXT2<2:0>    | FALTREG  | Specifies the Alternate Working Register Set 2 Association with<br>Interrupt Priority Level (IPL) bits<br>111 = Not assigned<br>110 = Alternate Register Set 2 is assigned to IPL Level 6<br>101 = Alternate Register Set 2 is assigned to IPL Level 5<br>100 = Alternate Register Set 2 is assigned to IPL Level 4<br>011 = Alternate Register Set 2 is assigned to IPL Level 3<br>010 = Alternate Register Set 2 is assigned to IPL Level 3<br>010 = Alternate Register Set 2 is assigned to IPL Level 2<br>001 = Alternate Register Set 2 is assigned to IPL Level 1 |

# TABLE 27-2: dsPIC33EVXXXGM00X/10X CONFIGURATION BITS DESCRIPTION (CONTINUED)

| R       | R                                                    | R |        | R<br>23:16> <sup>(1)</sup> | R | R | R      |

|---------|------------------------------------------------------|---|--------|----------------------------|---|---|--------|

|         |                                                      |   | DEVID  | 23.10/                     |   |   |        |

| bit 23  |                                                      |   |        |                            |   |   | bit 16 |

| R       | R                                                    | R | R      | R                          | R | R | R      |

|         |                                                      |   | DEVID< | <15:8> <b>(1)</b>          |   |   |        |

| bit 15  |                                                      |   |        |                            |   |   | bit 8  |

| R       | R                                                    | R | R      | R                          | R | R | R      |

|         |                                                      |   | DEVID  | <7:0> <sup>(1)</sup>       |   |   |        |

| bit 7   |                                                      |   |        |                            |   |   | bit 0  |

| Legend: | <b>gend:</b> R = Read-Only bit U = Unimplemented bit |   |        |                            |   |   |        |

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to "*dsPIC33EVXXXGM00X/10X Families Flash Programming Specification*" (DS70005137) for the list of Device ID values.

### REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER

| Legend: | R = Read-only bit |   |         | U = Unimplen           | nented bit |   |        |

|---------|-------------------|---|---------|------------------------|------------|---|--------|

| bit 7   |                   |   |         |                        |            |   | bit 0  |

|         |                   |   | DEVRE   | /<7:0> <sup>(1)</sup>  |            |   |        |

| R       | R                 | R | R       | R                      | R          | R | R      |

| bit 15  |                   |   |         |                        |            |   | bit 8  |

|         |                   |   | DEVREV  | <15:8> <sup>(1)</sup>  |            |   |        |

| R       | R                 | R | R       | R                      | R          | R | R      |

| bit 23  |                   |   |         |                        |            |   | bit 16 |

|         |                   |   | DEVREV< | <23:16> <sup>(1)</sup> |            |   |        |

| R       | R                 | R | R       | R                      | R          | R | R      |

### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to "*dsPIC33EVXXXGM00X/10X Families Flash Programming Specification*" (DS70005137) for the list of device revision values.

# 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

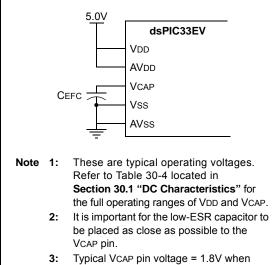

# 27.3 On-Chip Voltage Regulator

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

3: Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

# 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the Power-up Timer (PWRT) Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device should VDD fall below the BOR threshold voltage.

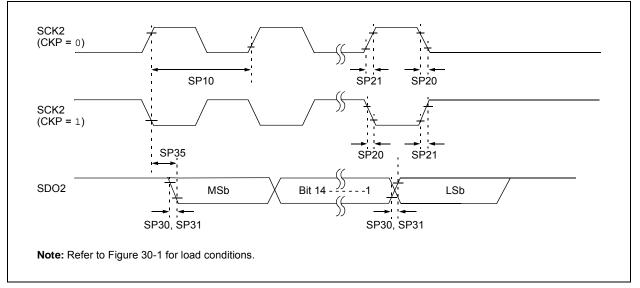

### TABLE 30-30: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industr} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Exterm} \end{array}$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                       | СКЕ | СКР | SMP |  |

| 15 MHz               | Table 30-31                              |                                             |                                                                                                                                                                                                                                                                                  | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-32                                 | —                                                                                                                                                                                                                                                                                | 1   | 0,1 | 1   |  |

| 9 MHz                | _                                        | Table 30-33                                 | —                                                                                                                                                                                                                                                                                | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-34                                                                                                                                                                                                                                                                      | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-35                                                                                                                                                                                                                                                                      | 1   | 1   | 0   |  |