Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·>>F

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

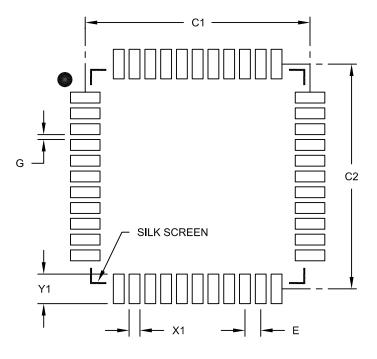

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 36-UQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm103-e-m5 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

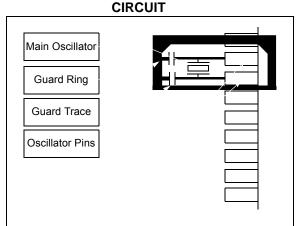

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

# FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

#### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EVXXXGM00X/10X family core has two Data Spaces: X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified, linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X DS is used by all instructions and supports all addressing modes. The X DS has separate read and write data buses. The X read data bus is the read data path for all instructions that view the DS as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class). The Y DS is used in concert with the X DS by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to the X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

### TABLE 4-22: PMD REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1               | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|---------|--------|--------|--------|--------|-------|-------|--------|--------|--------|---------------------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD    | T1MD    | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD <sup>(1)</sup> | AD1MD | 0000          |

| PMD2        | 0762  | _      | —      | —      | —       | IC4MD   | IC3MD  | IC2MD  | IC1MD  |        | —     |       | _      | OC4MD  | OC3MD  | OC2MD               | OC1MD | 0000          |

| PMD3        | 0764  | —      | —      | —      | —       | —       | CMPMD  | _      | _      |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD4        | 0766  | —      | —      | —      | —       | —       | —      | _      | _      |        | —     |       | _      | REFOMD | CTMUMD | _                   | —     | 0000          |

| PMD6        | 076A  | —      | —      | —      | —       | —       | PWM3MD | PWM2MD | PWM1MD |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD7        | 076C  | _      | —      | —      | —       | -       | —      | —      | _      | -      | —     | -     | DMA0MD | —      | —      |                     | —     | 0000          |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA1MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA2MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA3MD |        |        |                     |       |               |

| PMD8        | 076E  | —      | —      | —      | SENT2MD | SENT1MD | —      | _      | DMTMD  |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

| REGISTER      |                                                                                                                                                       | CON: DMA C                                                                                                                           |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|-----------------|--------|--|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                                 | R/W-0                                                                                                                                | R/W-0                                                                                                                                                        | R/W-0             | U-0             | U-0             | U-0    |  |  |  |  |  |

| CHEN          | SIZE                                                                                                                                                  | DIR                                                                                                                                  | HALF                                                                                                                                                         | NULLW             | —               | —               | _      |  |  |  |  |  |

| bit 15        |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              | •                 |                 |                 | bit 8  |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| U-0           | U-0                                                                                                                                                   | R/W-0                                                                                                                                | R/W-0                                                                                                                                                        | U-0               | U-0             | R/W-0           | R/W-0  |  |  |  |  |  |

| —             | —                                                                                                                                                     | AMODE1                                                                                                                               | AMODE0                                                                                                                                                       | —                 | _               | MODE1           | MODE0  |  |  |  |  |  |

| bit 7         |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 | bit 0  |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| Legend:       |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                 | W = Writable                                                                                                                         | bit                                                                                                                                                          | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                   | '1' = Bit is set                                                                                                                     |                                                                                                                                                              | '0' = Bit is clea | ared            | x = Bit is unkn | own    |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 15        | CHEN: DMA                                                                                                                                             | Channel Enabl                                                                                                                        | le bit                                                                                                                                                       |                   |                 |                 |        |  |  |  |  |  |

|               | 1 = Channel is enabled                                                                                                                                |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 0 = Channel is disabled                                                                                                                               |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 14        | SIZE: DMA D                                                                                                                                           | SIZE: DMA Data Transfer Size bit                                                                                                     |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 1 = Byte<br>0 = Word                                                                                                                                  |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| L:1 1 0       |                                                                                                                                                       | anafar Direction                                                                                                                     | a hit (a a ura a /d                                                                                                                                          | activation bus    | a a la at)      |                 |        |  |  |  |  |  |

| bit 13        | <ul> <li>DIR: DMA Transfer Direction bit (source/destination bus select)</li> <li>1 = Reads from RAM address, writes to peripheral address</li> </ul> |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 0 = Reads from peripheral address, writes to RAM address                                                                                              |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 12        | HALF: DMA Block Transfer Interrupt Select bit                                                                                                         |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 1 = Initiates interrupt when half of the data has been moved                                                                                          |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 0 = Initiates interrupt when all of the data has been moved                                                                                           |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 11        | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                     |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 1 = Null data write to peripheral in addition to RAM write (DIR bit must also be clear)                                                               |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 0 = Normal operation                                                                                                                                  |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 10-6      | -                                                                                                                                                     | ted: Read as '                                                                                                                       |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 5-4       | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                                   |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               | 11 = Reserved                                                                                                                                         |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                       | ral Indirect moon<br>Indirect without read without read without the second second second second second second second second second s |                                                                                                                                                              | ent mode          |                 |                 |        |  |  |  |  |  |

|               | •                                                                                                                                                     | Indirect with F                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 3-2       | •                                                                                                                                                     | ted: Read as '                                                                                                                       |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

| bit 1-0       | -                                                                                                                                                     | DMA Channel                                                                                                                          |                                                                                                                                                              | de Select bits    |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              |                   | transfer from   | /to each DMA bu | (ffer) |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      | <ul><li>11 = One-Shot Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)</li><li>10 = Continuous Ping-Pong modes are enabled</li></ul> |                   |                 |                 |        |  |  |  |  |  |

|               | 01 = One-Shot Ping-Pong modes are disabled<br>00 = Continuous Ping-Pong modes are disabled                                                            |                                                                                                                                      |                                                                                                                                                              |                   |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                       |                                                                                                                                      |                                                                                                                                                              | bled              |                 |                 |        |  |  |  |  |  |

## REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

- 6. The PPS pin mapping rules are as follows:

- Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin is disabled. Only the Analog Pin Select registers control the digital input buffer, not the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin; no exceptions.

#### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The Timer1 External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

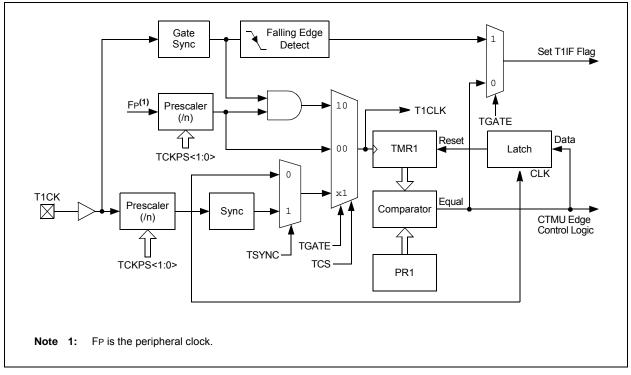

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are given in Table 12-1.

| TABLE 12-1: | TIMER MODE SETTI | NGS |

|-------------|------------------|-----|

|-------------|------------------|-----|

| Mode                    | TCS | TGATE | TSYNC |  |  |

|-------------------------|-----|-------|-------|--|--|

| Timer                   | 0   | 0     | x     |  |  |

| Gated Timer             | 0   | 1     | х     |  |  |

| Synchronous<br>Counter  | 1   | x     | 1     |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### BUFFER 22-7: CANx MESSAGE BUFFER WORD 6

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | Byte  | 7<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | Byte  | 6<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | <b>d as</b> '0' |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-8 Byte 7<15:8>: CANx Message Byte 7 bits

bit 7-0 Byte 6<7:0>: CANx Message Byte 6 bits

#### BUFFER 22-8: CANx MESSAGE BUFFER WORD 7

| U-0                                | U-0 | U-0                                     | R/W-x | R/W-x        | R/W-x            | R/W-x         | R/W-x |

|------------------------------------|-----|-----------------------------------------|-------|--------------|------------------|---------------|-------|

| —                                  |     | —                                       |       |              | FILHIT<4:0>(1)   |               |       |

| bit 15                             |     |                                         |       |              |                  |               | bit 8 |

|                                    |     |                                         |       |              |                  |               |       |

| U-0                                | U-0 | U-0                                     | U-0   | U-0          | U-0              | U-0           | U-0   |

| —                                  | —   |                                         | —     | —            | —                | —             |       |

| bit 7                              |     |                                         |       |              |                  |               | bit 0 |

| Legend:                            |     |                                         |       |              |                  |               |       |

| R = Readable I                     | bit | W = Writable I                          | oit   | U = Unimplen | nented bit, read | <b>as</b> '0' |       |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |              |                  | nown          |       |

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits<sup>(1)</sup>

Encodes number of filter that resulted in writing this buffer.

bit 7-0 Unimplemented: Read as '0'

Note 1: Only written by module for receive buffers, unused for transmit buffers.

# dsPIC33EVXXXGM00X/10X FAMILY

| R/W-                | 0 U-0                                | R/W-0                                  | R/W-0                                        | R/W-0                   | R/W-0                       | R/W-0                   | R/W-0                   |  |  |  |

|---------------------|--------------------------------------|----------------------------------------|----------------------------------------------|-------------------------|-----------------------------|-------------------------|-------------------------|--|--|--|

| CHON                | IB —                                 | CH0SB5 <sup>(1,3)</sup>                | CH0SB4 <sup>(1,3)</sup>                      | CH0SB3 <sup>(1,3)</sup> | CH0SB2 <sup>(1,3)</sup>     | CH0SB1 <sup>(1,3)</sup> | CH0SB0 <sup>(1,3)</sup> |  |  |  |

| bit 15              |                                      |                                        |                                              |                         |                             |                         | bit 8                   |  |  |  |

|                     |                                      |                                        |                                              |                         |                             |                         |                         |  |  |  |

| R/W-                |                                      | R/W-0                                  | R/W-0                                        | R/W-0                   | R/W-0                       | R/W-0                   | R/W-0                   |  |  |  |

| CHON                | IA —                                 | CH0SA5 <sup>(1,3)</sup>                | CH0SA4 <sup>(1,3)</sup>                      | CH0SA3 <sup>(1,3)</sup> | CH0SA2 <sup>(1,3)</sup>     | CH0SA1 <sup>(1,3)</sup> | CH0SA0 <sup>(1,3)</sup> |  |  |  |

| bit 7               |                                      |                                        |                                              |                         |                             |                         | bit 0                   |  |  |  |

| Logondi             |                                      |                                        |                                              |                         |                             |                         |                         |  |  |  |

| Legend:<br>R = Read | table bit                            | W = Writable b                         | nit                                          |                         | ented bit, read             | <b>ae</b> '0'           |                         |  |  |  |

|                     | e at POR                             | (1) = Bit is set                       | JIL                                          | '0' = Bit is clea       | -                           | x = Bit is unkr         | NWD                     |  |  |  |

|                     |                                      |                                        |                                              |                         | licu                        |                         |                         |  |  |  |

| bit 15              |                                      | nannel 0 Negativ                       |                                              | for Sample MU           | IX B bit                    |                         |                         |  |  |  |

|                     | 1 = Channe                           | el 0 negative inp                      | ut is AN1 <sup>(1)</sup>                     |                         |                             |                         |                         |  |  |  |

|                     |                                      | el 0 negative inp                      |                                              |                         |                             |                         |                         |  |  |  |

| bit 14              | -                                    | ented: Read as                         |                                              |                         |                             | 2)                      |                         |  |  |  |

| bit 13-8            |                                      | 0>: Channel 0 P                        |                                              |                         | e MUX B bits <sup>(1,</sup> | 3)                      |                         |  |  |  |

|                     |                                      | Channel 0 positiv<br>Channel 0 positiv |                                              |                         |                             |                         |                         |  |  |  |

|                     |                                      | Channel 0 positiv                      |                                              |                         | d aap voltage)              |                         |                         |  |  |  |

|                     | •                                    |                                        |                                              | ( III IIII              | 5 - F                       |                         |                         |  |  |  |

|                     | •                                    |                                        |                                              |                         |                             |                         |                         |  |  |  |

|                     | • 011111 = (                         | Channel 0 positiv                      | ve input is AN3                              | 1                       |                             |                         |                         |  |  |  |

|                     |                                      |                                        | el 0 positive input is AN30                  |                         |                             |                         |                         |  |  |  |

|                     | •                                    |                                        |                                              |                         |                             |                         |                         |  |  |  |

|                     | •                                    |                                        |                                              |                         |                             |                         |                         |  |  |  |

|                     | • 000001 = (                         | Channel 0 positiv                      | ve input is AN1                              |                         |                             |                         |                         |  |  |  |

|                     |                                      | Channel 0 positiv                      |                                              |                         |                             |                         |                         |  |  |  |

| bit 7               | CHONA: Ch                            | nannel 0 Negativ                       | e Input Select                               | for Sample MU           | IX A bit                    |                         |                         |  |  |  |

|                     |                                      | el 0 negative inp                      |                                              |                         |                             |                         |                         |  |  |  |

|                     | 0 = Channe                           | el 0 negative inp                      | ut is VREFL                                  |                         |                             |                         |                         |  |  |  |

| bit 6               | Unimpleme                            | ented: Read as                         | '0'                                          |                         |                             |                         |                         |  |  |  |

| Note 1:             | AN0 to AN7 are r                     |                                        | •                                            | • •                     | •                           | •                       |                         |  |  |  |

|                     | determine how er                     | • •                                    | · ·                                          | -                       |                             |                         |                         |  |  |  |

| 2:                  | If the op amp is a<br>input is used. | selected (OPAE                         | N bit (CMxCON                                | N<10>) = 1), the        | e OAx input is u            | ised; otherwise         | , the ANx               |  |  |  |

|                     |                                      |                                        | <b>,</b> , , , , , , , , , , , , , , , , , , |                         |                             | • • •                   |                         |  |  |  |

### REGISTER 24-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER

3: See the "Pin Diagrams" section for the available analog channels for each device.

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|------------------|------------------------------------|--------------------|-------|-------|--|

|                                    |       |       | CSS              | <15:8>                             |                    |       |       |  |

| bit 15                             |       |       |                  |                                    |                    |       | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|                                    |       |       | CSS              | <7:0>                              |                    |       |       |  |

| bit 7                              |       |       |                  |                                    |                    |       | bit C |  |

| Legend:                            |       |       |                  |                                    |                    |       |       |  |

| R = Readable bit W = Writable bit  |       |       | oit              | U = Unimplemented bit, read as '0' |                    |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared                               | x = Bit is unknown |       |       |  |

bit 15-0 CSS<15:0>: ADCx Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

**2:** CSSx = ANx, where 'x' = 0-5.

#### 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

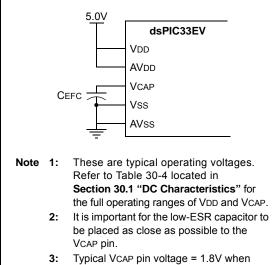

#### 27.3 On-Chip Voltage Regulator

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

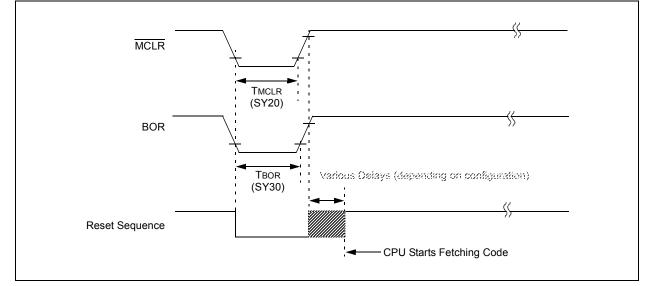

#### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the Power-up Timer (PWRT) Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device should VDD fall below the BOR threshold voltage.

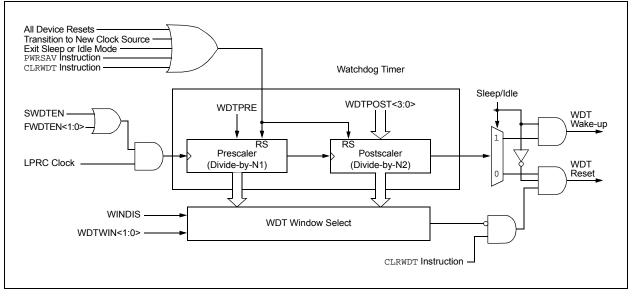

### 27.5 Watchdog Timer (WDT)

For dsPIC33EVXXXGM00X/10X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

#### 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

#### 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN<1:0> Configuration bits in the FWDT Configuration register. When the FWDTEN<1:0> Configuration bits are set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTENx Configuration bits have been programmed to '00'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window (WDTWIN<1:0>) select bits.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | # of<br>Words                                                                                                                                                                                                | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|

| 25                 | CTXTSWP              | CTXTSWP | #lit3                  | Switch CPU register context to context defined by lit3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                            | 2              | None                     |

|                    |                      | CTXTSWP | Wn                     | Switch CPU register context to context defined by Wn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                            | 2              | None                     |

| 26                 | DAW                  | DAW     | Wn                     | Wn = decimal adjust Wn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                            | 1              | С                        |

| 27                 | DEC                  | DEC     | f                      | f = f - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                            | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG                 | WREG = f – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                            | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | Ws,Wd                  | Wd = Ws - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                            | 1              | C,DC,N,OV,Z              |

| 28                 | DEC2                 | DEC2    | f                      | f = f - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                            | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | f,WREG                 | WREG = f – 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                            | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | Ws,Wd                  | Wd = Ws - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WordsCyclesntext121111111111111111111111111111111111111111118111811181118111811181118111811181118111111111111111111111111111111111111111111111111111111111111111111111111111111111 </td <td>C,DC,N,OV,Z</td> | C,DC,N,OV,Z    |                          |

| 29                 | DISI                 | DISI    | #lit14                 | Disable Interrupts for k instruction cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                            | 1              | None                     |

| 30                 | DIV                  | DIV.S   | Wm,Wn                  | Signed 16/16-bit Integer Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                            | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD  | Wm,Wn                  | Signed 32/16-bit Integer Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                            | 18             | N,Z,C,OV                 |