Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

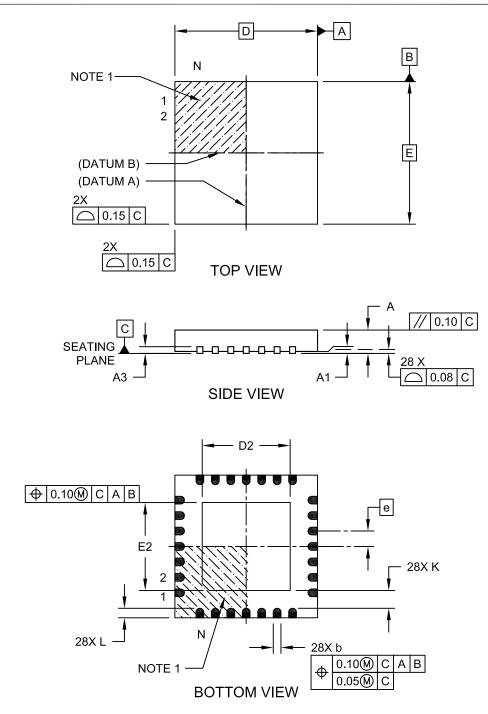

| Mounting Type              | Surface Mount                                                                   |

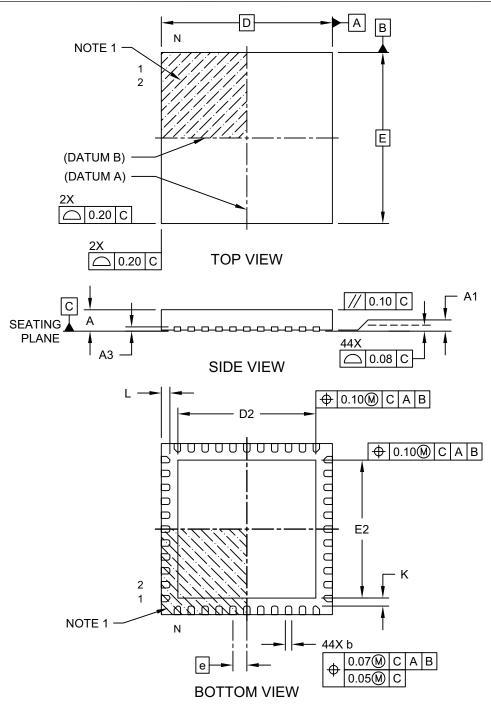

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm104-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                     | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10       | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------------------------------------------|--------|------------|---------|---------|--------------|-------|----------|------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1     | 0900  | _                                          | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     | —        | ENFLTA     | _            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                      | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                            |        |            |         |         |              | Ou    | tput Con | npare 1 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                                            |        |            |         |         |              |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                                            |        |            |         |         |              | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                                          | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                      | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                            |        |            |         |         |              | Ou    | tput Con | npare 2 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |                                            |        |            |         |         |              |       | Outpu    | ut Compare | e 2 Register |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |                                            |        |            |         |         |              | Out   | put Com  | pare 2 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC3CON1     | 0914  | _                                          | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                      | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                            |        |            |         |         |              | Ou    | tput Con | npare 3 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                            |        |            |         |         |              |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                            |        |            |         |         |              | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  | _                                          | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                      | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                            |        |            |         |         |              | Ou    | tput Con | npare 4 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC4R        | 0924  | Output Compare 4 Register                  |        |            |         |         |              |       |          |            |              | xxxx   |          |          |          |          |          |               |

| OC4TMR      | 0926  | Output Compare 4 Timer Value Register xxxx |        |            |         |         |              |       |          |            |              | xxxx   |          |          |          |          |          |               |

| Logondu     |       |                                            | -      | ot: – unim |         | 1 /-1   | <b>-</b> · · |       |          |            |              |        |          |          |          |          |          | <i>.</i>      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-26: DMAC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6    | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|---------|----------|---------|---------|---------|---------|---------|---------|---------------|

| DMA0CON     | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | —       | _        | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ     | 0B02  | FORCE  | _      | _      | _      | _      | _      | -     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL    | 0B04  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STAH    | 0B06  | _      | _      | _      | _      | _      |        |       |       |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA0STBL    | 0B08  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STBH    | 0B0A  | _      | _      | —      | _      | _      |        | _     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA0PAD     | 0B0C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0CNT     | 0B0E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA1CON     | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | _     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA1REQ     | 0B12  | FORCE  | —      | —      | _      |        | -      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA1STAL    | 0B14  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STAH    | 0B16  | —      | —      | —      | _      |        | -      | _     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA1STBL    | 0B18  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STBH    | 0B1A  | —      | —      | —      | _      |        | -      | _     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA1PAD     | 0B1C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1CNT     | 0B1E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA2CON     | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | _     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ     | 0B22  | FORCE  | —      | _      | —      | —      | —      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA2STAL    | 0B24  |        |        |        | -      |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STAH    | 0B26  | —      | —      |        | _      |        | —      | —     | —     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA2STBL    | 0B28  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STBH    | 0B2A  | —      | —      | —      | _      |        | -      | _     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA2PAD     | 0B2C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2CNT     | 0B2E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA3CON     | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | _     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ     | 0B32  | FORCE  | —      | —      | _      |        | -      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL    | 0B34  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STAH    | 0B36  | —      | —      | —      | _      |        | -      | _     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA3STBL    | 0B38  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STBH    | 0B3A  | —      | —      | _      |        | _      | _      | —     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA3PAD     | 0B3C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3CNT     | 0B3E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMAPWC      | 0BF0  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       |         |         | PWCC    | )L<3:0> |         | 0000          |

| DMARQC      | 0BF2  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       | _       |         | RQCC    | )L<3:0> |         | 0000          |

| DMAPPS      | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _     | _       | _        | _       | _       |         | PPS     | Г<3:0>  |         | 0000          |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

#### REGISTER 17-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |

|----------|-----|-----|-----|-----|-----|----------|----------|

| CHPCLKEN | —   | —   | —   | —   | —   | CHOPCLK9 | CHOPCLK8 |

| bit 15   |     |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CHOPCLK7 | CHOPCLK6 | CHOPCLK5 | CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | CHPCLKEN: Enable Chop Clock Generator bit                                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Chop clock generator is enabled                                                                                                   |

|           | 0 = Chop clock generator is disabled                                                                                                  |

| bit 14-10 | Unimplemented: Read as '0'                                                                                                            |

| bit 9-0   | CHOPCLK<9:0>: Chop Clock Divider bits                                                                                                 |

|           | The frequency of the chop clock signal is given by the following expression:<br>Chop Frequency = (FP/PCLKDIV<2:0>)/(CHOPCLK<9:0> + 1) |

#### REGISTER 17-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0            | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|------------------|-------|

|                 |       |                  | MDC   | <15:8>           |                 |                  |       |

| bit 15          |       |                  |       |                  |                 |                  | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0            | R/W-0 |

|                 |       |                  | MD    | C<7:0>           |                 |                  |       |

| bit 7           |       |                  |       |                  |                 |                  | bit 0 |

|                 |       |                  |       |                  |                 |                  |       |

| Legend:         |       |                  |       |                  |                 |                  |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | <b>id as</b> '0' |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki  | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

## REGISTER 17-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

|                 |                                                                      | DAMA             |                                                                            | D/14/ 0  |       | D 444 0 |       |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|----------------------------------------------------------------------------|----------|-------|---------|-------|--|--|--|--|--|

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0                                                                      | R/W-0    | R/W-0 | R/W-0   | R/W-0 |  |  |  |  |  |

|                 |                                                                      |                  | PDC                                                                        | x<15:8>  |       |         |       |  |  |  |  |  |

| bit 15          |                                                                      |                  |                                                                            |          |       |         | bit 8 |  |  |  |  |  |

|                 |                                                                      |                  |                                                                            |          |       |         | ]     |  |  |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0                                                                      | R/W-0    | R/W-0 | R/W-0   | R/W-0 |  |  |  |  |  |

|                 |                                                                      |                  | PDC                                                                        | \$x<7:0> |       |         |       |  |  |  |  |  |

| bit 7           |                                                                      |                  |                                                                            |          |       |         | bit 0 |  |  |  |  |  |

|                 |                                                                      |                  |                                                                            |          |       |         |       |  |  |  |  |  |

| Legend:         |                                                                      |                  |                                                                            |          |       |         |       |  |  |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                                                                            |          |       |         |       |  |  |  |  |  |

| -n = Value at P | OR                                                                   | '1' = Bit is set | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |          |       |         |       |  |  |  |  |  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

#### REGISTER 17-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PHAS  | Ex<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PHAS  | Ex<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs.

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL. NOTES:

## 21.2 UART Control Registers

## REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                                                                      | DE: UARTx N                                                       |                                                             | TER                                |                                                    |                  |                           |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------|----------------------------------------------------|------------------|---------------------------|--|--|--|--|

| R/W-0                 | U-0                                                                                                             | R/W-0                                                             | R/W-0                                                       | R/W-0                              | U-0                                                | R/W-0            | R/W-0                     |  |  |  |  |

| UARTEN <sup>(1)</sup> | _                                                                                                               | USIDL                                                             | IREN <sup>(2)</sup>                                         | RTSMD                              | _                                                  | UEN1             | UEN0                      |  |  |  |  |

| bit 15                |                                                                                                                 |                                                                   |                                                             | ·                                  |                                                    |                  | bit 8                     |  |  |  |  |

| R/W-0, HC             | R/W-0                                                                                                           | R/W-0, HC                                                         | R/W-0                                                       | R/W-0                              | R/W-0                                              | R/W-0            | R/W-0                     |  |  |  |  |

| WAKE                  | LPBACK                                                                                                          | ABAUD                                                             | URXINV                                                      | BRGH                               | PDSEL1                                             | PDSEL0           | STSEL                     |  |  |  |  |

| bit 7                 |                                                                                                                 | 101100                                                            | Orodity                                                     | ыкоп                               | TDOLLI                                             | TDOLLO           | bit (                     |  |  |  |  |

|                       |                                                                                                                 |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

| Legend:               |                                                                                                                 | HC = Hardwar                                                      | e Clearable bit                                             | t                                  |                                                    |                  |                           |  |  |  |  |

| R = Readable          | e bit                                                                                                           | W = Writable I                                                    | oit                                                         | U = Unimplemented bit, read as '0' |                                                    |                  |                           |  |  |  |  |

| -n = Value at         | POR                                                                                                             | '1' = Bit is set                                                  |                                                             | '0' = Bit is cle                   | eared                                              | x = Bit is unk   | nown                      |  |  |  |  |

| bit 15                | 1 = UARTx is                                                                                                    | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U          | ARTx pins are                                               |                                    |                                                    |                  |                           |  |  |  |  |

|                       | is minima                                                                                                       |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

| bit 14                | •                                                                                                               | ted: Read as '0                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

| bit 13                | <b>USIDL:</b> UARTx Stop in Idle Mode bit<br>1 = Discontinues module operation when the device enters Idle mode |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

|                       |                                                                                                                 | iues module op<br>es module opera                                 |                                                             |                                    | 's Idle mode                                       |                  |                           |  |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                           |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

|                       |                                                                                                                 | oder and decod                                                    |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

| bit 11                | 0 = IrDA encoder and decoder are disabled<br><b>RTSMD:</b> Mode Selection for $\overline{\text{UxRTS}}$ Pin bit |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

|                       | 1 = UxRTS p                                                                                                     | oin is in Simplex<br>oin is in Flow Co                            | mode                                                        |                                    |                                                    |                  |                           |  |  |  |  |

| bit 10                | •                                                                                                               | ited: Read as '0                                                  |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

| bit 9-8               | -                                                                                                               | IARTx Pin Enab                                                    |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

|                       | 11 = UxTX, L<br>10 = UxTX, L<br>01 = UxTX, L                                                                    | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used;    | i <u>nd use</u> d <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |  |  |  |

| bit 7                 | WAKE: UAR                                                                                                       | Tx Wake-up on                                                     | Start bit Detect                                            | During Sleep                       | Mode Enable I                                      | oit              |                           |  |  |  |  |

|                       | in hardwa                                                                                                       | ontinues to sam<br>are on the follow<br>is not enabled            |                                                             |                                    | generated on                                       | the falling edge | , bit is cleared          |  |  |  |  |

| bit 6                 | -                                                                                                               | RTx Loopback                                                      | Mode Select b                                               | it                                 |                                                    |                  |                           |  |  |  |  |

|                       |                                                                                                                 | k mode is enab                                                    |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

|                       | 0 = Loopbac                                                                                                     | k mode is disab                                                   | led                                                         |                                    |                                                    |                  |                           |  |  |  |  |

| "d:<br>tra            | efer to " <b>Univers</b><br>sPIC33/PIC24 F<br>Insmit operation                                                  | amily Referenc                                                    | e <i>Manual"</i> for i                                      | nformation on e                    | enabling the U                                     |                  |                           |  |  |  |  |

|                       | is feature is only                                                                                              | -                                                                 |                                                             |                                    | )).                                                |                  |                           |  |  |  |  |

| 3: Th                 | nis feature is only available on 44-pin and 64-pin devices.                                                     |                                                                   |                                                             |                                    |                                                    |                  |                           |  |  |  |  |

4: This feature is only available on 64-pin devices.

| U-0               | U-0                                                  | U-0              | U-0                  | U-0            | U-0              | U-0                | U-0   |  |  |

|-------------------|------------------------------------------------------|------------------|----------------------|----------------|------------------|--------------------|-------|--|--|

| _                 | —                                                    | _                | —                    | _              | —                | _                  | —     |  |  |

| bit 15            |                                                      |                  |                      |                |                  |                    | bit 8 |  |  |

|                   |                                                      |                  |                      |                |                  |                    |       |  |  |

| U-0               | U-0                                                  | U-0              | R-0                  | R-0            | R-0              | R-0                | R-0   |  |  |

| _                 | —                                                    | — DNCNT<4:0>     |                      |                |                  |                    |       |  |  |

| bit 7             |                                                      |                  |                      |                |                  |                    | bit 0 |  |  |

|                   |                                                      |                  |                      |                |                  |                    |       |  |  |

| Legend:           |                                                      |                  |                      |                |                  |                    |       |  |  |

| R = Readab        | ole bit                                              | W = Writable     | bit                  | U = Unimpler   | mented bit, read | <b>as</b> '0'      |       |  |  |

| -n = Value at POR |                                                      | '1' = Bit is set | '0' = Bit is cleared |                |                  | x = Bit is unknown |       |  |  |

|                   |                                                      |                  |                      |                |                  |                    |       |  |  |

| bit 15-5          | Unimplemented: Read as '0'                           |                  |                      |                |                  |                    |       |  |  |

| bit 4-0           | DNCNT<4:0>: DeviceNet™ Filter Bit Number bits        |                  |                      |                |                  |                    |       |  |  |

|                   | 10010-11111 = Invalid selection                      |                  |                      |                |                  |                    |       |  |  |

|                   | 10001 <b>= Co</b> r                                  | mpare up to Dat  | a Byte 3, bit 6      | 6 with EID<17> |                  |                    |       |  |  |

|                   | •                                                    |                  |                      |                |                  |                    |       |  |  |

|                   | •                                                    |                  |                      |                |                  |                    |       |  |  |

|                   | •                                                    |                  |                      |                |                  |                    |       |  |  |

|                   | 00001 = Compare up to Data Byte 1, bit 7 with EID<0> |                  |                      |                |                  |                    |       |  |  |

|                   | 00000 = D0                                           | not compare da   | la bytes             |                |                  |                    |       |  |  |

|                   |                                                      |                  |                      |                |                  |                    |       |  |  |

## REGISTER 22-2: CxCTRL2: CANx CONTROL REGISTER 2

|              | U-0                                                                                                                                                                  | U-0                                                                                                                                                                                                          | R/W-0                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                    | R/W-0                                                                                                           | R/W-0                                  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|

| _            | —                                                                                                                                                                    | _                                                                                                                                                                                                            | CH123SB2                                                                                                                                            | CH123SB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CH123NB1                                                                                                                                                 | CH123NB0                                                                                                        | CH123SB0                               |  |  |  |  |

| bit 15       |                                                                                                                                                                      |                                                                                                                                                                                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                                 | bit 8                                  |  |  |  |  |

| 11.0         | 11.0                                                                                                                                                                 | 11.0                                                                                                                                                                                                         | R/W-0                                                                                                                                               | D/M/ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                    |                                                                                                                 |                                        |  |  |  |  |

| U-0          | U-0                                                                                                                                                                  | U-0                                                                                                                                                                                                          | -                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                        | R/W-0<br>CH123NA0                                                                                               | R/W-0                                  |  |  |  |  |

|              |                                                                                                                                                                      |                                                                                                                                                                                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                                 | CH123SA0                               |  |  |  |  |

| bit 7        |                                                                                                                                                                      |                                                                                                                                                                                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                                 | bit                                    |  |  |  |  |

| Legend:      |                                                                                                                                                                      |                                                                                                                                                                                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                                 |                                        |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                               | W = Writable                                                                                                                                                                                                 | e bit                                                                                                                                               | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nented bit, read                                                                                                                                         | as '0'                                                                                                          |                                        |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                               | '1' = Bit is se                                                                                                                                                                                              | et                                                                                                                                                  | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ared                                                                                                                                                     | x = Bit is unknown                                                                                              |                                        |  |  |  |  |