Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

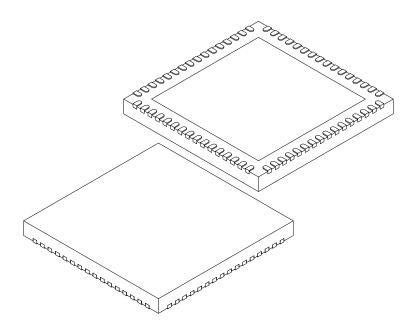

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm104t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

| Note: | The modulo corrected Effective Address    |

|-------|-------------------------------------------|

|       | is written back to the register only when |

|       | Pre-Modify or Post-Modify Addressing      |

|       | mode is used to compute the Effective     |

|       | Address. When an address offset, such as  |

|       | [W7 + W2] is used, Modulo Addressing      |

|       | correction is performed, but the contents |

|       | of the register remain unchanged.         |

#### 4.6 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.6.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these conditions are met:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |

|-------|-------------------------------------------|

|       | Addressing can be enabled simultaneously  |

|       | using the same W register, but Bit-       |

|       | Reversed Addressing operation will always |

|       | take precedence for data writes when      |

|       | enabled.                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

The operation of Bit-Reversed Addressing is shown in Figure 4-16 and Table 4-46.

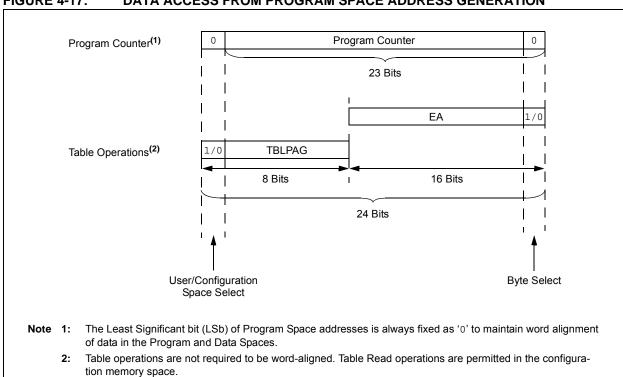

#### FIGURE 4-17: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

| U-0          | U-0                                             | U-0                                            | U-0          | U-0               | U-0              | U-0                | U-0   |  |  |  |  |

|--------------|-------------------------------------------------|------------------------------------------------|--------------|-------------------|------------------|--------------------|-------|--|--|--|--|

| —            | —                                               | —                                              | —            | —                 | —                | —                  | —     |  |  |  |  |

| bit 15       |                                                 |                                                |              |                   |                  |                    | bit 8 |  |  |  |  |

|              |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

| U-0          | U-0                                             | R/W-0                                          | R/W-0        | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |  |  |

| —            | —                                               |                                                |              | TUN               | l<5:0>           |                    |       |  |  |  |  |

| bit 7        |                                                 |                                                |              |                   |                  |                    | bit 0 |  |  |  |  |

|              |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

| Legend:      |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

| R = Readabl  | e bit                                           | W = Writable                                   | bit          | U = Unimplen      | nented bit, read | l as '0'           |       |  |  |  |  |

| n = Value at | POR                                             | '1' = Bit is set                               |              | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |  |  |  |

|              |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

| bit 15-6     | Unimplemen                                      | ted: Read as 'd                                | כי           |                   |                  |                    |       |  |  |  |  |

| oit 5-0      | TUN<5:0>: FRC Oscillator Tuning bits            |                                                |              |                   |                  |                    |       |  |  |  |  |

|              | 111111 <b>= Ce</b>                              | 111111 = Center frequency – 0.048% (7.363 MHz) |              |                   |                  |                    |       |  |  |  |  |

|              | •                                               | •                                              |              |                   |                  |                    |       |  |  |  |  |

|              |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

|              | 100001 <b>= Ce</b>                              | 100001 = Center frequency – 1.5% (7.259 MHz)   |              |                   |                  |                    |       |  |  |  |  |

|              | 100000 = Center frequency – 1.548% (7.2552 MHz) |                                                |              |                   |                  |                    |       |  |  |  |  |

|              |                                                 | nter frequency                                 |              |                   |                  |                    |       |  |  |  |  |

|              | •                                               | nter frequency                                 | + 1.452% (7. | 477 WHZ)          |                  |                    |       |  |  |  |  |

|              | •                                               |                                                |              |                   |                  |                    |       |  |  |  |  |

|              | •                                               |                                                |              |                   |                  |                    |       |  |  |  |  |

|              |                                                 | nter frequency                                 |              |                   |                  |                    |       |  |  |  |  |

|              | 000000 = Ce                                     | nter frequency                                 | (1.37 MHZ N  | ominal)           |                  |                    |       |  |  |  |  |

|              |                                                 |                                                |              |                   |                  |                    |       |  |  |  |  |

### **REGISTER 9-4:** OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(1)</sup>

| Periphera<br>Select II<br>Register | nput | Input/<br>Output | Pin Assignment                 |

|------------------------------------|------|------------------|--------------------------------|

| 00                                 | 000  | I                | Vss                            |

| 00                                 | 001  | Ι                | CMP1 <sup>(1)</sup>            |

| 0 0                                | 010  | Ι                | CMP2 <sup>(1)</sup>            |

| 000 00                             | 011  | Ι                | CMP3 <sup>(1)</sup>            |

| 000 01                             | 100  | Ι                | CMP4 <sup>(1)</sup>            |

| 000 01                             | 101  | —                | —                              |

| 000 11                             | 100  | Ι                | CMP5 <sup>(1)</sup>            |

| 000 11                             | 101  | _                | _                              |

| 000 11                             | 110  | _                |                                |

| 000 11                             | 111  | _                | _                              |

| 001 00                             | 000  | Ι                | RPI16                          |

| 001 00                             | 001  | I                | RPI17                          |

| 001 00                             | 010  | I                | RPI18                          |

| 001 00                             | 011  | I                | RPI19                          |

| 001 01                             | 100  | I/O              | RP20                           |

| 001 01                             | 101  | _                |                                |

| 001 01                             | 110  | _                | _                              |

| 001 01                             | 111  | _                | _                              |

| 001 10                             | 000  | I                | RPI24                          |

| 001 10                             | 001  | Ι                | RPI25                          |

| 001 10                             | 010  | _                | —                              |

| 001 10                             | 011  | I                | RPI27                          |

| 001 11                             | 100  | Ι                | RPI28                          |

| 001 11                             | 101  |                  | _                              |

| 001 11                             | 110  |                  | _                              |

| 001 11                             | 111  |                  | _                              |

| 010 00                             |      | Ι                | RPI32                          |

| 010 00                             |      | I                | RPI33                          |

| 010 00                             |      | I                | RPI34                          |

| 010 00                             |      | I/O              | RP35                           |

| 010 01                             |      | I/O              | RP36                           |

| 010 01                             |      | I/O              | RP37                           |

| 010 01                             |      | I/O              | RP38                           |

| 010 01                             |      | 1/O              | RP39                           |

| 010 10                             |      | I/O              |                                |

| 010 10                             |      | 1/U              | RPI44                          |

| 010 11                             |      | -                | RPI45                          |

| 010 11                             |      |                  | RPI46                          |

| 010 11                             |      | 1                | RPI47                          |

|                                    |      | I/O              |                                |

| 011 00                             |      | -                | RP48<br>the PPS Input register |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate the PPS Input register values that are unimplemented.

Note 1: These are virtual pins. See Section 11.5.4.1 "Virtual Connections" for more information on selecting this pin assignment.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP70R5 | RP70R4 | RP70R3 | RP70R2 | RP70R1 | RP70R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP69R5 | RP69R4 | RP69R3 | RP69R2 | RP69R1 | RP69R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup>

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP70R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP69R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP69 Output Pin bits (see Table 11-3 for peripheral function numbers) |

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|        | _   | RP97R5  | RP97R4  | RP97R3  | RP97R2  | RP97R1  | RP97R0  |

| bit 7  |     |         |         |         |         |         | bit 0   |

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP118R<5:0>:** Peripheral Output Function is Assigned to RP118 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/106 devices only.

### 15.1 Input Capture Control Registers

#### REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER     | 15-1: ICxCO                                                                                                                                            | N1: INPUT C                                                                                                                     | CAPTURE x CO       | ONTROL REG        | ISTER 1          |                 |              |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------------|-----------------|--------------|--|--|--|--|

| U-0          | U-0                                                                                                                                                    | R/W-0                                                                                                                           | R/W-0              | R/W-0             | R/W-0            | U-0             | U-0          |  |  |  |  |

| _            |                                                                                                                                                        | ICSIDL                                                                                                                          | ICTSEL2            | ICTSEL1           | ICTSEL0          | —               | _            |  |  |  |  |

| bit 15       |                                                                                                                                                        | •                                                                                                                               |                    |                   |                  |                 | bit          |  |  |  |  |

| U-0          | R/W-0                                                                                                                                                  | R/W-0                                                                                                                           | R-0, HC, HS        | R-0, HC, HS       | R/W-0            | R/W-0           | R/W-0        |  |  |  |  |

| _            | ICI1                                                                                                                                                   | ICI0                                                                                                                            | ICOV               | ICBNE             | ICM2             | ICM1            | ICM0         |  |  |  |  |

| bit 7        |                                                                                                                                                        |                                                                                                                                 |                    |                   |                  |                 | bit          |  |  |  |  |

| Legend:      |                                                                                                                                                        | HC = Hardwa                                                                                                                     | re Clearable bit   | HS = Hardwar      | re Settable bit  |                 |              |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                 | W = Writable                                                                                                                    | bit                | U = Unimplem      | nented bit, read | <b>l as</b> '0' |              |  |  |  |  |

| -n = Value a | t POR                                                                                                                                                  | '1' = Bit is set                                                                                                                |                    | '0' = Bit is clea | ared             | x = Bit is un   | known        |  |  |  |  |

| bit 15-14    | Unimplemen                                                                                                                                             | ted: Read as '                                                                                                                  | 0'                 |                   |                  |                 |              |  |  |  |  |

| bit 13       | -                                                                                                                                                      |                                                                                                                                 | p in Idle Mode C   | control bit       |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | -                                                                                                                               | t in CPU Idle mod  |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | -                                                                                                                               | tinue to operate   |                   | de               |                 |              |  |  |  |  |

| bit 12-10    |                                                                                                                                                        |                                                                                                                                 | e x Timer Select   |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                      |                    |                   |                  |                 |              |  |  |  |  |

|              | 110 = Reserved                                                                                                                                         |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

|              | 101 = Reserved                                                                                                                                         |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

|              | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                     |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

|              | 011 = 130LK is the clock source of the ICx                                                                                                             |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        |                                                                                                                                 | ource of the ICx   |                   |                  |                 |              |  |  |  |  |

| bit 9-7      |                                                                                                                                                        | ted: Read as '                                                                                                                  |                    |                   |                  |                 |              |  |  |  |  |

| bit 6-5      | ICI<1:0>: Nur                                                                                                                                          | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                        |                    |                   |                  |                 |              |  |  |  |  |

|              | 11 = Interrupt                                                                                                                                         | t on every four                                                                                                                 | th capture event   |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | 10 = Interrupt on every third capture event                                                                                     |                    |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | 01 = Interrupt on every second capture event                                                                                    |                    |                   |                  |                 |              |  |  |  |  |

|              | -                                                                                                                                                      | 00 = Interrupt on every capture event                                                                                           |                    |                   |                  |                 |              |  |  |  |  |

| bit 4        | -                                                                                                                                                      | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                                      |                    |                   |                  |                 |              |  |  |  |  |

|              | <ul> <li>1 = Input Capture x buffer overflow has occurred</li> <li>0 = Input Capture x buffer overflow has not occurred</li> </ul>                     |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

| bit 3        |                                                                                                                                                        | -                                                                                                                               |                    |                   | nlv)             |                 |              |  |  |  |  |

|              | ICBNE: Input Capture x Buffer Not Empty Status bit (read-only)<br>1 = Input Capture x buffer is not empty, at least one more capture value can be read |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

|              | 0 = Input Capture x buffer is empty                                                                                                                    |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

| bit 2-0      | ICM<2:0>: In                                                                                                                                           | put Capture x                                                                                                                   | Mode Select bits   |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        |                                                                                                                                 | tions as an inter  |                   | CPU Sleep an     | d Idle modes    | (rising edg  |  |  |  |  |

|              |                                                                                                                                                        | detect only, all other control bits are not applicable)                                                                         |                    |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        | <ul><li>110 = Unused (module is disabled)</li><li>101 = Capture mode, every 16th rising edge (Prescaler Capture mode)</li></ul> |                    |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        |                                                                                                                                 | / 16th rising edge |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        |                                                                                                                                 | / rising edge (Sir |                   |                  |                 |              |  |  |  |  |

|              |                                                                                                                                                        |                                                                                                                                 | / falling edge (Si |                   |                  |                 |              |  |  |  |  |

|              | 001 = Captur                                                                                                                                           | re mode, every                                                                                                                  | edge, rising and   |                   |                  | CI<1:0>) is not | t used in th |  |  |  |  |

|              | mode)<br>000 = Input Capture x module is turned off                                                                                                    |                                                                                                                                 |                    |                   |                  |                 |              |  |  |  |  |

000 = Input Capture x module is turned off

NOTES:

### 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EVXXXGM00X/10X device family offers two SPI modules on a single device, SPI1 and SPI2, that are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of this module, but results in a lower maximum speed. See **Section 30.0 "Electrical Characteristics"** for more information.

The SPIx serial interface consists of the following four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

**Note:** All of the 4 pins of the SPIx serial interface must be configured as digital in the ANSELx registers.

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5   | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>               |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|         | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul> |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|         | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive<br/>FIFO)</li> </ul>                                            |

|         | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                             |

|         | 1 = Receive buffer has overflowed                                                                                                                                           |

|         | 0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) resets the receive buffer and the UxRSR to the empty state         |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                  |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/                                                                                 |

PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

### 24.3 ADC Control Registers

#### REGISTER 24-1: ADxCON1: ADCx CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|--------|---------|-----|-------|-------|-------|

| ADON   | —   | ADSIDL | ADDMABM | —   | AD12B | FORM1 | FORM0 |

| bit 15 |     |        |         |     |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0, HC, HS | R/C-0, HC, HS       |

|-------|-------|-------|-------|--------|-------|---------------|---------------------|

| SSRC2 | SSRC1 | SSRC0 | SSRCG | SIMSAM | ASAM  | SAMP          | DONE <sup>(1)</sup> |

| bit 7 |       |       |       | •      |       |               | bit 0               |

| Legend: C = Clearable bit |                  | U = Unimplemented bit, read as '0' |                             |  |  |  |

|---------------------------|------------------|------------------------------------|-----------------------------|--|--|--|

| R = Readable bit          | W = Writable bit | HS = Hardware Settable bit         | HC = Hardware Clearable bit |  |  |  |

| -n = Value at POR         | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown          |  |  |  |

| bit 15  | ADON: ADCx Operating Mode bit                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADCx module is operating                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 0 = ADCx is off                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 13  | ADSIDL: ADCx Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                                   |

| bit 12  | ADDMABM: ADCx DMA Buffer Build Mode bit                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = DMA buffers are written in the order of conversion; the module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer</li> <li>0 = DMA buffers are written in Scatter/Gather mode; the module provides a Scatter/Gather mode address to the DMA channel based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 10  | AD12B: ADCx 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                                                                                                                                                                                                               |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                                                                                                                                                                                                                           |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                                                                                                                                                                                                                           |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                                                                                                                                                                                                            |

|         | For 10-Bit Operation:                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>)                                                                                                                                                                                                                                                                                                                                      |

|         | 10 = Fractional (Dout = dddd dddd dd00 0000)<br>01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)                                                                                                                                                                                                                                                                                         |

|         | $00 = \text{Integer}(\text{DOUT} = 0.000 \ 0.00 \text{d} \text{d} \text{d} \text{d} \text{d} \text{d} \text{d} \text{d}$                                                                                                                                                                                                                                                                                      |

|         | For 12-Bit Operation:                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                                                                     |

|         | 10 = Fractional (Dout = dddd dddd dddd 0000)                                                                                                                                                                                                                                                                                                                                                                  |

|         | 01 = Signed integer (Dout = ssss sddd dddd dddd, where s = .NOT.d<11>)<br>00 = Integer (Dout = 0000 dddd dddd dddd)                                                                                                                                                                                                                                                                                           |

|         |                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |                                                                                                                                                                                                                                                                                                                                                                                                               |

| REGISTER                | 24-2: ADx                                                                                                                                                                                      | CON2: ADCx (         | CONTROL RI      | EGISTER 2         |                     |                 |           |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|-------------------|---------------------|-----------------|-----------|--|--|--|

| R/W-0                   | R/W-0                                                                                                                                                                                          | R/W-0                | U-0             | U-0               | R/W-0               | R/W-0           | R/W-0     |  |  |  |

| VCFG2 <sup>(1)</sup>    | VCFG1 <sup>(1)</sup>                                                                                                                                                                           | VCFG0 <sup>(1)</sup> | —               | —                 | CSCNA               | CHPS1           | CHPS0     |  |  |  |

| bit 15                  |                                                                                                                                                                                                |                      |                 |                   |                     |                 | bit       |  |  |  |

| R-0                     | R/W-0                                                                                                                                                                                          | R/W-0                | R/W-0           | R/W-0             | R/W-0               | R/W-0           | R/W-0     |  |  |  |

| BUFS                    | SMPI4                                                                                                                                                                                          | SMPI3                | SMPI2           | SMPI1             | SMPI0               | BUFM            | ALTS      |  |  |  |

| bit 7                   |                                                                                                                                                                                                |                      | 0111112         |                   |                     | Dor m           | bit       |  |  |  |

| <u> </u>                |                                                                                                                                                                                                |                      |                 |                   |                     |                 |           |  |  |  |

| Legend:<br>R = Readable | , hit                                                                                                                                                                                          | W = Writable I       | sit             | II – Unimplor     | monted bit read     |                 |           |  |  |  |

| -n = Value at           |                                                                                                                                                                                                | '1' = Bit is set     | JIL             | '0' = Bit is cle  | nented bit, read    | x = Bit is unkr |           |  |  |  |

|                         | PUR                                                                                                                                                                                            | I = DILIS SEL        |                 |                   | areu                | X = DILIS UNKI  | IOWII     |  |  |  |

| bit 15-13               | VCFG<2:0>                                                                                                                                                                                      | . Converter Volta    | ge Reference    | Configuration I   | bits <sup>(1)</sup> |                 |           |  |  |  |

|                         | Value                                                                                                                                                                                          | VREFH                | VREFL           |                   |                     |                 |           |  |  |  |

|                         | xxx                                                                                                                                                                                            | AVdd                 | AVss            |                   |                     |                 |           |  |  |  |

| bit 12-11               | Unimpleme                                                                                                                                                                                      | ented: Read as '0    | ,               |                   |                     |                 |           |  |  |  |

| bit 10                  | CSCNA: Inp                                                                                                                                                                                     | out Scan Select b    | it              |                   |                     |                 |           |  |  |  |

|                         |                                                                                                                                                                                                | nputs for CH0+ d     | uring Sample N  | /UX A             |                     |                 |           |  |  |  |

|                         | 0 = Does no                                                                                                                                                                                    | ot scan inputs       |                 |                   |                     |                 |           |  |  |  |

| bit 9-8                 | CHPS<1:0>: Channel Select bits                                                                                                                                                                 |                      |                 |                   |                     |                 |           |  |  |  |

|                         | In 12-Bit Mode (AD21B = 1), CHPS<1:0> bits are Unimplemented and are Read as '0':                                                                                                              |                      |                 |                   |                     |                 |           |  |  |  |

|                         | 1x = Converts CH0, CH1, CH2 and CH3<br>01 = Converts CH0 and CH1                                                                                                                               |                      |                 |                   |                     |                 |           |  |  |  |

|                         | 01 = Conve                                                                                                                                                                                     |                      |                 |                   |                     |                 |           |  |  |  |

| bit 7                   | BUFS: Buffer Fill Status bit (only valid when BUFM = 1)                                                                                                                                        |                      |                 |                   |                     |                 |           |  |  |  |

|                         | 1 = ADCx is currently filling the second half of the buffer; the user application should access data in the                                                                                    |                      |                 |                   |                     |                 |           |  |  |  |

|                         | first half of the buffer                                                                                                                                                                       |                      |                 |                   |                     |                 |           |  |  |  |

|                         | 0 = ADCx is currently filling the first half of the buffer; the user application should access data in th                                                                                      |                      |                 |                   |                     |                 |           |  |  |  |

|                         |                                                                                                                                                                                                | half of the buffer   |                 |                   |                     |                 |           |  |  |  |

| bit 6-2                 |                                                                                                                                                                                                | Increment Rate       | bits            |                   |                     |                 |           |  |  |  |

|                         | $\frac{\text{When ADDMAEN} = 0}{11117}$                                                                                                                                                        |                      |                 |                   |                     |                 |           |  |  |  |

|                         | x1111 = Generates interrupt after completion of every 16th sample/conversion operation<br>x1110 = Generates interrupt after completion of every 15th sample/conversion operation               |                      |                 |                   |                     |                 |           |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                 |                   |                     |                 |           |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                 |                   |                     |                 |           |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                 |                   |                     |                 |           |  |  |  |

|                         | x0001 = Generates interrupt after completion of every 2nd sample/conversion operation                                                                                                          |                      |                 |                   |                     |                 |           |  |  |  |

|                         | x0000 = Generates interrupt after completion of every sample/conversion operation<br>When ADDMAEN = 1:                                                                                         |                      |                 |                   |                     |                 |           |  |  |  |

|                         | $\frac{1}{11111}$ = Increments the DMA address after completion of every 32nd sample/conversion operation                                                                                      |                      |                 |                   |                     |                 |           |  |  |  |

|                         | 11111 = Increments the DMA address after completion of every 32nd sample/conversion operation<br>11110 = Increments the DMA address after completion of every 31st sample/conversion operation |                      |                 |                   |                     |                 |           |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                 |                   | -                   |                 |           |  |  |  |

|                         | •                                                                                                                                                                                              |                      |                 |                   |                     |                 |           |  |  |  |

|                         | •<br>00001 = lpc                                                                                                                                                                               | crements the DM      | A address after | completion of     | every 2nd sam       | nle/conversion  | operation |  |  |  |

|                         |                                                                                                                                                                                                | crements the DM      |                 |                   |                     |                 |           |  |  |  |

| Note 1. TL              |                                                                                                                                                                                                | H Input is connec    | tod to AVpp     |                   | put in passa-t-     | d to AV/aa      |           |  |  |  |

| NOLE I: IN              |                                                                                                                                                                                                | ·□ πουπis connec     | ieu iu aviju ar | IU IIIE VREEL III | IOULIS CONNECTE     | UIUAVSS.        |           |  |  |  |

#### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2

**Note 1:** The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

# dsPIC33EVXXXGM00X/10X FAMILY

#### **FIGURE 30-2: EXTERNAL CLOCK TIMING** Q1 Q2 Q3 Q4 Q1 Q2 ı, Q3 Q4 OSC1 **OS20** OS30 **OS30** 0531 0531 **OS25** CLKO **OS41** OS40

|              |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ\text{C} \le \text{Ta} \le +85^\circ\text{C} \mbox{ for Industrial} \\ -40^\circ\text{C} \le \text{Ta} \le +125^\circ\text{C} \mbox{ for Extended} \end{array}$ |                     |              |            |                               |  |

|--------------|---------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------------|-------------------------------|--|

| Param<br>No. | Sym           | Characteristic                                                                     | Min.                                                                                                                                                                                                                                                                                                                | Тур. <sup>(1)</sup> | Max.         | Units      | Conditions                    |  |

| OS10         | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                                                                                                                                  | _                   | 40           | MHz        | EC                            |  |

|              |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                                                                                                                                                                                           | _                   | 10<br>25     | MHz<br>MHz | XT<br>HS                      |  |

| OS20         | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                                                                                                                                                                                                |                     | DC           | ns         | TA = +125°C                   |  |

| OS25         | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                                                                                                                                                                                                                                                                                  |                     | DC           | ns         | TA = +125°C                   |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                                                                                                                                                                                        | —                   | 0.625 x Tosc | ns         | EC                            |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                                                                                                                                                                                                                                                                                   | —                   | 20           | ns         | EC                            |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | —                                                                                                                                                                                                                                                                                                                   | 5.2                 | —            | ns         |                               |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      |                                                                                                                                                                                                                                                                                                                     | 5.2                 |              | ns         |                               |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —                                                                                                                                                                                                                                                                                                                   | 12                  | _            | mA/V       | HS, VDD = 5.0V,<br>TA = +25°C |  |

|              |               |                                                                                    | —                                                                                                                                                                                                                                                                                                                   | 6                   | —            | mA/V       | XT, VDD = 5.0V,<br>TA = +25°C |  |

#### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

4: This parameter is characterized but not tested in manufacturing.

# TABLE 30-44:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS