Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XEI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 36x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm106-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

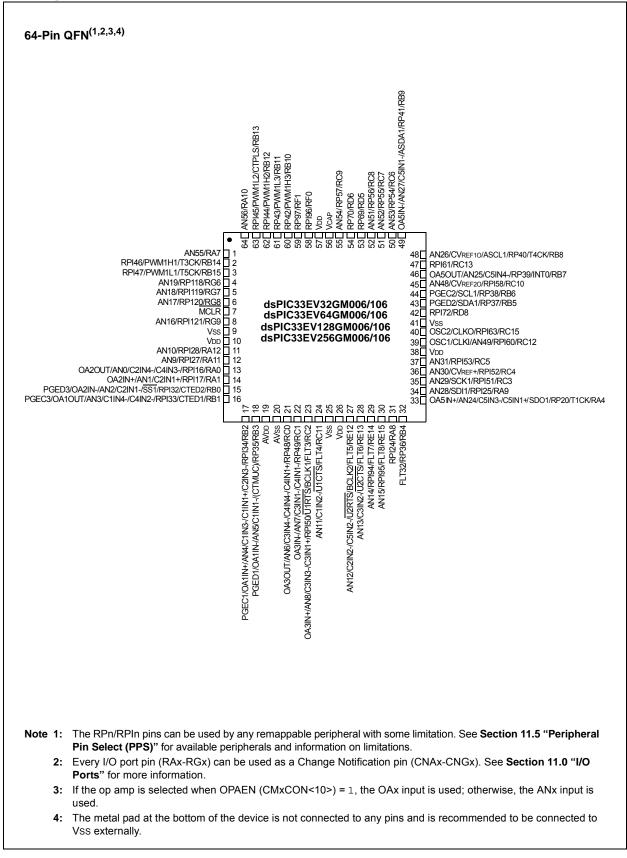

#### Pin Diagrams (Continued)

## TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                                                                                                                                                                                                                                                                                                           | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10       | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 0    | All<br>Resets |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|---------|---------|--------------|-------|----------|------------|--------------|--------|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|

| OC1CON1     | 0900  | _                                                                                                                                                                                                                                                                                                                                                | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     | —        | ENFLTA     | _            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1                                                                                                                                                                                                                                                                                                                                                                                                              | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                                                                                                                                                                                                                                                                                                                            | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1                                                                                                                                                                                                                                                                                                                                                                                                          | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Ou    | tput Con | npare 1 Se | condary Re   | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC1R        | 0906  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC1TMR      | 0908  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC2CON1     | 090A  | -       OCSIDL       OCTSEL2       OCTSEL1       OCTSEL0       -       ENFLTA       -       -       OCFLTA       TRIGMODE       OCM2       OCM1       OCM0         FLTMD       FLTOUT       FLTTRIEN       OCINV       -       -       OC32       OCTRIG       TRIGSTAT       OCTRIS       SYNCSEL4       SYNCSEL2       SYNCSEL1       SYNCSEL0 |        |            |         |         |              |       |          |            | 0000         |        |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          |               |

| OC2CON2     | 090C  | FLTMD                                                                                                                                                                                                                                                                                                                                            | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1                                                                                                                                                                                                                                                                                                                                                                                                          | SYNCSEL0 | 000C          |

| OC2RS       | 090E  | Output Compare 2 Secondary Register                                                                                                                                                                                                                                                                                                              |        |            |         |         |              |       |          |            |              |        | xxxx     |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          |               |

| OC2R        | 0910  | Output Compare 2 Register                                                                                                                                                                                                                                                                                                                        |        |            |         |         |              |       |          |            |              | xxxx   |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          |               |

| OC2TMR      | 0912  | Output Compare 2 Timer Value Register                                                                                                                                                                                                                                                                                                            |        |            |         |         |              |       |          |            |              | xxxx   |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          |               |

| OC3CON1     | 0914  | _                                                                                                                                                                                                                                                                                                                                                | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1                                                                                                                                                                                                                                                                                                                                                                                                              | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                                                                                                                                                                                                                                                                                                                            | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | OCM2     OCM1     OCM0       SYNCSEL2     SYNCSEL1     SYNCSEL0       OCM2     OCM1     OCM0       OCM2     OCM1     OCM0 |          | 000C          |

| OC3RS       | 0918  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Ou    | tput Con | npare 3 Se | condary Re   | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC3R        | 091A  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC3TMR      | 091C  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC4CON1     | 091E  | _                                                                                                                                                                                                                                                                                                                                                | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1                                                                                                                                                                                                                                                                                                                                                                                                              | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                                                                                                                                                                                                                                                                                                                            | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1                                                                                                                                                                                                                                                                                                                                                                                                          | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Ou    | tput Con | npare 4 Se | condary Reg  | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC4R        | 0924  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              |       | Outpu    | ut Compare | e 4 Register |        |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| OC4TMR      | 0926  |                                                                                                                                                                                                                                                                                                                                                  |        |            |         |         |              | Out   | put Com  | pare 4 Tin | ner Value Re | gister |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | xxxx          |

| Logondu     |       |                                                                                                                                                                                                                                                                                                                                                  | -      | ot: – unim |         | 1 /-1   | <b>-</b> · · |       |          |            |              |        |          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                   |          | <i>.</i>      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-41: PORTF REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 Bit ( | All<br>Resets |

|-------------|-------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|---------------|

| TRISF       | 0E64  | _      | —       | —      | —      | —      | —      | —     | —     | _     | —     | —     | —     | —     | —     | TRISF<1:0>  | 0003          |

| PORTF       | 0E66  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | RF<1:0>     | xxxx          |

| LATF        | 0E68  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | LATF<1:0>   | xxxx          |

| ODCF        | 0E6A  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | ODCF<1:0>   | 0000          |

| CNENF       | 0E6C  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | CNIEF<1:0>  | 0000          |

| CNPUF       | 0E6E  | _      | _       | _      | _      | —      | _      | _     | _     | —     | _     | —     | _     | _     | _     | CNPUF<1:0>  | 0000          |

| CNPDF       | 0E70  | _      | _       | _      | _      | —      | _      | _     | _     | _     | _     | —     | _     | _     | _     | CNPDF<1:0>  | 0000          |

| Lawsurds    |       |        | n Decet |        |        |        |        |       |       |       |       |       |       |       |       |             |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-42: PORTG REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG       | 0E78  | _      | _      |        | —      |        | —      |         | TRISC | 6<9:6> |       | —     | _     |       | —     | —     | —     | 03C0          |

| PORTG       | 0E7A  |        | _      | _      | _      | _      | _      | RG<9:6> |       | _      | _     | _     | _     | _     | _     | xxxx  |       |               |

| LATG        | 0E7C  |        | _      | _      | _      | _      | _      |         | LATG  | <9:6>  |       | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG        | 0E7E  |        | _      | _      | _      | _      | _      |         | ODCO  | i<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG       | 0E80  |        | _      | _      | _      | _      | _      |         | CNIEC | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG       | 0E82  |        | _      | _      | _      | _      | _      |         | CNPU  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG       | 0E84  | _      | _      |        | —      |        | —      |         | CNPD  | G<9:6> |       | —     | -     | _     | _     | —     | _     | 0000          |

| ANSELG      | 0E86  | _      | _      |        | -      |        | -      |         | ANSG  | <9:6>  |       | -     | _     | _     | —     | _     |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| _       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | U1RXI | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>l as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

bit 7-0 U1RXR<7:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 • • • • • • • • •

```

00000000 = Input tied to Vss

```

#### REGISTER 11-9: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0             | U-0    | U-0              | U-0   | U-0                                | U-0   | U-0                | U-0   |  |  |  |

|-----------------|--------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|--|

| _               | _      | —                |       | _                                  | _     | _                  | _     |  |  |  |

| bit 15          | -<br>- |                  |       |                                    |       |                    | bit 8 |  |  |  |

| R/W-0           | R/W-0  | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |  |

|                 |        |                  | U2R>  | (R<7:0>                            |       |                    |       |  |  |  |

| bit 7           |        |                  |       |                                    |       |                    | bit 0 |  |  |  |

| Legend:         |        |                  |       |                                    |       |                    |       |  |  |  |

| R = Readable    | bit    | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |

| -n = Value at F | POR    | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |  |  |

| • • • • • • • • • • • • • • • • • • • •                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>U2RXR&lt;7:0&gt;:</b> Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

| 10110101 = Input tied to RPI181                                                                                                         |

| •                                                                                                                                       |

| •                                                                                                                                       |

| •                                                                                                                                       |

| 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

|                                                                                                                                         |

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCK2R6                                            | SCK2R5                                                                           | SCK2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SCK2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCK2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCK2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCK2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| R/W-0                                             | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SDI2R6                                            | SDI2R5                                                                           | SDI2R4                                                                                                                                                                                                                                                                                                                                                                                                        | SDI2R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI2R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SDI2R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| bit                                               | W = Writable                                                                     | bit                                                                                                                                                                                                                                                                                                                                                                                                           | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>d as</b> '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| POR                                               | '1' = Bit is set                                                                 | :                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| •<br>•<br>000000001 =<br>00000000 =               | Input tied to Cl                                                                 | MP1<br>SS                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |