Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev64gm106t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

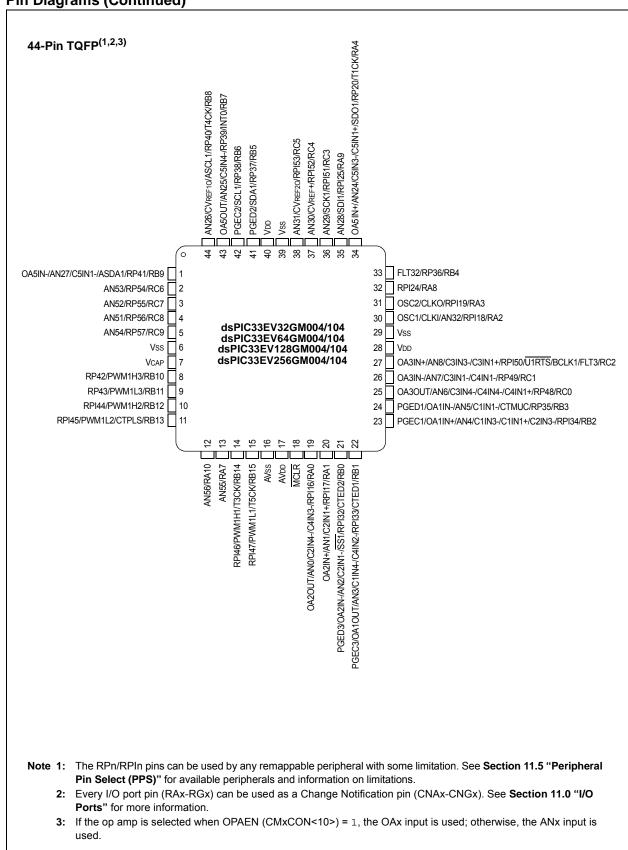

### Pin Diagrams (Continued)

TABLE 4-23: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13   | Bit 12  | Bit 11 | Bit 10                 | Bit 9                     | Bit 8                  | Bit 7   | Bit 6                 | Bit 5      | Bit 4    | Bit 3 | Bit 2                 | Bit 1       | Bit 0    | All<br>Resets |

|-------------|-------|--------|---------|----------|---------|--------|------------------------|---------------------------|------------------------|---------|-----------------------|------------|----------|-------|-----------------------|-------------|----------|---------------|

| IFS0        | 0800  | NVMIF  | DMA1IF  | AD1IF    | U1TXIF  | U1RXIF | SPI1IF                 | SPI1EIF                   | T3IF                   | T2IF    | OC2IF                 | IC2IF      | DMA0IF   | T1IF  | OC1IF                 | IC1IF       | INT0IF   | 0000          |

| IFS1        | 0802  | U2TXIF | U2RXIF  | INT2IF   | T5IF    | T4IF   | OC4IF                  | OC3IF                     | DMA2IF                 | _       | _                     | _          | INT1IF   | CNIF  | CMPIF                 | MI2C1IF     | SI2C1IF  | 0000          |

| IFS2        | 0804  | _      | _       | _        | _       | _      | _                      | _                         | _                      | _       | IC4IF                 | IC3IF      | DMA3IF   | C1IF  | C1RXIF <sup>(1)</sup> | SPI2IF      | SPI2EIF  | 0000          |

| IFS3        | 0806  | _      | _       | _        | _       | _      | _                      | PSEMIF                    | _                      | _       | _                     | _          | _        | _     | _                     | _           | _        | 0000          |

| IFS4        | 0808  | _      | -       | CTMUIF   |         | _      | _                      | _                         | _                      | -       | C1TXIF <sup>(1)</sup> | _          | _        | _     | U2EIF                 | U1EIF       | -        | 0000          |

| IFS5        | 080A  | PWM2IF | PWM1IF  | -        | _       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     | _                     | _           | _        | 0000          |

| IFS6        | 080C  | _      | -       | -        | ı       | -      | _                      | ı                         | ı                      | ı       | _                     | _          | _        | -     | _                     | -           | PWM3IF   | 0000          |

| IFS8        | 0810  | _      | ICDIF   | -        | ı       | -      | _                      | ı                         | ı                      | ı       | _                     | _          | _        | -     | _                     | -           | ı        | 0000          |

| IFS10       | 0814  | _      |         | I2C1BCIF |         |        | _                      | ı                         | ı                      | ı       | _                     | _          |          | ı     | _                     | ı           | ı        | 0000          |

| IFS11       | 0816  | _      | _       | _        | _       | _      | ECCSBEIF               | SENT2IF                   | SENT2EIF               | SENT1IF | SENT1EIF              | _          | _        | _     | _                     | _           | _        | 0000          |

| IEC0        | 0820  | NVMIE  | DMA1IE  | AD1IE    | U1TXIE  | U1RXIE | SPI1IE                 | SPI1EIE                   | T3IE                   | T2IE    | OC2IE                 | IC2IE      | DMA0IE   | T1IE  | OC1IE                 | IC1IE       | INT0IE   | 0000          |

| IEC1        | 0822  | U2TXIE | U2RXIE  | INT2IE   | T5IE    | T4IE   | OC4IE                  | OC3IE                     | DMA2IE                 | _       | _                     | _          | INT1IE   | CNIE  | CMPIE                 | MI2C1IE     | SI2C1IE  | 0000          |

| IEC2        | 0824  | _      | _       | _        | _       | _      | _                      | _                         | _                      | _       | IC4IE                 | IC3IE      | DMA3IE   | C1IE  | C1RXIE <sup>(1)</sup> | SPI2IE      | SPI2EIE  | 0000          |

| IEC3        | 0826  | _      | _       | _        | _       | _      | _                      | PSEMIE                    | _                      | _       | _                     | _          | _        | _     | _                     | _           |          | 0000          |

| IEC4        | 0828  | _      | _       | CTMUIE   | _       | _      | _                      | _                         | _                      | _       | C1TXIE <sup>(1)</sup> | _          | _        | _     | U2EIE                 | U1EIE       |          | 0000          |

| IEC5        | 082A  | PWM2IE | PWM1IE  | _        | -       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     | _                     | _           | -        | 0000          |

| IEC6        | 082C  | _      | _       | _        | _       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     | _                     | _           | PWM3IE   | 0000          |

| IEC8        | 0830  | _      | ICDIE   | _        | _       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     | _                     | _           | _        | 0000          |

| IEC10       | 0834  | _      | _       | I2C1BCIE | _       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     | _                     | _           | _        | 0000          |

| IEC11       | 0836  | _      | _       | _        | _       | _      | ECCSBEIE               | SENT2IE                   | SENT2EIE               | SENT1IE | SENT1EIE              | _          | _        | _     | _                     | _           | -        | 0000          |

| IPC0        | 0840  |        | T1IP2   | T1IP1    | T1IP0   |        | OC1IP2                 | OC1IP1                    | OC1IP0                 |         | IC1IP2                | IC1IP1     | IC1IP0   |       | INT0IP2               | INT0IP1     | INT0IP0  | 4444          |

| IPC1        | 0842  |        | T2IP2   | T2IP1    | T2IP0   |        | OC2IP2                 | OC2IP1                    | OC2IP0                 |         | IC2IP2                | IC2IP1     | IC2IP0   |       | DMA0IP2               | DMA0IP1     | DMA0IP0  | 4444          |

| IPC2        | 0844  |        | U1RXIP2 | U1RXIP1  | U1RXIP0 |        | SPI1IP2                | SPI1IP1                   | SPI1IP0                |         | SPI1EIP2              | SPI1EIP1   | SPI1EIP0 |       | T3IP2                 | T3IP1       | T3IP0    | 4444          |

| IPC3        | 0846  |        | NVMIP2  | NVMIP1   | NVMIP0  |        | DMA1IP2                | DMA1IP1                   | DMA1IP0                |         | AD1IP2                | AD1IP1     | AD1IP0   |       | U1TXIP2               | U1TXIP1     | U1TXIP0  | 4444          |

| IPC4        | 0848  | _      | CNIP2   | CNIP1    | CNIP0   | _      | CMPIP2                 | CMPIP1                    | CMPIP0                 | _       | MI2C1IP2              | MI2C1IP1   | MI2C1IP0 | _     | SI2C1IP2              | SI2C1IP1    | SI2C1IP0 | 4444          |

| IPC5        | 084A  | _      | _       | _        | _       | _      | _                      | _                         | _                      | _       | _                     | _          | _        | _     |                       | INT1IP<2:0> |          | 0004          |

| IPC6        | 084C  | _      | T4IP2   | T4IP1    | T4IP0   | _      | OC4IP2                 | OC4IP1                    | OC4IP0                 | _       | OC3IP2                | OC3IP1     | OC3IP0   | _     | DMA2IP2               | DMA2IP1     | DMA2IP0  | 4444          |

| IPC7        | 084E  | _      | U2TXIP2 | U2TXIP1  | U2TXIP0 | _      | U2RXIP2                | U2RXIP1                   | U2RXIP0                | _       | INT2IP2               | INT2IP1    | INT2IP0  | _     | T5IP2                 | T5IP1       | T5IP0    | 4444          |

| IPC8        | 0850  | _      | C1IP2   | C1IP1    | C1IP0   | _      | C1RXIP2 <sup>(1)</sup> | C1RXIP1 <sup>(1)</sup>    | C1RXIP0 <sup>(1)</sup> | _       | SPI2IP2               | SPI2IP1    | SPI2IP0  | _     | SPI2EIP2              | SPI2EIP1    | SPI2EIP0 | 4444          |

| IPC9        | 0852  | _      | _       | _        | _       | _      | IC4IP2                 | IC4IP1                    | IC4IP0                 | _       | IC3IP2                | IC3IP1     | IC3IP0   | _     | DMA3IP2               | DMA3IP1     | DMA3IP0  | 0444          |

| IPC14       | 085C  | _      | _       |          |         | _      |                        |                           |                        |         |                       | PSEMIP<2:0 |          | _     | _                     | _           |          | 0040          |

| IPC16       | 0860  | _      | _       |          |         | _      | U2EIP2                 | U2EIP1                    | U2EIP0                 |         | U1EIP2                | U1EIP1     | U1EIP0   | _     | _                     | _           |          | 0440          |

| IPC17       | 0862  | _      | _       | _        | _       |        | (                      | C1TXIP<2:0> <sup>(1</sup> | )                      | _       | _                     | _          | _        | _     | _                     | _           | _        | 0400          |

**Legend:** — = unimplemented, read as '0' Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

DS70005144E-page 57

TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                    | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|-------------------------------------------|--------|----------|---------|---------|---------|-------|----------|------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1     | 0900  | _                                         | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | _        | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | ОСМ0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                     | FLTOUT | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                           |        |          |         |         |         | Ou    | tput Con | npare 1 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                                           |        |          |         |         |         |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                                           |        |          |         |         |         | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                                         | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | _        | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | ОСМ0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                     | FLTOUT | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                           |        |          |         |         |         | Ou    | tput Con | npare 2 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC2R        | 0910  | Output Compare 2 Register                 |        |          |         |         |         |       |          |            |              | xxxx   |          |          |          |          |          |               |

| OC2TMR      | 0912  |                                           |        |          |         |         |         | Out   | put Com  | pare 2 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC3CON1     | 0914  |                                           | -      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | _        | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                     | FLTOUT | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                           |        |          |         |         |         | Ou    | tput Con | npare 3 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                           |        |          |         |         |         |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                           |        |          |         |         |         | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  | _                                         | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | _        | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                     | FLTOUT | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  | Output Compare 4 Secondary Register       |        |          |         |         |         |       |          |            |              | xxxx   |          |          |          |          |          |               |

| OC4R        | 0924  | Output Compare 4 Register x:              |        |          |         |         |         |       |          |            | xxxx         |        |          |          |          |          |          |               |

| OC4TMR      | 0926  | Output Compare 4 Timer Value Register xxx |        |          |         |         |         |       |          |            | xxxx         |        |          |          |          |          |          |               |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

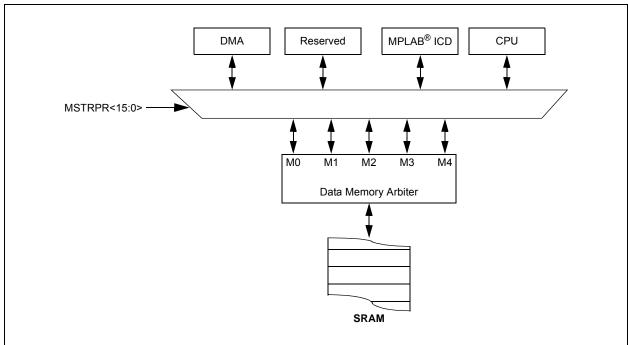

## 4.3.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the MPLAB<sup>®</sup> ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the MPLAB ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities

below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are listed in Table 4-44.

Figure 4-13 shows the arbiter architecture.

The bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

TABLE 4-44: DATA MEMORY BUS ARBITER PRIORITY

| Driority     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |           |  |  |  |  |  |

|--------------|-----------------------------------------|-----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020    |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA       |  |  |  |  |  |

| M1           | Reserved                                | CPU       |  |  |  |  |  |

| M2           | Reserved                                | Reserved  |  |  |  |  |  |

| M3           | DMA                                     | Reserved  |  |  |  |  |  |

| M4 (lowest)  | MPLAB <sup>®</sup> ICD                  | MPLAB ICD |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

FIGURE 4-13: ARBITER ARCHITECTURE

### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EVXXXGM00X/10X Product Families" section for the page sizes of each device.memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to era

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Table 30-13 in **Section 30.0 "Electrical Characteristics"** lists the typical erase and programming times.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. See Figure 4-1 to Figure 4-5 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

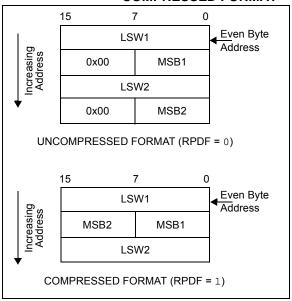

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

For more information on erasing and programming the Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

- Note 1: Before reprogramming either of the two words in a double-word pair, the user must erase the Flash memory page in which it is located.

- 2: Before reprogramming any word in a row, the user must erase the Flash memory page in which it is located.

FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual" for details and code examples on programming using RTSP.

### 7.3 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EVXXXGM00X/10X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

Note:

Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 7.4 Interrupt Control and Status Registers

dsPIC33EVXXXGM00X/10X family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- IFSx

- IECx

- IPCx

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from the INTCON1, INTCON2, INTCON3 and INTCON4 registers.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMT (Deadman Timer), DMA and  ${\tt DO}$  stack overflow status trap sources

The INTCON4 register contains the ECC Double-Bit Error (ECCDBE) and Software-Generated Hard Trap (SGHT) status bit.

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared through software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into Vector Number (VECNUM<7:0>) and Interrupt Priority Level bit (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 to Register 7-7.

#### **REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HS, SC           | R-0, HS, SC |

|-------|-----|-----|-----|-----|-----|-----------------------|-------------|

| _     | _   | _   | _   | _   | _   | ECCDBE <sup>(1)</sup> | SGHT        |

| bit 7 |     |     |     |     |     |                       | bit 0       |

| Legend:           | HS = Hardware Settable bit | SC = Software Clearable b          | it                 |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-2 Unimplemented: Read as '0'

**ECCDBE:** ECC Double-Bit Error Trap bit<sup>(1)</sup> bit 1

> 1 = ECC double-bit error trap has occurred 0 = ECC double-bit error trap has not occurred

bit 0

**SGHT:** Software-Generated Hard Trap Status bit

1 = Software-generated hard trap has occurred 0 = Software-generated hard trap has not occurred

**Note 1:** ECC double-bit error causes a generic hard trap.

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **4:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain outputs. This is controlled by the Open-Drain Control x register (ODCx) associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See Table 30-10 in **Section 30.0 "Electrical Characteristics"** for the maximum VIH specification of each pin.

## 11.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bits must be cleared.

The ANSELx register has a default value of 0xFFFF. Therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions table (see Table 1-1 in **Section 1.0 "Device Overview"**).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a  $\mathtt{NOP}$ , as shown in Example 11-1.

### 11.3 Input Change Notification (ICN)

The Input Change Notification function (ICN) of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pull-downs act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

Note: The pull-ups and pull-downs on ICN pins should always be disabled when the port pin is configured as a digital output.

## EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

|   | MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> |

|---|------|------------|---|-----------------------|

|   |      |            | ; | as inputs             |

|   | MOV  | W0, TRISB  | ; | and PORTB<7:0>        |

|   |      |            | ; | as outputs            |

|   | NOP  |            | ; | Delay 1 cycle         |

|   | BTSS | PORTB, #13 | ; | Next Instruction      |

| 1 |      |            |   |                       |

| IOTES: |  |  |  |  |

|--------|--|--|--|--|

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

### REGISTER 22-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0 | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   |

|--------|--------|-----|-----|-----|---------|---------|---------|

| _      | WAKFIL | _   | _   |     | SEG2PH2 | SEG2PH1 | SEG2PH0 |

| bit 15 |        |     |     |     |         |         | bit 8   |

| R/W-x    | R/W-x | R/W-x   | R/W-x   | R/W-x   | R/W-x  | R/W-x  | R/W-x  |

|----------|-------|---------|---------|---------|--------|--------|--------|

| SEG2PHTS | SAM   | SEG1PH2 | SEG1PH1 | SEG1PH0 | PRSEG2 | PRSEG1 | PRSEG0 |

| bit 7    |       |         |         |         |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14 WAKFIL: Select CAN Bus Line Filter for Wake-up bit

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 **Unimplemented:** Read as '0'

bit 10-8 **SEG2PH<2:0>:** Phase Segment 2 bits

111 = Length is 8 x TQ

•

000 = Length is 1 x TQ

bit 7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PH<2:0> bits or Information Processing Time (IPT), whichever is greater

bit 6 SAM: Sample of the CAN Bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Segment 1 bits

111 = Length is 8 x TQ

•

. . . .

000 = Length is  $1 \times TQ$

bit 2-0 **PRSEG<2:0>:** Propagation Time Segment bits

111 = Length is 8 x TQ

•

\_

000 = Length is  $1 \times TQ$

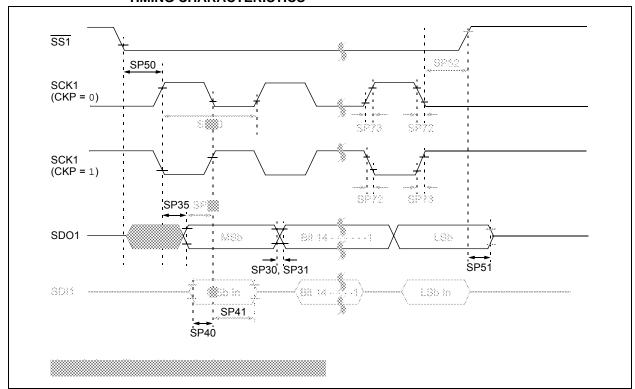

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

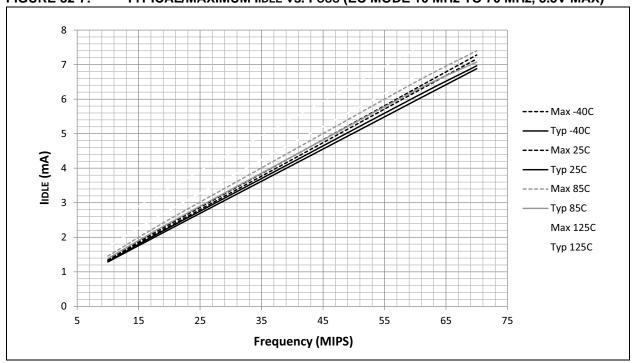

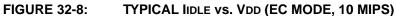

### 32.2 IIDLE

FIGURE 32-7: TYPICAL/MAXIMUM lidle vs. Fosc (EC MODE 10 MHz TO 70 MHz, 5.5V MAX)

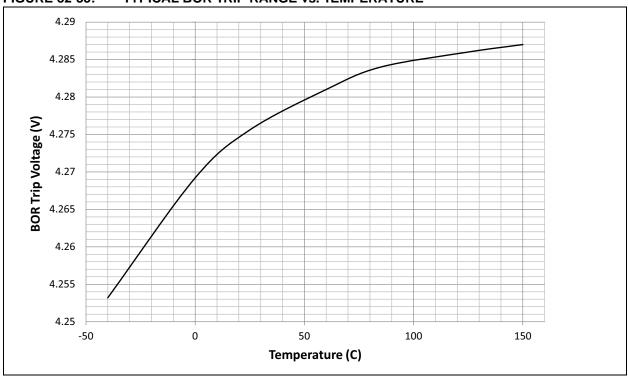

### 32.12 VBOR

FIGURE 32-35: TYPICAL BOR TRIP RANGE vs. TEMPERATURE

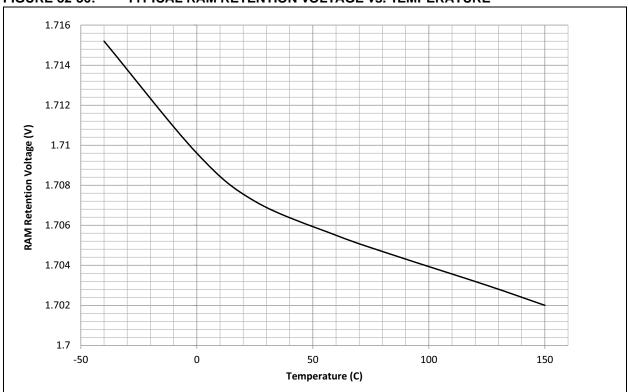

### 32.13 RAM Retention

FIGURE 32-36: TYPICAL RAM RETENTION VOLTAGE vs. TEMPERATURE

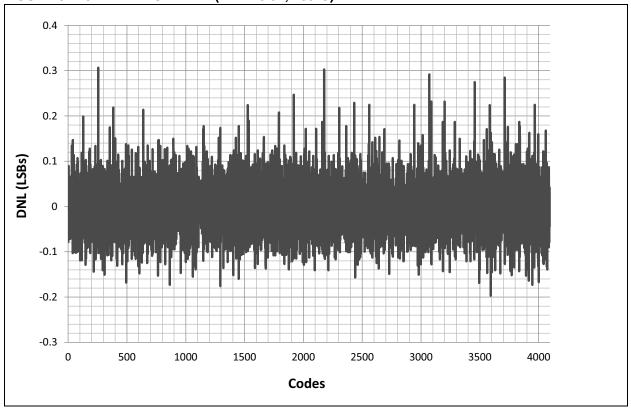

FIGURE 32-43: TYPICAL DNL (VDD = 5.5V, +85°C)

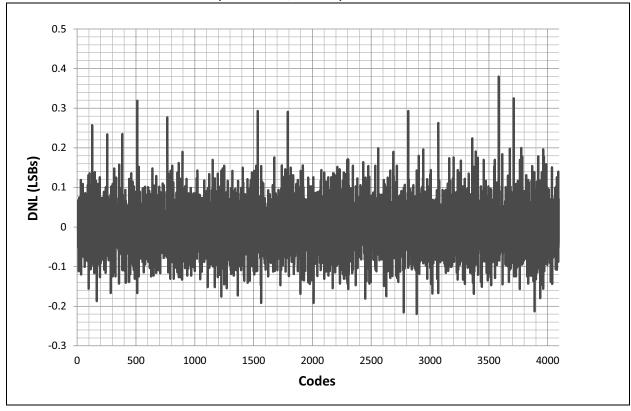

FIGURE 32-44: TYPICAL DNL (VDD = 5.5V, +125°C)

### 33.3 IDOZE

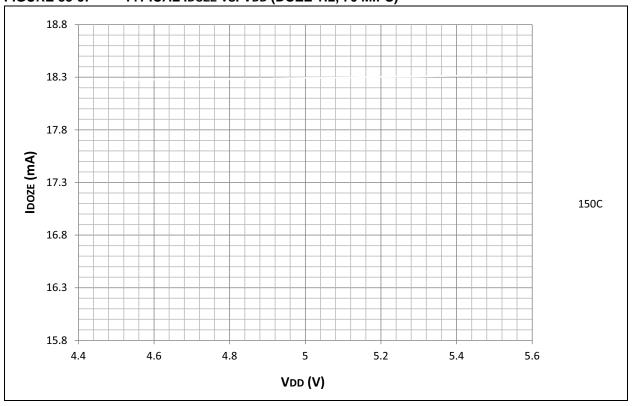

FIGURE 33-9: TYPICAL IDOZE vs. VDD (DOZE 1:2, 70 MIPS)

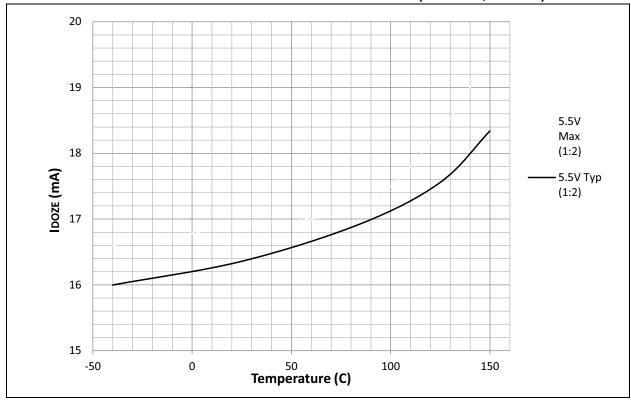

FIGURE 33-10: TYPICAL/MAXIMUM IDOZE vs. TEMPERATURE (DOZE 1:2, 70 MIPS)

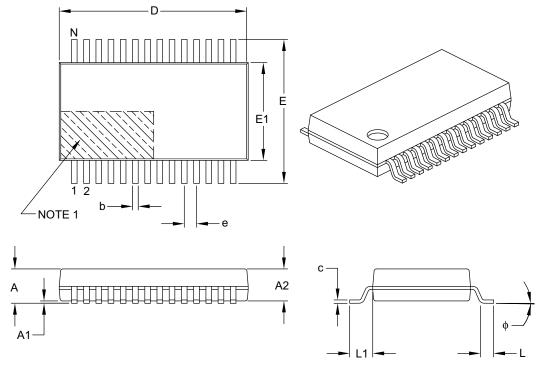

### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | MILLIMETERS | 3     |

|--------------------------|----------|------|-------------|-------|

| Dimensio                 | n Limits | MIN  | NOM         | MAX   |

| Number of Pins           | N        |      | 28          |       |

| Pitch                    | е        |      | 0.65 BSC    |       |

| Overall Height           | Α        | _    | -           | 2.00  |

| Molded Package Thickness | A2       | 1.65 | 1.75        | 1.85  |

| Standoff                 | A1       | 0.05 | -           | _     |

| Overall Width            | Е        | 7.40 | 7.80        | 8.20  |

| Molded Package Width     | E1       | 5.00 | 5.30        | 5.60  |

| Overall Length           | D        | 9.90 | 10.20       | 10.50 |

| Foot Length              | L        | 0.55 | 0.75        | 0.95  |

| Footprint                | L1       |      | 1.25 REF    | •     |

| Lead Thickness           | С        | 0.09 | _           | 0.25  |

| Foot Angle               | ф        | 0°   | 4°          | 8°    |

| Lead Width               | b        | 0.22 | _           | 0.38  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

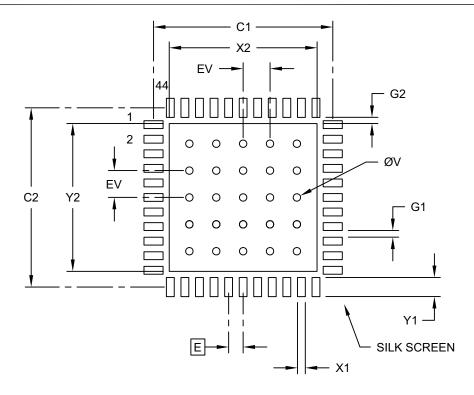

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

| Units                            |    | MILLIMETERS |      |      |

|----------------------------------|----|-------------|------|------|

| Dimension Limits                 |    | MIN         | NOM  | MAX  |

| Contact Pitch                    | Е  | 0.65 BSC    |      |      |

| Optional Center Pad Width        | X2 |             |      | 6.60 |

| Optional Center Pad Length       | Y2 |             |      | 6.60 |

| Contact Pad Spacing              | C1 |             | 8.00 |      |

| Contact Pad Spacing              | C2 |             | 8.00 |      |

| Contact Pad Width (X44)          | X1 |             |      | 0.35 |

| Contact Pad Length (X44)         | Y1 |             |      | 0.85 |

| Contact Pad to Contact Pad (X40) | G1 | 0.30        |      |      |

| Contact Pad to Center Pad (X44)  | G2 | 0.28        |      |      |

| Thermal Via Diameter             | V  |             | 0.33 |      |

| Thermal Via Pitch                | EV |             | 1.20 |      |

#### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M  $\,$

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

| E                                             |          | Instruction Addressing Modes                    | 74  |

|-----------------------------------------------|----------|-------------------------------------------------|-----|

| Electrical Characteristics                    | 341      | File Register Instructions                      |     |

| AC                                            |          | Fundamental Modes Supported                     | 75  |

| Equations                                     | 551, 400 | MAC Instructions                                | 75  |

| BRG Formula                                   | 220      | MCU Instructions                                | 74  |

| Device Operating Frequency                    |          | Move and Accumulator Instructions               | 75  |

| ,                                             |          | Other Instructions                              | 75  |

| Fosc Calculation                              |          | Instruction Set                                 |     |

| Frame Time Calculations                       |          | Overview                                        | 330 |

| FSCL Frequency                                |          | Summary                                         |     |

| Fvco Calculation                              |          | Symbols Used in Opcode                          |     |

| SYNCMIN and SYNCMAX Calculations              |          | Interfacing Program and Data Memory Spaces      |     |

| Tick Period Calculation                       |          | Inter-Integrated Circuit (I <sup>2</sup> C)     |     |

| Errata                                        | 11       | Baud Rate Generator                             |     |

| F                                             |          | Control Registers                               |     |

|                                               |          | Inter-Integrated Circuit. See I <sup>2</sup> C. | 23  |

| Flash Program Memory                          |          | Internal LPRC Oscillator                        |     |

| Control Registers                             | 85       |                                                 | 001 |

| Error Correcting Code (ECC)                   | 85       | Use with WDT                                    |     |

| Operations                                    | 84       | Internet Address                                | 493 |

| Resources                                     | 85       | Interrupt Controller                            |     |

| RTSP Operation                                | 84       | Control and Status Registers                    |     |

| Table Instructions                            | 83       | IECx                                            | 100 |

| Flexible Configuration                        | 317      | IFSx                                            | 100 |

| <b>3</b>                                      |          | INTCON1                                         | 100 |

| G                                             |          | INTCON2                                         | 100 |

| Getting Started with 16-Bit DSCs              | 17       | INTCON3                                         | 100 |

| Connection Requirements                       |          | INTCON4                                         | 100 |

| CPU Logic Filter Capacitor Connection (VCAI   |          | INTTREG                                         | 100 |

| Decoupling Capacitors                         |          | IPCx                                            | 100 |

| External Oscillator Pins                      |          | Reset Sequence                                  |     |

|                                               |          | Interrupt Vector Table (IVT)                    |     |

| ICSP Pins                                     |          | Details                                         |     |

| Master Clear (MCLR) Pin                       |          | Dotailo                                         |     |

| Oscillator Value Conditions on Device Start-u | •        | M                                               |     |

| Unused I/Os                                   | 19       | Memory Maps                                     |     |

| Н                                             |          | EDS                                             | 73  |

|                                               |          | Memory Organization                             |     |

| High Temperature                              | 404      | Microchip Internet Web Site                     | 491 |

| Thermal Operating Conditions                  |          | Modulo Addressing                               |     |

| High-Speed PWM                                |          | =                                               |     |

| Control Registers                             |          | Applicability Operation Example                 |     |

| Faults                                        |          |                                                 |     |

| Resources                                     |          | Start and End Address                           |     |

| High-Temperature Electrical Characteristics   | 403      | W Address Register Selection                    |     |

| Absolute Maximum Ratings                      | 403      | MPLAB PM3 Device Programmer                     |     |

| 1                                             |          | MPLAB REAL ICE In-Circuit Emulator System       | 339 |

| 1                                             |          | MPLAB X Integrated Development                  |     |

| I/O Ports                                     |          | Environment Software                            |     |

| Configuring Analog/Digital Port Pins          | 144      | MPLINK Object Linker/MPLIB Object Librarian     | 338 |

| Helpful Tips                                  | 151      | 0                                               |     |

| High-Voltage Detect (HVD)                     | 151      | 0                                               |     |

| Open-Drain Configuration                      |          | Op Amp/Comparator                               | 30′ |

| Parallel I/O (PIO)                            |          | Control Registers                               | 303 |

| Peripheral Pin Select (PPS)                   |          | Oscillator Configuration                        |     |

| Slew Rate Selection                           |          | Bit Values for Clock Selection                  |     |

| Write/Read Timing                             |          | CPU Clocking System                             | 124 |

| In-Circuit Debugger                           |          | Output Compare                                  |     |

| MPLAB ICD 3                                   |          | Control Registers                               |     |

|                                               |          | Control (Cognotoro                              |     |

| PICkit 3 Programmer                           |          | P                                               |     |

| In-Circuit Emulation                          |          | Packaging                                       | 46  |

| In-Circuit Serial Programming (ICSP)          |          | Details                                         |     |

| Input Capture                                 |          | Marking                                         |     |

| Control Registers                             |          | Peripheral Module Disable (PMD)                 |     |

| Input Change Notification (ICN)               | 144      | i chipricial Module Disable (FMD)               | 130 |

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support