Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LQFP                                                                   |

| Supplier Device Package    | 44-VQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51rc2-rltim |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 3. Pin Description for 40 - 44 Pin Packages (Continued)

|             | Pin Num | ber            |              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------|---------|----------------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic    | DIL     | LCC            | VQFP44 1.4   | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             |         |                |              | I/O   | CEX4: Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P1.0 - P1.7 |         |                |              | I/O   | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|             |         |                |              |       | When SPI is in master mode, MOSI outputs data to the slave peripheral. When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| XTAL1       | 19      | 21             | 15           | I     | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| XTAL2       | 18      | 20             | 14           | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P2.0 - P2.7 | 21 - 28 | 24 - 31        | 18 - 25      | 1/0   | Port 2: Port 2 is an 8 - bit bidirectional I/O port with internal pull - ups. Port 2 pins that have 1s written to them are pulled high by the internal pull - ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull - ups. Port 2 emits the high - order address byte during fetches from external program memory and during accesses to external data memory that use 16 - bit addresses (MOVX @DPTR). In this application, it uses strong internal pull - ups emitting 1s. During accesses to external data memory that use 8 - bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins receive the high order address bits during EPROM programming and verification:<br>P2.0 to P2.5 for 16 KB devices |  |  |  |

| P3.0 - P3.7 | 10 - 17 | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O   | <b>Port 3:</b> Port 3 is an 8 - bit bidirectional I/O port with internal pull - ups. Port 3 pins that have 1s written to them are pulled high by the internal pull - ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull - ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|             | 10      | 11             | 5            | I     | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|             | 11      | 13             | 7            | 0     | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|             | 12      | 14             | 8            | I     | INTO (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             | 13      | 15             | 9            | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             | 14      | 16             | 10           | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             | 15      | 17             | 11           | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             | 16      | 18             | 12           | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|             | 17      | 19             | 13           | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RST         | 9       | 10             | 4            | I/O   | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power - on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ALE/PROG    | 30      | 33             | 27           | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during Flash programming. ALE can be disabled by setting SFR's AUXR. 0 bit. With this bit set, ALE will be inactive during internal fetches.                                                                                                                                                                                                                                                   |  |  |  |

# Table 7. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                | 4                             | 3              | 2                                                  | 1    | 0            |

|---------------|-----------------|----------------------------------|-------------------------------|----------------|----------------------------------------------------|------|--------------|

| -             | -               | -                                | -                             | -              | -                                                  | -    | SPIX2        |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                               |                |                                                    |      |              |

| 7             | -               | Reserved                         |                               |                |                                                    |      |              |

| 6             | -               | Reserved                         |                               |                |                                                    |      |              |

| 5             | -               | Reserved                         |                               |                |                                                    |      |              |

| 4             | -               | Reserved                         |                               |                |                                                    |      |              |

| 3             | -               | Reserved                         |                               |                |                                                    |      |              |

| 2             | -               | Reserved                         |                               |                |                                                    |      |              |

| 1             | -               | Reserved                         |                               |                |                                                    |      |              |

| 0             | SPIX2           | this bit has no<br>Clear to sele | o effect).<br>ct 6 clock peri | ods per peripl | e CPU clock ><br>neral clock cyc<br>eral clock cyc | cle. | n X2 is low, |

Reset Value = XXXX XXX0b Not bit addressable

# Registers

## Table 10. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                                                                                                                                                                                                            | 4                                                                                                                                                                                                            | 3                                                             | 2              | 1            | 0  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|--------------|----|--|

| -             | -               | МО                                                                                                                                                                                                                           | -                                                                                                                                                                                                            | XRS1                                                          | XRS0           | EXTRAM       | AO |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                  |                                                                                                                                                                                                              |                                                               |                |              |    |  |

| 7             | -               | <b>Reserved</b><br>The value re                                                                                                                                                                                              | ad from this b                                                                                                                                                                                               | it is indetermir                                              | nate. Do not s | et this bit. |    |  |

| 6             | -               | <b>Reserved</b><br>The value re                                                                                                                                                                                              | ad from this b                                                                                                                                                                                               | it is indetermir                                              | nate. Do not s | et this bit. |    |  |

| 5             | МО              | periods (defa                                                                                                                                                                                                                | tretch MOVX (<br>ault).                                                                                                                                                                                      | control: the Rl                                               |                |              |    |  |

| 4             | -               | <b>Reserved</b><br>The value re                                                                                                                                                                                              | ad from this b                                                                                                                                                                                               | it is indetermir                                              | nate. Do not s | et this bit. |    |  |

| 3             | XRS1            | XRAM Size                                                                                                                                                                                                                    |                                                                                                                                                                                                              |                                                               |                |              |    |  |

| 2             | XRS0            | XRS1 2<br>0 0<br>0 1<br>1 0<br>1 1                                                                                                                                                                                           | ) 256<br>512<br>) 768                                                                                                                                                                                        | <u>M size</u><br>bytes (default)<br>bytes<br>bytes<br>4 bytes | 1              |              |    |  |

| 1             | EXTRAM          | EXTRAM bit<br>Cleared to access internal XRAM using movx @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte<br>(HSB), default setting, XRAM selected. |                                                                                                                                                                                                              |                                                               |                |              |    |  |

| 0             | AO              | Cleared, ALI<br>X2 mode is t                                                                                                                                                                                                 | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if<br>X2 mode is used). (default) Set, ALE is active only during a MOVX or MOVC<br>instruction is used. |                                                               |                |              |    |  |

Reset Value = XX0X 00'HSB. XRAM'0b (See Table 69) Not bit addressable

| Timer 2          | The Timer 2 in the T89C51RB2/RC2 is the standard C52 Timer 2.<br>It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 11) and T2MOD (Table 12) registers. Timer 2 operation is similar to Timer 0 and Timer 1.C/T2 selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                           |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Cap-<br>ture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                    |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Auto-Reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br>the Atmel C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as<br>an Up/down timer/counter as shown in Figure 8. In this mode the T2EX pin controls the<br>direction of count.                                                                                           |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                        |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                     |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                                                                                         |

Table 18. CCAPnL Registers (n = 0-4)

CCAP0L - PCA Module 0 Compare/Capture Control Register Low (0EAh)

CCAP1L - PCA Module 1 Compare/Capture Control Register Low (0EBh)

CCAP2L - PCA Module 2 Compare/Capture Control Register Low (0ECh)

CCAP3L - PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L - PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                        | 4 | 3            | 2     | 1 | 0 |

|---------------|-----------------|--------------------------|---|--------------|-------|---|---|

| -             | -               | -                        | - | -            | -     | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |              |       |   |   |

| 7-0           | -               | PCA Module<br>CCAPnL Val |   | /Capture Con | itrol |   |   |

Reset Value = 0000 0000b Not bit addressable

### Table 19. CH Register

CH - PCA Counter Register High (0F9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7-0           | -               | PCA counte<br>CH Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

### Table 20. CL Register

CL - PCA Counter Register Low (0E9h)

| 7             | 6               | 5                      | 4  | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|----|---|---|---|---|

| -             | -               | -                      | -  | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |    |   |   |   |   |

| 7-0           | -               | PCA Counte<br>CL Value | er |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

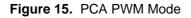

# Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 15 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 13 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- periodically change the compare value so it will never match the PCA timer,

- periodically change the PCA timer value so it will never match the compare values, or

- disable the watchdog by clearing the WDTE bit before a match occurs and then reenable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3.If the program counter ever goes astray, a match will eventually occur and

|                                  | Figure 18. UART Timings in Modes 2 and 3                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                  |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

|                                  | Start<br>Start                                                                                                                                                                                                                                                                                                        | Data byte                                                                                                                                                                                                                                                                              | → → → →<br>Ninth Stop<br>bit bit                                                                                                                                |  |  |  |  |

|                                  | RI                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

|                                  | SMOD0=0                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

|                                  | RI<br>SMOD0=1                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                        | ]                                                                                                                                                               |  |  |  |  |

|                                  | FE<br>SMOD0=1                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                        | ·                                                                                                                                                               |  |  |  |  |

|                                  | SMOD0=1                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

| Automatic Address<br>Recognition | nication feature is enabled (S<br>Implemented in hardware, au<br>communication feature by a<br>incoming command frame. C<br>receiver sets RI bit in SCON r<br>is not interrupted by comman<br>If desired, the user may enab<br>this configuration, the stop bit<br>the received command frame<br>by a valid stop bit. | M2 bit in SCON register is<br>utomatic address recognitio<br>allowing the serial port to<br>Only when the serial port re-<br>register to generate an inter<br>of frames addressed to othe<br>ole the automatic address r<br>t takes the place of the ninth<br>address matches the devi | examine the address of each<br>ecognizes its own address, the<br>rupt. This ensures that the CPU                                                                |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        | ddress recognition features cannot register in mode 0 has no effect).                                                                                           |  |  |  |  |

| Given Address                    | register is a mask byte that<br>device's given address. The o<br>slaves at a time. The followin                                                                                                                                                                                                                       | t contains don't-care bits (<br>don't-care bits provide the fl<br>g example illustrates how a                                                                                                                                                                                          | in SADDR register; the SADEN<br>(defined by zeros) to form the<br>lexibility to address one or more<br>a given address is formed.<br>DEN mask byte must be 1111 |  |  |  |  |

|                                  | The following is an example of<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                                                                                                                                                                                                | of how to use given address                                                                                                                                                                                                                                                            | ses to address different slaves:                                                                                                                                |  |  |  |  |

|                                  | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

|                                  | Slave C:SADDR1111 0010b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |  |  |  |  |

# Table 32. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                        | 4                                                                                                            | 3                               | 2               | 1               | 0                                                                                               |  |  |  |  |  |

|---------------|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SMOD1         | SMOD0           | -                        | POF                                                                                                          | GF1                             | GF0             | PD              | IDL                                                                                             |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                          |                                                                                                              | Desc                            | ription         |                 |                                                                                                 |  |  |  |  |  |

| 7             | SMOD1           |                          | <b>Mode bit 1 fc</b><br>t double baud                                                                        | or UART                         | 1, 2 or 3.      |                 |                                                                                                 |  |  |  |  |  |

| 6             | SMOD0           | Cleared to s             | <b>Mode bit 0 fo</b><br>elect SM0 bit<br>t FE bit in SC0                                                     | in SCON regis                   | ster.           |                 |                                                                                                 |  |  |  |  |  |

| 5             | -               | Reserved<br>The value re | ead from this t                                                                                              | oit is indetermi                | nate. Do not s  | et this bit.    |                                                                                                 |  |  |  |  |  |

| 4             | POF             |                          | ecognize next<br>ware when VC                                                                                |                                 | ) to its nomina | ıl voltage. Car | n also be set                                                                                   |  |  |  |  |  |

| 3             | GF1             | -                        | user for gener                                                                                               | al purpose usa<br>irpose usage. | age.            |                 |                                                                                                 |  |  |  |  |  |

| 2             | GF0             | Cleared by               | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage. |                                 |                 |                 |                                                                                                 |  |  |  |  |  |

| 1             | PD              | Cleared by I             | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.               |                                 |                 |                 |                                                                                                 |  |  |  |  |  |

| 0             | IDL             | Cleared by I             | nardware whe                                                                                                 | n interrupt or i                | eset occurs.    |                 | Idle mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode. |  |  |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

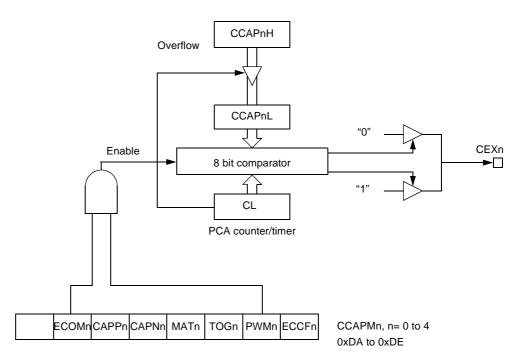

# Interrupt System

The <u>T89C51RB2/RC2</u> has a total of 10 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 21.

Figure 21. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 38 and Table 36). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 39) and in the Interrupt Priority High register (Table 37 and Table 38) shows the bit values and priority levels associated with each combination.

# Interrupt Sources and Vector Addresses

# Table 41. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INTO             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

# **Keyboard Interface**

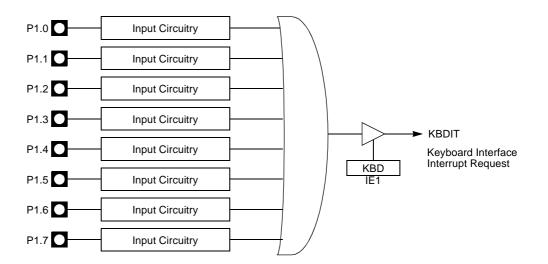

The T89C51RB2/RC2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power down modes.

The keyboard interface interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 44), KBE, The Keyboard interrupt Enable register (Table 43), and KBF, the Keyboard Flag register (Table 42).

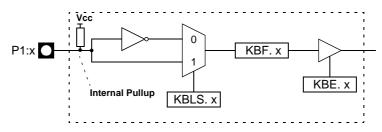

Interrupt The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 22). As detailed in Figure 23 each keyboard input has the capability to detect a programmable level according to KBLS. x bit value. Level detection is then reported in interrupt flags KBF. x that can be masked by software using KBE. x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

Figure 22. Keyboard Interface Block Diagram

Figure 23. Keyboard Input Circuitry

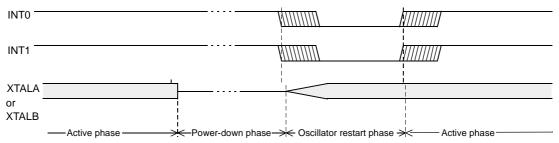

#### **Power Reduction Mode**

P1 inputs allow exit from idle and power down modes as detailed in Section "Powerdown Mode", page 75.

# Table 43. KBE Register

KBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                                                                                                               | 3          | 2              | 1               | 0     |  |

|---------------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|-----------------|-------|--|

| KBE7          | KBE6            | KBE5          | KBE4                                                                                                                                            | KBE3       | KBE2           | KBE1            | KBE0  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                                                                                                                 |            |                |                 |       |  |

| 7             | KBE7            | Cleared to en | n <b>e 7 Enable I</b><br>nable standar<br>e KBF. 7 bit in                                                                                       | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 6             | KBE6            | Cleared to en | ne 6 Enable I<br>nable standar<br>e KBF. 6 bit in                                                                                               | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 5             | KBE5            | Cleared to en | ne 5 Enable I<br>nable standar<br>e KBF. 5 bit in                                                                                               | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 4             | KBE4            | Cleared to en | n <b>e 4 Enable I</b><br>nable standar<br>e KBF. 4 bit in                                                                                       | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 3             | KBE3            | Cleared to en | ne 3 Enable I<br>nable standar<br>e KBF. 3 bit in                                                                                               | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 2             | KBE2            | Cleared to en | n <b>e 2 Enable I</b><br>nable standar<br>e KBF. 2 bit in                                                                                       | d I/O pin. | to generate ar | n interrupt req | uest. |  |

| 1             | KBE1            | Cleared to en | Keyboard line 1 Enable bit<br>Cleared to enable standard I/O pin.<br>Set to enable KBF. 1 bit in KBF register to generate an interrupt request. |            |                |                 |       |  |

| 0             | KBE0            | Cleared to en | n <b>e 0 Enable I</b><br>nable standar<br>e KBF. 0 bit in                                                                                       | d I/O pin. | to generate ar | n interrupt req | uest. |  |

Reset Value= 0000 0000b

# Table 44. KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7             | 6               | 5             | 4                                                                                                                                                             | 3                                                  | 2     | 1     | 0     |

|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|

| KBLS7         | KBLS6           | KBLS5         | KBLS4                                                                                                                                                         | KBLS3                                              | KBLS2 | KBLS1 | KBLS0 |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                                                                                                                               |                                                    |       |       |       |

| 7             | KBLS7           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on P |       |       |       |

| 6             | KBLS6           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on P |       |       |       |

| 5             | KBLS5           | Cleared to en | <b>Keyboard line 5 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 5.<br>Set to enable a high level detection on Port line 5. |                                                    |       |       |       |

| 4             | KBLS4           | Cleared to en | <b>Keyboard line 4 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 4.<br>Set to enable a high level detection on Port line 4. |                                                    |       |       |       |

| 3             | KBLS3           | Cleared to en | <b>Keyboard line 3 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 3.<br>Set to enable a high level detection on Port line 3. |                                                    |       |       |       |

| 2             | KBLS2           | Cleared to en | <b>Keyboard line 2 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 2.<br>Set to enable a high level detection on Port line 2. |                                                    |       |       |       |

| 1             | KBLS1           | Cleared to en | <b>Keyboard line 1 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1. |                                                    |       |       |       |

| 0             | KBLS0           | Cleared to en | Keyboard line 0 Level Selection bit<br>Cleared to enable a low level detection on Port line 0.<br>Set to enable a high level detection on Port line 0.        |                                                    |       |       |       |

Reset Value= 0000 0000b

#### Table 51. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7             | 6               | 5                                                                                                                                                                       |                                                                           | 4                                                                                                                                           | 3                                                                                                                                                | 2                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| -             | -               | -                                                                                                                                                                       |                                                                           | -                                                                                                                                           | -                                                                                                                                                | S2                                                                                                | S1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S0                               |