Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51rc2-slsim |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 3. Pin Description for 40 - 44 Pin Packages (Continued)

|          | Pin Number |     |            |      |                                                                                                                                                                                                                                                                                                                                         |

|----------|------------|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic | DIL        | LCC | VQFP44 1.4 | Туре | Name and Function                                                                                                                                                                                                                                                                                                                       |

| PSEN     | 29         | 32  | 26         | 0    | <b>Program Strobe ENable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory. |

| EA       | 31         | 35  | 29         | I    | <b>External Access Enable:</b> EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH (RD). If security level 1 is programmed, EA will be internally latched on Reset.                                                                                                 |

## Functional Block Diagram

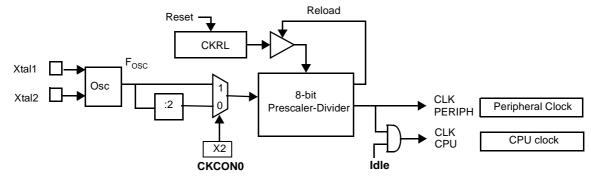

Figure 3. Functional Oscillator Block Diagram

#### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh: F<sub>CLK CPU</sub> = F<sub>CLK PERIPH</sub> = F<sub>OSC</sub>/2 (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/1020$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/510$  (X2 Mode)

- CKRL = FFh: maximum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}$  (X2 Mode)

$F_{\text{CLK CPU}}$  and  $F_{\text{CLK PERIPH}}$

In X2 Mode:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$$

In X1 Mode:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$$

### Table 7. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                | 4                                                                                                                                                                                                                                         | 3 | 2 | 1 | 0     |  |  |  |  |

|---------------|-----------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|--|--|--|--|

| -             | -               | -                                | -                                                                                                                                                                                                                                         | - | - | - | SPIX2 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      | Description                                                                                                                                                                                                                               |   |   |   |       |  |  |  |  |

| 7             | -               | Reserved                         |                                                                                                                                                                                                                                           |   |   |   |       |  |  |  |  |

| 6             | -               | Reserved                         |                                                                                                                                                                                                                                           |   |   |   |       |  |  |  |  |

| 5             | -               | Reserved                         | Reserved                                                                                                                                                                                                                                  |   |   |   |       |  |  |  |  |

| 4             | -               | Reserved                         | Reserved                                                                                                                                                                                                                                  |   |   |   |       |  |  |  |  |

| 3             | -               | Reserved                         |                                                                                                                                                                                                                                           |   |   |   |       |  |  |  |  |

| 2             | -               | Reserved                         |                                                                                                                                                                                                                                           |   |   |   |       |  |  |  |  |

| 1             | -               | Reserved                         |                                                                                                                                                                                                                                           |   |   |   |       |  |  |  |  |

| 0             | SPIX2           | this bit has no<br>Clear to sele | SPI (This control bit is validated when the CPU clock X2 is set; when X2 is low,<br>this bit has no effect).<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |   |   |   |       |  |  |  |  |

Reset Value = XXXX XXX0b Not bit addressable

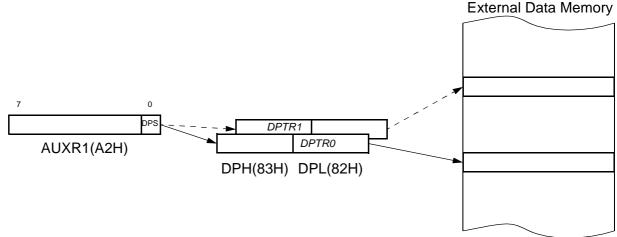

# Dual Data Pointer Register DPTR

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 8) that allows the program code to switch between them (Refer to Figure 6).

#### Figure 6. Use of Dual Pointer

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

## Registers

#### Table 13. CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                                                                                                                                                             | 4                                                                                                                                                            | 3               | 2              | 1             | 0   |  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|-----|--|--|--|

| CIDL          | WDTE            | -                                                                                                                                                             | -                                                                                                                                                            | -               | CPS1           | CPS0          | ECF |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                   | Description                                                                                                                                                  |                 |                |               |     |  |  |  |

| 7             | CIDL            | Cleared to p                                                                                                                                                  | Counter Idle Control<br>Cleared to program the PCA Counter to continue functioning during idle Mode.<br>Set to program PCA to be gated off during idle.      |                 |                |               |     |  |  |  |

| 6             | WDTE            | Cleared to di                                                                                                                                                 | Watchdog Timer Enable           Cleared to disable Watchdog Timer function on PCA Module 4.           Set to enable Watchdog Timer function on PCA Module 4. |                 |                |               |     |  |  |  |

| 5             | -               | Reserved<br>The value                                                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                              |                 |                |               |     |  |  |  |

| 4             | -               | Reserved<br>The value                                                                                                                                         | read from this                                                                                                                                               | bit is indeterr | ninate. Do not | set this bit. |     |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value                                                                                                                                  | read from this                                                                                                                                               | bit is indeterr | ninate. Do not | set this bit. |     |  |  |  |

| 2             | CPS1            | PCA Count                                                                                                                                                     | Pulse Select                                                                                                                                                 |                 |                |               |     |  |  |  |

| 1             | CPS0            | CPS1         CPS0           0         0           1         0           1         1                                                                           | 0     1     Internal clock fCLK PERIPH/2       1     0     Timer 0 Overflow                                                                                  |                 |                |               |     |  |  |  |

| 0             | ECF             | PCA Enable Counter Overflow Interrupt<br>Cleared to disable CF bit in CCON to inhibit an interrupt.<br>Set to enable CF bit in CCON to generate an interrupt. |                                                                                                                                                              |                 |                |               |     |  |  |  |

Reset Value = 00XX X000b Not bit addressable

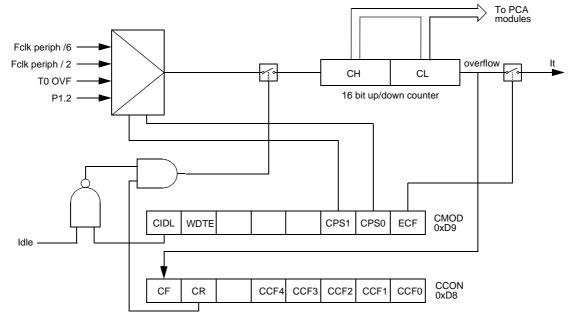

The CMOD register includes three additional bits associated with the PCA (See Figure 10 and Table 13).

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 14).

- Bit CR (CCON. 6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON. 7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

### Table 14. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                               | 4                                                                                                                                                                                                                  | 3    | 2          | 1    | 0    |  |  |

|---------------|-----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------|------|--|--|

| CF            | CR              | -                               | CCF4                                                                                                                                                                                                               | CCF3 | CCF2       | CCF1 | CCF0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                                                                                                                                                    |      |            |      |      |  |  |

| 7             | CF              | Set by hardv<br>CMOD is set     | PCA Counter Overflow flag<br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in<br>CMOD is set. CF may be set by either hardware or software but can only be<br>cleared by software. |      |            |      |      |  |  |

| 6             | CR              | Must be clea                    | <b>PCA Counter Run control bit</b><br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                      |      |            |      |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                    |      |            |      |      |  |  |

| 4             | CCF4            | Must be clea                    | <b>e 4 interrupt</b><br>ired by softwa<br>vare when a n                                                                                                                                                            | •    | re occurs. |      |      |  |  |

| 3             | CCF3            | Must be clea                    | <b>a 3 interrupt</b><br>ired by softwa<br>vare when a n                                                                                                                                                            | •    | re occurs. |      |      |  |  |

| 2             | CCF2            | Must be clea                    | PCA Module 2 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |      |            |      |      |  |  |

| 1             | CCF1            | Must be clea                    | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |      |            |      |      |  |  |

| 0             | CCF0            | Must be clea                    | PCA Module 0 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |      |            |      |      |  |  |

Reset Value = 000X 0000b Not bit addressable

The watchdog timer function is implemented in module 4 (See Figure 13).

The PCA interrupt system is shown in Figure 11.

cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

### Table 31. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                       | 4                                                                                                                                                                                                                                                                                                                                 | 3                                                                 | 2               | 1              | 0        |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|----------------|----------|--|--|--|

| TF2           | EXF2            | RCLK                                                                    | TCLK                                                                                                                                                                                                                                                                                                                              | EXEN2                                                             | TR2             | C/T2#          | CP/RL2#  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                         | Description                                                                                                                                                                                                                                                                                                                       |                                                                   |                 |                |          |  |  |  |

| 7             | TF2             | Must be clea                                                            | <b>Timer 2 overflow Flag</b><br>Aust be cleared by software.<br>Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                    |                                                                   |                 |                |          |  |  |  |

| 6             | EXF2            | Set when a<br>EXEN2=1.<br>When set, c<br>interrupt is e<br>Must be clea | <b>Timer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down ounter mode (DCEN = 1) |                                                                   |                 |                |          |  |  |  |

| 5             | RCLK            | Cleared to u                                                            | Receive Clock bit for UART<br>Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                    |                                                                   |                 |                |          |  |  |  |

| 4             | TCLK            | Cleared to u                                                            | Transmit Clock bit for UART<br>Cleared to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                 |                                                                   |                 |                |          |  |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                           | e a capture or                                                                                                                                                                                                                                                                                                                    | e <b>bit</b><br>on T2EX pin fo<br>reload when a<br>used to clock  | a negative trar | nsition on T2E | X pin is |  |  |  |

| 2             | TR2             |                                                                         | n control bit<br>urn off timer 2<br>on timer 2.                                                                                                                                                                                                                                                                                   | 2.                                                                |                 |                |          |  |  |  |

| 1             | C/T2#           | Cleared for<br>Set for coun                                             | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be<br>0 for clock out mode.                                                                                     |                                                                   |                 |                |          |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 of<br>timer 2 over<br>Cleared to a<br>if EXEN2=1              | flow.<br>auto-reload on                                                                                                                                                                                                                                                                                                           | <b>bit</b><br>P/RL2# is igno<br>timer 2 overfl<br>e transitions o | ows or negativ  | ve transitions |          |  |  |  |

Reset Value = 0000 0000b Bit addressable

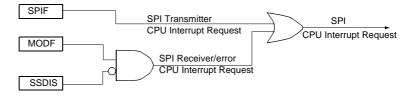

#### Figure 30. SPI Interrupt Requests Generation

#### Registers

Serial Peripheral Control register (SPCON)

There are three registers in the module that provide control, status and data storage functions. These registers are describes in the following paragraphs.

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates,

- Configure the SPI module as Master or Slave,

- Selects serial clock polarity and phase,

- Enables the SPI module,

- Frees the SS pin for a general purpose

Table 47 describes this register and explains the use of each bit.

#### Table 47. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

| 7          | 6       | 5      | 4                                                                                                                                                                                    | 3              | 2    | 1    | 0    |  |  |

|------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------|--|--|

| SPR2       | SPEN    | SSDIS  | MSTR                                                                                                                                                                                 | CPOL           | СРНА | SPR1 | SPR0 |  |  |

| Bit Number | Bit Mne | emonic | Description                                                                                                                                                                          |                |      |      |      |  |  |

| 7          | SF      | PR2    | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate.                                                                                                            |                |      |      |      |  |  |

| 6          | SP      | PEN    | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                |                |      |      |      |  |  |

| 5          | SSDIS   |        | <b>SS Disable</b><br>Cleared to enable SS# in both Master and Slave modes.<br>Set to disable SS# in both Master and Slave modes. In Slave mo<br>this bit has no effect if CPHA ='0'. |                |      |      |      |  |  |

| 5          | MS      | STR    | Serial Periphe<br>Cleared to con<br>Set to configur                                                                                                                                  | figure the SPI |      |      |      |  |  |

| 4          | CF      | POL    | <b>Clock Polarity</b><br>Cleared to have the SCK set to'0' in idle state.<br>Set to have the SCK set to'1' in idle low.                                                              |                |      |      |      |  |  |

| 3          | CF      | PHA    | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the idle<br>state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see<br>CPOL).  |                |      |      |      |  |  |

| Bit Number | Bit Mnemonic | Descri | ption |             |                              |

|------------|--------------|--------|-------|-------------|------------------------------|

|            |              | SPR2   | SPR1  | <u>SPR0</u> | Serial Peripheral Rate       |

| 2          | SPR1         | 0      | 0     | 0           | F <sub>CLK PERIPH</sub> /2   |

|            |              | 0      | 0     | 1           | F <sub>CLK PERIPH</sub> /4   |

|            |              | 0      | 1     | 0           | F <sub>CLK PERIPH</sub> /8   |

|            |              | 0      | 1     | 1           | F <sub>CLK PERIPH</sub> /16  |

|            |              | 1      | 0     | 0           | F <sub>CLK PERIPH</sub> /32  |

| 1          | SPR0         | 1      | 0     | 1           | F <sub>CLK PERIPH</sub> /64  |

|            |              | 1      | 1     | 0           | F <sub>CLK PERIPH</sub> /128 |

|            |              | 1      | 1     | 1           | Invalid                      |

Reset Value= 0001 0100b

Not bit addressable

Serial Peripheral Status Register (SPSTA)

- tus Register The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 48 describes the SPSTA register and explains the use of every bit in the register.

#### Table 48. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7             | 6               | 5                            | 4                                                                                                                                                                                                                                                             | 3               | 2              | 1            | 0 |  |  |  |

|---------------|-----------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|---|--|--|--|

| SPIF          | WCOL            | -                            | MODF                                                                                                                                                                                                                                                          | -               | -              | -            | - |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                  | Description                                                                                                                                                                                                                                                   |                 |                |              |   |  |  |  |

| 7             | SPIF            | Cleared by ha<br>approved by | Serial Peripheral data transfer flag<br>Cleared by hardware to indicate data transfer is in progress or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed.                                |                 |                |              |   |  |  |  |

| 6             | WCOL            | Cleared by hat approved by   | Write Collision flag<br>Cleared by hardware to indicate that no collision has occurred or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that a collision has been detected.                                                     |                 |                |              |   |  |  |  |

| 5             | -               | Reserved<br>The value rea    | ad from this bi                                                                                                                                                                                                                                               | t is indetermin | ate. Do not se | et this bit. |   |  |  |  |

| 4             | MODF            | has been app                 | <b>Mode Fault</b><br>Cleared by hardware to indicate that the $\overline{SS}$ pin is at appropriate logic level, or<br>has been approved by a clearing sequence.<br>Set by hardware to indicate that the $\overline{SS}$ pin is at inappropriate logic level. |                 |                |              |   |  |  |  |

| 3             | -               | Reserved<br>The value rea    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                |                 |                |              |   |  |  |  |

| 2             | -               | Reserved<br>The value rea    | ad from this bi                                                                                                                                                                                                                                               | t is indetermir | ate. Do not se | et this bit  |   |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |

|---------------|-----------------|----------------------------------------------------------------------------------------|

| 1             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

| 0             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

Reset Value= 00X0 XXXXb

Not Bit addressable

Serial Peripheral DATa register (SPDAT) The Serial Peripheral Data Register (Table 49) is a read/write buffer for the receive data register. A write to SPDAT places data directly into the shift register. No transmit buffer is available in this model.

A Read of the SPDAT returns the value located in the receive buffer and not the content of the shift register.

#### Table 49. SPDAT Register

SPDAT - Serial Peripheral Data Register (0C5H)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Reset Value= Indeterminate

R7:R0: Receive data bits

SPCON, SPSTA and SPDAT registers may be read and written at any time while there is no on-going exchange. However, special care should be taken when writing to them while a transmission is on-going:

- Do not change SPR2, SPR1 and SPR0

- Do not change CPHA and CPOL

- Do not change MSTR

- Clearing SPEN would immediately disable the peripheral

- Writing to the SPDAT will cause an overflow

# Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the WatchDog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

**Using the WDT** To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must write 01EH and 0E1H to WDTRST. WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x T<sub>CLK PERIPH</sub>, where T<sub>CLK PERIPH</sub> = 1/F<sub>CLK PERIPH</sub>. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16ms to 2s @  $F_{OSCA}$  = 12MHz. To manage this feature, refer to WDTPRG register description, Table 50.

Table 50.

WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

| Idle Mode       | An instruction that sets PCON. 0 indicates that it is the last instruction to be executed before going into Idle mode. In Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is pre-<br>served in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high level.                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON. 0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.                                                                                                                                                                                                                                                                                       |

|                 | The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred dur-<br>ing normal operation or during idle. For example, an instruction that activates idle can<br>also set one or both flag bits. When idle is terminated by an interrupt, the interrupt ser-<br>vice routine can examine the flag bits.                                                                                                                                                                                                                                                                                   |

|                 | The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.                                                                                                                                                                                                                                                                                                                                                                           |

| Power-down Mode | To save maximum power, a power-down mode can be invoked by software (refer to Table 5, PCON register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | In power-down mode, the oscillator is stopped and the instruction that invoked power-<br>down mode is the last instruction executed. The internal RAM and SFRs retain their<br>value until the power-down mode is terminated. $V_{CC}$ can be lowered to save further<br>power. Either a hardware reset or an external interrupt can cause an exit from power-<br>down. To properly terminate power-down, the reset or external interrupt should not be<br>executed before $V_{CC}$ is restored to its normal operating level and must be held active<br>long enough for the oscillator to restart and stabilize. |

|                 | Only external interrupts INTO, INT1 and Keyboard Interrupts are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensi-<br>tive interrupt input. When Keyboard Interrupt occurs after a power down mode, 1024 clocks are necessary to exit to power down mode and enter in operating mode.                                                                                                                                                                                                                                                                     |

|                 | Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 32. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put T89C51RB2/RC2 into power-down mode.                                                              |

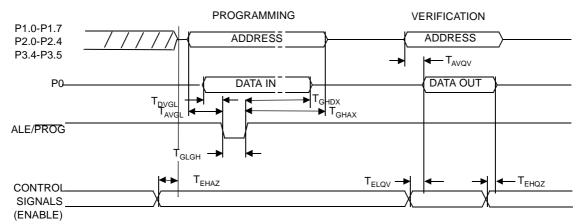

#### Flash EEPROM Programming and Verification Waveforms

Figure 40. Flash EEPROM Programming and Verification Waveforms

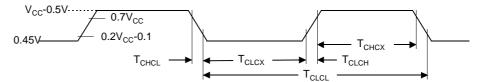

#### **External Clock Drive Characteristics (XTAL1)**

#### Table 68. External Clock Drive Characteristics (XTAL1)

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 3   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 3   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 3   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 3   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

#### **External Clock Drive** Waveforms

Figure 41. External Clock Drive Waveforms

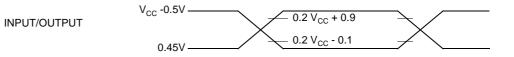

#### **AC Testing Input/Output** Waveforms

Figure 42. AC Testing Input/Output Waveforms

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min. for a logic "1" and V<sub>IL</sub> max for a logic "0".

T89C51RB2/RC2

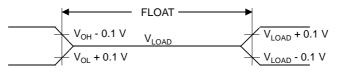

#### **Float Waveforms**

Figure 43. Float Waveforms

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$  mA.

#### **Clock Waveforms**

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.

| Table 75. API | Calls (0 | Continued) |

|---------------|----------|------------|

|---------------|----------|------------|

| API Call                            | Parameter                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROGRAM<br>SOFTWARE<br>SECURITY BIT | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 05h<br>DPH = 00h<br>DPL = 00h – security bit # 1 (inhibit writing to Flash)<br>01h – security bit # 2 (inhibit Flash verify)<br>10h - allows ISP writing to Flash (see Note 1)<br>11h - allows ISP Flash verify (see Note 1)<br>Return Parameter<br>none |

| PROGRAM BOOT<br>STATUS BYTE         | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 06h<br>DPH = 00h<br>DPL = 00h<br>ACC = status byte<br>Return Parameter<br>ACC = status byte                                                                                                                                                              |

| PROGRAM BOOT<br>VECTOR              | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 06h<br>DPH = 00h<br>DPL = 01h<br>ACC = boot vector<br>Return Parameter<br>ACC = boot vector                                                                                                                                                              |

| PROGRAM X2<br>MODE                  | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 0Ah<br>DPH = 00h<br>DPL = 08h<br>ACC = value (00 or 01h)<br>Return Parameter<br>ACC = boot vector                                                                                                                                                        |

| PROGRAM BLJB                        | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 0Ah<br>DPH = 00h<br>DPL = 04h<br>ACC = value (00 or 01h)<br>Return Parameter<br>ACC = boot vector                                                                                                                                                        |

| READ DEVICE DATA                    | Input Parameters:<br>R1 = 03h<br>DPTR = address of byte to read<br>Return Parameter<br>ACC = value of byte read                                                                                                                                                                                                                                            |

## Table 75. API Calls (Continued)

| API Call                            | Parameter                                                                                                                                                                                                       |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ copy of the<br>MANUFACTURER ID | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 00h<br>DPH = 00h<br>DPL = 00h (manufacturer ID)<br>Return Parameter<br>ACC = value of byte read               |

| READ copy of the device ID # 1      | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 00h<br>DPH = 00h<br>DPL = 01h (device ID # 1)<br>Return Parameter<br>ACC = value of byte read                 |

| READ copy of the device ID # 2      | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 00h<br>DPH = 00h<br>DPL = 02h (device ID # 2)<br>Return Parameter<br>ACC = value of byte read                 |

| READ copy of the device ID # 3      | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 00h<br>DPH = 00h<br>DPL = 03h (device ID # 2)<br>Return Parameter<br>ACC = value of byte read                 |

| READ SOFTWARE<br>SECURITY BITS      | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 07h<br>DPH = 00h<br>DPL = 00h (Software security bits)<br>Return Parameter<br>ACC = value of byte read        |

| READ HARDWARE<br>SECURITY BITS      | Input Parameters:<br>R0 = osc freq (integer Not required, left for Philips compatibility)<br>R1 = 07h -> OBh<br>DPH = 00h<br>DPL = 04h (Hardware security bits)<br>Return Parameter<br>ACC = value of byte read |

# **Table of Contents**

| Features                                      | 1    |

|-----------------------------------------------|------|

| Description                                   | 1    |

| Block Diagram                                 | 2    |

| SFR Mapping                                   | 3    |

| Pin Configurations                            | 5    |

| Oscillator                                    | 9    |

| Registers                                     | 9    |

| Functional Block Diagram                      |      |

| Enhanced Features                             | 11   |

| X2 Feature                                    | . 11 |

| Dual Data Pointer Register DPTR               | 15   |

| Expanded RAM (XRAM)                           | 18   |

| Registers                                     |      |

| Timer 2                                       | 21   |

| Auto-Reload Mode                              | . 21 |

| Programmable Clock-Output                     |      |

| Registers                                     |      |

| Programmable Counter Array PCA                | 26   |

| Registers                                     | . 28 |

| PCA Capture Mode                              | . 34 |

| 16-bit Software Timer/ Compare Mode           | . 35 |

| High Speed Output Mode                        | . 36 |

| Pulse Width Modulator Mode                    | . 37 |

| PCA Watchdog Timer                            | . 37 |

| Serial I/O Port                               | 39   |

| Framing Error Detection                       | . 39 |

| Automatic Address Recognition                 | . 40 |

| Registers                                     |      |

| Baud Rate Selection for UART for Mode 1 and 3 |      |

| UART registers                                | . 45 |

| Interrupt System                              | 50   |

| . Registers                                   | . 51 |