# E·XFL

#### Zilog - Z8F0411HH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessoreZ8Core Size8-BitSpeed20MHzConnectivityPC, IrDA, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size4KB (4K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature4.0°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0.5SOP (0.209", 5.30mm Width)Supplier Device Package- |                            |                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------|

| Core Size8-BitCore Size8-BitSpeed20MHzConnectivityPC, IrDA, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size4KB (4K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-   | Product Status             | Obsolete                                                      |

| Speed20MHzConnectivityPC, IrDA, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size4KB (4K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)                                                                              | Core Processor             | eZ8                                                           |

| ConnectivityPC, IrDA, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size4KB (4K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)                                                                 | Core Size                  | 8-Bit                                                         |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O11Program Memory Size4KB (4K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case2.5SOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                 | Speed                      | 20MHz                                                         |

| Number of I/O11Program Memory Size4KB (4K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case2.5SOP (0.209", 5.30mm Width)Suppler Device Package-                                                                                                                           | Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                            |

| Program Memory Size4KB (4K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case2.5SOP (0.209", 5.30mm Width)Suppler Device Package-                                                                                                                                          | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Program Memory TypeFLASHEEPROM Size-RAM SizeIK × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0.5SOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                        | Number of I/O              | 11                                                            |

| EEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                               | Program Memory Size        | 4KB (4K x 8)                                                  |

| RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                           | Program Memory Type        | FLASH                                                         |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                         | EEPROM Size                | -                                                             |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                              | RAM Size                   | 1K x 8                                                        |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                              | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                     | Data Converters            | -                                                             |

| Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                            | Oscillator Type            | Internal                                                      |

| Package / Case     20-SSOP (0.209", 5.30mm Width)       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                     | Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                 | Mounting Type              | Surface Mount                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0411hh020ec00tr                                                                                                                                                                                                                                                                                                                                                                | Supplier Device Package    | -                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0411hh020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Introduction                       |

|------------------------------------|

| About This Manual                  |

| Intended Audience                  |

| Manual Conventionsx                |

| Safeguards                         |

| Abbreviations/Acronymsxii          |

| Introduction                       |

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| eZ8 CPU Features                   |

| General Purpose Input/Output 4     |

| Flash Controller                   |

| 10-Bit Analog-to-Digital Converter |

| UART                               |

| I <sup>2</sup> C                   |

| Serial Peripheral Interface        |

| Timers                             |

| Interrupt Controller               |

| Reset Controller                   |

| On-Chip Debugger                   |

| Signal and Pin Descriptions        |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

| Address Space                      |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Information Area                   |

| Register File Address Map 15       |

| Control Register Summary           |

| Reset and Stop Mode Recovery       |

| Reset Types                        |

| System Reset                       |

#### X

## Introduction

This Product Specification provides detailed operating information for Z8 Encore! XP<sup>®</sup> F0822 Series devices within the Z8 Encore! XP Microcontroller (MCU) family of products. Within this document, Z8 Encore! XP<sup>®</sup> F0822 Series is referred as Z8 Encore! XP or the F0822 Series unless specifically stated otherwise.

#### About This Manual

Zilog recommends that you read and understand everything in this manual before setting up and using the product. We have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### Intended Audience

This document is written for Zilog customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• **Example:** FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• **Example:** R1 is set to F8H.

#### Brackets

The square brackets [], indicate a register or bus.

• **Example:** For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

#### 29

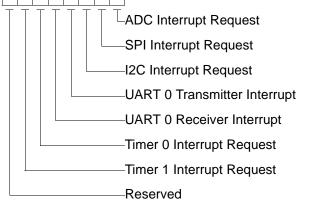

#### Interrupt Request 0 IRQ0 (FC0H - Read/Write) D7/D6/D5/D4/D3/D2/D1/D0

For all of the above peripherals: 0 = Peripheral IRQ is not pending 1 = Peripheral IRQ is awaiting service

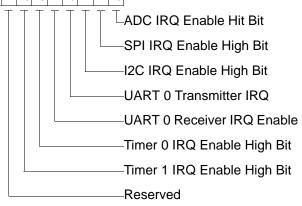

#### IRQ0 Enable High Bit IRQ0ENH (FC1H - Read/Write) D7D6D5D4D3D2D1D0

31

#### Interrupt Request 2 IRQ2 (FC6H - Read/Write) D7D6D5D4D3D2D1D0

Port C Pin Interrupt Request 0 = IRQ from corresponding pin [3:0] is not pending 1 = IRQ from corresponding pin [3:0] is awaiting service Reserved

IRQ2 Enable High Bit IRQ2ENH (FC7H - Read/Write) D7/D6/D5/D4/D3/D2/D1/D0

Port C Pin IRQ Enable High

------Reserved

IRQ2 Enable Low Bit IRQ2ENL (FC8H - Read/Write) P7D6D5D4D3D2D1D0 Port C Pin IRQ Enable Low Reserved

Interrupt Control IRQCTL (FCFH - Read/Write) D7D6D5D4D3D2D1D0

Reserved

Interrupt Request Enable

0 = Interrupts are disabled

1 = Interrupts are enabled

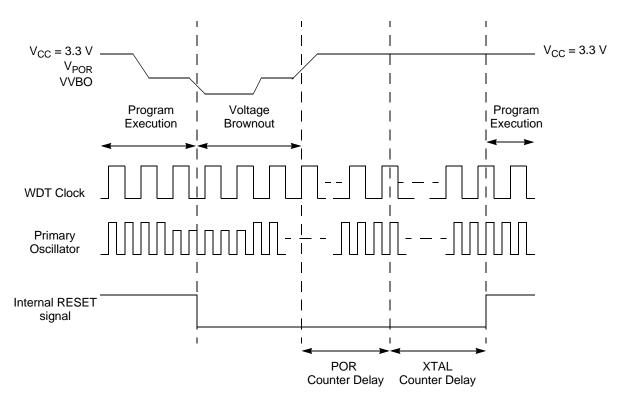

remains below the POR voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset state.

After the supply voltage again exceeds the POR voltage threshold, the device progresses through a full System Reset sequence as described in the POR section. Following POR, the POR status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1. Figure 7 displays the VBO operation. See Electrical Characteristics on page 185 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The VBO circuit can be either enabled or disabled during STOP mode. Operation during STOP mode is set by the VBO\_AO Option Bit. For information on configuring VBO\_AO, see Option Bits on page 163.

Figure 7. Voltage Brownout Reset Operation

#### Watchdog Timer Reset

If the device is in NORMAL or HALT mode, WDT initiates a System Reset at time-out, if the WDT\_RES Option Bit is set to 1. This is the default (unprogrammed) setting of the WDT\_RES Option Bit. The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the WDT.

#### Stop Mode Recovery Using WDT Time-Out

If the WDT times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the WDT Control Register, the WDT and STOP bits are set to 1. If the WDT is configured to generate an interrupt upon time-out and the Z8 Encore! XP<sup>®</sup> F0822 Series device is configured to respond to interrupts, the eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

#### Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a STOP Mode Recover source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. The GPIO Stop Mode Recovery signals are filtered to reject pulses less than 10 ns (typical) in duration. In the WDT Control Register, the STOP bit is set to 1.

#### Caution:

In STOP mode, the GPIO Port Input Data Registers (PxIN) are disabled. The Port Input Data Registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. Therefore, short pulses on the Port pin initiates Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin). pins.To determine the alternate function associated with each port pin, see GPIO Port Pin Block Diagram on page 48.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 17. Port A–CA–C Alternate Function Sub-Registers

| BITS  | 7        | 6                           | 5           | 4             | 3            | 2             | 1            | 0        |  |

|-------|----------|-----------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|

| FIELD | AF7      | AF6 AF5 AF4 AF3 AF2 AF1 AF0 |             |               |              |               |              |          |  |

| RESET |          | 0                           |             |               |              |               |              |          |  |

| R/W   | R/W      |                             |             |               |              |               |              |          |  |

| ADDR  | lf 02H i | n Port A–C                  | Address Reg | gister, acces | sible throug | h the Port A- | -C Control F | Register |  |

#### AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–C Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–C Output Control Sub-Registers

The Port A–C Output Control sub-register (Table 18) is accessed through the Port A–C Control Register by writing 03H to the Port A–C Address Register. Setting the bits in the Port A–C Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

| Table 18. Por | t A-C Output | t Control Sub-Regis | sters |

|---------------|--------------|---------------------|-------|

|---------------|--------------|---------------------|-------|

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |  |  |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|--|--|

| FIELD | POC7     | POC6       | POC5        | POC4          | POC3         | POC2         | POC1         | POC0     |  |  |

| RESET |          | 0          |             |               |              |              |              |          |  |  |

| R/W   |          | R/W        |             |               |              |              |              |          |  |  |

| ADDR  | lf 03H i | n Port A–C | Address Reo | gister, acces | sible throug | h the Port A | -C Control F | Register |  |  |

#### POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The drains are enabled for any output mode (unless overridden by the

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

0, then reading the UART Receive Data Register clears this bit.

0 = No overrun error occurred.

1 = An overrun error occurred.

#### **FE—Framing Error**

This bit indicates that a framing error (no STOP bit following data reception) was detected. Reading the UART Receive Data Register clears this bit.

0 = No framing error occurred.

1 = A framing error occurred.

#### **BRKD**—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and STOP bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data Register clears this bit.

0 = No break occurred.

1 = A break occurred.

#### **TDRE**—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data Register is empty and ready for additional data. Writing to the UART Transmit Data Register resets this bit.

0 = Do not write to the UART Transmit Data Register.

1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.

#### **TXE**—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

#### CTS—CTS Signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal.

#### UART Status 1 Register

This register contains multiprocessor control and status bits.

#### Table 55. UART Status 1 Register (U0STAT1)

| BITS  | 7                    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|----------------------|---|---|----|----|---|---|---|

| FIELD | Reserved NEWFRM MPRX |   |   |    |    |   |   |   |

| RESET | 0                    |   |   |    |    |   |   |   |

| R/W   | R R/W R              |   |   |    |    |   | ł |   |

| ADDR  |                      |   |   | F4 | 4H |   |   |   |

### **SPI Control Register**

The SPI Control Register configures the SPI for transmit and receive operations.

#### Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6                                         | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|-------------------------------------------|---|----|----|---|---|---|--|--|

| FIELD | IRQE | IRQE STR BIRQ PHASE CLKPOL WOR MMEN SPIEN |   |    |    |   |   |   |  |  |

| RESET |      | <u> </u>                                  |   |    |    |   |   |   |  |  |

| R/W   |      | R/W                                       |   |    |    |   |   |   |  |  |

| ADDR  |      |                                           |   | F6 | 1H |   |   |   |  |  |

#### **IRQE**—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

#### STR—Start an SPI Interrupt Request

- 0 = No effect.

- 1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status Register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status Register clears this bit to 0.

#### **BIRQ—BRG Timer Interrupt Request**

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

- 0 = BRG timer function is disabled.

- 1 = BRG timer function and time-out interrupt are enabled.

#### **PHASE**—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 116.

#### **CLKPOL**—Clock Polarity

- 0 = SCK idles Low (0).

- 1 = SCK idle High (1).

#### WOR-Wire-OR (Open-Drain) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

#### MMEN—SPI MASTER Mode Enable

0 = SPI configured in SLAVE mode.

1 = SPI configured in MASTER mode.

#### SPIEN—SPI Enable

- 0 = SPI disabled.

- 1 = SPI enabled.

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers (Tables 73 and 73) combine to form a 16bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]

Table 73. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| BITS  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|-----|---|---|----|----|---|---|---|

| FIELD | BRH |   |   |    |    |   |   |   |

| RESET | FFH |   |   |    |    |   |   |   |

| R/W   | R/W |   |   |    |    |   |   |   |

| ADDR  |     |   |   | F5 | 3H |   |   |   |

## **BRH** = $I^2C$ Baud Rate High Byte

Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

| BITS  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|-----|---|---|----|----|---|---|---|

| FIELD | BRL |   |   |    |    |   |   |   |

| RESET | FFH |   |   |    |    |   |   |   |

| R/W   | R/W |   |   |    |    |   |   |   |

| ADDR  |     |   |   | F5 | 4H |   |   |   |

## **BRL** = $I^2C$ Baud Rate Low Byte

Least significant byte, BRG[7:0], of the  $I^2C$  Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRL register returns the current value of the  $I^2C$  Baud Rate Counter [7:0].

## I<sup>2</sup>C Diagnostic State Register

The I<sup>2</sup>C Diagnostic State register (Table 75) provides observability of internal state. This is a read only register used for I<sup>2</sup>C diagnostics and manufacturing test.

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

168

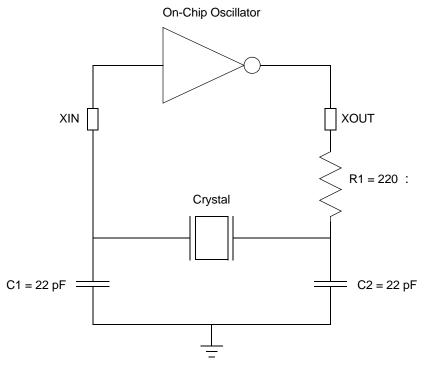

Figure 34. Recommended 20 MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 25          | W     | Maximum  |

| Load Capacitance (CL)               | 20          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 91. Recommended Crystal Oscillator Specifications (20 MHz Operation)

## **Oscillator Operation with an External RC Network**

The External RC oscillator mode is applicable to timing insensitive applications. Figure 35 on page 169 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

## Table 93. On-Chip Debugger Commands

| Debug Command                 | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                                            |

|-------------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision             | 00H             | Yes                                   | -                                                                                                                                                                                                 |

| Write OCD Counter<br>Register | 01H             | -                                     | -                                                                                                                                                                                                 |

| Read OCD Status<br>Register   | 02H             | Yes                                   | -                                                                                                                                                                                                 |

| Read OCD Counter<br>Register  | 03H             | -                                     | -                                                                                                                                                                                                 |

| Write OCD Control<br>Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                                                                                                                                                                          |

| Read OCD Control<br>Register  | 05H             | Yes                                   | -                                                                                                                                                                                                 |

| Write Program Counter         | 06H             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Counter          | 07H             | -                                     | Disabled                                                                                                                                                                                          |

| Write Register                | 08H             | -                                     | Only writes of the peripheral control<br>registers at address F00H-FFH are<br>allowed.<br>Additionally, only the Mass Erase<br>command is allowed to be written to the<br>Flash Control Register. |

| Read Register                 | 09H             | -                                     | Only reads of the peripheral control registers at address F00H-FFH are allowed.                                                                                                                   |

| Write Program Memory          | 0AH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory           | 0BH             | -                                     | Disabled                                                                                                                                                                                          |

| Write Data Memory             | 0CH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Data Memory              | 0DH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory<br>CRC    | 0EH             | -                                     | -                                                                                                                                                                                                 |

| Reserved                      | 0FH             | -                                     | -                                                                                                                                                                                                 |

| Step Instruction              | 10H             | -                                     | Disabled                                                                                                                                                                                          |

| Stuff Instruction             | 11H             | -                                     | Disabled                                                                                                                                                                                          |

177

A "reset and stop" function can be achieved by writing 81H to this register. A "reset and go" function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a "run" function can be implemented by writing 40H to this register.

Table 94. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4       | 3     | 2      | 1        | 0   |

|-------|---------|-------|--------|---------|-------|--------|----------|-----|

| FIELD | DBGMODE | BRKEN | DBGACK | BRKLOOP | BRKPC | BRKZRO | Reserved | RST |

| RESET | 0       |       |        |         |       |        |          |     |

| R/W   |         | R/W   |        |         | R/W   |        |          |     |

#### **DBGMODE—Debug Mode**

Setting this bit to 1 causes the device to enter DEBUG mode. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.

0 = The Z8 Encore! XP F0822 Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F0822 Series device is in DEBUG mode.

#### **BRKEN**—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves like an NOP instruction. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRK-LOOP bit.

0 = BRK instruction is disabled.

1 = BRK instruction is enabled.

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

#### **BRKLOOP**—Breakpoint Loop

This bit determines what action the OCD takes when a BRK instruction is decoded if breakpoints are enabled (BRKEN is 1). If this bit is 0, then the DBGMODE bit is automatically set to 1 and the OCD enter DEBUG mode. If BRKLOOP is set to 1, then the eZ8 CPU loops on the BRK instruction.

0 = BRK instruction sets DBGMODE to 1.

1 = eZ8 CPU loops on BRK instruction.

#### **BRKPC—Break when PC == OCDCNTR**

If this bit is set to 1, then the OCDCNTR register is used as a hardware breakpoint. When the program counter matches the value in the OCDCNTR register, DBGMODE is automatically set to 1. If this bit is set, the OCDCNTR register does not count when the CPU is running.

0 = OCDCNTR is setup as counter

1 = OCDCNTR generates hardware break when PC == OCDCNTR

#### BRKZRO—Break when OCDCNTR == 0000H

If this bit is set, then the OCD automatically sets the DBGMODE bit when the OCD-CNTR register counts down to 0000H. If this bit is set, the OCDCNTR register is not reset when the part leaves DEBUG Mode.

0 = OCD does not generate BRK when OCDCNTR decrements to 0000H 1 = OCD sets DBGMODE to 1 when OCDCNTR decrements to 0000H

#### Reserved

These bits are reserved and must be 0.

#### **RST**—Reset

Setting this bit to 1 resets the Z8 Encore! XP<sup>®</sup> F0822 Series device. The device goes through a normal POR sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 when the reset finishes.

0 = No effect.

1 = Reset the Z8 Encore! XP F0822 Series device.

#### **OCD Status Register**

The OCD Status register reports status information about the current state of the debugger and the system.

| BITS  | 7    | 6    | 5    | 4        | 3 | 2 | 1 | 0 |  |  |  |

|-------|------|------|------|----------|---|---|---|---|--|--|--|

| FIELD | IDLE | HALT | RPEN | Reserved |   |   |   |   |  |  |  |

| RESET |      |      |      | 0        |   |   |   |   |  |  |  |

| R/W   | R    |      |      |          |   |   |   |   |  |  |  |

#### Table 95. OCD Status Register (OCDSTAT)

#### **IDLE—CPU Idling**

This bit is set if the part is in DEBUG mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.

0 = The eZ8 CPU is running.

1 = The eZ8 CPU is either stopped or looping on a BRK instruction.

#### HALT—HALT Mode

- 0 = The device is not in HALT mode.

- 1 = The device is in HALT mode.

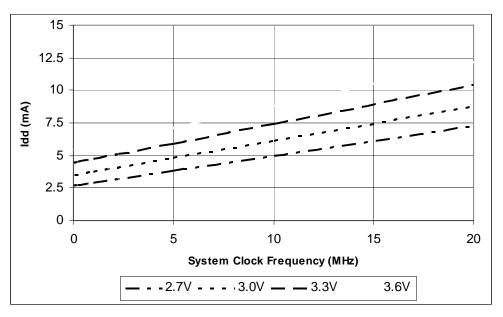

Figure 41. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

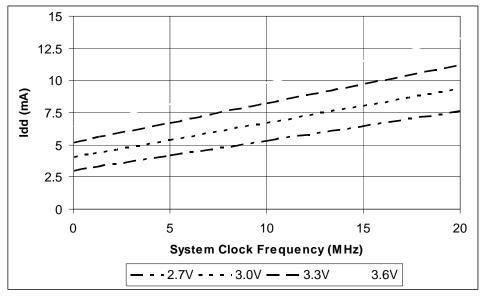

Figure 42 displays the maximum active mode current consumption across the full operating temperature range of the device and versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 42. Maximum Active Mode I<sub>DD</sub> Versus System Clock Frequency

189

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

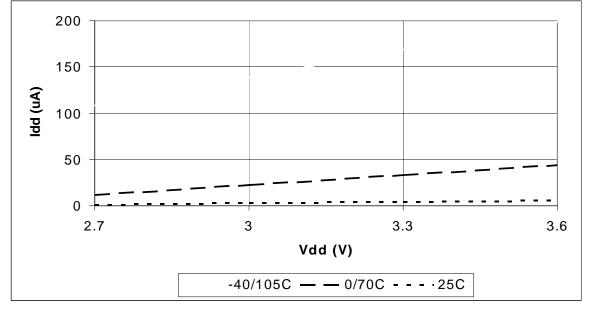

Figure 46. Maximum STOP Mode  $\mathrm{I}_{\mathrm{DD}}$  with VBO Disabled versus Power Supply Voltage

212

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                   |  |  |  |  |  |  |

|--------|------------------------------|--|--|--|--|--|--|

| dst    | Destination Operand          |  |  |  |  |  |  |

| src    | Source Operand               |  |  |  |  |  |  |

| @      | Indirect Address Prefix      |  |  |  |  |  |  |

| SP     | Stack Pointer                |  |  |  |  |  |  |

| PC     | Program Counter              |  |  |  |  |  |  |

| FLAGS  | Flags Register               |  |  |  |  |  |  |

| RP     | Register Pointer             |  |  |  |  |  |  |

| #      | Immediate Operand Prefix     |  |  |  |  |  |  |

| В      | Binary Number Suffix         |  |  |  |  |  |  |

| %      | Hexadecimal Number<br>Prefix |  |  |  |  |  |  |

| Н      | Hexadecimal Number<br>Suffix |  |  |  |  |  |  |

|        |                              |  |  |  |  |  |  |

#### Table 116. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

dst m dst + src

indicates the source data is added to the destination data and the result is stored in the destination location.

## **Ordering Information**

Order Z8 Encore! XP F0822 Series from Zilog<sup>®</sup>, using the following part numbers. For more information regarding ordering, consult your local Zilog sales office. Zilog website at <u>www.zilog.com</u> lists all regional offices and provides additional Z8 Encore! XP product information.

| Jaq<br>G<br>E<br>N<br>Z<br>Z8F08xx with 8 KB Flas | ч<br>sel<br>H, 10-Bit | Me<br>We<br>Analog | of I/O Lines | Interrupts | D 16-Bit Timers w/PWM | 10-Bit A/D Channels | 1 <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

|---------------------------------------------------|-----------------------|--------------------|--------------|------------|-----------------------|---------------------|------------------|-----|-----------------|---------------------|

| Standard Temperature: 0                           | °C to 70              | °C                 |              |            |                       |                     |                  |     |                 |                     |

| Z8F0821HH020SC                                    | 8 KB                  | 1 KB               | 11           | 16         | 2                     | 2                   | 1                | 0   | 1               | SSOP 20-pin package |

| Z8F0821PH020SC                                    | 8 KB                  | 1 KB               | 11           | 16         | 2                     | 2                   | 1                | 0   | 1               | PDIP 20-pin package |

| Z8F0822SJ020SC                                    | 8 KB                  | 1 KB               | 19           | 19         | 2                     | 5                   | 1                | 1   | 1               | SOIC 28-pin package |

| Z8F0822PJ020SC                                    | 8 KB                  | 1 KB               | 19           | 19         | 2                     | 5                   | 1                | 1   | 1               | PDIP 28-pin package |

| Extended Temperature: -40° to +105°C              |                       |                    |              |            |                       |                     |                  |     |                 |                     |

| Z8F0821HH020EC                                    | 8 KB                  | 1 KB               | 11           | 16         | 2                     | 2                   | 1                | 0   | 1               | SSOP 20-pin package |

| Z8F0821PH020EC                                    | 8 KB                  | 1 KB               | 11           | 16         | 2                     | 2                   | 1                | 0   | 1               | PDIP 20-pin package |

| Z8F0822SJ020EC                                    | 8 KB                  | 1 KB               | 19           | 19         | 2                     | 5                   | 1                | 1   | 1               | SOIC 28-pin package |

| Z8F0822PJ020EC                                    | 8 KB                  | 1 KB               | 19           | 19         | 2                     | 5                   | 1                | 1   | 1               | PDIP 28-pin package |