# E·XFL

### Zilog - Z8F0411HH020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 11                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0411hh020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Signal and Pin Descriptions

Z8 Encore! X<sup>fp</sup> FO822 Series products are available in a variety of packages, styles, and pin configurations. This chapter describigs allseand available pin configurations for each of the package styles. For information gethe physical page specifications, see Packaging page 233.

### Available Packages

Table 2identifies the package styles available device virit ZA Encore! XP F0822 Series product line.

| Part Number | 10-Bit ADC | 20-Pin SSOPand PDIP | 28-Pin SOIC and PDIP |

|-------------|------------|---------------------|----------------------|

| Z8F0822     | Yes        |                     | Х                    |

| Z8F0821     | Yes        | Х                   |                      |

| Z8F0812     | No         |                     | Х                    |

| Z8F0811     | No         | Х                   |                      |

| Z8F0422     | Yes        |                     | Х                    |

| Z8F0421     | Yes        | Х                   |                      |

| Z8F0412     | No         |                     | Х                    |

| Z8F0411     | No         | Х                   |                      |

Table 2. Z8 Encore! XP F0822 Series Package Options

## **Pin Configurations**

Figure 2througRigure 5display the pin configurations for all of the packages available in Z8 Encore! XP FO822 SeriesTable 4for a description of the signals.

Note: The analog input alternate functions (ANAx) are not available on Z<sup>§</sup> E0832 ℓ. XP Series devices.

>

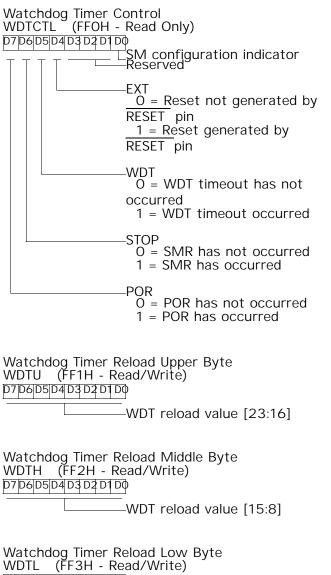

D7D6D5D4D3D2D1D0

WDT reload value [7:0]

## Port A C Output Data Register

The Port A C Output Data Registable (23) controls the output data to the pins.

## Table 23. Port A C Output Data Register (ROUT)

| BITS  | 7     | 6     | 5     | 4        | 3        | 2     | 1     | 0     |

|-------|-------|-------|-------|----------|----------|-------|-------|-------|

| FIELD | POUT7 | POUT6 | POUT5 | POUT4    | POUT3    | POUT2 | POUT1 | POUTO |

| RESET |       | 0     |       |          |          |       |       |       |

| R/W   |       | R/W   |       |          |          |       |       |       |

| ADDR  |       |       |       | FD3H, FD | 7H, FDBH |       |       |       |

## POUT[7:0] Port Output Data

These bits contain the data to be drever ontopins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternat function operation.

- O = Drive a logical O (Low).

- 1 = Drive a logical 1 (High). High valuet idmoen if the drain has been disabled by setting the corresponding pour Control Register bit to 1.

UORXI UART O Receiver Interrupt Request

0 = No interrupt requestorising efor the UART O receiver.

1 = An interrupt request from RTeCUAeceiver is awaiting service.

UOTXI UART O Transmitter Interrupt Request

O = No interrupt request is pending for the UART O transmitter.

1 = An interrupt request from RTeCUPransmitter is awaiting service.

I 2CI I <sup>2</sup>C Interrupt Request

$O = No interrupt request is pending^{2} for the I$

1 = An interrupt request from Ctilsealwaiting service.

SPII SPI Interrupt Request

O = No interrupt request is pending for the SPI.

1 = An interrupt request from the SPI is awaiting service.

ADCI ADC Interrupt Request

O = No interrupt request is pending for the ADC.

1 = An interrupt request from the ADC is awaiting service.

### Interrupt Request 1 Register

The Interrupt Request 1 (IRQ1) Register 25 stores interrupt requests for both vectored and polled interrupts. When ais equess the to the rimpt controller, the corresponding bit in the IRQ1 register described. If interrupts are globally enabled (vectored interrupts), the interrupt consts of searn interrupt request to the eZ8 CPU. If interrupts are globally disabledd (inditerrupts), the eZ8 CPU reads the IRQ1 Register to determine if interrupt requests are pending.

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| FIELD | PA7I | PA6I | PA5I | PA4I | PA3I | PA2I | PA1I | PAOI |

| RESET |      | 0    |      |      |      |      |      |      |

| R/W   |      | R/W  |      |      |      |      |      |      |

| ADDR  |      | FC3H |      |      |      |      |      |      |

Table 26. Interrupt Request 1 Register (IRQ1)

PAxI Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin

1 = An interrupt request from GPIO Pontia pinaiting service.

Where x indicates the specific GPIO pin number (0 through 7).

6. Write to the Timer Control Regisstread the timer and initiate counting.

In CONTINUOUS mode, the system clocky slypeovides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s)= Reload ValuexPrescale

System Clock Frequency (Hz)

If an initial starting value otheodom this loaded into the Timer High and Low Byte Registers, the ONE-SHOT mode equation be must be determine the first time-out period.

#### COUNTER Mode

In COUNTER mode, the timerundes input transitions from Daport pin. The timer input is taken from the GPIO Profimeir Input alternate function Profile bit in the Timer Control Register selects whether the course on the rising edge or the falling edge of the Timer Input signa DUN TER mode, the prescaler is disabled.

Caution: The input frequency of the Timer Inputmsignalot exceed one-fourth system clock frequency.

Upon reaching the Reload variated in the Timer Reload High and Low Byte Registers, the timer generates an interneupbunt value in the Timer High and Low Byte Registers is reset too01H and counting resumes. Also, Tinthe Output alternate function is enabled, the Timer Output pin chang (fronte to High or from High to Low) at timer Reload.

Follow the steps below for config**timegr** for COUNTER mode and initiating the count:

1. Write to the Timer Control Register to:

Disable the timer

Configure the timer for COUNTER mode.

Select either the rising edge or falling **edg**eTimer Input signal for the count. This also sets the initial logic level (Higow) for the Timer Output alternate function. However, the Timer Output for does not have to be enabled.

- 2. Write to the Timer High and Low BysteeRegio set the starting count value. This only affects the first pass in COUNTER. After the first timer Reload in COUNTER mode, counting always begins at the reset DOOLULE Generally, in COUNTER mode the Timer High and Low Registers must be written with the value0001H

- 3. Write to the Timer Reload High an Byttew Registers to set the Reload value.

- 3. Write to the PWM High and Lowregyisters to set the PWM value.

- 4. Write to the Timer Reload High an Byttew Registers to set the Reload value (PWM period). The Reload values travely greater than the PWM value.

- 5. If required, enable the **timer**rupt and set the timerupt registers.

- 6. Configure the associated GPIO poot phe Timer Output alternate function.

- 7. Write to the Timer Control Registreabte the timer and initiate counting.

The PWM period is given by the following equation.

PWM Period (s)= Reload ValuexPrescale

System Clock Frequency (Hz)

If an initial starting value other OCCONDEM is loaded into the Timer High and Low Byte Registers, the ONE-SHOT mode equations and disto determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWMightpinte to the total period is given by

PWM Output High Time Ratio (%)

Reload Value

PWM Value

x100

Reload Value

Reload Value

x100

x100

If TPOL is set to 1, the ratio of the PWNHightpionte to the total period is given by

PWM Output High Time Ratio (%) PWM Value x100 Reload Value

#### CAPTURE Mode

In CAPTURE mode, the current timer counctisvate corded with the desired external Timer Input transition occurs. The Capture advants written to the Timer PWM High and Low Byte Registers. The timplet is the system clock TPM tebit in the Timer Control Register determines if the Capture not cruiting edge or a falling edge of the Timer Input signal. When the Capture event arcting the rupt is generated and the timer continues counting.

The timer continues **cing**nup to the 16-bit Reload statued in the Timer Reload High and Low Byte registers. Upon reabbin Repload luce, the time generates an interrupt and continues counting.

Follow the steps below for configuiring for CAPTURE mode and initiating the count:

Write to the Timer Control Register to: Disable the timer

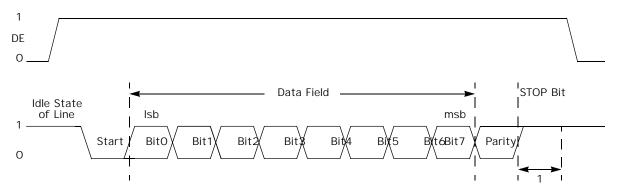

Enable signal asserts at least one UARTido tape no greater than two UART bit periods before the Start bit signitrand. This format allows up sime to enable the transceiver. The Driver Enable signal deasses the total action of the transceiver before disabling it, also where a bility determine if another character follows the current character. In the vertice to back chara (newsdata must be written to the Transmit Data Register before the previous formed to the UART Control DE signal is not deasserted between terms and the DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Starst dup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}} \le \text{DE to Start Bit Setup Time } (s) \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

### UART Interrupts

The UART features separate interruptstfonstmitter and theivercen addition, when the UART primary funcation is disabled, the BRG also functions as a basic timer with interrupt capability.

### Transmitter Interrupts

The transmitter generates a single invitementative Transmit Detergister Empty bit (TDRE) is set to 1. This indicates the entropy to accept new data for transmission. The TDRE interrupt occursh after ansmit shift register has shifted the first bit of data out. At this point, sime TD and Register canvoide ten with the next character to send. This provides 7 bit of entropy to load the Transmit Data Register before the Transmit shift register coshifted she current character. Writing to the UART Transmit Data Register cleared to 0.

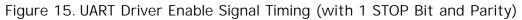

## Serial Peripheral Interface

The Serial Peripheral Inter(aRe) is a synchronous inderfallowing several SPI-type devices to be intercotred. SPI-compatible devines. Let Berroms, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

Full-duplex, synchronous, and character-oriented communication

Four-wire interface

Data transfers rates up to a maximum of one-half the system clock frequency

Error detection

Dedicated Baud Rate Generator

The SPI is not available in 20-pin package devices.

## Architecture

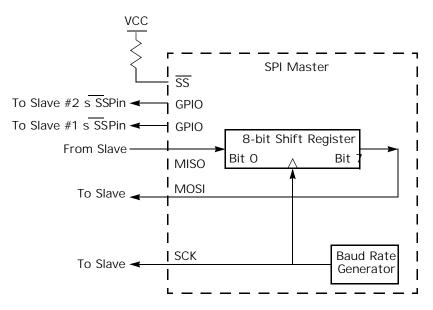

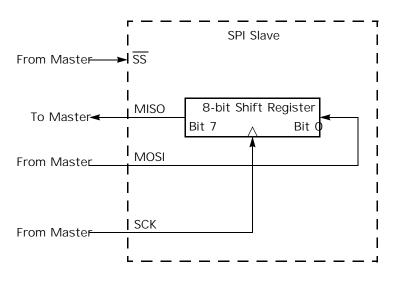

The SPI is be configureditate a Master (in single or multi-master systems) or a Slave as displayed Frigure 20througFrigure 2.2

Figure 20. SPI Configured as a Master in a Single Master, Single Slave System

Figure 21. SPI Configured as a Master in a Single Master, Multiple Slave System

Figure 22. SPI Configured as a Slave

## Operation

The SPI is a full-duplex, synchronous, and tel mariented channel that supports a fourwire interface (serial clock, transmit, receive and Slave select). The SPI block consists of transmit/receive shift eegas Baud Rate (clock) and a control unit.

| TXRXSTATE | State Description                                                                       |

|-----------|-----------------------------------------------------------------------------------------|

| 1_0111    | 10-bit addressing: Bit 0 (R/W) of 1st address byte                                      |

| 1_1000    | 10-bit addressing: Acknowledge state for 1st address byte                               |

| 1_1001    | 10-bit addressing: Bit 7 of 2nd address byte<br>7-bit addressing: Bit 7 of address byte |

| 1_1010    | 10-bit addressing: Bit 6 of 2nd address byte<br>7-bit addressing: Bit 6 of address byte |

| 1_1011    | 10-bit addressing: Bit 5 of 2nd address byte<br>7-bit addressing: Bit 5 of address byte |

| 1_1100    | 10-bit addressing: Bit 4 of 2nd address byte<br>7-bit addressing: Bit 4 of address byte |

| 1_1101    | 10-bit addressing: Bit 3 of 2nd address byte<br>7-bit addressing: Bit 3 of address byte |

| 1_1110    | 10-bit addressing: Bit 2 of 2nd address byte<br>7-bit addressing: Bit 2 of address byte |

| 1_1111    | 10-bit addressing: Bit 1 of 2nd address byte<br>7-bit addressing: Bit 1 of address byte |

|           |                                                                                         |

## I<sup>2</sup>C Diagnostic Control Register

The PC Diagnostic registEable 7 provides control over diagnostic modes. This register is a read/write register usediagnostics.

|                    | 2             |                         |  |

|--------------------|---------------|-------------------------|--|

| <b>T I I 7 / I</b> |               |                         |  |

| 1000 /6 1          | 14 INDADACTIC | L'ANTRAL DAGISTAR       |  |

|                    |               | <b>Control Register</b> |  |

|                    |               |                         |  |

|                    |               |                         |  |

| BITS  | 7 | 7     6     5     4     3     2     1     C |  |  |  |  |  |      |

|-------|---|---------------------------------------------|--|--|--|--|--|------|

| FIELD |   | Reserved                                    |  |  |  |  |  | DIAG |

| RESET |   | 0                                           |  |  |  |  |  |      |

| R/W   |   | R R/W                                       |  |  |  |  |  | R/W  |

| ADDR  |   | F56H                                        |  |  |  |  |  |      |

DIAG = Diagnostic Contribit Selects read back value of the Baud Rate Reload registers.

- O = Normal mode. Reading the Baud Rate High and Low Byte registers returns the baud rate reload value.

- 1 = Diagnostic mode. Reading the Baud Rate High and Low Byte registers returns the baud rate counter value.

## ADCD\_L ADC Data Low Bits

These are the least significant two bits diffith DC output. These bits are undefined after a Reset.

Reserved These bits are reserved and are always undefined.

## Z8 Encore! XP<sup>fi</sup> F0822 Series Product Specification

154

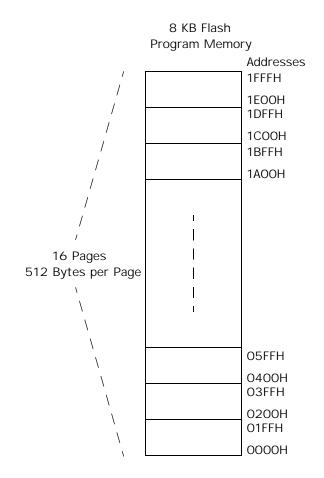

Figure 33. Flash Memory Arrangement

## Information Area

Table 82on page 155 describes the Z8 Enc<sup>f</sup>or E0 & P2 Series Information Area. This 512-byte Information Area is seed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area page into Flash Memory and overlays the 512 bytes at addresses to FFFH. When the Information Area access is enabled, LDC instructions return flatma the Information Area! icoBtruction fetches always comes from Flash Memory regardles shoft the tion Area access bit. Access to the Information Area is read-only.

## Debug Mode

The operating characteristics of the Z8  $Entite{b08}22$  Series devices in DEBUG mode are:

The eZ8 CPU fetch unit stops, idling  $\mathbb{R} = \mathbb{R} + \mathbb{R}$  is the OCD to execute specific instructions.

The system clock operates unless in STOP mode.

All enabled on-chip peripheoplerate unless in STOP mode.

Automatically exits HALT mode.

Constantly refreshes the the age Timer, if enabled.

#### Entering Debug Mode

The device enters DEBUG mode following any of the following operations:

Writing the BGMODEbit in the OCD Control Register to 1 using the OCD interface.

eZ8 CPU execution of a BRK (Breakpoint) instruction.

Match of PC to OCDCNTR register (when enabled)

OCDCNTR register decrements to OOOOH (when enabled)

If the DBG pin is Low when the device  $\ensuremath{\texttt{Resides}}$  , the OCD automatically puts the device into DEBUG mode.

Exiting Debug Mode

The device exits DEBUG mode following of the following operations:

Clearing the BGMODE bit in the OCD Control Register to O.

Power-On Reset

Voltage Brownout reset

Asserting the set pin Low to initiate a Reset.

Driving the BG pin Low while the devis in STOP mode initiates a System Reset.

#### OCD Data Format

The OCD interface uses the asynchronofous modata defined for RS-232. Each character is transmitted as 1 Start bit, is solated as 1 Start bit, is solated by the set of the set o

| START | DO | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-------|----|----|----|----|----|----|----|----|------|

|-------|----|----|----|----|----|----|----|----|------|

Figure 40. OCD Data Format

**OCDCNTR Register**

The OCD contains a multipurpose 16-bterCRegister. It can be used for the following:

Count system clock cycles between Breakpoints.

Generate a BRK when it counts down to zero.

Generate a BRK when itsevahatches the Program Counter.

When configured as a counter, the OCDCNTR register starts counting when the OCD leaves DEBUG mode and stops countingtvements DEBUG mode again or when it reaches the maximum counterford. The OCDCNTR register automatically resets itself toOOOOHwhen the OCD exits DEBUG modeisfconfigured to count clock cycles between breakpoints.

Caution: The OCDCNTR register is used by many of the OCD commands. It counts the number of bytes for the register and memory read/write commands. It holds the residual value when **giengeth**e CRC. Therefore, if the OCD-CNTR is being used to generate at BRKalue should be written as a last step before leaving DEBUG mode.

Since this register is overwritten by QatDoaommands, it shownly be used to generate temporary breakpoints, such as symplace instruction running to a specific instruction and stopping.

## On-Chip Debugger Commands

The host communicatesetOCD by sending OCD commands using the DBG interface. During normal operation, only a subtret OCD commands are available. In DEBUG mode, all OCD commands become availables time user code and control registers are protected by programming the Read Protect OPP) on the iter and control registers are protected in memory being read out of the Z8 Encore! XP FO822 Series products. When this option is enabled of the OCD commands are disabled. Table 93on page 177 contains a summary of the OCD commands. Each OCD command is described further in the bullistelt also lists the commonstant operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

## eZ8 CPU Instruction Classes

eZ8 CPU instructions are dividedidaaldy into the following groups:

Arithmetic

Bit Manipulation

Block Transfer

CPU Control

Load

Logical

Program Control

Rotate and Shift

Tables 118throughable 125on page 218 contain threaddisches belonging to each group and the number of operands requised fostruction. Somseructions appear in more than one table as these instruction one address a subset of more than one category. Within these tables, the source is piecentified as src, the destination operand is dst and a condition code is cc.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| СРХ      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

| MULT     | dst      | Multiply                                     |

|          |          |                                              |

Table 118. Arithmetic Instructions

215

Table 118. Arithmetic Instructions (Continued)

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

Table 119. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | (           | Complement Carry Flag                                |

| RCF      | F           | Reset Carry Flag                                     |

| SCF      | S           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| TM       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

Table 120. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| Assembly     | Symbolic                                                                                                                      | Address<br>Mode |     | Opcode(s) | Flags |   |   |   |   |   | - Fetch | Instr.         |        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------|-------|---|---|---|---|---|---------|----------------|--------|

| Mnemonic     | Operation                                                                                                                     | dst             | src | (Hex)     |       | Ζ | S | ١ | / | D | Н       |                | Cycles |

| DECW dst     | dst← dst - 1                                                                                                                  | RR              |     | 80        | -     | , | * | * | * |   | -       | - 2            | 5      |

|              |                                                                                                                               | IRR             |     | 81        |       |   |   |   |   |   |         | 2              | 6      |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                                      |                 |     | 8F        | -     | - | - | - | - | - |         | - 1            | 2      |

| DJNZ dst, RA | dst← dst 1<br>if ds≢ 0<br>PC← PC + X                                                                                          | r               |     | OA-FA     | -     | - | - |   | - | - | _       | · 2            | 3      |

| EI           | $IRQCTL[7] \leftarrow 1$                                                                                                      |                 |     | 9F        | -     | - | - |   | - | - | -       | - 1            | 2      |

| HALT         | HALT Mode                                                                                                                     |                 |     | 7F        | -     | - | - |   | - | - | -       | · 1            | 2      |

| INC dst      | dst⊱ dst + 1                                                                                                                  | R               |     | 20        | -     | ; | * | * | * | ; | -       | - 2            | 2      |

|              |                                                                                                                               | IR              |     | 21        |       |   |   |   |   |   |         | 2              | 3      |

|              |                                                                                                                               | r               |     | OE-FE     |       |   |   |   |   |   |         | 1              | 2      |

| INCW dst     | dst⊱dst + 1                                                                                                                   | RR              |     | AO        | -     | * |   | * | * |   | -       | - 2            | 5      |

|              |                                                                                                                               | IRR             |     | A1        |       |   |   |   |   |   |         | 2              | 6      |

| IRET         | $FLAGS \leftarrow @SP$<br>$SP \leftarrow SP + 1$<br>$PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$<br>$IRQCTL[7] \leftarrow 1$ |                 |     | BF        | *     | * | * |   | * | * | *       | <sup>5</sup> 1 | 5      |

| JP dst       | PC← dst                                                                                                                       | DA              |     | 8D        | -     | - | - | - | - | - |         | - 3            | 2      |

|              |                                                                                                                               | IRR             |     | C4        |       |   |   |   |   |   |         | 2              | 3      |

| JP cc, dst   | if cc is true<br>PC← dst                                                                                                      | DA              |     | OD-FD     | -     | - | - |   | - | - | -       | 3              | 2      |

| JR dst       | $PC \leftarrow PC + X$                                                                                                        | DA              |     | 8B        | -     | - | - | - | - | - |         | - 2            | 2      |

| JR cc, dst   | if cc is true<br>PC← PC + X                                                                                                   | DA              |     | OB-FB     | -     | - | - |   | - | - | -       | 2              | 2      |

## Table 126. eZ8 CPU Instruction Summary (Continued)

| Assembly      | Symbolic                                                                           | Address<br>Mode |     | _ Opcode(s) |   |   | Fla | gs  | - Fetch | Instr. |        |        |

|---------------|------------------------------------------------------------------------------------|-----------------|-----|-------------|---|---|-----|-----|---------|--------|--------|--------|

| Mnemonic      | Operation                                                                          | dst             | src | (Hex)       | С | Ζ | S   | V   | D       | Н      | Cycles | Cycles |

| POPX dst      | dst← @SP<br>SP ← SP + 1                                                            | ER              |     | D8          | - | - | -   | -   | -       | -      | 3      | 2      |

| PUSH src      | $SP \leftarrow SP = 1$                                                             | R               |     | 70          | - | - | -   | -   | -       | -      | 2      | 2      |

|               | @SP ← src                                                                          | IR              |     | 71          |   |   |     |     |         |        | 2      | 3      |

| PUSHX src     | $\begin{array}{rrr} SP \leftarrow SP & 1 \\ @SP & \leftarrow src \end{array}$      | ER              |     | C8          | - | - | -   | -   | -       | -      | 3      | 2      |

| RCF           | $C \leftarrow O$                                                                   |                 |     | CF          | 0 | - | -   | -   | -       | -      | 1      | 2      |

| RET           | $\begin{array}{l} PC \ \leftarrow @SP \\ SP \ \leftarrow \ SP \ + \ 2 \end{array}$ |                 |     | AF          | - | - | -   | -   | -       | -      | 1      | 4      |

| RL dst        | _ []                                                                               | R               |     | 90          | * | * | *   | ; , | *       | -      | - 2    | 2      |

|               | dst                                                                                | IR              |     | 91          |   |   |     |     |         |        | 2      | 3      |

| RLC dst       |                                                                                    | R               |     | 10          | * | * | *   | *   | · .     |        | - 2    | 2      |

|               | C < D7D6D5D4D3D2D1DC<br>dst                                                        | IR              |     | 11          |   |   |     |     |         |        | 2      | 3      |

| RR dst        |                                                                                    | R               |     | EO          | * | * | *   | *   | -       |        | - 2    | 2      |

|               | •D7D6D5D4D3D2D1D0 ►                                                                | IR              |     | E1          |   |   |     |     |         |        | 2      | 3      |

| RRC dst       |                                                                                    | R               |     | СО          | * | * | *   | *   | -       |        | - 2    | 2      |

|               | • <u>D7D6D5D4D3D2D1D0</u> >C<br>dst                                                | IR              |     | C1          |   |   |     |     |         |        | 2      | 3      |

| SBC dst, src  | dsŧ– dst src - C                                                                   | r               | r   | 32          |   | * | *   | *   | *       | 1      | * 2    |        |

|               | -                                                                                  | r               | lr  | 33          |   |   |     |     |         |        | 2      | 4      |

|               | -                                                                                  | R               | R   | 34          |   |   |     |     |         |        | 3      | 3      |

|               | _                                                                                  | R               | IR  | 35          |   |   |     |     |         |        | 3      | 4      |

|               | _                                                                                  | R               | IM  | 36          |   |   |     |     |         |        | 3      | 3      |

|               |                                                                                    | IR              | IM  | 37          |   |   |     |     |         |        | 3      | 4      |

| SBCX dst, sro | c dste⊢dst src -C                                                                  | ER              | ER  | 38          | * | · | k   | *   | *       | 1      | * 4    | 3      |

|               |                                                                                    | ER              | IM  | 39          |   |   |     |     |         |        | 4      | 3      |

## Table 126. eZ8 CPU Instruction Summary (Continued)

## Ordering Information

Order Z8 Encore! XR0822 Series from Žilogsing the following part nurfibers more information regardingriogdeconsult your local Zilog sales office. Zilog website at<u>www.zilog.co</u>rfists all regional offices and provides additional Z8 Encore! XP product information.

|                                                             |           |          |    |             | 5                   |                     |                         |                 |             |                     |  |

|-------------------------------------------------------------|-----------|----------|----|-------------|---------------------|---------------------|-------------------------|-----------------|-------------|---------------------|--|

| Part Number                                                 | Flash     | <u> </u> |    | sidnilailli | 16-Bit Timers w/PWM | 10-Bit A/D Channels | 1 <sup>2</sup> C<br>sdi | UARTs with Irda | Descrintion |                     |  |

| Z8F08xx with 8 KB Flash, 10-Bit Analog-to-Digital Converter |           |          |    |             |                     |                     |                         |                 |             |                     |  |

| Standard Temperature:                                       | 0 °C to 7 | ′0 ℃     |    |             |                     |                     |                         |                 |             |                     |  |

| Z8F0821HH020SC                                              | 8 KB      | 1 KB     | 11 | 16          | 2                   | 2                   | 1                       | 0               | 1           | SSOP 20-pin package |  |

| Z8F0821PH020SC                                              | 8 KB      | 1 KB     | 11 | 16          | 2                   | 2                   | 1                       | 0               | 1           | PDIP 20-pin package |  |

| Z8F0822SJ020SC                                              | 8 KB      | 1 KB     | 19 | 19          | 2                   | 5                   | 1                       | 1               | 1           | SOIC 28-pin package |  |

| Z8F0822PJ020SC                                              | 8 KB      | 1 KB     | 19 | 19          | 2                   | 5                   | 1                       | 1               | 1           | PDIP 28-pin package |  |

| Extended Temperature: -40° to +105°C                        |           |          |    |             |                     |                     |                         |                 |             |                     |  |

| Z8F0821HH020EC                                              | 8 KB      | 1 KB     | 11 | 16          | 2                   | 2                   | 1                       | 0               | 1           | SSOP 20-pin package |  |

| Z8F0821PH020EC                                              | 8 KB      | 1 KB     | 11 | 16          | 2                   | 2                   | 1                       | 0               | 1           | PDIP 20-pin package |  |

| Z8F0822SJ020EC                                              | 8 KB      | 1 KB     | 19 | 19          | 2                   | 5                   | 1                       | 1               | 1           | SOIC 28-pin package |  |

| Z8F0822PJ020EC                                              | 8 KB      | 1 KB     | 19 | 19          | 2                   | 5                   | 1                       | 1               | 1           | PDIP 28-pin package |  |

Z8 Encore! XP<sup>fi</sup> F0822 Series Product Specification

248

rotate left through 22178y rotate rig2118 rotate rig2118 RP 212 RR 211, 218 rr 211 RRC 218

## S

SBC 215 SCF 215 216 SCK 115 SDA and SCL (IrDA) signal628 second opcode map after282H serial clock15 serial peripheral interface (SP3) set carry flag 5 216 set register poin2166 shift right arithm@ti8 shift right logica18 signal descriptions single-shot conversion (ADC) SIO 5 slave data transfer formats132C) slave seledt16 software tr2p7 source opera2d2 SP 212 SPL architectufe 3 baud rate generatized baud rate high and low byte ragister clock phase16 configured as slaMe4 control registle22 control register definitions data registe21 error detection19 interrupt 519 mode fault errbr9 mode regist€24 multi-master operation8 operation14

overrun erron9 signals115 single master, multiple slave system single master, single slave system status register3 timing, PHASE = 017timing, PHASE=1118 SPI controller signals SPI mode (SPIMODE)24 SPIBRH register25 SPIBRL register 26 SPICTL register 22 SPIDATA register 21 SPIMODE register24 SPISTAT register 23 SRA 218 src212 SRL 218 SRP 216 SS, SPI signal15 stack point@12 status register, 120 STOP 216 stop mode5 216 stop mode recovery sources 3 using a GPIO port pin trans#t4on using watch-dog timer time4out SUB 215 subtrac215 subtract - extended addressing subtract with carts subtract with carry - extended ad 21 essing **SUBX 215 SWAP 218** swap nibbles18 symbols, addition212 system and core resolutions

## Т

TCM 215 TCMX 215 test complement under 20125sk