Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0411ph020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| OCD Interface                                           | 1 |

|---------------------------------------------------------|---|

| Debug Mode                                              | 3 |

| OCD Data Format 173                                     | 3 |

| OCD Auto-Baud Detector/Generator 174                    | 4 |

| OCD Serial Errors 174                                   |   |

| Breakpoints                                             |   |

| OCDCNTR Register                                        |   |

| On-Chip Debugger Commands 176                           |   |

| On-Chip Debugger Control Register Definitions           |   |

| OCD Control Register                                    |   |

| OCD Status Register                                     |   |

| Electrical Characteristics                              |   |

| Absolute Maximum Ratings                                |   |

| DC Characteristics                                      |   |

| AC Characteristics                                      |   |

| On-Chip Peripheral AC and DC Electrical Characteristics |   |

| General Purpose I/O Port Input Data Sample Timing       |   |

| General Purpose I/O Port Output Timing                  |   |

| On-Chip Debugger Timing                                 |   |

| SPI MASTER Mode Timing                                  |   |

| SPI SLAVE Mode Timing                                   |   |

| I2C Timing                                              |   |

| eZ8 CPU Instruction Set                                 |   |

| Assembly Language Programming Introduction              |   |

| Assembly Language Programming infoduction               |   |

| eZ8 CPU Instruction Notation                            |   |

| Condition Codes                                         |   |

| eZ8 CPU Instruction Classes                             |   |

| eZ8 CPU Instruction Summary                             |   |

| Flags Register                                          |   |

| Opcode Maps                                             |   |

| Packaging                                               |   |

| Ordering Information                                    |   |

| Part Number Suffix Designations                         |   |

| Index                                                   |   |

| Customer Support                                        |   |

|                                                         |   |

Table of Contents

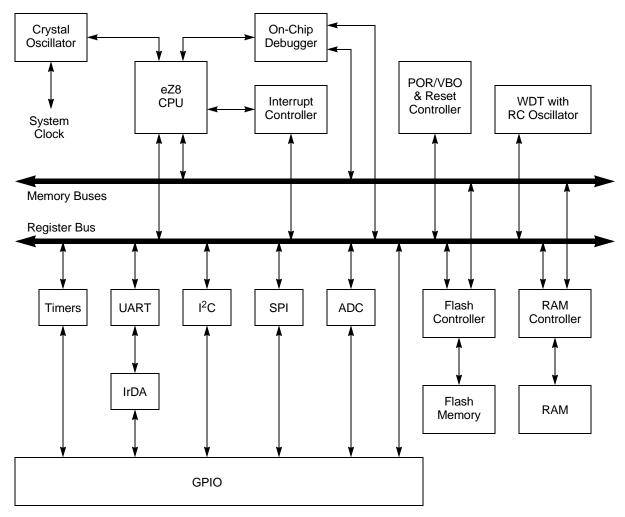

## **Block Diagram**

Figure 1 displays the block diagram of the architecture of Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0822 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0822 Series Block Diagram

## **CPU and Peripheral Overview**

#### eZ8 CPU Features

Zilog's latest eZ8 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{$ <sup>®</sup> instruction set.

7

## **Signal and Pin Descriptions**

Z8 Encore! XP<sup>®</sup> F0822 Series products are available in a variety of packages, styles, and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information regarding the physical package specifications, see Packaging on page 233.

#### **Available Packages**

Table 2 identifies the package styles available for each device within Z8 Encore! XP F0822 Series product line.

| Part Number | 10-Bit ADC | 20-Pin SSOP and PDIP | 28-Pin SOIC and PDIP |

|-------------|------------|----------------------|----------------------|

| Z8F0822     | Yes        |                      | Х                    |

| Z8F0821     | Yes        | Х                    |                      |

| Z8F0812     | No         |                      | Х                    |

| Z8F0811     | No         | Х                    |                      |

| Z8F0422     | Yes        |                      | Х                    |

| Z8F0421     | Yes        | Х                    |                      |

| Z8F0412     | No         |                      | Х                    |

| Z8F0411     | No         | Х                    |                      |

|             |            |                      |                      |

Table 2. Z8 Encore! XP F0822 Series Package Options

## **Pin Configurations**

Figure 2 through Figure 5 display the pin configurations for all of the packages available in Z8 Encore! XP F0822 Series. See Table 4 for a description of the signals.

**Note:** *The analog input alternate functions (ANAx) are not available on Z8 Encore! XP*<sup>®</sup> *F0822 Series devices.*

61

Poor coding style that resulting in lost interrupt requests: LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Note:** To avoid missing interrupts, the following style of coding to set bits in the Interrupt Request Registers is recommended

Good coding style that avoids lost interrupt requests: ORX IRQ0, MASK

## **Interrupt Control Register Definitions**

For all interrupts other than the WDT interrupt, the Interrupt Control Registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register (Table 25) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ0 Register to determine if any interrupt requests are pending.

| BITS  | 7        | 6   | 5   | 4     | 3     | 2    | 1    | 0    |  |  |

|-------|----------|-----|-----|-------|-------|------|------|------|--|--|

| FIELD | Reserved | T1I | тоі | U0RXI | U0TXI | I2CI | SPII | ADCI |  |  |

| RESET | 0        |     |     |       |       |      |      |      |  |  |

| R/W   |          | R/W |     |       |       |      |      |      |  |  |

| ADDR  |          |     |     | FC    | 0H    |      |      |      |  |  |

#### Table 25. Interrupt Request 0 Register (IRQ0)

#### Reserved—Must be 0

#### **T1I**—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

#### **T0I**—**Timer 0 Interrupt Request**

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register (Table 27) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ2 Register to determine if any interrupt requests are pending.

## Table 27. Interrupt Request 2 Register (IRQ2)

| BITS  | 7    | 6    | 5     | 4 | 3    | 2    | 1    | 0    |  |  |

|-------|------|------|-------|---|------|------|------|------|--|--|

| FIELD |      | Rese | erved |   | PC3I | PC2I | PC1I | PC0I |  |  |

| RESET | 0    |      |       |   |      |      |      |      |  |  |

| R/W   | R/W  |      |       |   |      |      |      |      |  |  |

| ADDR  | FC6H |      |       |   |      |      |      |      |  |  |

Reserved—Must be 0

#### PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin *x*.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

Where *x* indicates the specific GPIO Port C pin number (0 through 3).

## **IRQ0 Enable High and Low Bit Registers**

The IRQ0 Enable High and Low Bit Registers (Table 29 and Table 30) form a priority encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register. Table 28 describes the priority control for IRQ0.

| Table 28. IRQ0 Enable and Price | ority Encoding |

|---------------------------------|----------------|

|---------------------------------|----------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

where *x* indicates the register bits from 0 through 7.

#### Table 50. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7                                                                                   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|----------|-------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|--|--|

| FIELD    |                                                                                     | WDTH |   |   |   |   |   |   |  |  |  |

| RESET    |                                                                                     | 1    |   |   |   |   |   |   |  |  |  |

| R/W      |                                                                                     | R/W* |   |   |   |   |   |   |  |  |  |

| ADDR     |                                                                                     | FF2H |   |   |   |   |   |   |  |  |  |

| R/W*-Rea | R/W*–Read returns the current WDT count value. Write sets the desired Reload Value. |      |   |   |   |   |   |   |  |  |  |

#### WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

#### Table 51. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7                                                                                   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|----------|-------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|--|--|

| FIELD    |                                                                                     | WDTL |   |   |   |   |   |   |  |  |  |

| RESET    |                                                                                     | 1    |   |   |   |   |   |   |  |  |  |

| R/W      |                                                                                     | R/W* |   |   |   |   |   |   |  |  |  |

| ADDR     |                                                                                     | FF3H |   |   |   |   |   |   |  |  |  |

| R/W*-Rea | R/W*–Read returns the current WDT count value. Write sets the desired Reload Value. |      |   |   |   |   |   |   |  |  |  |

#### WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

- 5. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to step 6. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 6. Write the UART Control 1 Register to select the outgoing address bit:

- Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 7. Write data byte to the UART Transmit Data Register. The transmitter automatically transfers data to the Transmit Shift Register and then transmits the data.

- 8. If required, and multiprocessor mode is enabled, make any changes to the Multiprocessor Bit Transmitter (MPBT) value.

- 9. To transmit additional bytes, return to step 5.

#### **Transmitting Data Using Interrupt-Driven Method**

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Follow the below steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte Registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt Control Registers to enable the UART Transmitter interrupt and set the required priority.

- 5. If MULTIPROCESSOR mode is required, write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions:

- Set the Multiprocessor Mode Select (MPEN) to enable MULTIPROCESSOR mode.

- 6. Write to the UART Control 0 Register to:

- Set the transmit enable (TEN) bit to enable the UART for data transmission

- Enable parity, if required, and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear the CTSE bit to enable or disable control from the remote receiver through the  $\overline{\text{CTS}}$  pin.

- 7. Execute an EI instruction to enable interrupts.

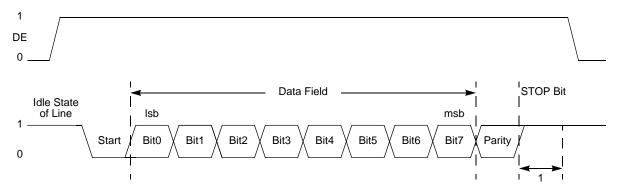

Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This format allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the last STOP bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 15. UART Driver Enable Signal Timing (with 1 STOP Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the BRG also functions as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. At this point, the Transmit Data Register can be written with the next character to send. This provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register (Table 53). The Read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

#### Table 53. UART Receive Data Register (U0RXD)

| BITS  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|-----|---|---|----|----|---|---|---|--|--|

| FIELD | RXD |   |   |    |    |   |   |   |  |  |

| RESET | X   |   |   |    |    |   |   |   |  |  |

| R/W   | R   |   |   |    |    |   |   |   |  |  |

| ADDR  |     |   |   | F4 | 0H |   |   |   |  |  |

#### **RXD**—Receive Data

UART receiver data byte from the RXDx pin

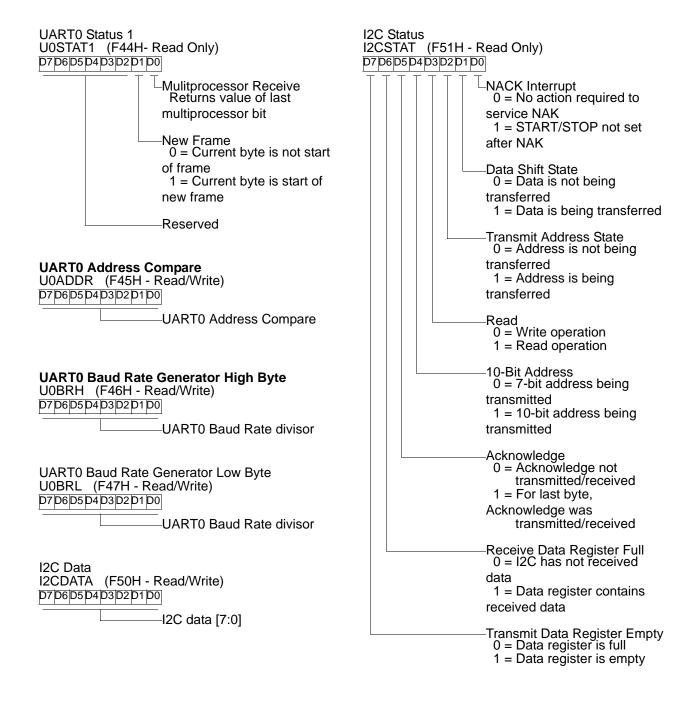

#### UART Status 0 Register

The UART Status 0 and Status 1 registers (Table 54 and Table 55 on page 102) identify the current UART operating configuration and status.

#### Table 54. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6  | 5  | 4  | 3    | 2    | 1   | 0   |  |  |  |

|-------|-----|----|----|----|------|------|-----|-----|--|--|--|

| FIELD | RDA | PE | OE | FE | BRKD | TDRE | TXE | CTS |  |  |  |

| RESET |     |    | 0  | ,  | Х    |      |     |     |  |  |  |

| R/W   |     | R  |    |    |      |      |     |     |  |  |  |

| ADDR  |     |    |    | F4 | 1H   |      |     |     |  |  |  |

#### **RDA**—Receive Data Available

This bit indicates that the UART Receive Data Register has received data. Reading the UART Receive Data Register clears this bit.

0 = The UART Receive Data Register is empty.

1 = There is a byte in the UART Receive Data Register.

#### **PE—Parity Error**

This bit indicates that a parity error has occurred. Reading the UART Receive Data Register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

#### **OE—Overrun Error**

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data Register has not been read. If the RDA bit is reset to

#### Reserved—Must be 0

**NEWFRM**—Status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

#### MPRX—Multiprocessor Receive

Returns the value of the last multiprocessor bit received. Reading from the UART Receive Data Register resets this bit to 0.

#### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 56 and Table 57 on page 104) configure the properties of the UART's transmit and receive operations. The UART Control Registers must not been written while the UART is enabled.

#### Table 56. UART Control 0 Register (U0CTL0)

| BITS  | 7 6 |     | 5 4  |             | 3  | 2    | 1    | 0    |  |  |  |  |  |  |

|-------|-----|-----|------|-------------|----|------|------|------|--|--|--|--|--|--|

| FIELD | TEN | REN | CTSE | CTSE PEN PS |    | SBRK | STOP | LBEN |  |  |  |  |  |  |

| RESET | 0   |     |      |             |    |      |      |      |  |  |  |  |  |  |

| R/W   | R/W |     |      |             |    |      |      |      |  |  |  |  |  |  |

| ADDR  |     |     |      | F4          | 2H |      |      |      |  |  |  |  |  |  |

#### **TEN—Transmit Enable**

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

- 0 = Transmitter disabled.

- 1 = Transmitter enabled.

#### **REN**—Receive Enable

This bit enables or disables the receiver.

- 0 = Receiver disabled.

- 1 =Receiver enabled.

#### CTSE—CTS Enable

$0 = \text{The } \overline{\text{CTS}}$  signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

#### **PEN—Parity Enable**

This bit enables or disables parity. Even or odd is determined by the PSEL bit. This bit is overridden by the MPEN bit.

- 0 =Parity is disabled.

- 1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

necessary for  $\overline{SS}$  to deassert between characters to generate the interrupt. The SPI in SLAVE mode also generates an interrupt if the  $\overline{SS}$  signal deasserts prior to transfer of all the bits in a character (see description of Slave Abort Error). Writing a 1 to the IRQ bit in the SPI Status Register clears the pending SPI interrupt request. The IRQ bit must be cleared to 0 by the ISR to generate future interrupts. To start the transfer process, an SPI interrupt can be forced by software writing a 1 to the STR bit in the SPICTL Register.

If the SPI is disabled, an SPI interrupt can be generated by a BRG time-out. This timer function must be enabled by setting the BIRQ bit in the SPICTL Register. This BRG time-out does not set the IRQ bit in the SPISTAT Register, just the SPI interrupt bit in the interrupt controller.

#### **SPI Baud Rate Generator**

In SPI MASTER mode, the BRG creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the BRG is the system clock. The SPI Baud Rate High and Low Byte Registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2x\text{BRG}[15:0]}$

Minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of  $(2 \times 65536 = 131072)$ .

When the SPI is disabled, BRG functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure BRG as a timer with interrupt on time-out:

- 1. Disable the SPI by clearing the SPIEN bit in the SPI Control Register to 0.

- 2. Load the desired 16-bit count value into the SPI Baud Rate High and Low Byte registers.

- 3. Enable BRG timer function and associated interrupt by setting the BIRQ bit in the SPI Control Register to 1.

When configured as a general-purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0] ]

## 126

#### **BRH = SPI Baud Rate High Byte**

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

#### Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 2 1 |  |  |  |  |  |  |

|-------|------|---|---|---|---|---|-----|--|--|--|--|--|--|

| FIELD | BRL  |   |   |   |   |   |     |  |  |  |  |  |  |

| RESET | 1    |   |   |   |   |   |     |  |  |  |  |  |  |

| R/W   | R/W  |   |   |   |   |   |     |  |  |  |  |  |  |

| ADDR  | F67H |   |   |   |   |   |     |  |  |  |  |  |  |

#### **BRL = SPI Baud Rate Low Byte**

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

START bits in the Control Register are set.

In order for a receive (read) DMA transaction to send a Not Acknowledge on the last byte, the receive DMA must be set up to receive n-1 bytes, then software must set the NAK bit and receive the last (nth) byte directly.

#### **Start and Stop Conditions**

The Master ( $I^2C$ ) drives all Start and Stop signals and initiates all transactions. To start a transaction, the  $I^2C$  Controller generates a START condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the  $I^2C$  Controller generates a Stop condition by creating a low-to-high transition of the SDA signal while the SCL signal is high. The START and STOP bits in the  $I^2C$  Control Register control the sending of the Start and Stop conditions. A Master is also allowed to end one transaction and begin a new one by issuing a Restart. This is accomplished by setting the START bit at the end of a transaction, rather than the STOP bit.

**Note:** The Start condition not sent until the START bit is set and data has been written to the  $I^2C$ Data Register.

#### **Master Write and Read Transactions**

The following sections provide a recommended procedure for performing  $I^2C$  write and read transactions from the  $I^2C$  Controller (Master) to slave  $I^2C$  devices. In general software should rely on the TDRE, RDRF and NCKI bits of the status register (these bits generate interrupts) to initiate software actions. When using interrupts or DMA, the TXI bit is set to start each transaction and cleared at the end of each transaction to eliminate a 'trailing' Transmit Interrupt.

Caution should be used in using the ACK status bit within a transaction because it is difficult for software to tell when it is updated by hardware.

When writing data to a slave, the I<sup>2</sup>C pauses at the beginning of the Acknowledge cycle if the data register has not been written with the next value to be sent (TDRE bit in the I<sup>2</sup>C Status register equal to 1). In this scenario where software is not keeping up with the I<sup>2</sup>C bus (TDRE asserted longer than one byte time), the Acknowledge clock cycle for byte n is delayed until the data register is written with byte n + 1, and appears to be grouped with the data clock cycles for byte n + 1. If either the START or STOP bit is set, the I<sup>2</sup>C does not pause prior to the Acknowledge cycle because no additional data is sent.

When a Not Acknowledge condition is received during a write (either during the address or data phases), the I<sup>2</sup>C Controller generates the Not Acknowledge interrupt (NCKI = 1) and pause until either the STOP or START bit is set. Unless the Not Acknowledge was received on the last byte, the data register will already have been written with the next address or data byte to send. In this case the FLUSH bit of the control register should be set at the same time the STOP or START bit is set to remove the stale transmit data and enable subsequent Transmit Interrupts.

When reading data from the slave, the  $I^2C$  pauses after the data Acknowledge cycle until the receive interrupt is serviced and the RDRF bit of the status register is cleared by reading the  $I^2C$  Data Register. Once the  $I^2C$  Data Register has been read, the  $I^2C$  reads the next data byte.

#### Address Only Transaction with a 7-bit Address

In the situation where software determines if a slave with a 7-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 26 on page 131 displays this "address only" transaction to determine if a slave with a 7-bit address will acknowledge. As an example, this transaction can be used after a "write" has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge, the transaction is repeated until the slave does Acknowledge.

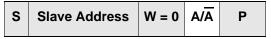

Figure 26. 7-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable Transmit interrupts.

- 3. The I<sup>2</sup>C interrupt asserts, because the I<sup>2</sup>C Data Register is empty (TDRE = 1)

- 4. Software responds to the TDRE bit by writing a 7-bit Slave address plus write bit (=0) to the I<sup>2</sup>C Data Register. As an alternative this could be a read operation instead of a write operation.

- 5. Software sets the START and STOP bits of the I<sup>2</sup>C Control Register and clears the TXI bit.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  Slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

- 8. Software polls the STOP bit of the I<sup>2</sup>C Control Register. Hardware deasserts the STOP bit when the address only transaction is completed.

- 9. Software checks the ACK bit of the I<sup>2</sup>C Status Register. If the slave acknowledged, the ACK bit is equal to 1. If the slave does not acknowledge, the ACK bit is equal to 0. The NCKI interrupt does not occur in the not acknowledge case because the STOP bit was set.

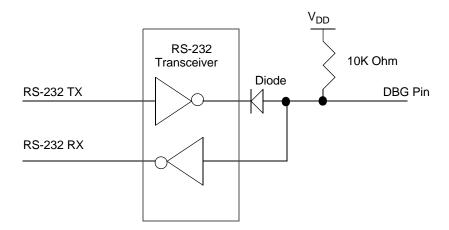

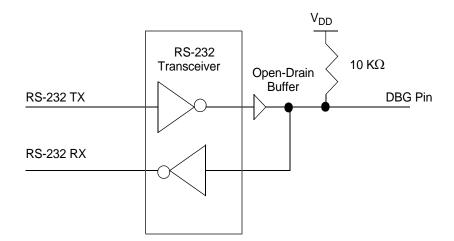

transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8 Encore! XP F0822 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 38 and Figure 39.

# **!** Caution: For operation of the OCD, all power pins $(V_{DD} \text{ and } AV_{DD})$ must be supplied with power, and all ground pins $(V_{SS} \text{ and } AV_{SS})$ must be properly grounded. The DBG pin is open-drain and must always be connected to $V_{DD}$ through an external pull-up resistor to insure proper operation.

Figure 38. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

Figure 39. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

| Assembly      | Symbolic                            | Address<br>Mode |    | _ Opcode(s) | Flags |   |   |   |   |   | - Fetch | Instr. |  |

|---------------|-------------------------------------|-----------------|----|-------------|-------|---|---|---|---|---|---------|--------|--|

| Mnemonic      | Operation                           | dst src         |    | (Hex)       | C Z   |   | S | ۷ | D | Н |         | Cycles |  |

| SCF           | C ← 1                               |                 |    | DF          | 1     | - | - | - | - | - | 1       | 2      |  |

| SRA dst       | ŤŤ                                  | R               |    | D0          | *     | * | * | 0 | - | - | 2       | 2      |  |

|               | D7 D6 D5 D4 D3 D2 D1 D0 →<br>dst    | IR              |    | D1          |       |   |   |   |   |   | 2       | 3      |  |

| SRL dst       | →D7D6D5D4D3D2D1D0                   | R               |    | 1F C0       | *     | * | 0 | * | - | - | 3       | 2      |  |

|               | dst                                 | IR              |    | 1F C1       |       |   |   |   |   |   | 3       | 3      |  |

| SRP src       | $RP \leftarrow src$                 |                 | IM | 01          | -     | - | - | - | - | - | 2       | 2      |  |

| STOP          | STOP Mode                           |                 |    | 6F          | -     | - | - | - | - | - | 1       | 2      |  |

| SUB dst, src  | $dst \gets dst - src$               | r               | r  | 22          | *     | * | * | * | 1 | * | 2       | 3      |  |

|               | -                                   | r               | lr | 23          |       |   |   |   |   |   | 2       | 4      |  |

|               | -                                   | R               | R  | 24          |       |   |   |   |   |   | 3       | 3      |  |

|               | -                                   | R               | IR | 25          |       |   |   |   |   |   | 3       | 4      |  |

|               | -                                   | R               | IM | 26          |       |   |   |   |   |   | 3       | 3      |  |

|               | -                                   | IR              | IM | 27          |       |   |   |   |   |   | 3       | 4      |  |

| SUBX dst, src | $dst \gets dst - src$               | ER              | ER | 28          | *     | * | * | * | 1 | * | 4       | 3      |  |

|               | -                                   | ER              | IM | 29          |       |   |   |   |   |   | 4       | 3      |  |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R               |    | F0          | Х     | * | * | Х | - | - | 2       | 2      |  |

|               | -                                   | IR              |    | F1          |       |   |   |   |   |   | 2       | 3      |  |

| TCM dst, src  | (NOT dst) AND src                   | r               | r  | 62          | -     | * | * | 0 | - | - | 2       | 3      |  |

|               | -                                   | r               | lr | 63          |       |   |   |   |   |   | 2       | 4      |  |

|               | -                                   | R               | R  | 64          |       |   |   |   |   |   | 3       | 3      |  |

|               | -                                   | R               | IR | 65          |       |   |   |   |   |   | 3       | 4      |  |

|               | -                                   | R               | IM | 66          |       |   |   |   |   |   | 3       | 3      |  |

|               | -                                   | IR              | IM | 67          |       |   |   |   |   |   | 3       | 4      |  |

| TCMX dst, src | (NOT dst) AND src                   | ER              | ER | 68          | -     | * | * | 0 | - | - | 4       | 3      |  |

|               | -                                   | ER              | IM | 69          |       |   |   |   |   |   | 4       | 3      |  |

## Table 126. eZ8 CPU Instruction Summary (Continued)

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

|          |                         | Lower Nibble (Hex)       |                            |                             |                            |                            |                            |                                |                               |                                |                            |                          |                           |                           |                  |                          |

|----------|-------------------------|--------------------------|----------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|------------------|--------------------------|

|          | 0                       | 1                        | 2                          | 3                           | 4                          | 5                          | 6                          | 7                              | 8                             | 9                              | А                          | В                        | С                         | D                         | E                | F                        |

| 0        | 1.2<br>BRK              | 2.2<br>SRP               | 2.3<br><b>ADD</b><br>r1,r2 | 2.4<br><b>ADD</b><br>r1,lr2 | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1       | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1        | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1 | 2.3<br>ADC<br>r1,r2        | 2.4<br>ADC<br>r1,lr2        | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1       | 3.3<br>ADC<br>R1,IM        | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                  | See 2nd<br>Opcode<br>Map |

| 2        | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2        | 2.4<br>SUB<br>r1,lr2        | 3.3<br>SUB<br>R2,R1        | 3.4<br>SUB<br>IR2,R1       | 3.3<br>SUB<br>R1,IM        | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                  | map                      |

| 3        | 2.2<br>DEC<br>R1        | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2        | 2.4<br>SBC<br>r1,lr2        | 3.3<br>SBC<br>R2,R1        | 3.4<br>SBC<br>IR2,R1       | 3.3<br>SBC<br>R1,IM        | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX                    |                            |                          |                           |                           |                  |                          |

| 4        | 2.2<br>DA<br>R1         | 2.3<br>DA<br>IR1         | 2.3<br>OR<br>r1,r2         | 2.4<br>OR<br>r1,lr2         | 3.3<br>OR<br>R2,R1         | 3.4<br>OR<br>IR2,R1        | 3.3<br>OR<br>R1,IM         | 3.4<br>OR<br>IR1,IM            | 4.3<br>ORX<br>ER2,ER1         | 4.3<br><b>ORX</b>              |                            |                          |                           |                           |                  |                          |

| 5        | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2        | 2.4<br>AND<br>r1,lr2        | 3.3<br>AND<br>R2,R1        | 3.4<br>AND<br>IR2,R1       | 3.3<br>AND<br>R1,IM        | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                           |                           |                  | 1.2<br>WDT               |

| 6        | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2        | 2.4<br>TCM<br>r1,lr2        | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1       | 3.3<br>TCM<br>R1,IM        | 3.4<br>TCM<br>IR1,IM           | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                  | 1.2<br>STOP              |

| <b>7</b> | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2  | 2.4<br><b>TM</b><br>r1,lr2  | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1 | 3.3<br>TM<br>R1,IM         | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                  | 1.2<br>HALT              |

| 8        | 2.5<br>DECW<br>RR1      | 2.6                      | 2.5<br>LDE<br>r1,lrr2      | 2.9<br>LDEI<br>Ir1,Irr2     | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2      | 3.4<br>LDX                 | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                          |                           |                           |                  | 1.2<br><b>DI</b>         |

| 9        | 2.2<br>RL<br>R1         | 2.3<br><b>RL</b><br>IR1  | 2.5<br>LDE<br>r2,Irr1      | 2.9<br>LDEI<br>Ir2,Irr1     | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1      | 3.4<br>LDX<br>R2,IRR1      | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                  | 1.2<br>El                |

| A        | 2.5<br>INCW<br>RR1      | 2.6<br>INCW              | 2.3<br><b>CP</b><br>r1,r2  | 2.4<br><b>CP</b><br>r1,lr2  | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1 | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                  | 1.4<br>RET               |

| в        | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br>XOR<br>r1,r2        | 2.4<br>XOR<br>r1,lr2        | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br>XOR<br>IR2,R1       | 3.3<br>XOR<br>R1,IM        | 3.4<br>XOR<br>IR1,IM           | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                          |                           |                           |                  | 1.5<br>IRET              |

| с        | 2.2<br>RRC<br>R1        | 2.3<br>RRC<br>IR1        | 2.5<br>LDC<br>r1,lrr2      | 2.9<br>LDCI<br>Ir1,Irr2     | 2.3<br>JP<br>IRR1          | 2.9<br>LDC<br>lr1,lrr2     | i ci jim                   | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                           |                           |                  | 1.2<br>RCF               |

| D        | 2.2<br>SRA<br>R1        | 2.3<br>SRA<br>IR1        | 2.5<br>LDC<br>r2,Irr1      | 2.9<br>LDCI<br>Ir2,Irr1     | 2.6<br>CALL<br>IRR1        | 2.2<br>BSWAP<br>R1         | 3.3<br>CALL<br>DA          | 3.4<br>LD<br>r2,r1,X           | 3.2<br>POPX<br>ER1            |                                |                            |                          |                           |                           |                  | 1.2<br>SCF               |

| Е        | 2.2<br>RR<br>R1         | 2.3<br><b>RR</b><br>IR1  | 2.2<br>BIT<br>p,b,r1       | 2.3<br>LD<br>r1,lr2         | 3.2<br>LD<br>R2,R1         | 3.3<br>LD<br>IR2,R1        | 3.2<br>LD<br>R1,IM         | 3.3<br>LD<br>IR1,IM            | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                          |                           |                           |                  | 1.2<br>CCF               |

| F        | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector      | 2.3<br>LD<br>lr1,r2         | 2.8<br>MULT<br>RR1         | 3.3<br>LD<br>R2,IR1        | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               | ,                              | V                          |                          |                           |                           |                  |                          |

Figure 58. First Opcode Map

Upper Nibble (Hex)

231

#### Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

compare 82 compare - extended addressing 214 compare mode 82 compare with carry 214 compare with carry - extended addressing 214 complement 217 complement carry flag 215, 216 condition code 211 continuous conversion (ADC) 148 continuous mode 81 control register definition, UART 100 control register, I2C 141 counter modes 81 CP 214 **CPC 214 CPCX 214** CPU and peripheral overview 3 CPU control instructions 216 CPX 214 Customer Feedback Form 251 customer feedback form 240 Customer Information 251

## D

DA 211. 214 data register, I2C 139 DC characteristics 187 debugger, on-chip 171 **DEC 214** decimal adjust 214 decrement 214 and jump non-zero 217 word 214 **DECW 214** destination operand 212 device, port availability 47 DI 216 direct address 211 disable interrupts 216 **DJNZ 217** DMA controller 5 dst 212

## E

EI 216 electrical characteristics 185 ADC 199 flash memory and timing 196 GPIO input data sample timing 200 watch-dog timer 197 enable interrupt 216 ER 211 extended addressing register 211 external pin reset 43 external RC oscillator 196 eZ8 features 3 eZ8 CPU features 3 eZ8 CPU instruction classes 214 eZ8 CPU instruction notation 210 eZ8 CPU instruction set 209 eZ8 CPU instruction summary 218

## F

FCTL register 159 features, Z8 Encore! 1 first opcode map 231 FLAGS 212 flags register 212 flash controller 4 option bit address space 163 option bit configuration - reset 163 program memory address 0001H 165 flash memory arrangement 154 byte programming 157 code protection 156 control register definitions 159 controller bypass 158 electrical characteristics and timing 196 flash control register 159 flash status register 160 frequency high and low byte registers 161 mass erase 158 operation 155