Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0412pj020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Braces

The curly braces { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• **Example:** The 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### **Parentheses**

The parentheses (), indicate an indirect register address lookup.

• **Example:** (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• **Example:** Assume PC[15:0] contains the value 1234h. (PC [15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* cannot be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• **Example:** ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least* significant byte and most significant byte, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and most significant bit, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings and conditions in general text.

- **Example 1**: The receiver forces the SCL line to Low.

- **Example 2:** The Master generates a STOP condition to abort the transfer.

- 2.7 V to 3.6 V operating voltage with 5 V-tolerant inputs

- 20-pin and 28-pin packages

- 0 °C to +70 °C standard temperature and -40 °C to +105 °C extended temperature operating ranges

### **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\text{®}}$  F0822 Series product line.

| Dert           | 16-bit<br>Flash RAM Timers ADC UARTs |      |     |          |   |           |                  |     | Package Pin<br>Counts |    |

|----------------|--------------------------------------|------|-----|----------|---|-----------|------------------|-----|-----------------------|----|

| Part<br>Number | (KB)                                 | (KB) | I/O | with PWM | - | with IrDA | I <sup>2</sup> C | SPI | 20                    | 28 |

| Z8F0822        | 8                                    | 1    | 19  | 2        | 5 | 1         | 1                | 1   |                       | Х  |

| Z8F0821        | 8                                    | 1    | 11  | 2        | 2 | 1         | 1                |     | Х                     |    |

| Z8F0812        | 8                                    | 1    | 19  | 2        | 0 | 1         | 1                | 1   |                       | Х  |

| Z8F0811        | 8                                    | 1    | 11  | 2        | 0 | 1         | 1                |     | Х                     |    |

| Z8F0422        | 4                                    | 1    | 19  | 2        | 5 | 1         | 1                | 1   |                       | Х  |

| Z8F0421        | 4                                    | 1    | 11  | 2        | 2 | 1         | 1                |     | Х                     |    |

| Z8F0412        | 4                                    | 1    | 19  | 2        | 0 | 1         | 1                | 1   |                       | Х  |

| Z8F0411        | 4                                    | 1    | 11  | 2        | 0 | 1         | 1                |     | Х                     |    |

## Table 1. Z8 Encore! XP<sup>®</sup> F0822 Series Part Selection Guide

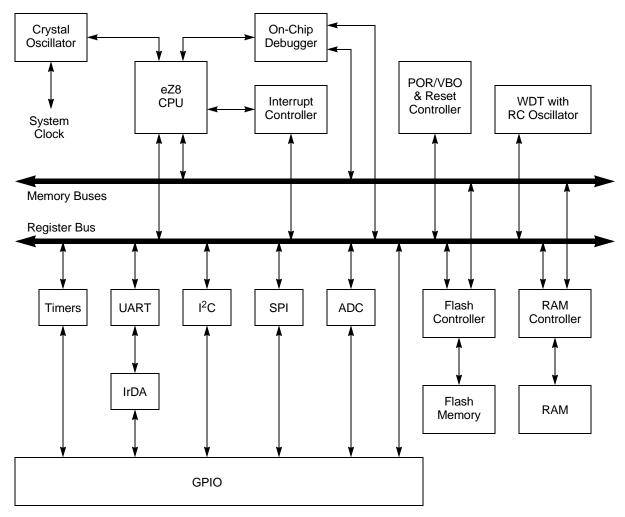

## **Block Diagram**

Figure 1 displays the block diagram of the architecture of Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0822 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0822 Series Block Diagram

## **CPU and Peripheral Overview**

#### eZ8 CPU Features

Zilog's latest eZ8 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{$ <sup>®</sup> instruction set.

#### **UARTO Status 0** U0STAT0 (F41H - Read Only) **UART0** Control 0 D7 D6 D5 D4 D3 D2 D1 D0 U0CTL0 (F42H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 -CTS signal Returns the level of the CTS -Loop Back Enable 0 = Normal operation 1 = Transmit data is looped signal Transmitter Empty 0 = Data is currently back to the receiver transmitting 1 = Transmission is STOP Bit Select 0 = Transmitter sends 1 complete STOP bit -Transmitter Data Register 0 = Transmit Data Register is 1 = Transmitter sends 2STOP bits full 1 = Transmit Data register is Send Break 0 = No break is sent empty 1 = Output of the transmitter Break Detect 0 = No break occurred is zero Parity Select 0 = Even parity 1 = A break occurred 1 = Odd parity Framing Error 0 = No framing error Parity Enable 0 = Parity is disabled occurred 1 = A framing occurred 1 = Parity is enabled Overrun Error CTS Enable 0 = No overrrun error0 = CTS signal has no effect occurred on the 1 = An overrun error transmitter occurred 1 = UART recognizes $\overline{CTS}$ signal as a Parity Error transmit enable control 0 = No parity error occurred 1 = A parity error occurred signal Receive Data Available Receive Enable 0 = Receive Data Register is 0 = Receiver disabled 1 = Receiver enabled empty 1 = A byte is available in the Transmit Enable 0 = Transmitter disabled Receive Data Register 1 = Transmitter enabled

21

32

Port A Address PAADDR (FD0H - Read/Write) D7D6D5D4D3D2D1D0 Port A Address[7:0] Selects Port Sub-Registers: 00H = No function 01H = Data direction 02H = Alternate function03H = Output control (opendrain) 04H = High drive enable05H = STOP mode recovery enable 06H = Pull-up enable07H-FFH = No function Port A Control PACTL (FD1H - Read/Write) D7D6D5D4D3D2D1D0 Port A Control[7:0] Provides Access to Port Sub-Registers Port A Input Data PAIN (FD2H - Read Only) D7 D6 D5 D4 D3 D2 D1 D0 -Port A Input Data [7:0] Port A Output Data PAOUT (FD3H - Read/Write) D7D6D5D4D3D2D1D0

Port A Output Data [7:0]

- 4. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte Registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte Registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- Configure the timer for CAPTURE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte Registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte Registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte Registers to 0000H. This allows user software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte Registers still contains 0000H after the interrupt, then the interrupt was generated by a Reload.

- 5. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event is calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value)xPrescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte Registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

Follow the steps below for configuring a timer for COMPARE mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if required

- 2. Write to the Timer High and Low Byte registers to set the starting count value

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value

#### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the WDT Reload registers. The WDT then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the WDT Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0822 Series device is operating in DEBUG Mode (using the OCD), the WDT is continuously refreshed to prevent spurious WDT time-outs.

#### Watchdog Timer Time-Out Response

The WDT times out when the counter reaches 000000H. A WDT time-out generates either an Interrupt or a Reset. The WDT\_RES Option Bit determines the time-out response of the WDT. For information regarding programming of the WDT\_RES Option Bit, see Option Bits on page 163.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the WDT issues an interrupt request to the interrupt controller and sets the WDT Status Bit in the WDT Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the WDT interrupt vector and executing the code from the vector address. After time-out and interrupt generation, the WDT counter rolls over to its maximum value of FFFFFH and continues counting. The WDT counter is not automatically returned to its Reload Value.

#### WDT Reset in STOP Mode

If enabled in STOP mode and configured to generate a Reset when a time-out occurs and the device is in STOP mode, the WDT initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the WDT Control Register is set to 1 following the WDT time-out in STOP mode. For more information, see Reset and Stop Mode Recovery on page 39. Default operation is for the WDT and its RC oscillator to be enabled during STOP mode.

To minimize power consumption in STOP mode, the WDT and its RC oscillator is disabled in STOP mode. The following sequence configures the WDT to be disabled when the Z8F082x family device enters STOP mode following execution of a STOP instruction:

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write 81H to the Watchdog Timer Control Register (WDTCTL) to configure the WDT and its oscillator to be disabled during STOP mode. Alternatively, write 00H to the WDTCTL as the third step in this sequence to reconfigure the WDT and its oscillator to be enabled during STOP mode. This sequence only affects WDT operation in STOP mode.

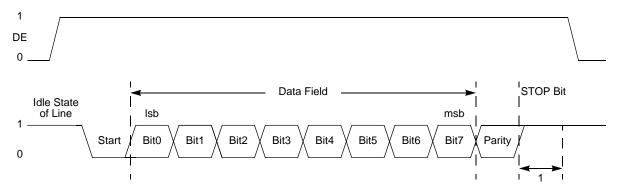

Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This format allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the last STOP bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 15. UART Driver Enable Signal Timing (with 1 STOP Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the BRG also functions as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. At this point, the Transmit Data Register can be written with the next character to send. This provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

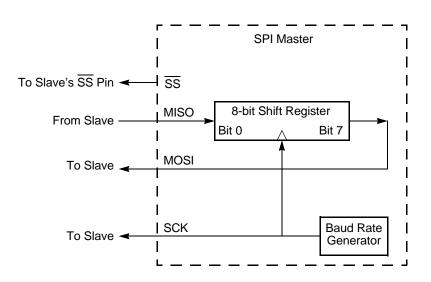

# **Serial Peripheral Interface**

The Serial Peripheral Interface (SPI) is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, and character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

The SPI is not available in 20-pin package devices.

### Architecture

The SPI is be configured as either a Master (in single or multi-master systems) or a Slave as displayed in Figure 20 through Figure 22.

#### Figure 20. SPI Configured as a Master in a Single Master, Single Slave System

necessary for  $\overline{SS}$  to deassert between characters to generate the interrupt. The SPI in SLAVE mode also generates an interrupt if the  $\overline{SS}$  signal deasserts prior to transfer of all the bits in a character (see description of Slave Abort Error). Writing a 1 to the IRQ bit in the SPI Status Register clears the pending SPI interrupt request. The IRQ bit must be cleared to 0 by the ISR to generate future interrupts. To start the transfer process, an SPI interrupt can be forced by software writing a 1 to the STR bit in the SPICTL Register.

If the SPI is disabled, an SPI interrupt can be generated by a BRG time-out. This timer function must be enabled by setting the BIRQ bit in the SPICTL Register. This BRG time-out does not set the IRQ bit in the SPISTAT Register, just the SPI interrupt bit in the interrupt controller.

#### **SPI Baud Rate Generator**

In SPI MASTER mode, the BRG creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the BRG is the system clock. The SPI Baud Rate High and Low Byte Registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2xBRG[15:0]}$

Minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of  $(2 \times 65536 = 131072)$ .

When the SPI is disabled, BRG functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure BRG as a timer with interrupt on time-out:

- 1. Disable the SPI by clearing the SPIEN bit in the SPI Control Register to 0.

- 2. Load the desired 16-bit count value into the SPI Baud Rate High and Low Byte registers.

- 3. Enable BRG timer function and associated interrupt by setting the BIRQ bit in the SPI Control Register to 1.

When configured as a general-purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0] ]

$1 = \overline{SS}$  pin driven High (1). This bit has no effect if SSIO = 0 or SPI configured as a Slave

#### **SPI Diagnostic State Register**

The SPI Diagnostic State Register provides observability of internal state. This is a read only register used for SPI diagnostics.

#### Table 67. SPI Diagnostic State Register (SPIDST)

| BITS  | 7     | 6     | 5 | 5 4 3 2 1 |    |  |  |  |  |  |  |

|-------|-------|-------|---|-----------|----|--|--|--|--|--|--|

| FIELD | SCKEN | TCKEN |   | SPISTATE  |    |  |  |  |  |  |  |

| RESET |       |       |   | (         | )  |  |  |  |  |  |  |

| R/W   |       | R     |   |           |    |  |  |  |  |  |  |

| ADDR  |       |       |   | F6        | 4H |  |  |  |  |  |  |

#### SCKEN–Shift Clock Enable

0 = The internal Shift Clock Enable signal is deasserted

1 = The internal Shift Clock Enable signal is asserted (shift register is updates on next system clock)

#### **TCKEN–Transmit Clock Enable**

0 = The internal Transmit Clock Enable signal is deasserted.

1 = The internal Transmit Clock Enable signal is asserted. When this is asserted the serial data out is updated on the next system clock (MOSI or MISO).

#### **SPISTATE–SPI State Machine**

Defines the current state of the internal SPI State Machine.

#### SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte Registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

| Table 68. SPI Baud Rate High | Byte Register (SPIBRH) |

|------------------------------|------------------------|

|------------------------------|------------------------|

| BITS  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|-----|---|---|----|----|---|---|---|--|--|--|

| FIELD | BRH |   |   |    |    |   |   |   |  |  |  |

| RESET |     |   |   |    | 1  |   |   |   |  |  |  |

| R/W   |     |   |   | R/ | W  |   |   |   |  |  |  |

| ADDR  |     |   |   | F6 | 6H |   |   |   |  |  |  |

## 126

#### **BRH = SPI Baud Rate High Byte**

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

#### Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|-----|-----|---|----|----|---|---|---|--|--|--|

| FIELD | BRL |     |   |    |    |   |   |   |  |  |  |

| RESET |     |     |   |    | 1  |   |   |   |  |  |  |

| R/W   |     | R/W |   |    |    |   |   |   |  |  |  |

| ADDR  |     |     |   | F6 | 7H |   |   |   |  |  |  |

#### **BRL = SPI Baud Rate Low Byte**

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

# **Flash Memory**

The products in Z8 Encore! XP<sup>®</sup> F0822 Series feature either 8 KB (8192) or 4 KB (4096) bytes of Flash memory with Read/Write/Erase capability. The Flash memory is programmed and erased in-circuit by either user code or through the OCD.

The Flash memory array is arranged in 512-byte per page. The 512-byte page is the minimum Flash block size that can be erased. The Flash memory is divided into eight sectors which is protected from programming and erase operations on a per sector basis.

Table 80 describes the Flash memory configuration for each device in the Z8F082x family. Table 81 lists the sector address ranges. Figure 33 on page 154 displays the Flash memory arrangement.

| Part Number | Flash Size  | Number<br>of Pages | Flash Memory<br>Addresses | Sector Size  | Number of<br>Sectors | Pages<br>per<br>Sector |

|-------------|-------------|--------------------|---------------------------|--------------|----------------------|------------------------|

| Z8F08xx     | 8 KB (8192) | 16                 | 0000H - 1FFFH             | 1 KB (1024)  | 8                    | 2                      |

| Z8F04xx     | 4 KB (4096) | 8                  | 0000H - 0FFFH             | 0.5 KB (512) | 8                    | 1                      |

#### **Table 80. Flash Memory Configurations**

#### Table 81. Flash Memory Sector Addresses

|               | Flash Sector Address Ranges |             |  |  |  |  |  |

|---------------|-----------------------------|-------------|--|--|--|--|--|

| Sector Number | Z8F04xx                     | Z8F08xx     |  |  |  |  |  |

| 0             | 0000H-01FFH                 | 0000H-03FFH |  |  |  |  |  |

| 1             | 0200H-03FFH                 | 0400H-07FFH |  |  |  |  |  |

| 2             | 0400H-05FFH                 | 0800H-0BFFH |  |  |  |  |  |

| 3             | 0600H-07FFH                 | 0C00H-0FFFH |  |  |  |  |  |

| 4             | 0800H-09FFH                 | 1000H-13FFH |  |  |  |  |  |

| 5             | 0A00H-0BFFH                 | 1400H-17FFH |  |  |  |  |  |

| 6             | 0C00H-0DFFH                 | 1800H-1BFFH |  |  |  |  |  |

| 7             | 0E00H-0FFFH                 | 1C00H-1FFFH |  |  |  |  |  |

Follow the steps below to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

#### **Flash Write Protection Option Bit**

The Flash Write Protect option bit can block all program and erase operations from user code. For more information, see Option Bits on page 163.

#### **Byte Programming**

When the Flash Controller is unlocked, writes to Flash Memory from user code programs a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all 1s (FFH). The programming operation is used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte Programming is accomplished using the eZ8 CPU's LDC or LDCI instructions. Refer to eZ8 CPU Core User Manual (UM0128) for a description of the LDC and LDCI instructions.

While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a Programming operation is in progress are serviced once the Programming operation is complete. To exit Programming mode and lock the Flash Controller, write 00H to the Flash Control Register.

User code cannot program Flash Memory on a page that is located in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

## **Caution:** *Each memory location must not be programmed more than twice before an erase occurs.*

Follow the steps below to program the Flash from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

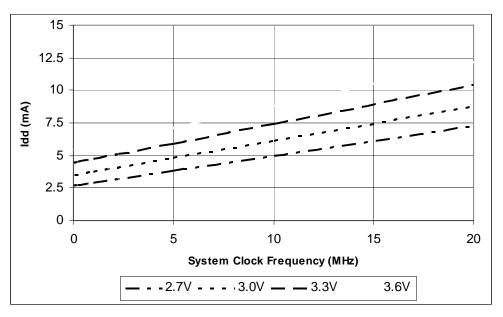

Figure 41. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

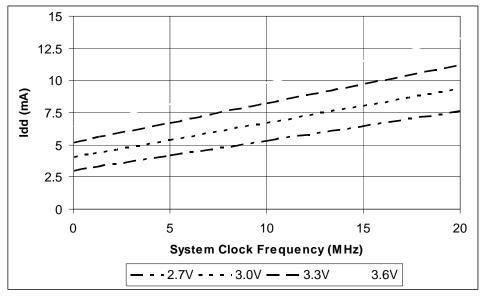

Figure 42 displays the maximum active mode current consumption across the full operating temperature range of the device and versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 42. Maximum Active Mode I<sub>DD</sub> Versus System Clock Frequency

189

## Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 113. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H | 08H | (ADD dst, src) |

|---------------------------|-----|-----|-----|----------------|

| Object Code               | 04  | 08  | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 114. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 115 on page 211.

| Jaquin<br>M<br>Ture<br>Z8F04xx with 4 KB Flas | y<br>Flash | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description                                    |

|-----------------------------------------------|------------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|------------------------------------------------|

| Standard Temperature: 0                       | °C to 70   | °C       |           |            |                     |                     |                  |     |                 |                                                |

| Z8F0411HH020SC                                | 4 KB       | 1 KB     | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package                            |

| Z8F0411PH020SC                                | 4 KB       | 1 KB     | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package                            |

| Z8F0412SJ020SC                                | 4 KB       | 1 KB     | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package                            |

| Z8F0412PJ020SC                                | 4 KB       | 1 KB     | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package                            |

| Extended Temperature: -                       | 40 °C to   | 105 °C   |           |            |                     |                     |                  |     |                 |                                                |

| Z8F0411HH020EC                                | 4 KB       | 1 KB     | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package                            |

| Z8F0411PH020EC                                | 4 KB       | 1 KB     | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package                            |

| Z8F0412SJ020EC                                | 4 KB       | 1 KB     | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package                            |

| Z8F0412PJ020EC                                | 4 KB       | 1 KB     | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package                            |

| Z8F08200100KITG                               |            |          |           |            |                     |                     |                  |     |                 | Development Kit (20- and 28-pin)               |

| ZUSBSC00100ZACG                               |            |          |           |            |                     |                     |                  |     |                 | USB Smart Cable<br>Accessory Kit               |

| ZUSBOPTSC01ZACG                               |            |          |           |            |                     |                     |                  |     |                 | Opto-Isolated USB Smart<br>Cable Accessory Kit |

| Note: Replace C with G for                    | lead-free  | packagir | ng.       |            |                     |                     |                  |     |                 |                                                |

239

#### Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

## Index

## **Symbols**

# 212 % 212 @ 212

## Numerics

10-bit ADC 4 40-lead plastic dual-inline package 234

## A

absolute maximum ratings 185 AC characteristics 194 ADC 214 architecture 147 automatic power-down 148 block diagram 147 continuous conversion 148 control register 150 control register definitions 150 data high byte register 151 data low bits register 151 electrical characteristics and timing 199 operation 148 single-shot conversion 148 ADCCTL register 150 ADCDH register 151 ADCDL register 151 ADCX 214 ADD 214 additional symbols 212 address space 13 **ADDX 214** analog signals 10 analog-to-digital converter (ADC) 147 AND 217 **ANDX 217** arithmetic instructions 214 assembly language programming 209

assembly language syntax 210

## B

B 212 b 211 baud rate generator, UART 99 **BCLR 215** binary number suffix 212 **BIT 215** bit 211 clear 215 manipulation instructions 215 set 215 set or clear 215 swap 215, 218 test and jump 217 test and jump if non-zero 217 test and jump if zero 217 block diagram 3 block transfer instructions 215 **BRK 217 BSET 215** BSWAP 215, 218 **BTJ 217** BTJNZ 217 **BTJZ 217**

## С

CALL procedure 217 capture mode 81 capture/compare mode 82 cc 211 CCF 216 characteristics, electrical 185 clear 216 clock phase (SPI) 116 CLR 216 COM 217 IRR 211 Irr 211 p 211 R 211 r 211 RA 211 RR 211 rr 211 vector 211 X 211 notational shorthand 211

Ir 211

## 0

OCD architecture 171 auto-baud detector/generator 174 baud rate limits 174 block diagram 171 breakpoints 175 commands 176 control register 181 data format 173 DBG pin to RS-232 Interface 172 debug mode 173 debugger break 217 interface 171 serial errors 174 status register 183 timing 202 OCD commands execute instruction (12H) 181 read data memory (0DH) 180 read OCD control register (05H) 179 read OCD revision (00H) 178 read OCD status register (02H) 178 read program counter (07H) 179 read program memory (0BH) 180 read program memory CRC (0EH) 181 read register (09H) 179 read runtime counter (03H) 178 step instruction (10H) 181 stuff instruction (11H) 181

write data memory (0CH) 180 write OCD control register (04H) 178 write program counter (06H) 179 write program memory (0AH) 180 write register (08H) 179 on-chip debugger 5 on-chip debugger (OCD) 171 on-chip debugger signals 11 on-chip oscillator 167 one-shot mode 81 opcode map abbreviations 230 cell description 229 first 231 second after 1FH 232 **Operational Description 89** OR 217 ordering information 236 **ORX 217** oscillator signals 11

## P

p 211 packaging **PDIP 234** part selection guide 2 PC 212 **PDIP 234** peripheral AC and DC electrical characteristics 195 PHASE=0 timing (SPI) 117 PHASE=1 timing (SPI) 118 pin characteristics 12 polarity 211 POP 216 pop using extended addressing 216 **POPX 216** port availability, device 47 port input timing (GPIO) 200 port output timing, GPIO 201 power supply signals 11 power-down, automatic (ADC) 148 power-on and voltage brown-out 195 power-on reset (POR) 41

246