## Zilog - Z8F0412SJ020SC Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0412sj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **¢** Warning: DO NOT USE IN LIFE SUPPORT

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

xiii

| Abbreviations/<br>Acronyms | Expansion                        |

|----------------------------|----------------------------------|

| PDIP                       | Plastic Dual Inline Package      |

| SOIC                       | Small Outline Integrated Circuit |

| SSOP                       | Small Shrink Outline Package     |

| PC                         | Program Counter                  |

| IRQ                        | Interrupt Request                |

|                            |                                  |

| 17 |  |

|----|--|

|----|--|

| Address            |                                       |          |             |         |

|--------------------|---------------------------------------|----------|-------------|---------|

| (Hex)              | Register Description                  | Mnemonic | Reset (Hex) | Page No |

| FCE                | Reserved                              |          | 00          |         |

| FCF                | Interrupt Control                     | IRQCTL   | 00          | 67      |

| <b>GPIO Port A</b> |                                       |          |             |         |

| FD0                | Port A Address                        | PAADDR   | 00          | 50      |

| FD1                | Port A Control                        | PACTL    | 00          | 51      |

| FD2                | Port A Input Data                     | PAIN     | XX          | 54      |

| FD3                | Port A Output Data                    | PAOUT    | 00          | 55      |

| GPIO Port B        |                                       |          |             |         |

| FD4                | Port B Address                        | PBADDR   | 00          | 50      |

| FD5                | Port B Control                        | PBCTL    | 00          | 51      |

| FD6                | Port B Input Data                     | PBIN     | XX          | 54      |

| FD7                | Port B Output Data                    | PBOUT    | 00          | 55      |

| GPIO Port C        |                                       |          |             |         |

| FD8                | Port C Address                        | PCADDR   | 00          | 50      |

| FD9                | Port C Control                        | PCCTL    | 00          | 51      |

| FDA                | Port C Input Data                     | PCIN     | XX          | 54      |

| FDB                | Port C Output Data                    | PCOUT    | 00          | 55      |

| FDC-FEF            | Reserved                              | _        | XX          |         |

| Watchdog Tir       | ner (WDT)                             |          |             |         |

| FF0                | Watchdog Timer Control                | WDTCTL   | XXX00000b   | 86      |

| FF1                | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | 87      |

| FF2                | Watchdog Timer Reload High Byte       | WDTH     | FF          | 87      |

| FF3                | Watchdog Timer Reload Low Byte        | WDTL     | FF          | 87      |

| FF4-FF7            | Reserved                              |          | XX          |         |

| Flash Memory       | y Controller                          |          |             |         |

| FF8                | Flash Control                         | FCTL     | 00          | 159     |

| FF8                | Flash Status                          | FSTAT    | 00          | 160     |

| FF9                | Page Select                           | FPS      | 00          | 160     |

| FF9 (if enabled)   | Flash Sector Protect                  | FPROT    | 00          | 161     |

| FFA                | Flash Programming Frequency High Byte |          | 00          | 161     |

| FFB                | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 161     |

| Read-Only Me       | emory                                 |          |             |         |

| FF8                | Reserved                              | _        | XX          |         |

| FF9                | Page Select                           | RPS      | 00          | 160     |

| FFA-FFB            | Reserved                              | _        | XX          |         |

| eZ8 CPU            |                                       |          |             |         |

| XX=Undefined       |                                       |          |             |         |

# Table 7. Register File Address Map (Continued)

27

#### SPI Diagnostic State SPIDST (F64H - Read Only) D7D6D5D4D3D2D1D0 SPI State Transmit Clock Enable 0 = Internal transmit clock enable signal is deasserted 1 = Internal transmit clock enable signal is asserted Shift Clock Enable 0 = Internal shift clock enable signal is deasserted 1 = Internal shift clock enable signal is deasserted 1 = Internal shift clock enable signal is deasserted 1 = Internal shift clock enable signal is asserted

SPI Baud Rate Generator High Byte SPIBRH (F66H - Read/Write) D7D6D5D4D3D2D1D0

SPI Baud Rate Generator Low Byte SPIBRL (F67H - Read/Write) D7D6D5D4D3D2D1D0

\_\_\_\_\_SPI Baud Rate divisor [7:0]

61

Poor coding style that resulting in lost interrupt requests: LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Note:** To avoid missing interrupts, the following style of coding to set bits in the Interrupt Request Registers is recommended

Good coding style that avoids lost interrupt requests: ORX IRQ0, MASK

# **Interrupt Control Register Definitions**

For all interrupts other than the WDT interrupt, the Interrupt Control Registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

# **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register (Table 25) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ0 Register to determine if any interrupt requests are pending.

| BITS  | 7        | 6    | 5   | 4     | 3     | 2    | 1    | 0    |  |  |  |  |  |

|-------|----------|------|-----|-------|-------|------|------|------|--|--|--|--|--|

| FIELD | Reserved | T1I  | тоі | U0RXI | U0TXI | I2CI | SPII | ADCI |  |  |  |  |  |

| RESET |          | 0    |     |       |       |      |      |      |  |  |  |  |  |

| R/W   |          | R/W  |     |       |       |      |      |      |  |  |  |  |  |

| ADDR  |          | FC0H |     |       |       |      |      |      |  |  |  |  |  |

#### Table 25. Interrupt Request 0 Register (IRQ0)

#### Reserved—Must be 0

#### **T1I**—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

#### **T0I**—**Timer 0 Interrupt Request**

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

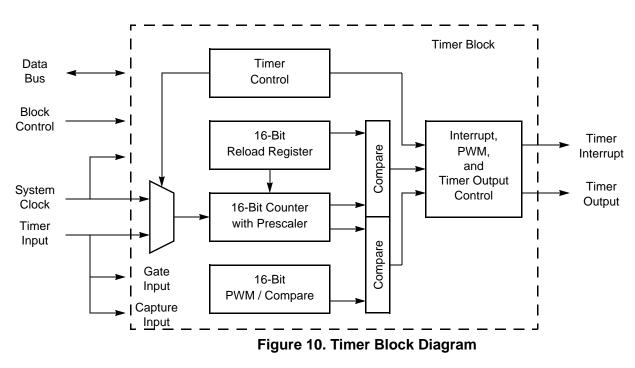

# **Timer Operating Modes**

The timers are configured to operate in the following modes:

# **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. On reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or vice-versa) on timer Reload. If it is required for the Timer Output to make a permanent state change on One-Shot time-out, first set the TPOL bit in the Timer Control Register to the start value before beginning ONE-SHOT mode. Then, after starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode

## **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the *first* external Timer Input transition. The required transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent desired transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H)

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers

- 5. Configure the associated GPIO port pin for the Timer Input alternate function

- 6. Write to the Timer Control Register to enable the timer

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event is calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value)xPrescale System Clock Frequency (Hz)

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte

of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal. This procedure allows the Endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# **Infrared Endec Control Register Definitions**

All Infrared Endec configuration and status information is set by the UART control registers as defined in UART Control Register Definitions on page 100.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Endec before enabling the GPIO Port alternate function for the corresponding pin.

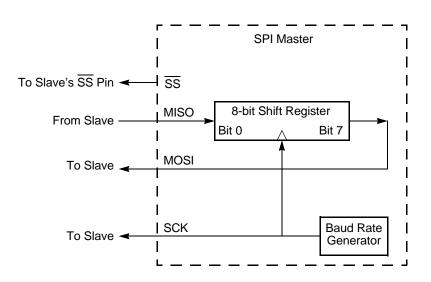

# **Serial Peripheral Interface**

The Serial Peripheral Interface (SPI) is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, and character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

The SPI is not available in 20-pin package devices.

# Architecture

The SPI is be configured as either a Master (in single or multi-master systems) or a Slave as displayed in Figure 20 through Figure 22.

# Figure 20. SPI Configured as a Master in a Single Master, Single Slave System

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

## **SPI Signals**

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (Serial Clock)

- <u>SS</u> (Slave Select)

The following sections discuss these SPI signals. Each signal is described in both Master and Slave modes.

### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

115

$1 = \overline{SS}$  pin driven High (1). This bit has no effect if SSIO = 0 or SPI configured as a Slave

# **SPI Diagnostic State Register**

The SPI Diagnostic State Register provides observability of internal state. This is a read only register used for SPI diagnostics.

#### Table 67. SPI Diagnostic State Register (SPIDST)

| BITS  | 7     | 6     | 5 | 5 4 3 2 1 0 |    |  |  |  |  |  |  |  |  |

|-------|-------|-------|---|-------------|----|--|--|--|--|--|--|--|--|

| FIELD | SCKEN | TCKEN |   | SPISTATE    |    |  |  |  |  |  |  |  |  |

| RESET |       | 0     |   |             |    |  |  |  |  |  |  |  |  |

| R/W   |       | R     |   |             |    |  |  |  |  |  |  |  |  |

| ADDR  |       |       |   | F6          | 4H |  |  |  |  |  |  |  |  |

#### SCKEN–Shift Clock Enable

0 = The internal Shift Clock Enable signal is deasserted

1 = The internal Shift Clock Enable signal is asserted (shift register is updates on next system clock)

#### **TCKEN–Transmit Clock Enable**

0 = The internal Transmit Clock Enable signal is deasserted.

1 = The internal Transmit Clock Enable signal is asserted. When this is asserted the serial data out is updated on the next system clock (MOSI or MISO).

#### **SPISTATE–SPI State Machine**

Defines the current state of the internal SPI State Machine.

### SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte Registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

| Table 68. SPI Baud Rate High | Byte Register (SPIBRH) |

|------------------------------|------------------------|

|------------------------------|------------------------|

| BITS  | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|-----|-----|---|----|----|---|---|---|--|--|--|--|

| FIELD | BRH |     |   |    |    |   |   |   |  |  |  |  |

| RESET |     | 1   |   |    |    |   |   |   |  |  |  |  |

| R/W   |     | R/W |   |    |    |   |   |   |  |  |  |  |

| ADDR  |     |     |   | F6 | 6H |   |   |   |  |  |  |  |

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

- 5. Re-write the page written in step 2 to the Page Select Register.

- 6. Write Flash Memory using LDC or LDCI instructions to program the Flash.

- 7. Repeat step 6 to program additional memory locations on the same page.

- 8. Write 00H to the Flash Control Register to lock the Flash Controller.

#### Page Erase

Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Page Select Register identifies the page to be erased. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. Interrupts that occur when the Page Erase operation is in progress are serviced once the Page Erase operation is complete. When the Page Erase operation is complete, the Flash Controller returns to its locked state. Only pages located in unprotected sectors can be erased.

Follow the steps below to perform a Page Erase operation:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page to be erased to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Re-write the page written in step 2 to the Page Select Register.

- 6. Write the Page Erase command 95H to the Flash Control Register.

## **Mass Erase**

The Flash memory cannot be Mass Erased by user code.

# Flash Controller Bypass

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Programming algorithms by controlling the Flash programming signals directly.

Flash Controller Bypass is recommended for gang programming applications and large volume customers who do not require in-circuit programming of the Flash memory.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore! XP, available for download at <u>www.zilog.com</u>.

162

frequency range for the device. The Flash Frequency High and Low Byte Registers must be loaded with the correct value to insure proper program and erase times.

# Table 87. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7      | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|--------|-----|---|----|----|---|---|---|--|--|--|--|

| FIELD | FFREQH |     |   |    |    |   |   |   |  |  |  |  |

| RESET |        | 0   |   |    |    |   |   |   |  |  |  |  |

| R/W   |        | R/W |   |    |    |   |   |   |  |  |  |  |

| ADDR  |        |     |   | FF | AH |   |   |   |  |  |  |  |

# Table 88. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|--|--|

| FIELD |   | FFREQL |   |    |    |   |   |   |  |  |  |  |

| RESET |   | 0      |   |    |    |   |   |   |  |  |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |  |  |

| ADDR  |   |        |   | FF | BH |   |   |   |  |  |  |  |

# FFREQH and FFREQL—Flash Frequency High and Low Bytes

These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

170

# Figure 36. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

# 173

# **Debug Mode**

The operating characteristics of the Z8 Encore! XP<sup>®</sup> F0822 Series devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

## **Entering Debug Mode**

The device enters DEBUG mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface.

- eZ8 CPU execution of a BRK (Breakpoint) instruction.

- Match of PC to OCDCNTR register (when enabled)

- OCDCNTR register decrements to 0000H (when enabled)

- If the DBG pin is Low when the device exits Reset, the OCD automatically puts the device into DEBUG mode.

#### **Exiting Debug Mode**

The device exits DEBUG mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0.

- Power-On Reset

- Voltage Brownout reset

- Asserting the **RESET** pin Low to initiate a Reset.

- Driving the DBG pin Low while the device is in STOP mode initiates a System Reset.

# **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 STOP bit (see Figure 40).

| ST | ART | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|----|-----|----|----|----|----|----|----|----|----|------|

|----|-----|----|----|----|----|----|----|----|----|------|

# Figure 40. OCD Data Format

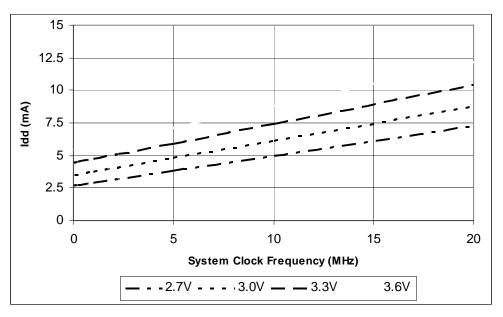

Figure 41. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

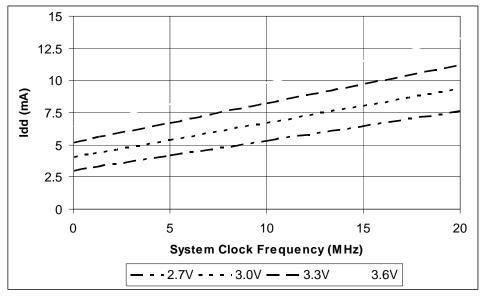

Figure 42 displays the maximum active mode current consumption across the full operating temperature range of the device and versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 42. Maximum Active Mode I<sub>DD</sub> Versus System Clock Frequency

189

| Assembly       | Symbolic                               |       | ress<br>ode | _ Opcode(s) | _ | _ | Fla | ags | _ |   | - Fetch | Instr. |

|----------------|----------------------------------------|-------|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic       | Operation                              | dst   | src         | (Hex)       | С | Ζ | S   | ۷   | D | Н |         | Cycles |

| LDX dst, src   | $dst \leftarrow src$                   | r     | ER          | 84          | - | - | -   | -   | - | - | 3       | 2      |

|                |                                        | lr    | ER          | 85          | - |   |     |     |   |   | 3       | 3      |

|                |                                        | R     | IRR         | 86          | - |   |     |     |   |   | 3       | 4      |

|                |                                        | IR    | IRR         | 87          | - |   |     |     |   |   | 3       | 5      |

|                |                                        | r     | X(rr)       | 88          | - |   |     |     |   |   | 3       | 4      |

|                |                                        | X(rr) | r           | 89          | - |   |     |     |   |   | 3       | 4      |

|                |                                        | ER    | r           | 94          | - |   |     |     |   |   | 3       | 2      |

|                |                                        | ER    | lr          | 95          | - |   |     |     |   |   | 3       | 3      |

|                |                                        | IRR   | R           | 96          | - |   |     |     |   |   | 3       | 4      |

|                |                                        | IRR   | IR          | 97          | - |   |     |     |   |   | 3       | 5      |

|                |                                        | ER    | ER          | E8          | - |   |     |     |   |   | 4       | 2      |

|                |                                        | ER    | IM          | E9          | - |   |     |     |   |   | 4       | 2      |

| LEA dst, X(sro | $\Rightarrow$ dst $\leftarrow$ src + X | r     | X(r)        | 98          | - | - | -   | -   | - | - | 3       | 3      |

|                |                                        | rr    | X(rr)       | 99          | - |   |     |     |   |   | 3       | 5      |

| MULT dst       | dst[15:0] ←<br>dst[15:8] *<br>dst[7:0] | RR    |             | F4          | - | - | -   | -   | - | - | 2       | 8      |

| NOP            | No operation                           |       |             | 0F          | - | - | -   | -   | - | - | 1       | 2      |

| OR dst, src    | $dst \gets dst \ OR \ src$             | r     | r           | 42          | - | * | *   | 0   | - | - | 2       | 3      |

|                |                                        | r     | lr          | 43          | - |   |     |     |   |   | 2       | 4      |

|                |                                        | R     | R           | 44          | - |   |     |     |   |   | 3       | 3      |

|                |                                        | R     | IR          | 45          | - |   |     |     |   |   | 3       | 4      |

|                |                                        | R     | IM          | 46          | - |   |     |     |   |   | 3       | 3      |

|                |                                        | IR    | IM          | 47          | - |   |     |     |   |   | 3       | 4      |

| ORX dst, src   | $dst \gets dst \ OR \ src$             | ER    | ER          | 48          | - | * | *   | 0   | - | - | 4       | 3      |

|                |                                        | ER    | IM          | 49          | - |   |     |     |   |   | 4       | 3      |

| POP dst        | $dst \gets @SP$                        | R     |             | 50          | - | - | -   | -   | - | - | 2       | 2      |

|                | $SP \leftarrow SP + 1$                 | IR    |             | 51          | - |   |     |     |   |   | 2       | 3      |

# Table 126. eZ8 CPU Instruction Summary (Continued)

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

compare 82 compare - extended addressing 214 compare mode 82 compare with carry 214 compare with carry - extended addressing 214 complement 217 complement carry flag 215, 216 condition code 211 continuous conversion (ADC) 148 continuous mode 81 control register definition, UART 100 control register, I2C 141 counter modes 81 CP 214 **CPC 214 CPCX 214** CPU and peripheral overview 3 CPU control instructions 216 CPX 214 Customer Feedback Form 251 customer feedback form 240 Customer Information 251

# D

DA 211. 214 data register, I2C 139 DC characteristics 187 debugger, on-chip 171 **DEC 214** decimal adjust 214 decrement 214 and jump non-zero 217 word 214 **DECW 214** destination operand 212 device, port availability 47 DI 216 direct address 211 disable interrupts 216 **DJNZ 217** DMA controller 5 dst 212

# E

EI 216 electrical characteristics 185 ADC 199 flash memory and timing 196 GPIO input data sample timing 200 watch-dog timer 197 enable interrupt 216 ER 211 extended addressing register 211 external pin reset 43 external RC oscillator 196 eZ8 features 3 eZ8 CPU features 3 eZ8 CPU instruction classes 214 eZ8 CPU instruction notation 210 eZ8 CPU instruction set 209 eZ8 CPU instruction summary 218

# F

FCTL register 159 features, Z8 Encore! 1 first opcode map 231 FLAGS 212 flags register 212 flash controller 4 option bit address space 163 option bit configuration - reset 163 program memory address 0001H 165 flash memory arrangement 154 byte programming 157 code protection 156 control register definitions 159 controller bypass 158 electrical characteristics and timing 196 flash control register 159 flash status register 160 frequency high and low byte registers 161 mass erase 158 operation 155

IRR 211 Irr 211 p 211 R 211 r 211 RA 211 RR 211 rr 211 vector 211 X 211 notational shorthand 211

Ir 211

# 0

OCD architecture 171 auto-baud detector/generator 174 baud rate limits 174 block diagram 171 breakpoints 175 commands 176 control register 181 data format 173 DBG pin to RS-232 Interface 172 debug mode 173 debugger break 217 interface 171 serial errors 174 status register 183 timing 202 OCD commands execute instruction (12H) 181 read data memory (0DH) 180 read OCD control register (05H) 179 read OCD revision (00H) 178 read OCD status register (02H) 178 read program counter (07H) 179 read program memory (0BH) 180 read program memory CRC (0EH) 181 read register (09H) 179 read runtime counter (03H) 178 step instruction (10H) 181 stuff instruction (11H) 181

write data memory (0CH) 180 write OCD control register (04H) 178 write program counter (06H) 179 write program memory (0AH) 180 write register (08H) 179 on-chip debugger 5 on-chip debugger (OCD) 171 on-chip debugger signals 11 on-chip oscillator 167 one-shot mode 81 opcode map abbreviations 230 cell description 229 first 231 second after 1FH 232 **Operational Description 89** OR 217 ordering information 236 **ORX 217** oscillator signals 11

# P

p 211 packaging **PDIP 234** part selection guide 2 PC 212 **PDIP 234** peripheral AC and DC electrical characteristics 195 PHASE=0 timing (SPI) 117 PHASE=1 timing (SPI) 118 pin characteristics 12 polarity 211 POP 216 pop using extended addressing 216 **POPX 216** port availability, device 47 port input timing (GPIO) 200 port output timing, GPIO 201 power supply signals 11 power-down, automatic (ADC) 148 power-on and voltage brown-out 195 power-on reset (POR) 41

246