Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |  |  |

|----------------------------|-----------------------------------------------------------|--|--|

| Product Status             | Obsolete                                                  |  |  |

| Core Processor             | eZ8                                                       |  |  |

| Core Size                  | 8-Bit                                                     |  |  |

| Speed                      | 20MHz                                                     |  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |  |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |  |  |

| Number of I/O              | 11                                                        |  |  |

| Program Memory Size        | 4KB (4K x 8)                                              |  |  |

| Program Memory Type        | FLASH                                                     |  |  |

| EEPROM Size                | -                                                         |  |  |

| RAM Size                   | 1K x 8                                                    |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |  |

| Data Converters            | A/D 2x10b                                                 |  |  |

| Oscillator Type            | Internal                                                  |  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |  |

| Mounting Type              | Through Hole                                              |  |  |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |  |  |

| Supplier Device Package    | -                                                         |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0421ph020sc |  |  |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **¢** Warning: DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| Timer 0–1 Control 1 Registers                            | 81                |

|----------------------------------------------------------|-------------------|

| Watchdog Timer                                           | 83                |

| Operation                                                | 83                |

| Watchdog Timer Refresh                                   | 84                |

| Watchdog Timer Time-Out Response                         | 84                |

| Watchdog Timer Reload Unlock Sequence                    | 85                |

| Watchdog Timer Control Register Definitions              | 86                |

| Watchdog Timer Control Register                          | 86                |

| Watchdog Timer Reload Upper, High and Low Byte Registers | 87                |

| Universal Asynchronous Receiver/Transmitter              | 89                |

| Architecture                                             | 89                |

| Operation                                                | 90                |

| Data Format                                              |                   |

| Transmitting Data using Polled Method                    |                   |

| Transmitting Data Using Interrupt-Driven Method          |                   |

| Receiving Data using the Polled Method                   |                   |

| Receiving Data Using Interrupt-Driven Method             |                   |

| Clear To Send Operation                                  |                   |

| Multiprocessor (9-bit) Mode                              |                   |

| External Driver Enable                                   |                   |

|                                                          |                   |

| UART Baud Rate Generator                                 |                   |

| UART Control Register Definitions.                       |                   |

| UART Transmit Data Register                              |                   |

| UART Receive Data Register.                              |                   |

| UART Status 0 Register                                   |                   |

| UART Status 1 Register                                   |                   |

| UART Control 0 and Control 1 Registers                   |                   |

| UART Address Compare Register                            |                   |

| UART Baud Rate High and Low Byte Registers               |                   |

| Infrared Encoder/Decoder                                 |                   |

| Architecture                                             |                   |

|                                                          |                   |

| 0508                                                     | Table of Contents |

|                                                          |                   |

Timer 0–3 Control 0 Registers ..... 80

#### vi

#### Braces

The curly braces { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• **Example:** The 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### **Parentheses**

The parentheses (), indicate an indirect register address lookup.

• **Example:** (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• **Example:** Assume PC[15:0] contains the value 1234h. (PC [15:0]) then refers to the contents of the memory location at address 1234h.

## Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* cannot be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• **Example:** ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least* significant byte and most significant byte, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and most significant bit, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings and conditions in general text.

- **Example 1**: The receiver forces the SCL line to Low.

- **Example 2:** The Master generates a STOP condition to abort the transfer.

| 17 |  |

|----|--|

|----|--|

| Address            |                                       |          |             |         |

|--------------------|---------------------------------------|----------|-------------|---------|

| (Hex)              | Register Description                  | Mnemonic | Reset (Hex) | Page No |

| FCE                | Reserved                              |          | 00          |         |

| FCF                | Interrupt Control                     | IRQCTL   | 00          | 67      |

| <b>GPIO Port A</b> |                                       |          |             |         |

| FD0                | Port A Address                        | PAADDR   | 00          | 50      |

| FD1                | Port A Control                        | PACTL    | 00          | 51      |

| FD2                | Port A Input Data                     | PAIN     | XX          | 54      |

| FD3                | Port A Output Data                    | PAOUT    | 00          | 55      |

| GPIO Port B        |                                       |          |             |         |

| FD4                | Port B Address                        | PBADDR   | 00          | 50      |

| FD5                | Port B Control                        | PBCTL    | 00          | 51      |

| FD6                | Port B Input Data                     | PBIN     | XX          | 54      |

| FD7                | Port B Output Data                    | PBOUT    | 00          | 55      |

| GPIO Port C        |                                       |          |             |         |

| FD8                | Port C Address                        | PCADDR   | 00          | 50      |

| FD9                | Port C Control                        | PCCTL    | 00          | 51      |

| FDA                | Port C Input Data                     | PCIN     | XX          | 54      |

| FDB                | Port C Output Data                    | PCOUT    | 00          | 55      |

| FDC-FEF            | Reserved                              | _        | XX          |         |

| Watchdog Tir       | ner (WDT)                             |          |             |         |

| FF0                | Watchdog Timer Control                | WDTCTL   | XXX00000b   | 86      |

| FF1                | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | 87      |

| FF2                | Watchdog Timer Reload High Byte       | WDTH     | FF          | 87      |

| FF3                | Watchdog Timer Reload Low Byte        | WDTL     | FF          | 87      |

| FF4-FF7            | Reserved                              |          | XX          |         |

| Flash Memory       | y Controller                          |          |             |         |

| FF8                | Flash Control                         | FCTL     | 00          | 159     |

| FF8                | Flash Status                          | FSTAT    | 00          | 160     |

| FF9                | Page Select                           | FPS      | 00          | 160     |

| FF9 (if enabled)   | Flash Sector Protect                  | FPROT    | 00          | 161     |

| FFA                | Flash Programming Frequency High Byte |          | 00          | 161     |

| FFB                | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 161     |

| Read-Only Me       | emory                                 |          |             |         |

| FF8                | Reserved                              | _        | XX          |         |

| FF9                | Page Select                           | RPS      | 00          | 160     |

| FFA-FFB            | Reserved                              | _        | XX          |         |

| eZ8 CPU            |                                       |          |             |         |

| XX=Undefined       |                                       |          |             |         |

# Table 7. Register File Address Map (Continued)

## **External Pin Reset**

The RESET pin contains a Schmitt-triggered input, an internal pull-up, an analog filter, and a digital filter to reject noise. After the RESET pin is asserted for at least 4 system clock cycles, the device progresses through the System Reset sequence. While the RESET input pin is asserted Low, Z8 Encore! XP F0822 Series device continues to be held in the Reset state. If the RESET pin is held Low beyond the System Reset time-out, the device exits the Reset state immediately following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1.

## **On-Chip Debugger Initiated Reset**

A POR is initiated using the OCD by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the WDT Control Register is set.

# **Stop Mode Recovery**

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. For detailed information on STOP mode, see Low-Power Modes on page 45. During Stop Mode Recovery, the device is held in reset for 66 cycles of the WDT oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the WDT Control Register and does not affect any other values in the Register File, including the Stack Pointer, Register Pointer, Flags, Peripheral Control Registers, and General-Purpose RAM.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the WDT Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information on each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                      | Action                                                               |

|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | WDT time-out when configured for Reset                                         | Stop Mode Recovery                                                   |

|                | WDT time-out when configured for interrupt                                     | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

| Table 10. Stop Mode Recovery Sources and Resulting Action | Table 10. Sto |

|-----------------------------------------------------------|---------------|

|-----------------------------------------------------------|---------------|

64

#### Table 29. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6                                                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|----------|--------------------------------------------------------|---|---|---|---|---|---|--|--|

| FIELD | Reserved | Reserved T1ENH T0ENH U0RENH U0TENH I2CENH SPIENH ADCEN |   |   |   |   |   |   |  |  |

| RESET |          | 0                                                      |   |   |   |   |   |   |  |  |

| R/W   | R/W      |                                                        |   |   |   |   |   |   |  |  |

| ADDR  |          | FC1H                                                   |   |   |   |   |   |   |  |  |

Reserved—Must be 0 T1ENH—Timer 1 Interrupt Request Enable High Bit

**TOENH**—Timer 0 Interrupt Request Enable High Bit **UORENH**—UART 0 Receive Interrupt Request Enable High Bit **UOTENH**—UART 0 Transmit Interrupt Request Enable High Bit **I2CENH**—I<sup>2</sup>C Interrupt Request Enable High Bit **SPIENH**—SPI Interrupt Request Enable High Bit **ADCENH**—ADC Interrupt Request Enable High Bit

#### Table 30. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6                                                       | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|----------|---------------------------------------------------------|---|----|----|---|---|---|--|

| FIELD | Reserved | Reserved T1ENL T0ENL U0RENL U0TENL I2CENL SPIENL ADCENL |   |    |    |   |   |   |  |

| RESET |          | 0                                                       |   |    |    |   |   |   |  |

| R/W   | R/W      |                                                         |   |    |    |   |   |   |  |

| ADDR  |          |                                                         |   | FC | 2H |   |   |   |  |

#### Reserved—Must be 0

**T1ENL**—Timer 1 Interrupt Request Enable Low Bit **T0ENL**—Timer 0 Interrupt Request Enable Low Bit **U0RENL**—UART 0 Receive Interrupt Request Enable Low Bit **U0TENL**—UART 0 Transmit Interrupt Request Enable Low Bit **I2CENL**—I<sup>2</sup>C Interrupt Request Enable Low Bit **SPIENL**—SPI Interrupt Request Enable Low Bit **ADCENL**—ADC Interrupt Request Enable Low Bit

# **IRQ1 Enable High and Low Bit Registers**

Table 31 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit Registers (Table 32 and Table 33) form a priority encoded enabling for interrupts in the Interrupt Request 1 Register. Priority is generated by setting bits in each register.

# **Timers**

Z8 Encore! XP<sup>®</sup> F0822 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated signals. The timer features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generators for any unused UART, SPI, or  $I^2C$  peripherals can also be used to provide basic timing functionality. See the respective serial communication peripheral chapters for information on using the Baud Rate Generators as timers.

# Architecture

Figure 10 displays the architecture of the timers.

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

All three Watchdog Timer Reload Registers must be written in this order. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes occur unless the sequence is restarted. The value in the Watchdog Timer Reload Registers is loaded into the counter when the WDT is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Control Register Definitions

## Watchdog Timer Control Register

The Watchdog Timer Control Register (WDTCTL), detailed in Table 48, is a Read-Only Register that indicates the source of the most recent Reset event, a Stop Mode Recovery event, and a WDT time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL address produce no effect on the bits in the WDTCTL. The locking mechanism prevents spurious writes to the Reload registers.

| BITS  | 7                         | 7 6 5 4 3 2 1 |  |    |    |  |  |  |

|-------|---------------------------|---------------|--|----|----|--|--|--|

| FIELD | POR STOP WDT EXT Reserved |               |  |    |    |  |  |  |

| RESET | See descriptions below 0  |               |  |    |    |  |  |  |

| R/W   | R                         |               |  |    |    |  |  |  |

| ADDR  |                           |               |  | FF | 0H |  |  |  |

#### Table 48. Watchdog Timer Control Register (WDTCTL)

| POR | STOP                  | WDT               | EXT                                                                                                                   |

|-----|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1   |                       |                   |                                                                                                                       |

|     | 0                     | 0                 | 0                                                                                                                     |

| 0   | 0                     | 0                 | 1                                                                                                                     |

| 0   | 0                     | 1                 | 0                                                                                                                     |

| 1   | 0                     | 0                 | 0                                                                                                                     |

| 1   | 0                     | 0                 | 0                                                                                                                     |

| 0   | 1                     | 0                 | 0                                                                                                                     |

| 0   | 1                     | 1                 | 0                                                                                                                     |

|     | 0<br>1<br>1<br>0<br>0 | 1 0<br>1 0<br>0 1 | 1         0         0           1         0         0           1         0         0           0         1         0 |

#### **POR—Power-On Reset Indicator**

If this bit is set to 1, a POR event occurred. This bit is reset to 0, if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0, when the register is read.

# Universal Asynchronous Receiver/Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator

- Selectable Multiprocessor (9-bit) mode with three configurable interrupt schemes

- BRG timer mode

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud Rate Generator. The UART's transmitter and receiver functions independently, but use the same baud rate and data format. Figure 11 on page 90 displays the UART architecture.

# **Clear To Send Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would be done during STOP bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## Multiprocessor (9-bit) Mode

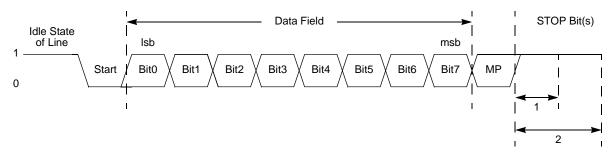

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit is transmitted following the 8-bits of data and immediately preceding the STOP bit(s) as displayed in Figure 14.

Figure 14. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 Registers provide Multiprocessor (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

## **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When multiprocessor mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software, or combination of the two depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not need to access the UART when it receives data directed to other devices on the When reading data from the slave, the  $I^2C$  pauses after the data Acknowledge cycle until the receive interrupt is serviced and the RDRF bit of the status register is cleared by reading the  $I^2C$  Data Register. Once the  $I^2C$  Data Register has been read, the  $I^2C$  reads the next data byte.

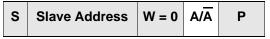

#### Address Only Transaction with a 7-bit Address

In the situation where software determines if a slave with a 7-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 26 on page 131 displays this "address only" transaction to determine if a slave with a 7-bit address will acknowledge. As an example, this transaction can be used after a "write" has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge, the transaction is repeated until the slave does Acknowledge.

Figure 26. 7-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable Transmit interrupts.

- 3. The I<sup>2</sup>C interrupt asserts, because the I<sup>2</sup>C Data Register is empty (TDRE = 1)

- 4. Software responds to the TDRE bit by writing a 7-bit Slave address plus write bit (=0) to the I<sup>2</sup>C Data Register. As an alternative this could be a read operation instead of a write operation.

- 5. Software sets the START and STOP bits of the I<sup>2</sup>C Control Register and clears the TXI bit.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  Slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

- 8. Software polls the STOP bit of the I<sup>2</sup>C Control Register. Hardware deasserts the STOP bit when the address only transaction is completed.

- 9. Software checks the ACK bit of the I<sup>2</sup>C Status Register. If the slave acknowledged, the ACK bit is equal to 1. If the slave does not acknowledge, the ACK bit is equal to 0. The NCKI interrupt does not occur in the not acknowledge case because the STOP bit was set.

## Write Transaction with a 7-Bit Address

Figure 27 displays the data transfer format for a 7-bit addressed slave. Shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

|--|

Figure 27. 7-Bit Addressed Slave Data Transfer Format

Follow the steps below for a transmit operation to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable Transmit Interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data Register is empty.

- 4. Software responds to the TDRE bit by writing a 7-bit Slave address plus write bit (=0) to the  $I^2C$  Data Register.

- 5. Software asserts the START bit of the  $I^2C$  Control Register.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  Slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

- 8. After one bit of address has been shifted out by the SDA signal, the Transmit Interrupt is asserted (TDRE = 1).

- 9. Software responds by writing the transmit data into the  $I^2C$  Data Register.

- 10. The  $I^2C$  Controller shifts the rest of the address and write bit out by the SDA signal.

- If the I<sup>2</sup>C Slave sends an acknowledge (by pulling the SDA signal low) during the next high period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 12.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore following steps).

- 12. The I<sup>2</sup>C Controller loads the contents of the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C Controller shifts the data out of using the SDA signal. After the first bit is sent, the Transmit Interrupt is asserted.

## **OCDCNTR Register**

The OCD contains a multipurpose 16-bit Counter Register. It can be used for the following:

- Count system clock cycles between Breakpoints.

- Generate a BRK when it counts down to zero.

- Generate a BRK when its value matches the Program Counter.

When configured as a counter, the OCDCNTR register starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH. The OCDCNTR register automatically resets itself to 0000H when the OCD exits DEBUG mode if it is configured to count clock cycles between breakpoints.

**Caution:** The OCDCNTR register is used by many of the OCD commands. It counts the number of bytes for the register and memory read/write commands. It holds the residual value when generating the CRC. Therefore, if the OCD-CNTR is being used to generate a BRK, its value should be written as a last step before leaving DEBUG mode.

Since this register is overwritten by various OCD commands, it should only be used to generate temporary breakpoints, such as stepping over CALL instructions or running to a specific instruction and stopping.

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8 Encore! XP F0822 Series products. When this option is enabled, several of the OCD commands are disabled. Table 93 on page 177 contains a summary of the OCD commands. Each OCD command is described further in the bulleted list. It also lists the commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

# Table 93. On-Chip Debugger Commands

| Debug Command                 | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                                            |

|-------------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision             | 00H             | Yes                                   | -                                                                                                                                                                                                 |

| Write OCD Counter<br>Register | 01H             | -                                     | -                                                                                                                                                                                                 |

| Read OCD Status<br>Register   | 02H             | Yes                                   | -                                                                                                                                                                                                 |

| Read OCD Counter<br>Register  | 03H             | -                                     | -                                                                                                                                                                                                 |

| Write OCD Control<br>Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                                                                                                                                                                          |

| Read OCD Control<br>Register  | 05H             | Yes                                   | -                                                                                                                                                                                                 |

| Write Program Counter         | 06H             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Counter          | 07H             | -                                     | Disabled                                                                                                                                                                                          |

| Write Register                | 08H             | -                                     | Only writes of the peripheral control<br>registers at address F00H-FFH are<br>allowed.<br>Additionally, only the Mass Erase<br>command is allowed to be written to the<br>Flash Control Register. |

| Read Register                 | 09H             | -                                     | Only reads of the peripheral control registers at address F00H-FFH are allowed.                                                                                                                   |

| Write Program Memory          | 0AH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory           | 0BH             | -                                     | Disabled                                                                                                                                                                                          |

| Write Data Memory             | 0CH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Data Memory              | 0DH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory<br>CRC    | 0EH             | -                                     | -                                                                                                                                                                                                 |

| Reserved                      | 0FH             | -                                     | -                                                                                                                                                                                                 |

| Step Instruction              | 10H             | -                                     | Disabled                                                                                                                                                                                          |

| Stuff Instruction             | 11H             | -                                     | Disabled                                                                                                                                                                                          |

177

## 187

# **DC Characteristics**

Table 97 lists the DC characteristics of the Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

# Table 97. DC Characteristics

|                  |                                            | T <sub>A</sub> = -40 °C to 105 °C |         |                      |       |                                                                                                                                |  |

|------------------|--------------------------------------------|-----------------------------------|---------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                  | Minimum                           | Typical | Maximum              | Units | Conditions                                                                                                                     |  |

| V <sub>DD</sub>  | Supply Voltage                             | 2.7                               | -       | 3.6                  | V     |                                                                                                                                |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage                 | -0.3                              | _       | 0.3*V <sub>DD</sub>  | V     | For all input pins except $\overline{RESET}$ , DBG, and XIN.                                                                   |  |

| V <sub>IL2</sub> | Low Level Input<br>Voltage                 | -0.3                              | -       | 0.2*V <sub>DD</sub>  | V     | For $\overline{RESET}$ , DBG, and XIN.                                                                                         |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage                | 0.7*V <sub>DD</sub>               | -       | 5.5                  | V     | Ports A and C pins when their programmable pull-ups are disabled.                                                              |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage                | 0.7*V <sub>DD</sub>               | _       | V <sub>DD</sub> +0.3 | V     | Port B pins. Ports A and C pins<br>when their programmable pull-<br>ups are enabled.                                           |  |

| V <sub>IH3</sub> | High Level Input<br>Voltage                | 0.8*V <sub>DD</sub>               | _       | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and XIN pins.                                                                                                      |  |

| V <sub>OL1</sub> | Low Level<br>Output Voltage                | -                                 | _       | 0.4                  | V     | I <sub>OL</sub> = 2 mA; VDD = 3.0 V<br>High Output Drive disabled.                                                             |  |

| V <sub>OH1</sub> | High Level<br>Output Voltage               | 2.4                               | _       | -                    | V     | I <sub>OH</sub> = -2 mA; VDD = 3.0 V<br>High Output Drive disabled.                                                            |  |

| V <sub>OL2</sub> | Low Level<br>Output Voltage<br>High Drive  | -                                 | _       | 0.6                  | V     | $I_{OL} = 20 \text{ mA}; \text{VDD} = 3.3 \text{ V}$<br>High Output Drive enabled<br>$T_A = -40 \text{ °C to } +70 \text{ °C}$ |  |

| V <sub>OH2</sub> | High Level<br>Output Voltage<br>High Drive | 2.4                               | _       | -                    | V     | $I_{OH} = -20$ mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A = -40$ °C to +70 °C                                       |  |

| V <sub>OL3</sub> | Low Level<br>Output Voltage<br>High Drive  | -                                 | _       | 0.6                  | V     | $I_{OL}$ = 15mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A$ = +70 °C to +105 °C                                        |  |

| V <sub>OH3</sub> | High Level<br>Output Voltage<br>High Drive | 2.4                               | -       | -                    | V     | $I_{OH}$ = 15 mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A$ = +70 °C to +105 °C                                       |  |

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

# Table 113. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H | 08H | (ADD dst, src) |

|---------------------------|-----|-----|-----|----------------|

| Object Code               | 04  | 08  | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

# Table 114. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 115 on page 211.

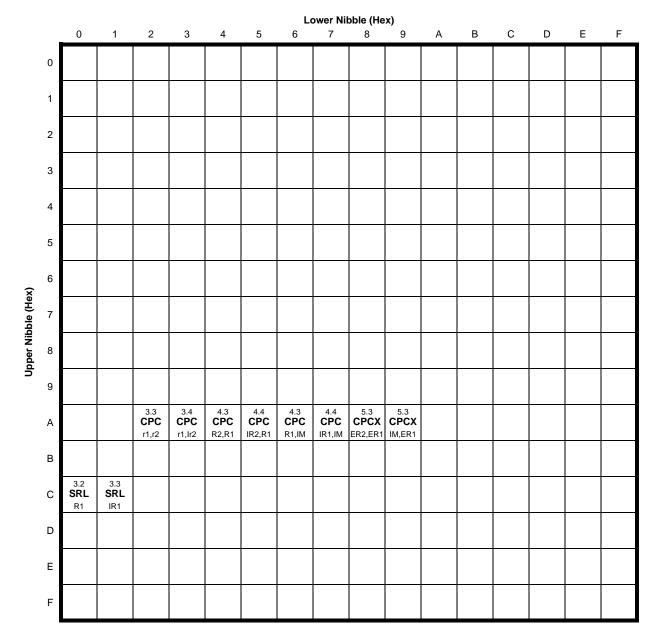

Figure 59. Second Opcode Map after 1FH

232

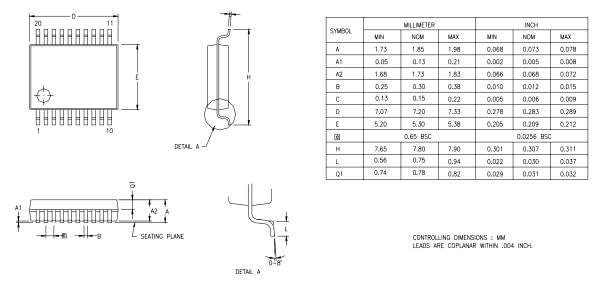

# Packaging

Figure 60 displays the 20-pin SSOP package available for Z8 Encore!  $XP^{\mbox{\sc B}}$  F0822 Series devices.

Figure 60. 20-Pin Small Shrink Outline Package (SSOP)

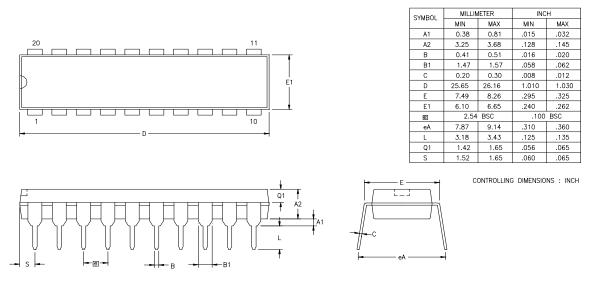

Figure 61 displays the 20-pin PDIP package available for Z8 Encore! XP F0822 Series devices.

Figure 61. 20-Pin Plastic Dual-Inline Package (PDIP)

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

compare 82 compare - extended addressing 214 compare mode 82 compare with carry 214 compare with carry - extended addressing 214 complement 217 complement carry flag 215, 216 condition code 211 continuous conversion (ADC) 148 continuous mode 81 control register definition, UART 100 control register, I2C 141 counter modes 81 CP 214 **CPC 214 CPCX 214** CPU and peripheral overview 3 CPU control instructions 216 CPX 214 Customer Feedback Form 251 customer feedback form 240 Customer Information 251

# D

DA 211. 214 data register, I2C 139 DC characteristics 187 debugger, on-chip 171 **DEC 214** decimal adjust 214 decrement 214 and jump non-zero 217 word 214 **DECW 214** destination operand 212 device, port availability 47 DI 216 direct address 211 disable interrupts 216 **DJNZ 217** DMA controller 5 dst 212

# E

EI 216 electrical characteristics 185 ADC 199 flash memory and timing 196 GPIO input data sample timing 200 watch-dog timer 197 enable interrupt 216 ER 211 extended addressing register 211 external pin reset 43 external RC oscillator 196 eZ8 features 3 eZ8 CPU features 3 eZ8 CPU instruction classes 214 eZ8 CPU instruction notation 210 eZ8 CPU instruction set 209 eZ8 CPU instruction summary 218

# F

FCTL register 159 features, Z8 Encore! 1 first opcode map 231 FLAGS 212 flags register 212 flash controller 4 option bit address space 163 option bit configuration - reset 163 program memory address 0001H 165 flash memory arrangement 154 byte programming 157 code protection 156 control register definitions 159 controller bypass 158 electrical characteristics and timing 196 flash control register 159 flash status register 160 frequency high and low byte registers 161 mass erase 158 operation 155

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.